#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 114                                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 144-LQFP                                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407zet6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introd | luction   |                                                                                                                         |

|---|--------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| 2 | Descr  | iption .  |                                                                                                                         |

|   | 2.1    | Full com  | patibility throughout the family                                                                                        |

|   | 2.2    | Device of | overview                                                                                                                |

|   |        | 2.2.1     | $ARM^{\textcircled{R}}$ Cortex <sup><math>\textcircled{R}</math></sup> -M4 core with FPU and embedded Flash and SRAM 20 |

|   |        | 2.2.2     | Adaptive real-time memory accelerator (ART Accelerator™)20                                                              |

|   |        | 2.2.3     | Memory protection unit                                                                                                  |

|   |        | 2.2.4     | Embedded Flash memory                                                                                                   |

|   |        | 2.2.5     | CRC (cyclic redundancy check) calculation unit                                                                          |

|   |        | 2.2.6     | Embedded SRAM                                                                                                           |

|   |        | 2.2.7     | Multi-AHB bus matrix                                                                                                    |

|   |        | 2.2.8     | DMA controller (DMA)                                                                                                    |

|   |        | 2.2.9     | Flexible static memory controller (FSMC)23                                                                              |

|   |        | 2.2.10    | Nested vectored interrupt controller (NVIC)                                                                             |

|   |        | 2.2.11    | External interrupt/event controller (EXTI)                                                                              |

|   |        | 2.2.12    | Clocks and startup                                                                                                      |

|   |        | 2.2.13    | Boot modes                                                                                                              |

|   |        | 2.2.14    | Power supply schemes                                                                                                    |

|   |        | 2.2.15    | Power supply supervisor                                                                                                 |

|   |        | 2.2.16    | Voltage regulator                                                                                                       |

|   |        | 2.2.17    | Regulator ON/OFF and internal reset ON/OFF availability                                                                 |

|   |        | 2.2.18    | Real-time clock (RTC), backup SRAM and backup registers                                                                 |

|   |        | 2.2.19    | Low-power modes                                                                                                         |

|   |        | 2.2.20    | V <sub>BAT</sub> operation                                                                                              |

|   |        | 2.2.21    | Timers and watchdogs                                                                                                    |

|   |        | 2.2.22    | Inter-integrated circuit interface (I <sup>2</sup> C)                                                                   |

|   |        | 2.2.23    | Universal synchronous/asynchronous receiver transmitters (USART) . 34                                                   |

|   |        | 2.2.24    | Serial peripheral interface (SPI)                                                                                       |

|   |        | 2.2.25    | Inter-integrated sound (I2S) 35                                                                                         |

|   |        | 2.2.26    | Audio PLL (PLLI2S)                                                                                                      |

|   |        | 2.2.27    | Secure digital input/output interface (SDIO)                                                                            |

|   |        | 2.2.28    | Ethernet MAC interface with dedicated DMA and IEEE 1588 support . 36                                                    |

|   |        | 2.2.29    | Controller area network (bxCAN)                                                                                         |

| recommended footprint                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ball grid array package outline                                              | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ball grid array recommended footprint                                        | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UFBGA176+25 marking example (package top view)1                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline          | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint 18 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LQFP176 marking example (package top view)18                                 | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as peripheral-only and used                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| in Full speed mode                                                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as host-only and used in full speed mode           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured in dual mode and used in full speed mode           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as peripheral, host, or dual-mode                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and used in high speed mode                                                  | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MII mode using a 25 MHz crystal                                              | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RMII with a 50 MHz oscillator                                                | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RMII with a 25 MHz crystal and PHY with PLL19                                | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                              | ball grid array package outline11UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch11ball grid array recommended footprint11UFBGA176+25 marking example (package top view)11LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline14LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint.16LQFP176 marking example (package top view)16USB controller configured as peripheral-only and used16in Full speed mode16USB controller configured as host-only and used in full speed mode16USB controller configured as peripheral, host, or dual-mode16and used in high speed mode16MII mode using a 25 MHz crystal16RMII with a 50 MHz oscillator16 |

# 2.2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU and embedded Flash and SRAM

The ARM Cortex-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4 32-bit RISC processor with FPU features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F405xx and STM32F407xx family is compatible with all ARM tools and software.

*Figure 5* shows the general block diagram of the STM32F40xxx family.

Note: Cortex-M4 with FPU is binary compatible with Cortex-M3.

## 2.2.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM Cortex-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 210 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 168 MHz.

## 2.2.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

## 2.2.4 Embedded Flash memory

The STM32F40xxx devices embed a Flash memory of 512 Kbytes or 1 Mbytes available for storing programs and data.

DocID022152 Rev 8

Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the  $V_{12}$  domain is controlled by an external power.

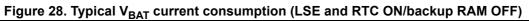

## 2.2.20 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is not connected to  $V_{DD}$  (internal reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

## 2.2.21 Timers and watchdogs

The STM32F405xx and STM32F407xx devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 4* compares the features of the advanced-control, general-purpose and basic timers.

| Timer<br>type        | Timer         | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) |

|----------------------|---------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|---------------------------|------------------------------------|--------------------------------|

| Advanceo<br>-control | TIM1,<br>TIM8 | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                       | 84                                 | 168                            |

Table 4. Timer feature comparison

|   |      | •              |        |       |      |      |        |      |      |        |

|---|------|----------------|--------|-------|------|------|--------|------|------|--------|

|   | 10   | 9              | 8      | 7     | 6    | 5    | 4      | 3    | 2    | 1      |

| A | VBAT | PC13           | PDR_ON | BOOT0 | PB4  | PD7  | PD4    | PC12 | PA14 | VDD    |

| В | PC14 | PC15           | VDD    | PB7   | PB3  | PD6  | PD2    | PA15 | PI1  | VCAP_2 |

| С | PA0  | vss            | PB9    | PB6   | PD5  | PD1  | PC11   | PI0  | PA12 | PA11   |

| D | PC2  | BYPASS_<br>REG | PB8    | PB5   | PD0  | PC10 | PA13   | PA10 | PA9  | PA8    |

| E | PC0  | PC3            | vss    | VSS   | VDD  | VSS  | VDD    | PC9  | PC8  | PC7    |

| F | PH0  | PH1            | PA1    | VDD   | PE10 | PE14 | VCAP_1 | PC6  | PD14 | PD15   |

| G | NRST | VDDA           | PA5    | PB0   | PE7  | PE13 | PE15   | PD10 | PD12 | PD11   |

| н | VSSA | PA3            | PA6    | PB1   | PE8  | PE12 | PB10   | PD9  | PD8  | PB15   |

| J | PA2  | PA4            | PA7    | PB2   | PE9  | PE11 | PB11   | PB12 | PB14 | PB13   |

|   | •    | :              |        |       |      | 1    | 1      |      | :    |        |

Figure 17. STM32F40xxx WLCSP90 ballout

1. This figure shows the package bump view.

| Table 6. Legend/abbreviations used in the | pinout table |

|-------------------------------------------|--------------|

|-------------------------------------------|--------------|

| Name                   | Abbreviation                                   | Definition                                                                                         |  |  |  |  |  |

|------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin name               |                                                | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |

|                        | S                                              | Supply pin                                                                                         |  |  |  |  |  |

| Pin type               | I                                              | Input only pin                                                                                     |  |  |  |  |  |

|                        | I/O                                            | Input / output pin                                                                                 |  |  |  |  |  |

|                        | FT                                             | 5 V tolerant I/O                                                                                   |  |  |  |  |  |

|                        | ТТа                                            | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |  |

| I/O structure          | B Dedicated BOOT0 pin                          |                                                                                                    |  |  |  |  |  |

|                        | RST                                            | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |  |  |

| Notes                  | Unless otherwise                               | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |

| Alternate<br>functions | Functions selected through GPIOx_AFR registers |                                                                                                    |  |  |  |  |  |

| Additional functions   | Functions directly                             | selected/enabled through peripheral registers                                                      |  |  |  |  |  |

|        | F       | Pin r   | numb    |          |         |                                                                   |                     |    |                         | demittions (continued)                                                                                     |   |

|--------|---------|---------|---------|----------|---------|-------------------------------------------------------------------|---------------------|----|-------------------------|------------------------------------------------------------------------------------------------------------|---|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup>              | Alternate functions |    | Additional<br>functions |                                                                                                            |   |

| 29     | H4      | 47      | 69      | R12      | 79      | PB10                                                              | I/O                 | FT | -                       | SPI2_SCK / I2S2_CK /<br>I2C2_SCL/ USART3_TX /<br>OTG_HS_ULPI_D3 /<br>ETH_MII_RX_ER /<br>TIM2_CH3/ EVENTOUT | - |

| 30     | J4      | 48      | 70      | R13      | 80      | PB11                                                              | I/O                 | FT | -                       | I2C2_SDA/USART3_RX/<br>OTG_HS_ULPI_D4 /<br>ETH_RMII_TX_EN/<br>ETH_MII_TX_EN /<br>TIM2_CH4/ EVENTOUT        | - |

| 31     | F4      | 49      | 71      | M10      | 81      | V <sub>CAP_1</sub>                                                | S                   |    | -                       | -                                                                                                          | - |

| 32     | -       | 50      | 72      | N10      | 82      | V <sub>DD</sub>                                                   | S                   |    | -                       | -                                                                                                          | - |

| -      | -       | -       | -       | M11      | 83      | PH6 I/O FT - I2C2_SMBA / TIM12_CH1 /<br>ETH_MII_RXD2/<br>EVENTOUT |                     | -  |                         |                                                                                                            |   |

| -      | -       | -       | -       | N12      | 84      | PH7                                                               | I/O                 | FT | -                       | I2C3_SCL /<br>ETH_MII_RXD3/<br>EVENTOUT                                                                    | - |

| -      | -       | -       | -       | M12      | 85      | PH8                                                               | I/O                 | FT | -                       | I2C3_SDA /<br>DCMI_HSYNC/<br>EVENTOUT                                                                      | - |

| -      | -       | -       | -       | M13      | 86      | PH9                                                               | I/O                 | FT | -                       | I2C3_SMBA / TIM12_CH2/<br>DCMI_D0/ EVENTOUT                                                                | - |

| -      | -       | -       | -       | L13      | 87      | PH10                                                              | I/O                 | FT | -                       | TIM5_CH1 / DCMI_D1/<br>EVENTOUT                                                                            | - |

| -      | -       | -       | -       | L12      | 88      | PH11                                                              | I/O                 | FT | -                       | TIM5_CH2 / DCMI_D2/<br>EVENTOUT                                                                            | - |

| -      | -       | -       | -       | K12      | 89      | PH12                                                              | I/O                 | FT | -                       | TIM5_CH3 / DCMI_D3/<br>EVENTOUT                                                                            | - |

| -      | -       | -       | I       | H12      | 90      | V <sub>SS</sub>                                                   | S                   | -  | -                       | -                                                                                                          | - |

| -      | -       | -       | -       | J12      | 91      | $V_{DD}$                                                          | S                   | -  | -                       | -                                                                                                          | - |

Table 7. STM32F40xxx pin and ball definitions (continued)

|        | I       | Pin r   | numb    | er       |         |                                                      |          |                 |       |                                                                          |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|--------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                      | Additional<br>functions |

| -      | A4      | 85      | 118     | D10      | 146     | PD4                                                  | I/O      | FT              | -     | FSMC_NOE/<br>USART2_RTS/<br>EVENTOUT                                     | -                       |

| -      | C6      | 86      | 119     | C11      | 147     | PD5                                                  | I/O      | FT              | -     | FSMC_NWE/USART2_TX/<br>EVENTOUT                                          | -                       |

| -      | -       | -       | 120     | D8       | 148     | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                        | -                       |

| -      | -       | -       | 121     | C8       | 149     | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                        | -                       |

| -      | B5      | 87      | 122     | B11      | 150     | PD6                                                  | I/O      | FT              | -     | FSMC_NWAIT/<br>USART2_RX/ EVENTOUT                                       | -                       |

| -      | A5      | 88      | 123     | A11      | 151     | PD7                                                  | I/O      | FT              | -     | USART2_CK/FSMC_NE1/<br>FSMC_NCE2/ EVENTOUT                               | -                       |

| -      | -       | -       | 124     | C10      | 152     | PG9                                                  | I/O      | FT              | -     | USART6_RX /<br>FSMC_NE2/FSMC_NCE3/<br>EVENTOUT                           | -                       |

| -      | -       | -       | 125     | B10      | 153     | PG10                                                 | I/O      | FT              | -     | FSMC_NCE4_1/<br>FSMC_NE3/ EVENTOUT                                       | -                       |

| -      | -       | -       | 126     | В9       | 154     | PG11                                                 | I/O      | FT              | -     | FSMC_NCE4_2 /<br>ETH_MII_TX_EN/<br>ETH_RMII_TX_EN/<br>EVENTOUT           | -                       |

| -      | -       | -       | 127     | B8       | 155     | PG12                                                 | I/O      | FT              | -     | FSMC_NE4 /<br>USART6_RTS/<br>EVENTOUT                                    | -                       |

| -      | -       | -       | 128     | A8       | 156     | PG13                                                 | I/O      | FT              | -     | FSMC_A24 /<br>USART6_CTS<br>/ETH_MII_TXD0/<br>ETH_RMII_TXD0/<br>EVENTOUT | -                       |

| -      | -       | -       | 129     | A7       | 157     | PG14                                                 | I/O      | FT              | -     | FSMC_A25 / USART6_TX<br>/ETH_MII_TXD1/<br>ETH_RMII_TXD1/<br>EVENTOUT     | -                       |

| -      | E8      | -       | 130     | D7       | 158     | $V_{SS}$                                             | S        | -               | -     | -                                                                        | -                       |

| -      | F7      | -       | 131     | C7       | 159     | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                        | -                       |

| -      | -       | -       | 132     | B7       | 160     | PG15                                                 | I/O      | FT              | -     | USART6_CTS /<br>DCMI_D13/ EVENTOUT                                       | -                       |

Table 7. STM32F40xxx pin and ball definitions (continued)

69/202

DocID022152 Rev 8

|        |      | 1   | r      | 1        | 1                |               |                                |                      |                        |                    | ``                        | ,                   |              | 1                    | 1              | r    | ,        |

|--------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|---------------------|--------------|----------------------|----------------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10                | AF11         | AF12                 | AF13           |      |          |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS   | ЕТН          | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PH0  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH1  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH2  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | ETH _MII_CRS | -                    | -              | -    | EVENTOUT |

|        | PH3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | ETH _MII_COL | -                    | -              | -    | EVENTOUT |

|        | PH4  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>NXT | -            | -                    | -              | -    | EVENTOUT |

|        | PH5  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH6  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | TIM12_CH1                 | -                   | ETH_MII_RXD2 | -                    | -              | -    | EVENTOUT |

| DestU  | PH7  | -   | -      | -        | -                | I2C3_SCL      | -                              | -                    | -                      | -                  | -                         | -                   | ETH_MII_RXD3 | -                    | -              | -    | EVENTOUT |

| Port H | PH8  | -   | -      | -        | -                | I2C3_SDA      | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_<br>HSYNC | -    | EVENTOUT |

|        | PH9  | -   | -      | -        | -                | I2C3_<br>SMBA | -                              | -                    | -                      | -                  | TIM12_CH2                 | -                   | -            | -                    | DCMI_D0        | -    | EVENTOUT |

|        | PH10 | -   | -      | TIM5_CH1 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D1        | -    | EVENTOUT |

|        | PH11 | -   | -      | TIM5_CH2 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D2        | -    | EVENTOUT |

|        | PH12 | -   | -      | TIM5_CH3 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D3        | -    | EVENTOUT |

|        | PH13 | -   | -      | -        | TIM8_CH1N        | -             | -                              | -                    | -                      | -                  | CAN1_TX                   | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH14 | -   | -      | -        | TIM8_CH2N        | -             | -                              | -                    | -                      | -                  | -                         | -                   | =            | -                    | DCMI_D4        | -    | EVENTOUT |

|        | PH15 | -   | -      | -        | TIM8_CH3N        | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D11       | -    | EVENTOUT |

Table 9. Alternate function mapping (continued)

577

|          |                                                |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |

|----------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol   | Parameter                                      | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|          | Supply<br>current in<br>Stop mode              | Flash in Stop mode, low-speed and high-<br>speed internal RC oscillators and high-speed<br>oscillator OFF (no independent watchdog)              | 0.45                      | 1.5                       | 11.00                     | 20.00                      |      |

|          | with main<br>regulator in<br>Run mode          | Flash in Deep power-down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.40                      | 1.5                       | 11.00                     | 20.00                      | mA   |

| IDD_STOP | Supply<br>current in<br>Stop mode              | Flash in Stop mode, low-speed and high-<br>speed internal RC oscillators and high-speed<br>oscillator OFF (no independent watchdog)              | 0.31                      | 1.1                       | 8.00                      | 15.00                      | ША   |

|          | with main<br>regulator in<br>Low-power<br>mode | Flash in Deep power-down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.28                      | 1.1                       | 8.00                      | 15.00                      |      |

| Table 23. Typical and maximum current consumptions in Stop mode | Table 23. | Typical and | maximum | current | consum | ptions | in Sto | p mode |

|-----------------------------------------------------------------|-----------|-------------|---------|---------|--------|--------|--------|--------|

|-----------------------------------------------------------------|-----------|-------------|---------|---------|--------|--------|--------|--------|

# Table 24. Typical and maximum current consumptions in Standby mode

|          |                           |                                                      |                                   | Тур                        |                            |                            | Max <sup>(1)</sup> |    |  |

|----------|---------------------------|------------------------------------------------------|-----------------------------------|----------------------------|----------------------------|----------------------------|--------------------|----|--|

| Symbol   | Parameter                 | Conditions                                           | Conditions T <sub>A</sub> = 25 °C |                            | T <sub>A</sub> =<br>85 °C  | T <sub>A</sub> =<br>105 °C | Unit               |    |  |

|          |                           |                                                      | V <sub>DD</sub> =<br>1.8 V        | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> = 3.6 V    |                    |    |  |

|          |                           | Backup SRAM ON, low-<br>speed oscillator and RTC ON  | 3.0                               | 3.4                        | 4.0                        | 20                         | 36                 |    |  |

|          | Supply current in Standby | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                               | 2.7                        | 3.3                        | 16                         | 32                 | ]  |  |

| IDD_STBY | mode                      | Backup SRAM ON, RTC<br>OFF                           | 2.4                               | 2.6                        | 3.0                        | 12.5                       | 24.8               | μA |  |

|          |                           | Backup SRAM OFF, RTC<br>OFF                          | 1.7                               | 1.9                        | 2.2                        | 9.8                        | 19.2               |    |  |

1. Guaranteed by characterization.

| Symbol                   |                            |                                                  | Тур                            |                             |                                | Ма                 |                            |      |  |

|--------------------------|----------------------------|--------------------------------------------------|--------------------------------|-----------------------------|--------------------------------|--------------------|----------------------------|------|--|

|                          | Parameter                  | Parameter Conditions                             |                                | T <sub>A</sub> = 25 °C      |                                |                    | T <sub>A</sub> =<br>105 °C | Unit |  |

|                          |                            |                                                  | V <sub>BAT</sub><br>=<br>1.8 V | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub><br>=<br>3.3 V | V <sub>BAT</sub> = | = 3.6 V                    |      |  |

|                          | Backup<br>domain<br>supply | Backup SRAM ON, low-speed oscillator and RTC ON  | 1.29                           | 1.42                        | 1.68                           | 6                  | 11                         |      |  |

| I <sub>DD_VBA</sub><br>T |                            | Backup SRAM OFF, low-speed oscillator and RTC ON | 0.62                           | 0.73                        | 0.96                           | 3                  | 5                          | μA   |  |

|                          | current                    | Backup SRAM ON, RTC OFF                          | 0.79                           | 0.81                        | 0.86                           | 5                  | 10                         |      |  |

|                          |                            | Backup SRAM OFF, RTC OFF                         | 0.10                           | 0.10                        | 0.10                           | 2                  | 4                          |      |  |

| Table 25. Typical and maximum current consumptions in V <sub>BAT</sub> mode |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

1. Guaranteed by characterization.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 28*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog pins by firmware.

- All peripherals are disabled unless otherwise mentioned

- The code is running from Flash memory and the Flash memory access time is equal to 5 wait states at 168 MHz.

- The code is running from Flash memory and the Flash memory access time is equal to 4 wait states at 144 MHz, and the power scale mode is set to 2.

- The ART accelerator is ON.

- The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- When the peripherals are enabled: HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

- The typical values are obtained for V<sub>DD</sub> = 3.3 V and T<sub>A</sub>= 25 °C, unless otherwise specified.

|                 |                                                    | I <sub>DD</sub> (T       | yp) <sup>(1)</sup>        |        |

|-----------------|----------------------------------------------------|--------------------------|---------------------------|--------|

| Perip           | heral                                              | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz) | Unit   |

|                 | GPIOA                                              | 2.70                     | 2.40                      |        |

|                 | GPIOB                                              | 2.50                     | 2.22                      |        |

|                 | GPIOC                                              | 2.54                     | 2.28                      |        |

|                 | GPIOD                                              | 2.55                     | 2.28                      |        |

|                 | GPIOE                                              | 2.68                     | 2.40                      |        |

|                 | GPIOF                                              | 2.53                     | 2.28                      |        |

|                 | GPIOG                                              | 2.51                     | 2.22                      |        |

|                 | GPIOH                                              | 2.51                     | 2.22                      |        |

| AHB1            | GPIOI                                              | 2.50                     | 2.22                      | µA/MHz |

| (up to 168 MHz) | OTG_HS+ULPI                                        | 28.33                    | 25.38                     |        |

|                 | CRC                                                | 0.41                     | 0.40                      |        |

|                 | BKPSRAM                                            | 0.63                     | 0.58                      |        |

|                 | DMA1                                               | 37.44                    | 33.58                     |        |

|                 | DMA2                                               | 37.69                    | 33.93                     |        |

|                 | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 20.43                    | 18.39                     |        |

Table 28. Peripheral current consumption

DocID022152 Rev 8

A device reset allows normal operations to be resumed.

The test results are given in *Table 43*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 4A              |

#### Table 43. EMS characteristics

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

## 5.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

## Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 47.

## **USB OTG FS characteristics**

This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |

|-------------------------------------|-------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |

Table 57. USB OTG FS startup time

1. Guaranteed by design.

| Sym              | bol                                  | Parameter                                                 | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|------------------|--------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

| Input            | $V_{DD}$                             | USB OTG FS operating<br>voltage                           | -                                                                | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

|                  | V <sub>DI</sub> <sup>(3)</sup>       | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |

| levels           | V <sub>CM</sub> <sup>(3)</sup>       | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                  | $V_{SE}^{(3)}$                       | Single ended receiver threshold                           | -                                                                | 1.3                 | -    | 2.0                 |      |

| Output<br>levels | V <sub>OL</sub>                      | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 V $^{(4)}$               | -                   | -    | 0.3                 | V    |

|                  | V <sub>OH</sub>                      | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| Б                |                                      | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |

| R <sub>F</sub>   | 'nD                                  | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                        | 0.65                | 1.1  | 2.0                 | kΩ   |

|                  | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP) |                                                           | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |

| R <sub>PU</sub>  |                                      | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |

### Table 58. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F405xx and STM32F407xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design.

4.  $\ensuremath{\,\mathsf{R}_{\mathsf{L}}}$  is the load connected on the USB OTG FS drivers

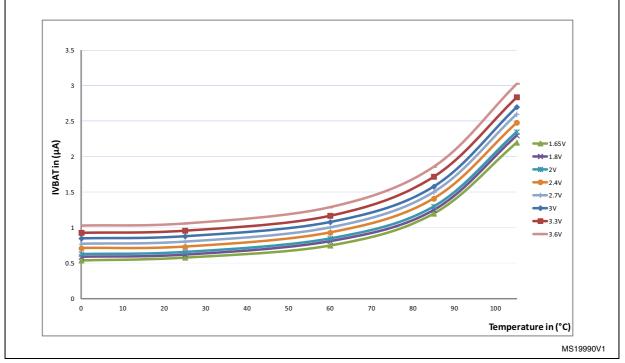

### **Ethernet characteristics**

Unless otherwise specified, the parameters given in *Table 64*, *Table 65* and *Table 66* for SMI, RMII and MII are derived from tests performed under the ambient temperature, f<sub>HCLK</sub> frequency summarized in *Table 14* and VDD supply voltage conditions summarized in *Table 63*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 5.3.16: I/O port characteristics for more details on the input/output characteristics.

| Symb        | ol              | Parameter                  | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|-------------|-----------------|----------------------------|---------------------|---------------------|------|

| Input level | V <sub>DD</sub> | Ethernet operating voltage | 2.7                 | 3.6                 | V    |

Table 63. Ethernet DC electrical characteristics

1. All the voltages are measured from the local ground potential.

*Table 64* gives the list of Ethernet MAC signals for the SMI (station management interface) and *Figure 46* shows the corresponding timing diagram.

#### Figure 46. Ethernet SMI timing diagram

| Symbol                | Parameter                | Min | Тур | Max | Unit |

|-----------------------|--------------------------|-----|-----|-----|------|

| t <sub>MDC</sub>      | MDC cycle time(2.38 MHz) | 411 | 420 | 425 |      |

| T <sub>d(MDIO)</sub>  | Write data valid time    | 6   | 10  | 13  | ne   |

| t <sub>su(MDIO)</sub> | Read data setup time     | 12  | -   | -   | ns   |

| t <sub>h(MDIO)</sub>  | Read data hold time      | 0   | -   | -   |      |

1. Guaranteed by characterization.

*Table 65* gives the list of Ethernet MAC signals for the RMII and *Figure 47* shows the corresponding timing diagram.

#### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k - 0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                                                                                                       | Тур  | Max <sup>(1)</sup> | Unit |  |

|--------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|--|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 60 MHz,<br>f <sub>ADC</sub> = 30 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 1.8 <sup>(2)</sup> to 3.6 V | ±2   | ±5                 | LSB  |  |

| EO     | Offset error                 |                                                                                                                                       | ±1.5 | ±2.5               |      |  |

| EG     | Gain error                   |                                                                                                                                       | ±1.5 | ±3                 |      |  |

| ED     | Differential linearity error |                                                                                                                                       | ±1   | ±2                 |      |  |

| EL     | Integral linearity error     |                                                                                                                                       | ±1.5 | ±3                 |      |  |

1. Guaranteed by characterization.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

Note:

te: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and SI<sub>INJ(PIN)</sub> in Section 5.3.16 does not affect the ADC accuracy.

| Symbol                      | Parameter                                    | Min                     | Max | Unit |

|-----------------------------|----------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period                              | 2T <sub>HCLK</sub> –0.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x=02)          | -                       | 0.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>   | FSMC_CLK low to FSMC_NEx high (x= 02)        | 0                       | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                | -                       | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high               | 3                       | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -                       | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>    | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 2                       | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FSMC_CLK low to FSMC_NOE low                 | -                       | 0.5 | ns   |

| t <sub>d(CLKL-NOEH)</sub>   | FSMC_CLK low to FSMC_NOE high                | 1.5                     | -   | ns   |

| t <sub>su(DV-CLKH)</sub>    | FSMC_D[15:0] valid data before FSMC_CLK high | 6                       | -   | ns   |

| t <sub>h(CLKH-DV)</sub>     | FSMC_D[15:0] valid data after FSMC_CLK high  | 3                       | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high        | 4                       | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high         | 0                       | -   | ns   |

Table 81. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

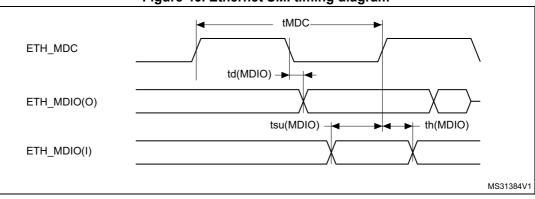

Figure 64. PC Card/CompactFlash controller waveforms for attribute memory read access

1. Only data bits 0...7 are read (bits 8...15 are disregarded).

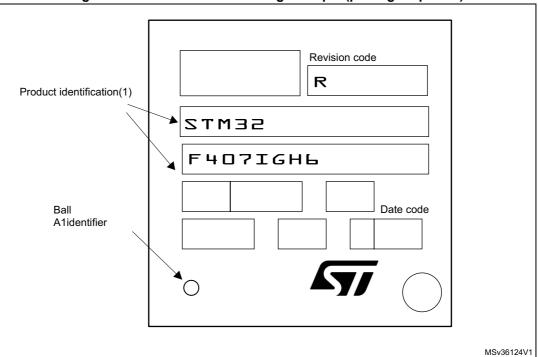

#### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking and ball A 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 89. UFBGA176+25 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 7 Part numbering

| Example:                                                   | STM32 | F | 405 R | E | Т | 6 | xxx |

|------------------------------------------------------------|-------|---|-------|---|---|---|-----|

| Device family                                              |       |   |       |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller                   |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Product type                                               |       |   |       |   |   |   |     |

| F = general-purpose                                        |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Device subfamily                                           |       |   |       |   |   |   |     |

| 405 = STM32F40xxx, connectivity                            |       |   |       |   |   |   |     |

| 407= STM32F40xxx, connectivity, camera interface, Ethernet |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Pin count                                                  |       |   |       |   |   |   |     |

| R = 64 pins                                                |       |   |       |   |   |   |     |

| O = 90 pins                                                |       |   |       |   |   |   |     |

| V = 100 pins                                               |       |   |       |   |   |   |     |

| Z = 144 pins                                               |       |   |       |   |   |   |     |