#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 114                                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 144-LQFP                                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407zgt6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 40. | SPI timing diagram - slave mode and CPHA = 1                                                 | 124 |

|------------|----------------------------------------------------------------------------------------------|-----|

| Figure 41. | SPI timing diagram - master mode                                                             |     |

| Figure 42. | I2S slave timing diagram (Philips protocol)                                                  | 127 |

| Figure 43. | I2S master timing diagram (Philips protocol) <sup>(1)</sup>                                  |     |

| Figure 44. | USB OTG FS timings: definition of data signal rise and fall time                             |     |

| Figure 45. | ULPI timing diagram                                                                          |     |

| Figure 46. | Ethernet SMI timing diagram                                                                  |     |

| Figure 47. | Ethernet RMII timing diagram                                                                 |     |

| Figure 48. | Ethernet MII timing diagram                                                                  |     |

| Figure 49. | ADC accuracy characteristics                                                                 |     |

| Figure 50. | Typical connection diagram using the ADC                                                     |     |

| Figure 51. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 52. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     |     |

| Figure 53. | 12-bit buffered /non-buffered DAC                                                            |     |

| Figure 54. | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                                   |     |

| Figure 55. | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                                  |     |

| Figure 56. | Asynchronous multiplexed PSRAM/NOR read waveforms.                                           |     |

| Figure 57. | Asynchronous multiplexed PSRAM/NOR write waveforms                                           |     |

| Figure 58. | Synchronous multiplexed NOR/PSRAM read timings                                               |     |

| Figure 59. | Synchronous multiplexed PSRAM write timings                                                  |     |

| Figure 60. | Synchronous non-multiplexed NOR/PSRAM read timings                                           |     |

| Figure 61. | Synchronous non-multiplexed PSRAM write timings                                              |     |

| Figure 62. | PC Card/CompactFlash controller waveforms for common memory read access                      |     |

| Figure 63. | PC Card/CompactFlash controller waveforms for common memory write access                     | 154 |

| Figure 64. | PC Card/CompactFlash controller waveforms for attribute memory read                          |     |

|            | access                                                                                       | 155 |

| Figure 65. | PC Card/CompactFlash controller waveforms for attribute memory write                         |     |

|            | access                                                                                       |     |

| Figure 66. | PC Card/CompactFlash controller waveforms for I/O space read access                          |     |

| Figure 67. | PC Card/CompactFlash controller waveforms for I/O space write access                         |     |

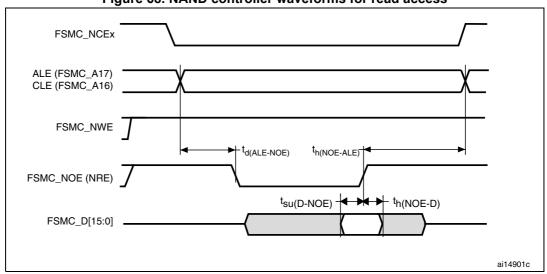

| Figure 68. | NAND controller waveforms for read access                                                    |     |

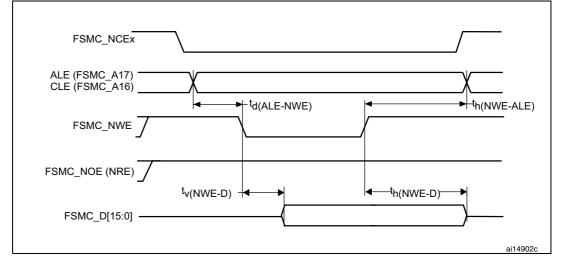

| Figure 69. | NAND controller waveforms for write access                                                   |     |

| Figure 70. | NAND controller waveforms for common memory read access                                      |     |

| Figure 71. | NAND controller waveforms for common memory write access                                     |     |

| Figure 72. | DCMI timing diagram                                                                          |     |

| Figure 73. | SDIO high-speed mode                                                                         |     |

| Figure 74. | SD default mode                                                                              | 163 |

| Figure 75. | WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale                            |     |

|            | package outline                                                                              | 164 |

| Figure 76. | WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale                            |     |

|            | recommended footprint                                                                        |     |

| Figure 77. | WLCSP90 marking example (package top view)                                                   |     |

| Figure 78. | LQFP64 – 64-pin, 10 x 10 mm low-profile quad flat package outline                            | 167 |

| Figure 79. | LQFP64 – 64-pin, 10 x 10 mm low-profile quad flat package                                    |     |

|            | recommended footprint                                                                        |     |

| Figure 80. | LPQF64 marking example (package top view)                                                    |     |

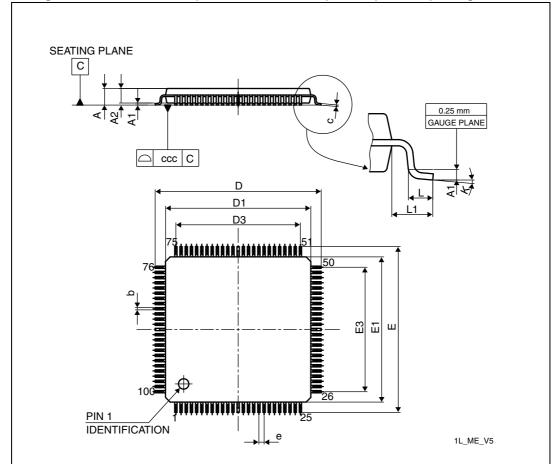

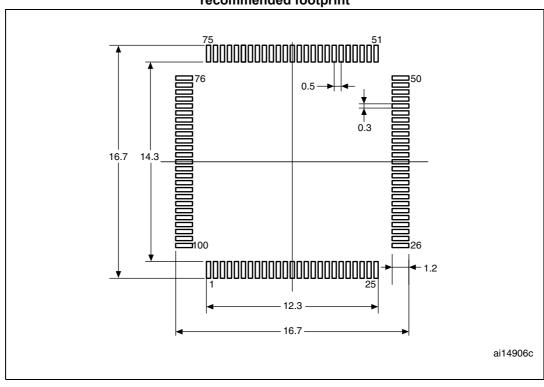

| Figure 81. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                          | 170 |

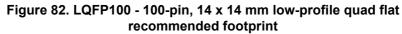

| Figure 82. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          |     |

|            | recommended footprint                                                                        |     |

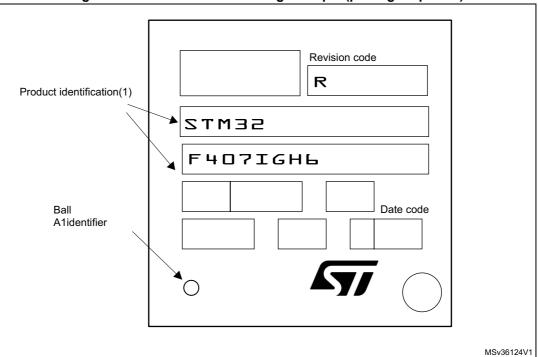

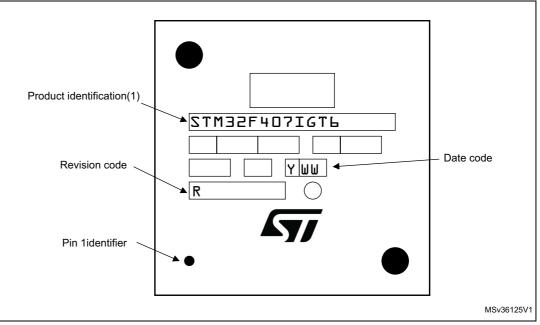

| Figure 83. | LQFP100 marking example (package top view)                                                   |     |

| Figure 84. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline                          | 173 |

| Figure 85. | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package                                   |     |

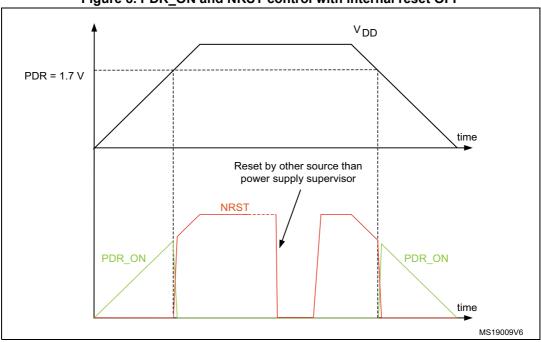

Figure 8. PDR\_ON and NRST control with internal reset OFF

### 2.2.16 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

### **Regulator ON**

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. Refer to *Table 14: General operating conditions*.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

- The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost)

Two external ceramic capacitors should be connected on V<sub>CAP\_1</sub> & V<sub>CAP\_2</sub> pin. Refer to *Figure 21: Power supply scheme* and *Figure 16: VCAP\_1/VCAP\_2 operating conditions*.

All packages have regulator ON feature.

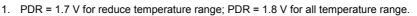

### **Regulator OFF**

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a  $V_{12}$  voltage source through  $V_{CAP_1}$  and  $V_{CAP_2}$  pins.

Since the internal voltage scaling is not manage internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu\text{F}$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

Refer to Figure 21: Power supply scheme

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The standby mode is not available

#### Figure 9. Regulator OFF

alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 84 MHz.

### 2.2.35 Analog-to-digital converters (ADCs)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

### 2.2.36 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.8 V and 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

### 2.2.37 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

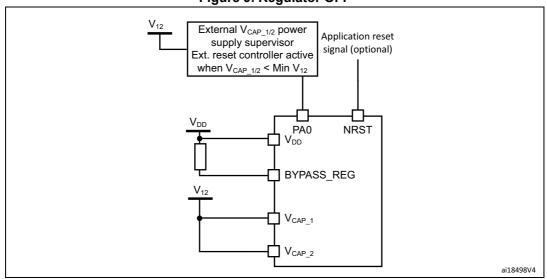

### 3 Pinouts and pin description

1. The above figure shows the package top view.

|        | I       | Pin r   | numb    |          |         |                                                      |          |                 |       | definitions (continued)                                                                                         |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                             | Additional<br>functions |

|        | D9      |         |         | L4       | 48      | BYPASS_REG                                           | Ι        | FT              | -     | -                                                                                                               | -                       |

| 19     | E4      | 28      | 39      | K4       | 49      | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                               | -                       |

| 20     | J9      | 29      | 40      | N4       | 50      | PA4                                                  | I/O      | TTa             | (4)   | SPI1_NSS / SPI3_NSS /<br>USART2_CK /<br>DCMI_HSYNC /<br>OTG_HS_SOF/ I2S3_WS/<br>EVENTOUT                        | ADC12_IN4<br>/DAC_OUT1  |

| 21     | G8      | 30      | 41      | P4       | 51      | PA5                                                  | I/O      | ТТа             | (4)   | SPI1_SCK/<br>OTG_HS_ULPI_CK /<br>TIM2_CH1_ETR/<br>TIM8_CH1N/ EVENTOUT                                           | ADC12_IN5/DAC_<br>OUT2  |

| 22     | H8      | 31      | 42      | P3       | 52      | PA6                                                  | I/O      | FT              | (4)   | SPI1_MISO /<br>TIM8_BKIN/TIM13_CH1 /<br>DCMI_PIXCLK / TIM3_CH1<br>/ TIM1_BKIN/ EVENTOUT                         | ADC12_IN6               |

| 23     | J8      | 32      | 43      | R3       | 53      | PA7                                                  | I/O      | FT              | (4)   | SPI1_MOSI/ TIM8_CH1N /<br>TIM14_CH1/TIM3_CH2/<br>ETH_MII_RX_DV /<br>TIM1_CH1N /<br>ETH_RMII_CRS_DV/<br>EVENTOUT | ADC12_IN7               |

| 24     | -       | 33      | 44      | N5       | 54      | PC4                                                  | I/O      | FT              | (4)   | ETH_RMII_RX_D0 /<br>ETH_MII_RX_D0/<br>EVENTOUT                                                                  | ADC12_IN14              |

| 25     | -       | 34      | 45      | P5       | 55      | PC5                                                  | I/O      | FT              | (4)   | ETH_RMII_RX_D1 /<br>ETH_MII_RX_D1/<br>EVENTOUT                                                                  | ADC12_IN15              |

| 26     | G7      | 35      | 46      | R5       | 56      | PB0                                                  | I/O      | FT              | (4)   | TIM3_CH3 / TIM8_CH2N/<br>OTG_HS_ULPI_D1/<br>ETH_MII_RXD2 /<br>TIM1_CH2N/ EVENTOUT                               | ADC12_IN8               |

| 27     | H7      | 36      | 47      | R4       | 57      | PB1                                                  | I/O      | FT              | (4)   | TIM3_CH4 / TIM8_CH3N/<br>OTG_HS_ULPI_D2/<br>ETH_MII_RXD3 /<br>TIM1_CH3N/ EVENTOUT                               | ADC12_IN9               |

| 28     | J7      | 37      | 48      | M6       | 58      | PB2/BOOT1<br>(PB2)                                   | I/O      | FT              | -     | EVENTOUT                                                                                                        | -                       |

63/202

DocID022152 Rev 8

|        | Table 9. Alternate function mapping (continued) |                       |           |          |                  |               |                                |                      |                        |                    |                           |                    |                                      |                      |                |      |          |

|--------|-------------------------------------------------|-----------------------|-----------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|--------------------|--------------------------------------|----------------------|----------------|------|----------|

|        |                                                 | AF0                   | AF1       | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10               | AF11                                 | AF12                 | AF13           |      |          |

| Po     | ort                                             | SYS                   | TIM1/2    | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS  | ETH                                  | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PB0                                             | -                     | TIM1_CH2N | TIM3_CH3 | TIM8_CH2N        | -             | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>D1 | ETH _MII_RXD2                        | -                    | -              | -    | EVENTOUT |

|        | PB1                                             | -                     | TIM1_CH3N | TIM3_CH4 | TIM8_CH3N        |               | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>D2 | ETH _MII_RXD3                        | -                    | -              | -    | EVENTOUT |

|        | PB2                                             | -                     | -         | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB3                                             | JTDO/<br>TRACES<br>WO | TIM2_CH2  | -        | -                | -             | SPI1_SCK                       | SPI3_SCK<br>I2S3_CK  | -                      | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB4                                             | NJTRST                | -         | TIM3_CH1 |                  | -             | SPI1_MISO                      | SPI3_MISO            | I2S3ext_SD             | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB5                                             | -                     | -         | TIM3_CH2 |                  | I2C1_SMB<br>A | SPI1_MOSI                      | SPI3_MOSI<br>I2S3_SD |                        | -                  | CAN2_RX                   | OTG_HS_ULPI_<br>D7 | ETH_PPS_OUT                          | -                    | DCMI_D10       | -    | EVENTOUT |

|        | PB6                                             | -                     | -         | TIM4_CH1 |                  | I2C1_SCL      | -                              | -                    | USART1_TX              | -                  | CAN2_TX                   | -                  | -                                    | -                    | DCMI_D5        | -    | EVENTOUT |

|        | PB7                                             | -                     | -         | TIM4_CH2 |                  | I2C1_SDA      | -                              | -                    | USART1_RX              | -                  | -                         | -                  | -                                    | FSMC_NL              | DCMI_VSYN<br>C | -    | EVENTOUT |

| Port B | PB8                                             | -                     | -         | TIM4_CH3 | TIM10_CH1        | I2C1_SCL      | -                              | -                    | -                      | -                  | CAN1_RX                   | -                  | ETH _MII_TXD3                        | SDIO_D4              | DCMI_D6        | -    | EVENTOUT |

|        | PB9                                             | -                     | -         | TIM4_CH4 | TIM11_CH1        | I2C1_SDA      | SPI2_NSS<br>I2S2_WS            | -                    | -                      | -                  | CAN1_TX                   | -                  | -                                    | SDIO_D5              | DCMI_D7        | -    | EVENTOUT |

|        | PB10                                            | -                     | TIM2_CH3  | -        | -                | I2C2_SCL      | SPI2_SCK<br>I2S2_CK            | -                    | USART3_TX              | -                  | -                         | OTG_HS_ULPI_<br>D3 | ETH_MII_RX_ER                        | -                    | -              | -    | EVENTOUT |

|        | PB11                                            | -                     | TIM2_CH4  | -        | -                | I2C2_SDA      | -                              | -                    | USART3_RX              | -                  | -                         | OTG_HS_ULPI_<br>D4 | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | -                    | -              | -    | EVENTOUT |

|        | PB12                                            | -                     | TIM1_BKIN | -        | -                | I2C2_<br>SMBA | SPI2_NSS<br>I2S2_WS            | -                    | USART3_CK              | -                  | CAN2_RX                   | OTG_HS_ULPI_<br>D5 | ETH _MII_TXD0<br>ETH _RMII_TXD0      | OTG_HS_ID            | -              | -    | EVENTOUT |

|        | PB13                                            | -                     | TIM1_CH1N | -        | -                | -             | SPI2_SCK<br>I2S2_CK            | -                    | USART3_CTS             | -                  | CAN2_TX                   | OTG_HS_ULPI_<br>D6 | ETH _MII_TXD1<br>ETH _RMII_TXD1      | -                    | -              | -    | EVENTOUT |

|        | PB14                                            | -                     | TIM1_CH2N | -        | TIM8_CH2N        | -             | SPI2_MISO                      | I2S2ext_SD           | USART3_RTS             | -                  | TIM12_CH1                 | -                  | -                                    | OTG_HS_DM            | -              | -    | EVENTOUT |

|        | PB15                                            | RTC_<br>REFIN         | TIM1_CH3N | -        | TIM8_CH3N        | -             | SPI2_MOSI<br>I2S2_SD           | -                    | -                      | -                  | TIM12_CH2                 | -                  | -                                    | OTG_HS_DP            | -              | -    | EVENTOUT |

Pinouts and pin description

577

67/202

DocID022152 Rev 8

|         |      |     |        |          |                  | Tab           | ole 9. Alt                     | ernate fi            | unction m              | apping             | (contin                   | ued)              |      |                      |          |      |          |

|---------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|----------------------|----------|------|----------|

|         |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                 | AF13     |      |          |

| P       | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ETH  | FSMC/SDIO<br>/OTG_FS | DCMI     | AF14 | AF15     |

|         | PF0  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A0              | -        | -    | EVENTOUT |

|         | PF1  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A1              | -        | -    | EVENTOUT |

|         | PF2  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A2              | -        | -    | EVENTOUT |

|         | PF3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A3              | -        | -    | EVENTOUT |

|         | PF4  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A4              | -        | -    | EVENTOUT |

|         | PF5  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A5              | -        | -    | EVENTOUT |

|         | PF6  | -   | -      | -        | TIM10_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NIORD           | -        | -    | EVENTOUT |

| Port F  | PF7  | -   | -      | -        | TIM11_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NREG            | -        | -    | EVENTOUT |

| T OIL I | PF8  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM13_CH1                 | -                 | -    | FSMC_<br>NIOWR       | -        | -    | EVENTOUT |

|         | PF9  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM14_CH1                 | -                 | -    | FSMC_CD              | -        | -    | EVENTOUT |

|         | PF10 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_INTR            | -        | -    | EVENTOUT |

|         | PF11 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    |                      | DCMI_D12 | -    | EVENTOUT |

|         | PF12 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A6              | -        | -    | EVENTOUT |

|         | PF13 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A7              | -        | -    | EVENTOUT |

|         | PF14 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A8              | -        | -    | EVENTOUT |

|         | PF15 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A9              | -        | -    | EVENTOUT |

Pinouts and pin description

5

| Bus  | Boundary address          | Peripheral         |

|------|---------------------------|--------------------|

|      | 0x4001 4C00 - 0x4001 57FF | Reserved           |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11              |

|      | 0x4001 4400 - 0x4001 47FF | TIM10              |

|      | 0x4001 4000 - 0x4001 43FF | ТІМ9               |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI               |

|      | 0x4001 3800 - 0x4001 3BFF | SYSCFG             |

|      | 0x4001 3400 - 0x4001 37FF | Reserved           |

|      | 0x4001 3000 - 0x4001 33FF | SPI1               |

| APB2 | 0x4001 2C00 - 0x4001 2FFF | SDIO               |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved           |

|      | 0x4001 2000 - 0x4001 23FF | ADC1 - ADC2 - ADC3 |

|      | 0x4001 1800 - 0x4001 1FFF | Reserved           |

|      | 0x4001 1400 - 0x4001 17FF | USART6             |

|      | 0x4001 1000 - 0x4001 13FF | USART1             |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved           |

|      | 0x4001 0400 - 0x4001 07FF | ТІМ8               |

|      | 0x4001 0000 - 0x4001 03FF | TIM1               |

|      | 0x4000 7800- 0x4000 FFFF  | Reserved           |

Table 10. register boundary addresses (continued)

|                 |                   |                                                                            |                       | Тур                       | Ма                        | x <sup>(2)</sup>           |      |

|-----------------|-------------------|----------------------------------------------------------------------------|-----------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter         | Conditions                                                                 | fhclk                 | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                   |                                                                            | 168 MHz               | 87                        | 102                       | 109                        |      |

|                 |                   |                                                                            | 144 MHz               | 67                        | 80                        | 86                         |      |

|                 |                   |                                                                            | 120 MHz               | 56                        | 69                        | 75                         |      |

|                 |                   |                                                                            | 90 MHz                | 44                        | 56                        | 62                         |      |

|                 |                   | - (2)                                                                      | 60 MHz                | 30                        | 42                        | 49                         |      |

|                 |                   | External clock <sup>(3)</sup> , all peripherals enabled <sup>(4)(5)</sup>  | 30 MHz                | 16                        | 28                        | 35                         |      |

|                 |                   | F F                                                                        | 25 MHz                | 12                        | 24                        | 31                         |      |

|                 |                   |                                                                            | 16 MHz <sup>(6)</sup> | 9                         | 20                        | 28                         |      |

|                 |                   |                                                                            | 8 MHz                 | 5                         | 17                        | 24                         |      |

|                 |                   |                                                                            | 4 MHz                 | 3                         | 15                        | 22                         |      |

|                 | Supply current in |                                                                            | 2 MHz                 | 2                         | 14                        | 21                         | mA   |

| I <sub>DD</sub> | Run mode          |                                                                            | 168 MHz               | 40                        | 54                        | 61                         |      |

|                 |                   |                                                                            | 144 MHz               | 31                        | 43                        | 50                         |      |

|                 |                   |                                                                            | 120 MHz               | 26                        | 38                        | 45                         |      |

|                 |                   |                                                                            | 90 MHz                | 20                        | 32                        | 39                         |      |

|                 |                   | - (2)                                                                      | 60 MHz                | 14                        | 26                        | 33                         |      |

|                 |                   | External clock <sup>(3)</sup> , all peripherals disabled <sup>(4)(5)</sup> | 30 MHz                | 8                         | 20                        | 27                         |      |

|                 |                   |                                                                            | 25 MHz                | 6                         | 18                        | 25                         |      |

|                 |                   |                                                                            | 16 MHz <sup>(6)</sup> | 5                         | 16                        | 24                         |      |

|                 |                   |                                                                            | 8 MHz                 | 3                         | 15                        | 22                         |      |

|                 |                   |                                                                            | 4 MHz                 | 2                         | 14                        | 21                         |      |

|                 |                   |                                                                            | 2 MHz                 | 2                         | 14                        | 21                         |      |

### Table 20. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM <sup>(1)</sup>

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization, tested in production at V<sub>DD</sub> max and f<sub>HCLK</sub> max with peripherals enabled.

3. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

6. In this case HCLK = system clock/2.

### Additional current consumption

The MCU is placed under the following conditions:

- All I/O pins are configured in analog mode.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency.

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 2 for f<sub>HCLK</sub> ≤ 144 MHz

- Scale 1 for 144 MHz <  $f_{HCLK} \le 168$  MHz.

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- The HSE crystal clock frequency is 25 MHz.

- T<sub>A</sub>= 25 °C.

# Table 26. Typical current consumption in Run mode, code with data processing running from Flash memory, regulator ON (ART accelerator enabled except prefetch), $V_{DD} = 1.8 V^{(1)}$

| Symbol | Parameter                     | Conditions                 | f <sub>HCLK</sub> (MHz) | Typ. at T <sub>A</sub> =<br>25 °C | Unit |

|--------|-------------------------------|----------------------------|-------------------------|-----------------------------------|------|

|        |                               |                            | 160                     | 36.2                              |      |

|        |                               |                            | 144                     | 29.3                              |      |

|        |                               |                            | 120                     | 24.7                              |      |

| IDD    | Supply current in<br>Run mode | All peripheral<br>disabled | 90                      | 19.3                              | mA   |

|        |                               |                            | 60                      | 13.4                              |      |

|        |                               |                            | 30                      | 7.7                               |      |

|        |                               |                            | 25                      | 6.0                               |      |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC or DAC) is not included.

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 48: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to

DocID022152 Rev 8

| Symbol                               | Parameter                                   | Conditions                              | •                                       | Min          | Тур  | Max          | Unit |

|--------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------------------|--------------|------|--------------|------|

|                                      |                                             |                                         | RMS                                     | -            | 25   | -            |      |

|                                      | Cycle-to-cycle jitter                       | System clock                            | peak<br>to<br>peak                      | -            | ±150 | -            |      |

|                                      |                                             | 120 MHz                                 | RMS                                     | -            | 15   | -            |      |

| Jitter <sup>(3)</sup>                | Period Jitter                               |                                         | peak<br>to<br>peak                      | -            | ±200 | -            | ps   |

|                                      | Main clock output (MCO) for RMII Ethernet   | Cycle to cycle at 50<br>on 1000 samples | -                                       | 32           | -    |              |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet | Cycle to cycle at 2<br>on 1000 samples  | -                                       | 40           | -    |              |      |

|                                      | Bit Time CAN jitter                         | Cycle to cycle at 1 on 1000 samples     | Cycle to cycle at 1 MHz on 1000 samples |              | 330  | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                | VCO freq = 100 MI                       | 0.15                                    | _            | 0.40 | mA           |      |

| 'DD(PLL)                             |                                             | VCO freq = 432 M                        | 0.45                                    |              | 0.75 |              |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA               | VCO freq = 100 M<br>VCO freq = 432 M    |                                         | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

Table 36. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization.

| Symbol                  | Parameter                              | Conditions                                                              |                    | Min                 | Тур  | Max  | Unit |

|-------------------------|----------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup>      | -                                                                       |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock         | -                                                                       | -                  | -                   | 216  | MHz  |      |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                      | -                                                                       | 100                | -                   | 432  | MHz  |      |

| +                       | DLL 126 look time                      | VCO freq = 100 MHz                                                      | 2                  | 75                  | -    | 200  |      |

| t <sub>LOCK</sub>       | PLLI2S lock time<br>VCO freq = 432 MHz |                                                                         | 2                  | 100                 | -    | 300  | μs   |

|                         |                                        | Cycle to cycle at                                                       | RMS                | -                   | 90   | -    |      |

|                         | Master I <sup>2</sup> S clock jitter   | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                            | peak<br>to<br>peak | -                   | ±280 | -    | ps   |

| Jitter <sup>(3)</sup>   |                                        | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | -                  | 90                  | -    | ps   |      |

|                         | WS I <sup>2</sup> S clock jitter       | Cycle to cycle at 48<br>on 1000 samples                                 | KHz                | -                   | 400  | -    | ps   |

### Table 37. PLLI2S (audio PLL) characteristics

Figure 68. NAND controller waveforms for read access

Figure 69. NAND controller waveforms for write access

### 6.3 LQPF100 package information

Figure 81. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

Table 93. LQPF100 – 100-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup>

| Symbol |        | millimeters |        | inches |        |        |  |  |  |

|--------|--------|-------------|--------|--------|--------|--------|--|--|--|

| Symbol | Min    | Тур         | Мах    | Min    | Тур    | Мах    |  |  |  |

| A      | -      | -           | 1.600  | -      | -      | 0.0630 |  |  |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -      | 0.0059 |  |  |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551 | 0.0571 |  |  |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087 | 0.0106 |  |  |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -      | 0.0079 |  |  |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |  |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |  |  |

| D3     | -      | 12.000      | -      | -      | 0.4724 | -      |  |  |  |

| E      | 15.80  | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |  |  |

|        |             |        |        | entinaea) |        |        |

|--------|-------------|--------|--------|-----------|--------|--------|

| Symbol | millimeters |        |        | inches    |        |        |

|        | Min         | Тур    | Мах    | Min       | Тур    | Max    |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433    | 0.5512 | 0.5591 |

| E3     | -           | 12.000 | -      | -         | 0.4724 | -      |

| е      | -           | 0.500  | -      | -         | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177    | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -         | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°        | 3.5°   | 7°     |

| CCC    | -           | -      | 0.080  | -         | -      | 0.0031 |

# Table 93. LQPF100 – 100-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup> (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking and ball A 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 89. UFBGA176+25 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| mechanical data (continued) |             |       |        |                       |        |        |

|-----------------------------|-------------|-------|--------|-----------------------|--------|--------|

| Symbol                      | millimeters |       |        | inches <sup>(1)</sup> |        |        |

| Symbol                      | Min         | Тур   | Мах    | Min                   | Тур    | Max    |

| ZD                          | -           | 1.250 | -      | -                     | 0.0492 | -      |

| Е                           | 23.900      | -     | 24.100 | 0.9409                | -      | 0.9488 |

| HE                          | 25.900      | -     | 26.100 | 1.0197                | -      | 1.0276 |

| ZE                          | -           | 1.250 | -      | -                     | 0.0492 | -      |

| е                           | -           | 0.500 | -      | -                     | 0.0197 | -      |

| L <sup>(2)</sup>            | 0.450       | -     | 0.750  | 0.0177                | -      | 0.0295 |

| L1                          | -           | 1.000 | -      | -                     | 0.0394 | -      |

| k                           | 0°          | -     | 7°     | 0°                    | -      | 7°     |

| CCC                         | -           | -     | 0.080  | -                     | -      | 0.0031 |

## Table 97. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. L dimension is measured at gauge plane at 0.25 mm above the seating plane.

### **Device marking for LQFP176**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 92. LQFP176 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

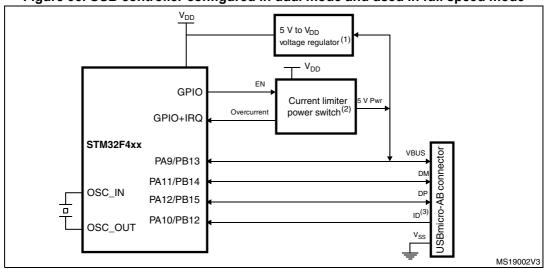

Figure 95. USB controller configured in dual mode and used in full speed mode

- 1. External voltage regulator only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

- 4. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Date<br>04-Jun-2013 | Revision<br>4<br>(continued) | Changes Updated Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline Updated Table 95: UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch ball grid array mechanical data Updated Figure 5: STM32F40xxx block diagram Updated Section 2: Description Updated figure 3: Compatible board design between STM32F10xx/STM32F2/STM32F40xxx for LQFP144 package Updated Figure 3: Compatible board design between STM32F10xx/STM32F2/STM32F40xxx for LQFP144 package Updated Section 2.2.14: Power supply schemes Updated Section 2.2.15: Power supply schemes Updated Table 14: General operating conditions, including footnote <sup>(2)</sup> . Updated footnote <sup>(1)</sup> in Table 57: ADC characteristics. Updated footnote <sup>(1)</sup> in Table 67: ADC characteristics. Updated footnote <sup>(1)</sup> in Table 67: ADC characteristics. Updated footnote <sup>(2)</sup> in Table 68: ADC accuracy at fADC = 30 MHZ. Updated footnote <sup>(2)</sup> in Table 67: ADC characteristics. Updated Figure 9: Regulator OFF. Updated Figure 9: Regulator OFF. Updated Figure 9: Power supply supervisor interconnection with internal reset OFF. Added Section 2.2.17: Regulator ON/OFF and internal reset ON/OFF availability. Updated footnote <sup>(2)</sup> of Figure 21: Power supply scheme. Replaced respectively "12S3_WS" by "12S3_WS", "12S3_CK" by "12S3_CK" and "FSMC_BLN" by "FSMC_NBL1" in Table 9: Alternate function mapping. Added "EVENTOUT" as alternate function "AF15" for pin PC13, PC14, PC15, PH0, PH1, PI8 in Table 9: Alternate function mapping Replaced "DCML_12" by "DCML_D12" in Table 7: STM32F40xxx pin and ball definitions. Removed the following sentence from Section : 12C interface characteristics: "Unless otherwise specified, the parameters given in Table 56 are derived from tests performed under the ambient temperature, f <sub>PCLK1</sub> frequency and V <sub>DD</sub> supply voltage conditions summarized in Table 14.". In Table 7: STM32F40xxx pin and ball definitions on page 47: For pin PC13, replaced "RTC_AF2" by "RTC_TAMP1, RTC_TAMP1, RTC_TS". For pin PB15, added RTC_REFI |

| Table 100. | <b>Document revision</b> | history | (continued) |

|------------|--------------------------|---------|-------------|

|            | Document revision        | matory  | (continueu) |