#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 114                                                                                       |

| Program Memory Size        | 1MB (1M × 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 144-LQFP                                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407zgt6tr                   |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### Internal reset OFF

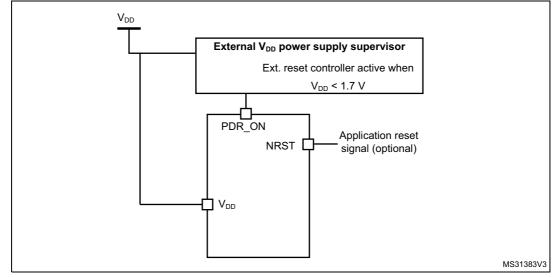

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled with the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 7: Power supply supervisor interconnection with internal reset OFF*.

Figure 7. Power supply supervisor interconnection with internal reset OFF

1. PDR = 1.7 V for reduce temperature range; PDR = 1.8 V for all temperature range.

The V<sub>DD</sub> specified threshold, below which the device must be maintained under reset, is 1.8 V (see *Figure 7*). This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range.

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry is disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>

All packages, except for the LQFP64 and LQFP100, allow to disable the internal reset through the PDR\_ON signal.

Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the  $V_{12}$  domain is controlled by an external power.

## 2.2.20 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is not connected to  $V_{DD}$  (internal reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

## 2.2.21 Timers and watchdogs

The STM32F405xx and STM32F407xx devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 4* compares the features of the advanced-control, general-purpose and basic timers.

| Timer<br>type        | Timer         | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) |

|----------------------|---------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|---------------------------|------------------------------------|--------------------------------|

| Advanceo<br>-control | TIM1,<br>TIM8 | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                       | 84                                 | 168                            |

Table 4. Timer feature comparison

Г

|        | I       | Pin r   | numb    | er       |         |                                                      |          |                 |       |                                 |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|---------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions             | Additional<br>functions |

| -      | -       | -       | 49      | R6       | 59      | PF11                                                 | I/O      | FT              | -     | DCMI_D12/ EVENTOUT              | -                       |

| -      | -       | -       | 50      | P6       | 60      | PF12                                                 | I/O      | FT              | -     | FSMC_A6/ EVENTOUT               | -                       |

| -      | -       | -       | 51      | M8       | 61      | V <sub>SS</sub>                                      | S        | -               | -     | -                               | -                       |

| -      | -       | -       | 52      | N8       | 62      | V <sub>DD</sub>                                      | S        | -               | -     | -                               | -                       |

| -      | -       | -       | 53      | N6       | 63      | PF13                                                 | I/O      | FT              | -     | FSMC_A7/ EVENTOUT               | -                       |

| -      | -       | -       | 54      | R7       | 64      | PF14                                                 | I/O      | FT              | -     | FSMC_A8/ EVENTOUT               | -                       |

| -      | -       | -       | 55      | P7       | 65      | PF15                                                 | I/O      | FT              | I     | FSMC_A9/ EVENTOUT               | -                       |

| -      | -       | -       | 56      | N7       | 66      | PG0                                                  | I/O      | FT              | -     | FSMC_A10/ EVENTOUT              | -                       |

| -      | -       | -       | 57      | M7       | 67      | PG1                                                  | I/O      | FT              | -     | FSMC_A11/ EVENTOUT              | -                       |

| -      | G6      | 38      | 58      | R8       | 68      | PE7                                                  | I/O      | FT              | -     | FSMC_D4/TIM1_ETR/<br>EVENTOUT   | -                       |

| -      | H6      | 39      | 59      | P8       | 69      | PE8                                                  | I/O      | FT              | -     | FSMC_D5/ TIM1_CH1N/<br>EVENTOUT | -                       |

| -      | J6      | 40      | 60      | P9       | 70      | PE9                                                  | I/O      | FT              | -     | FSMC_D6/TIM1_CH1/<br>EVENTOUT   | -                       |

| -      | -       | -       | 61      | M9       | 71      | V <sub>SS</sub>                                      | S        | -               | -     | -                               | -                       |

| -      | -       | -       | 62      | N9       | 72      | V <sub>DD</sub>                                      | S        | -               | -     | -                               | -                       |

| -      | F6      | 41      | 63      | R9       | 73      | PE10                                                 | I/O      | FT              | -     | FSMC_D7/TIM1_CH2N/<br>EVENTOUT  | -                       |

| -      | J5      | 42      | 64      | P10      | 74      | PE11                                                 | I/O      | FT              | -     | FSMC_D8/TIM1_CH2/<br>EVENTOUT   | -                       |

| -      | H5      | 43      | 65      | R10      | 75      | PE12                                                 | I/O      | FT              | -     | FSMC_D9/TIM1_CH3N/<br>EVENTOUT  | -                       |

| -      | G5      | 44      | 66      | N11      | 76      | PE13                                                 | I/O      | FT              | -     | FSMC_D10/TIM1_CH3/<br>EVENTOUT  | -                       |

| -      | F5      | 45      | 67      | P11      | 77      | PE14                                                 | I/O      | FT              | -     | FSMC_D11/TIM1_CH4/<br>EVENTOUT  | -                       |

| -      | G4      | 46      | 68      | R11      | 78      | PE15                                                 | I/O      | FT              | -     | FSMC_D12/TIM1_BKIN/<br>EVENTOUT | -                       |

| Table | 7. STM32F40xxx | pin | and b | call o | definitions | (continued) |

|-------|----------------|-----|-------|--------|-------------|-------------|

|       |                |     |       |        |             |             |

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 9400 - 0x4003 FFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0x4002 5000 - 0x4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| АПВТ | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0x4002 3400 - 0x4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2400 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0x4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

|      | 0x4001 5800- 0x4001 FFFF  | Reserved                 |

Table 10. register boundary addresses (continued)

| Symbol          | Parameter                                                                                                         | Conditions                                                            | Min  | Тур  | Max                       | Unit |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|---------------------------|------|--|

| eymser          |                                                                                                                   |                                                                       |      | .96  | max                       | •    |  |

|                 | Regulator ON:<br>1.2 V internal voltage on                                                                        | VOS bit in PWR_CR register = 0 <sup>(1)</sup><br>Max frequency 144MHz | 1.08 | 1.14 | 1.20                      | V    |  |

| V <sub>12</sub> | $V_{CAP_1}/V_{CAP_2}$ pins                                                                                        | VOS bit in PWR_CR register= 1<br>Max frequency 168MHz                 | 1.20 | 1.26 | 1.32                      | V    |  |

| 12              | Regulator OFF:                                                                                                    | Max frequency 144MHz                                                  | 1.10 | 1.14 | 1.20                      | V    |  |

|                 | 1.2 V external voltage must be supplied from external regulator on $V_{CAP_1}/V_{CAP_2}$ pins                     | Max frequency 168MHz                                                  | 1.20 | 1.26 | 1.30                      | V    |  |

|                 | Input voltage on RST and FT                                                                                       | $2 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$            | -0.3 | -    | 5.5                       |      |  |

|                 | pins <sup>(6)</sup>                                                                                               | $V_{DD} \le 2 V$                                                      | -0.3 | -    | 5.2                       |      |  |

| V <sub>IN</sub> | Input voltage on TTa pins                                                                                         | -                                                                     | -0.3 | -    | V <sub>DDA</sub> +<br>0.3 | V    |  |

|                 | Input voltage on B pin                                                                                            | -                                                                     | -    | -    | 5.5                       |      |  |

|                 |                                                                                                                   | LQFP64                                                                | -    | -    | 435                       |      |  |

|                 |                                                                                                                   | LQFP100                                                               | -    | -    | 465                       |      |  |

| P               | Power dissipation at $T_A = 85 \degree C$<br>for suffix 6 or $T_A = 105 \degree C$ for<br>suffix 7 <sup>(7)</sup> | LQFP144                                                               | -    | -    | 500                       | mW   |  |

| $P_D$           |                                                                                                                   | LQFP176                                                               | -    | -    | 526                       |      |  |

|                 |                                                                                                                   | UFBGA176                                                              | -    | -    | 513                       |      |  |

|                 |                                                                                                                   | WLCSP90                                                               | -    | -    | 543                       |      |  |

|                 | Ambient temperature for 6 suffix                                                                                  | Maximum power dissipation                                             | -40  | -    | 85                        | °C   |  |

| т.              | version                                                                                                           | Low-power dissipation <sup>(8)</sup>                                  | -40  | -    | 105                       |      |  |

| ΤΑ              | Ambient temperature for 7 suffix                                                                                  | Maximum power dissipation                                             | -40  | -    | 105                       | °C   |  |

|                 | version                                                                                                           | Low-power dissipation <sup>(8)</sup>                                  | -40  | -    | 125                       | °C   |  |

| ТJ              |                                                                                                                   | 6 suffix version                                                      | -40  | -    | 105                       | °C   |  |

| IJ              | Junction temperature range                                                                                        | 7 suffix version                                                      | -40  | -    | 125                       | - "  |  |

| Table 14. Genera | l operating | conditions | (continued) |

|------------------|-------------|------------|-------------|

|------------------|-------------|------------|-------------|

1. The average expected gain in power consumption when VOS = 0 compared to VOS = 1 is around 10% for the whole temperature range, when the system clock frequency is between 30 and 144 MHz.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

3. When the ADC is used, refer to *Table 67: ADC characteristics*.

4. If V<sub>REF+</sub> pin is present, it must respect the following condition: V<sub>DDA</sub>-V<sub>REF+</sub> < 1.2 V.

5. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

6. To sustain a voltage higher than  $V_{DD}$ +0.3, the internal pull-up and pull-down resistors must be disabled.

7. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$

8. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

|                         | -                    | I <sub>DD</sub> (1       | Гур) <sup>(1)</sup>       |        |  |

|-------------------------|----------------------|--------------------------|---------------------------|--------|--|

| Peripheral              |                      | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz) | Unit   |  |

|                         | OTG_FS               | 26.45                    | 26.67                     |        |  |

| AHB2<br>(up to 168 MHz) | DCMI                 | 5.87                     | 5.35                      | μA/MHz |  |

|                         | RNG                  | 1.50                     | 1.67                      |        |  |

| AHB3<br>(up to 168 MHz) | FSMC                 | 12.46                    | 11.31                     | µA/MHz |  |

| Bus m                   | atrix <sup>(2)</sup> | 13.10                    | 11.81                     | µA/MHz |  |

|                         | TIM2                 | 16.71                    | 16.50                     |        |  |

|                         | TIM3                 | 12.33                    | 11.94                     |        |  |

|                         | TIM4                 | 13.45                    | 12.92                     |        |  |

|                         | TIM5                 | 17.14                    | 16.58                     |        |  |

|                         | TIM6                 | 2.43                     | 3.06                      |        |  |

|                         | TIM7                 | 2.43                     | 2.22                      | 1      |  |

|                         | TIM12                | 6.62                     | 6.83                      | -      |  |

|                         | TIM13                | 5.05                     | 5.47                      |        |  |

|                         | TIM14                | 5.26                     | 5.61                      |        |  |

|                         | PWR                  | 1.00                     | 0.56                      |        |  |

|                         | USART2               | 2.69                     | 2.78                      |        |  |

|                         | USART3               | 2.74                     | 2.78                      |        |  |

| APB1<br>(up to 42 MHz)  | UART4                | 3.24                     | 3.33                      | µA/MH: |  |

|                         | UART5                | 2.69                     | 2.78                      |        |  |

|                         | I2C1                 | 2.67                     | 2.50                      |        |  |

|                         | I2C2                 | 2.83                     | 2.78                      |        |  |

|                         | I2C3                 | 2.81                     | 2.78                      |        |  |

|                         | SPI2                 | 2.43                     | 2.22                      |        |  |

|                         | SPI3                 | 2.43                     | 2.22                      |        |  |

|                         | I2S2 <sup>(3)</sup>  | 2.43                     | 2.22                      |        |  |

|                         | I2S3 <sup>(3)</sup>  | 2.26                     | 2.22                      |        |  |

|                         | CAN1                 | 5.12                     | 5.56                      |        |  |

|                         | CAN2                 | 4.81                     | 5.28                      |        |  |

|                         | DAC <sup>(4)</sup>   | 1.67                     | 1.67                      |        |  |

|                         | WWDG                 | 1.00                     | 0.83                      | 1      |  |

Table 28. Peripheral current consumption (continued)

| Symbol                                 | Parameter                                                                                    | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |

|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-----------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                       | -                  | 5                  | -                  | CPU<br>clock<br>cycle |

|                                        | Wakeup from Stop mode (regulator in Run mode and Flash memory in Stop mode)                  | -                  | 13                 | -                  |                       |

| twustop <sup>(2)</sup>                 | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Stop mode)            | -                  | 17                 | 40                 | 110                   |

| 'WUSTOP` '                             | Wakeup from Stop mode (regulator in Run mode and Flash memory in Deep power-down mode)       | -                  | 105                | -                  | μs                    |

|                                        | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power-down mode) | -                  | 110                | -                  |                       |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs                    |

| Table 29. | Low-power | mode | wakeup | timings |

|-----------|-----------|------|--------|---------|

|-----------|-----------|------|--------|---------|

1. Guaranteed by characterization.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and -45 °C, respectively.

## 5.3.8 External clock source characteristics

## High-speed external user clock generated from an external source

The characteristics given in *Table 30* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                           | Conditions                       | Min         | Тур | Max         | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|-------------|-----|-------------|------|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                  | 1           | -   | 50          | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | $0.7V_{DD}$ | -   | $V_{DD}$    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  | -                                | $V_{SS}$    | -   | $0.3V_{DD}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5           | -   | -           | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -           | -   | 10          | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -           | 5   | -           | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          | -                                | 45          | -   | 55          | %    |

| ١L                                         | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -           | -   | ±1          | μA   |

| Table 30. High-speed externa | l user clock characteristics |

|------------------------------|------------------------------|

|------------------------------|------------------------------|

1. Guaranteed by design.

| Symbol                          | Parameter Conditions                             |                              | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |

| Table 41 | . Flash n | nemory | programming | with | V <sub>PP</sub> |

|----------|-----------|--------|-------------|------|-----------------|

|----------|-----------|--------|-------------|------|-----------------|

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

#### Table 42. Flash memory endurance and data retention

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

## 5.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

| Symbol                 | Parameter                                                         | Conditions                                                      | Min    | Max                     | Unit                 |

|------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------|--------|-------------------------|----------------------|

| Symbol                 | Farameter                                                         | Conditions                                                      | IVIIII | IVIAX                   | Unit                 |

| t <sub>res(TIM)</sub>  |                                                                   | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | Timer resolution time                                             | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>168 MHz | 5.95   | -                       | ns                   |

|                        |                                                                   | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                                   | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 84 MHz                 | 11.9   | -                       | ns                   |

| r                      | Timer external clock                                              |                                                                 | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to<br>CH4                                        |                                                                 | 0      | 84                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                  | f <sub>TIMxCLK</sub> =<br>168 MHz                               | -      | 16                      | bit                  |

| t <sub>COUNTER</sub>   | 16-bit counter clock<br>period when internal<br>clock is selected | APB2 = 84 MHz                                                   | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                            |                                                                 | -      | 32768                   | t <sub>TIMxCLK</sub> |

Table 53. Characteristics of TIMx connected to the APB2 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM1, TIM8, TIM9, TIM10, and TIM11 timers.

## 5.3.19 Communications interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 5.3.16: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

Table 54. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

| Symbol                                                                          | Parameter                                                            | Conditions                                                                            | Min   | Тур   | Max              | Unit               |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|------------------|--------------------|

| t <sub>lat</sub> (4)                                                            | Injection trigger conversion                                         | f <sub>ADC</sub> = 30 MHz                                                             | -     | -     | 0.100            | μs                 |

| <sup>u</sup> at` ′                                                              | latency                                                              |                                                                                       | -     | -     | 3 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (4)                                                           | Regular trigger conversion                                           | f <sub>ADC</sub> = 30 MHz                                                             | -     | -     | 0.067            | μs                 |

| Hatr                                                                            | latency                                                              |                                                                                       | -     | -     | 2 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| ts <sup>(4)</sup>                                                               | Sampling time                                                        | f <sub>ADC</sub> = 30 MHz                                                             | 0.100 | -     | 16               | μs                 |

| U                                                                               |                                                                      | -                                                                                     | 3     | -     | 480              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(4)</sup>                                                | Power-up time                                                        | -                                                                                     | -     | 2     | 3                | μs                 |

|                                                                                 | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution                       | 0.50                                                                                  | -     | 16.40 | μs               |                    |

|                                                                                 | Total conversion time (including sampling time)                      | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution                                        | 0.43  | -     | 16.34            | μs                 |

|                                                                                 |                                                                      | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution                                         | 0.37  | -     | 16.27            | μs                 |

|                                                                                 |                                                                      | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution                                         | 0.30  | -     | 16.20            | μs                 |

|                                                                                 |                                                                      | 9 to 492 (t <sub>S</sub> for sampling +n-bit resolution for successive approximation) |       |       |                  | 1/f <sub>ADC</sub> |

|                                                                                 |                                                                      | 12-bit resolution<br>Single ADC                                                       | -     | -     | 2                | Msps               |

| $f_S^{(4)}$ Sampling rate<br>( $f_{ADC}$ = 30 MHz, and<br>$t_S$ = 3 ADC cycles) | $(f_{ADC} = 30 \text{ MHz}, \text{ and})$                            | 12-bit resolution<br>Interleave Dual ADC<br>mode                                      | -     | -     | 3.75             | Msps               |

|                                                                                 |                                                                      | 12-bit resolution<br>Interleave Triple ADC<br>mode                                    | -     | -     | 6                | Msps               |

| I <sub>VREF+</sub> (4)                                                          | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode | -                                                                                     | -     | 300   | 500              | μA                 |

| I <sub>VDDA</sub> <sup>(4)</sup>                                                | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode | -                                                                                     | -     | 1.6   | 1.8              | mA                 |

Table 67. ADC characteristics (continued)

1. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to *Section : Internal reset OFF*).

2. It is recommended to maintain the voltage difference between V\_{REF+} and V\_{DDA} below 1.8 V.

3. V<sub>DDA</sub> -V<sub>REF+</sub> < 1.2 V.

4. Guaranteed by characterization.

5.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

- 6.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.8 V, and minimum value for V<sub>DD</sub>=3.3 V.

- 7. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table* 67.

| Symbol                             | Parameter                                                                                                                                                          | Min | Тур | Мах  | Unit | Comments                                                                                                                                                                            |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                    | Offset error                                                                                                                                                       | -   | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                                                                                           |  |  |  |

| Offset <sup>(4)</sup>              | (difference between<br>measured value at Code<br>(0x800) and the ideal value                                                                                       | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at $V_{REF+}$ = 3.6 V                                                                                                                                   |  |  |  |

|                                    | = V <sub>REF+</sub> /2)                                                                                                                                            | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                                                                                                   |  |  |  |

| Gain<br>error <sup>(4)</sup>       | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                                                                                           |  |  |  |

| tsettling <sup>(4)</sup>           | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±4LSB | -   | 3   | 6    | μs   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                                   |  |  |  |

| THD <sup>(4)</sup>                 | Total Harmonic Distortion<br>Buffer ON                                                                                                                             | -   | -   | -    | dB   | $\begin{array}{l} C_{LOAD} \leq 50 \text{ pF}, \\ R_{LOAD} \geq 5  k\Omega \end{array}$                                                                                             |  |  |  |

| Update<br>rate <sup>(2)</sup>      | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                                   |  |  |  |

| t <sub>WAKEUP</sub> <sup>(4)</sup> | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $\label{eq:LOAD} \begin{split} C_{LOAD} &\leq 50 \text{ pF, } R_{LOAD} \geq 5 \text{ k}\Omega \\ \text{input code between lowest and} \\ \text{highest possible ones.} \end{split}$ |  |  |  |

| PSRR+ <sup>(2)</sup>               | Power supply rejection ratio (to $V_{DDA}$ ) (static DC measurement)                                                                                               | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                                                                                    |  |  |  |

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization.

2. Guaranteed by characterization.

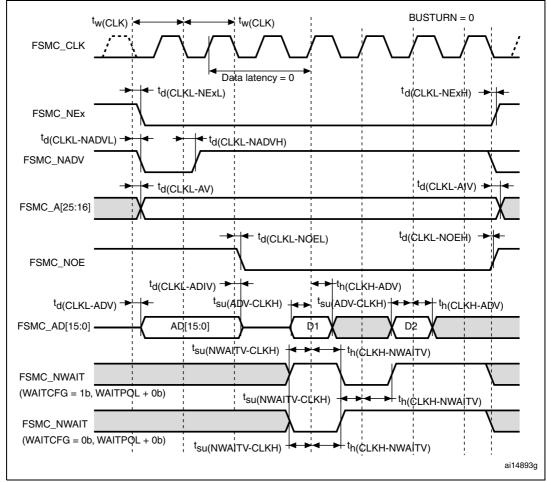

### Synchronous waveforms and timings

*Figure 58* through *Figure 61* represent synchronous waveforms and *Table 80* through *Table 82* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F40xxx/41xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period (with maximum FSMC\_CLK = 60 MHz).

|                   | package mechanical data |             |       |        |                       |        |  |  |  |

|-------------------|-------------------------|-------------|-------|--------|-----------------------|--------|--|--|--|

| Symbol            |                         | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |  |

| Symbol            | Min                     | Тур         | Мах   | Min    | Тур                   | Max    |  |  |  |

| А                 | 0.540                   | 0.570       | 0.600 | 0.0213 | 0.0224                | 0.0236 |  |  |  |

| A1                | -                       | 0.190       | -     | -      | 0.0075                | -      |  |  |  |

| A2                | -                       | 0.380       | -     | -      | 0.0150                | -      |  |  |  |

| A3 <sup>(2)</sup> | -                       | 0.025       | -     | -      | 0.0010                | -      |  |  |  |

| b <sup>(3)</sup>  | 0.240                   | 0.270       | 0.300 | 0.0094 | 0.0106                | 0.0118 |  |  |  |

| D                 | 4.188                   | 4.223       | 4.258 | 0.1649 | 0.1663                | 0.1676 |  |  |  |

| E                 | 3.934                   | 3.969       | 4.004 | 0.1549 | 0.1563                | 0.1576 |  |  |  |

| е                 | -                       | 0.400       | -     | -      | 0.0157                | -      |  |  |  |

| e1                | -                       | 3.600       | -     | -      | 0.1417                | -      |  |  |  |

| e2                | -                       | 3.200       | -     | -      | 0.1260                | -      |  |  |  |

| F                 | -                       | 0.3115      | -     | -      | 0.0123                | -      |  |  |  |

| G                 | -                       | 0.3845      | -     | -      | 0.0151                | -      |  |  |  |

| aaa               | -                       | 0.100       | -     | -      | 0.0039                | -      |  |  |  |

| bbb               | -                       | 0.100       | -     | -      | 0.0039                | -      |  |  |  |

| ссс               | -                       | 0.100       | -     | -      | 0.0039                | -      |  |  |  |

| ddd               | -                       | 0.050       | -     | -      | 0.0020                | -      |  |  |  |

| eee               | -                       | 0.050       | -     | -      | 0.0020                | -      |  |  |  |

# Table 90. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

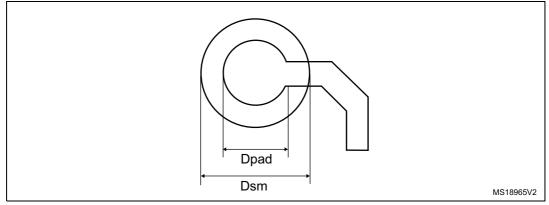

# Figure 76. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale recommended footprint

| Dimension      | Recommended values                            |  |  |  |  |  |

|----------------|-----------------------------------------------|--|--|--|--|--|

| Pitch          | 0.4 mm                                        |  |  |  |  |  |

| Dpad           | 260 μm max. (circular)<br>220 μm recommended  |  |  |  |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |  |  |  |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed |  |  |  |  |  |

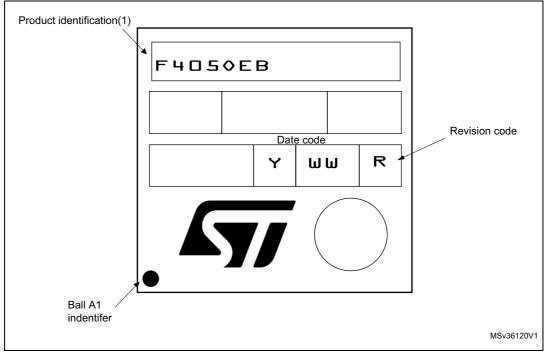

## **Device marking for WLCSP90**

The following figure gives an example of topside marking and ball A1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 77. WLCSP90 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

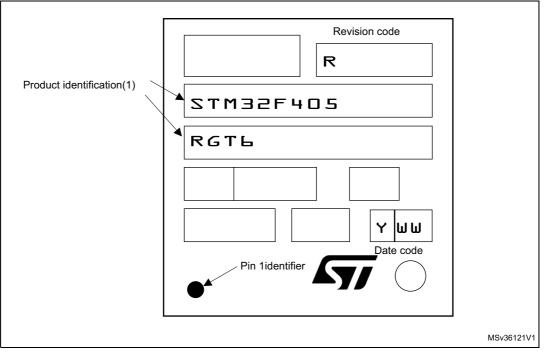

#### **Device marking for LQFP64**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 80. LPQF64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

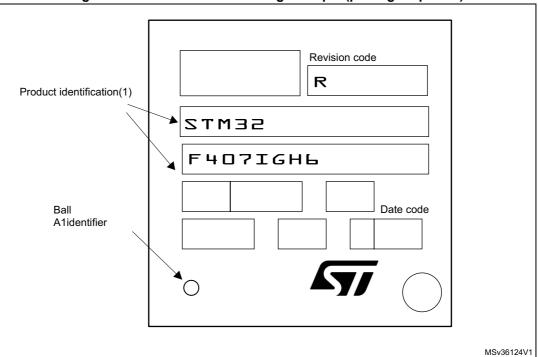

#### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking and ball A 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 89. UFBGA176+25 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

## 6.7 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                         | Value | Unit |  |

|---------------|-----------------------------------------------------------------------------------|-------|------|--|

|               | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch         | 46    |      |  |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch        | 43    |      |  |

| 0             | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch        | 40    | °C/W |  |

| $\Theta_{JA}$ | <b>Thermal resistance junction-ambient</b><br>LQFP176 - 24 × 24 mm / 0.5 mm pitch | 38    | 0/11 |  |

|               | Thermal resistance junction-ambient<br>UFBGA176 - 10× 10 mm / 0.65 mm pitch       | 39    |      |  |

|               | Thermal resistance junction-ambient<br>WLCSP90 - 0.400 mm pitch                   | 38.1  |      |  |

| Table 98. | Package | thermal | characteristics |

|-----------|---------|---------|-----------------|

|-----------|---------|---------|-----------------|

### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

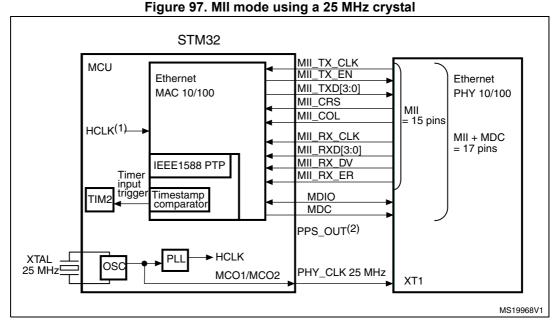

## A.3 Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

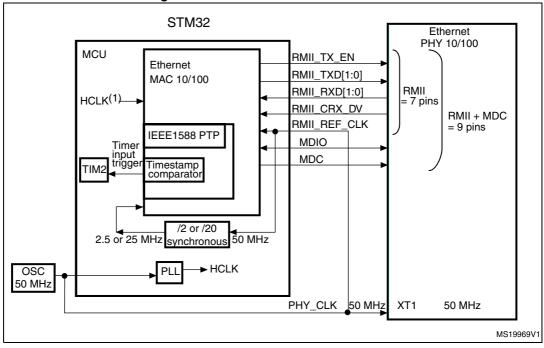

#### Figure 98. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>24-Jan-2012 | Revision<br>2<br>(continued) | Changes         Added V <sub>12</sub> in Table 19: Embedded reset and power control block characteristics.         Updated Table 21: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled) and Table 20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM. Added Figure , Figure 25, Figure 26, and Figure 27.         Updated Table 22: Typical and maximum current consumption in Sleep mode and removed Note 1.         Updated Table 23: Typical and maximum current consumptions in Stop mode and Table 24: Typical and maximum current consumptions in Stop mode and Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, and Table 27: Switching output I/O current consumption.         Section : On-chip peripheral current consumption: modified conditions, and updated Table 28: Peripheral current consumption and Note 2.         Changed f <sub>HSE_ext</sub> to 50 MHz and t <sub>r(HSE)</sub> /t <sub>f(HSE)</sub> maximum value in Table 30: High-speed external user clock characteristics.         Added C <sub>in(LSE)</sub> in Table 31: Low-speed external user clock characteristics.         Updated maximum PLL input clock frequency, removed related note, and deleted jitter for MCO for RMII Ethernet typical value in Table 36: Main PLL characteristics. Updated maximum PLLI2S input clock frequency and removed related note in Table 37: PLLI2S (audio PLL) characteristics.         Updated Section : Flash memory to specify that the devices are shipped to customers with the Flash memory erased. Updated Table 39: Fl |

Table 100. Document revision history (continued)

|             |                                       | 100. Document revision history (continued)                                           |

|-------------|---------------------------------------|--------------------------------------------------------------------------------------|

| Date        | Revision                              | Changes                                                                              |

|             |                                       | Updated Figure 6: Multi-AHB matrix.                                                  |

|             |                                       | Updated Figure 7: Power supply supervisor interconnection with<br>internal reset OFF |

|             |                                       | Changed 1.2 V to V <sub>12</sub> in <i>Section : Regulator OFF</i>                   |

|             |                                       | Updated LQFP176 pin 48.                                                              |

|             |                                       | Updated Section 1: Introduction.                                                     |

|             |                                       | Updated Section 2: Description.                                                      |

|             |                                       | Updated operating voltage in <i>Table 2: STM32F405xx and</i>                         |

|             |                                       | STM32F407xx: features and peripheral counts.                                         |

|             |                                       | Updated Note 1.                                                                      |

|             |                                       | Updated Section 2.2.15: Power supply supervisor.                                     |

|             |                                       | Updated Section 2.2.16: Voltage regulator.                                           |

|             |                                       | Updated Figure 9: Regulator OFF.                                                     |

|             |                                       | Updated Table 3: Regulator ON/OFF and internal reset ON/OFF availability.            |

|             |                                       | Updated Section 2.2.19: Low-power modes.                                             |

|             |                                       | Updated Section 2.2.20: VBAT operation.                                              |

|             |                                       | Updated Section 2.2.22: Inter-integrated circuit interface (I <sup>2</sup> C).       |

|             |                                       | Updated pin 48 in Figure 15: STM32F40xxx LQFP176 pinout.                             |

|             |                                       | Updated Table 6: Legend/abbreviations used in the pinout table.                      |

|             |                                       | Updated Table 7: STM32F40xxx pin and ball definitions.                               |

|             |                                       | Updated Table 14: General operating conditions.                                      |

|             | 4                                     | Updated Table 15: Limitations depending on the operating power                       |

| 04-Jun-2013 | (continued)                           | supply range.                                                                        |

|             | , , , , , , , , , , , , , , , , , , , | Updated Section 5.3.7: Wakeup time from low-power mode.                              |

|             |                                       | Updated Table 34: HSI oscillator characteristics.                                    |

|             |                                       | Updated Section 5.3.15: I/O current injection characteristics.                       |

|             |                                       | Updated Table 48: I/O static characteristics.                                        |

|             |                                       | Updated Table 51: NRST pin characteristics.                                          |

|             |                                       | Updated Table 56: I <sup>2</sup> C characteristics.                                  |

|             |                                       | Updated Figure 39: I <sup>2</sup> C bus AC waveforms and measurement circuit.        |

|             |                                       | Updated Section 5.3.19: Communications interfaces.                                   |

|             |                                       | Updated Table 67: ADC characteristics.                                               |

|             |                                       | Added Table 70: Temperature sensor calibration values.                               |

|             |                                       | Added Table 73: Internal reference voltage calibration values.                       |

|             |                                       | Updated Section 5.3.26: FSMC characteristics.                                        |

|             |                                       | Updated Section 5.3.28: SD/SDIO MMC card host interface (SDIO) characteristics.      |

|             |                                       | Updated Table 23: Typical and maximum current consumptions in Sto                    |

|             |                                       | mode.                                                                                |

|             |                                       | Updated Section : SPI interface characteristics included Table 55.                   |

|             |                                       | Updated Section : I2S interface characteristics included Table 56.                   |

|             |                                       | Updated Table 64: Dynamic characteristics: Eternity MAC signals for SMI.             |

|             |                                       | Updated Table 66: Dynamic characteristics: Ethernet MAC signals for MII.             |

| Table 100. Document revision history (continued) |

|--------------------------------------------------|

|--------------------------------------------------|