#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | CPU32+                                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 25MHz                                                                   |

| Co-Processors/DSP               | Communications; CPM                                                     |

| RAM Controllers                 | DRAM                                                                    |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10Mbps (1)                                                              |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 5.0V                                                                    |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                       |

| Security Features               |                                                                         |

| Package / Case                  | 357-BBGA                                                                |

| Supplier Device Package         | 357-PBGA (25x25)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68360cvr25lr2 |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 6.9.3.7             | Periodic Interrupt Timer Register (PITR)          | 6-38           |

| 6.9.3.8             | Software Service Register (SWSR)                  |                |

| 6.9.3.9             | CLKO Control Register (CLKOCR)                    |                |

| 6.9.3.10            | PLL Control Register (PLLCR)                      |                |

| 6.9.3.11            | Clock Divider Control Register (CDVCR)            | 6-42           |

| 6.9.3.12            | Breakpoint Address Register (BKAR)                | 6-44           |

| 6.9.3.13            | Breakpoint Control Register (BKCR)                | 6-44           |

| 6.9.4               | Port E Pin Assignment Register (PEPAR)            | 6-48           |

| 6.10                | Memory Controller                                 | 6-50           |

| 6.10.1              | Memory Controller Key Features                    | 6-50           |

| 6.10.2              | Memory Controller Overview                        | 6-51           |

| 6.11                | General-Purpose Chip-Select Overview (SRAM Banks) | 6-56           |

| 6.11.1              | Associated Registers                              | 6-56           |

| 6.11.2              | 8-, 16-, and 32-Bit Port Size Configuration       | 6-56           |

| 6.11.3              | Write Protect Configuration                       |                |

| 6.11.4              | Programmable Wait State Configuration             | 6-56           |

| 6.11.5              | Address and Address Space Checking                | 6-57           |

| 6.11.6              | SRAM Bank Parity                                  | 6-57           |

| 6.11.7              | External Master Support                           |                |

| 6.11.8              | Global (Boot) Chip-Select Operation               | 6-58           |

| 6.11.9              | SRAM Bus Error                                    |                |

| 6.12                | DRAM Controller Overview (DRAM Banks)             |                |

| 6.12.1              | DRAM Normal Access Support                        | 6-60           |

| 6.12.2              | DRAM Page Mode Support                            | 6-60           |

| 6.12.3              | DRAM Burst Access Support                         | 6-61           |

| 6.12.4              | DRAM Bank Parity                                  | 6-62           |

| 6.12.5              | Refresh Operation                                 |                |

| 6.12.6              | DRAM Bank External Master Support                 |                |

| 6.12.7              | Double-Drive RAS Lines                            |                |

| 6.12.8              | DRAM Bus Error                                    | 6-63           |

| 6.13                | Programming Model                                 |                |

| 6.13.1              | Global Memory Register (GMR)                      |                |

| 6.13.2              | Memory Controller Status Register (MSTAT)         |                |

| 6.13.3              | Base Register (BR)                                |                |

| 6.13.4              | Option Register (OR)                              |                |

| 6.13.5              | DRAM-SRAM Performance Summary;                    | 6-78           |

#### Section 7

#### **Communication Processor Module (CPM)**

|       | Introduction                                  | 7-1 |

|-------|-----------------------------------------------|-----|

| 7.1   | RISC Controller                               | 7-3 |

| 7.1.1 | RISC Controller Configuration Register (RCCR) | 7-4 |

| 7.1.2 | RISC Microcode Revision Number                |     |

| 7.2   | Command Set                                   | 7-5 |

| 7.2.1 | Command Register Examples                     | 7-8 |

| 7.2.2 | Command Execution Latency                     |     |

|       |                                               |     |

#### MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

# ge

| Paragraph<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

| 7.6.4.2.3           | IDMA Commands (INIT_IDMA)                     | 7-38           |

| 7.6.4.3             | Starting the IDMA                             |                |

| 7.6.4.4             | Requesting IDMA Transfers                     | 7-39           |

| 7.6.4.4.1           | Internal Maximum Rate                         | 7-39           |

| 7.6.4.4.2           | Internal Limited Rate                         | 7-39           |

| 7.6.4.4.3           | External Burst Mode                           | 7-40           |

| 7.6.4.4.4           | External Cycle Steal                          | 7-42           |

| 7.6.4.5             | IDMA Bus Arbitration                          | 7-43           |

| 7.6.4.6             | IDMA Operand Transfers                        | 7-45           |

| 7.6.4.6.1           | Dual Address Mode                             |                |

| 7.6.4.6.2           | Single Address Mode (Flyby Transfers)         | 7-48           |

| 7.6.4.6.3           | Fast-Termination Option                       | 7-50           |

| 7.6.4.6.4           | Externally Recognizing IDMA Operand Transfers | 7-51           |

| 7.6.4.7             | Bus Exceptions                                |                |

| 7.6.4.7.1           | Reset                                         | 7-51           |

| 7.6.4.7.2           | Bus Error                                     | 7-51           |

| 7.6.4.7.3           | Retry                                         | 7-51           |

| 7.6.4.8             | Ending the IDMA Transfer                      |                |

| 7.6.4.8.1           | Single Buffer Mode Termination                | 7-52           |

| 7.6.4.8.2           | Auto Buffer Mode Termination.                 |                |

| 7.6.4.8.3           | Buffer Chaining Mode Termination              | 7-54           |

| 7.6.5               | IDMA Examples                                 | 7-55           |

| 7.6.5.1             | Single Buffer Examples                        | 7-55           |

| 7.6.5.2             | Buffer Chaining Example                       |                |

| 7.6.5.3             | Auto Buffer Example                           | 7-56           |

| 7.7                 | SDMA Channels.                                | 7-57           |

| 7.7.1               | SDMA Bus Arbitration and Bus Transfers        | 7-57           |

| 7.7.2               | SDMA Registers                                |                |

| 7.7.2.1             | SDMA Configuration Register (SDCR)            | 7-59           |

| 7.7.2.2             | SDMA Status Register (SDSR)                   | 7-61           |

| 7.7.2.3             | SDMA Address Register (SDAR)                  | 7-61           |

| 7.8                 | Serial Interface with Time Slot Assigner      | 7-62           |

| 7.8.1               | SI Key Features                               | 7-62           |

| 7.8.2               | TSA Overview                                  | 7-64           |

| 7.8.3               | Enabling Connections to the TSA               | 7-67           |

| 7.8.4               | SI RAM                                        | 7-68           |

| 7.8.4.1             | One Multiplexed Channel with Static Frames    | 7-69           |

| 7.8.4.2             | One Multiplexed Channel with Dynamic Frames   | 7-69           |

| 7.8.4.3             | Two Multiplexed Channels with Static Frames   | 7-70           |

| 7.8.4.4             | Two Multiplexed Channels with Dynamic Frames  | 7-71           |

| 7.8.4.5             | Programming SI RAM Entries                    | 7-72           |

| 7.8.4.6             | SI RAM Programming Example                    | 7-75           |

| 7.8.4.7             | SI RAM Dynamic Changes                        | 7-75           |

| 7.8.5               | SI Registers                                  | 7-77           |

| 7.8.5.1             | SI Global Mode Register (SIGMR)               |                |

#### MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

Title

Paragraph

#### Page Number

| Number |                                                           | Numbe |

|--------|-----------------------------------------------------------|-------|

| 10.20  | Interrupt Controller AC Electrical Specifications         | 10-66 |

| 10.21  | Baud Rate Generator AC Electrical Specifications          | 10-67 |

| 10.22  | Timer Electrical Specifications                           | 10-68 |

| 10.23  | SI Electrical Specifications                              | 10-69 |

| 10.24  | SCC in NMSI Mode—External Clock Electrical Specifications | 10-75 |

| 10.25  | SCC in NMSI MODE—Internal Clock Electrical Specifications | 10-75 |

| 10.26  | Ethernet Electrical Specifications                        | 10-77 |

| 10.27  | SMC Transparent Mode Electrical Specifications            | 10-80 |

| 10.28  | SPI Master Electrical Specifications                      | 10-82 |

| 10.29  | SPI Slave Electrical Specifications                       | 10-83 |

| 10.30  | JTAG Electrical Specifications                            | 10-85 |

#### Section 11

### **Ordering Information and Mechanical Data**

| 11.1 | Standard Ordering Information                 | 11-1 |

|------|-----------------------------------------------|------|

| 11.2 | Pin Assignment—240-Lead Quad Flat Pack (QFP)  | 11-2 |

| 11.3 | Pin Assignment—241-Lead Pin Grid Array (PGA)  | 11-4 |

| 11.4 | Pin Assignment—357-Lead BALL Grid Array (BGA) | 11-5 |

| 11.5 | Package Dimensions—CQFP (FE Suffix)           | 11-6 |

| 11.6 | Package Dimensions—PGA (RC Suffix)            | 11-7 |

| 11.7 | Package Dimensions—BGA (ZP Suffix)            | 11-8 |

|      |                                               |      |

### Appendix A Serial Performance

## Appendix B

### **Development Tools and Support**

| B.1 Motorola Software Modules.   | B-1          |

|----------------------------------|--------------|

|                                  |              |

| B.2 Other protocol Software Sup  | portB-5      |

| B.3 Third-Party Software Support | rtB-6        |

| B.4 M68360QUADS Developmen       | nt SystemB-6 |

| B.5 Other Development Boards.    | B-10         |

| B.6 Direct Target Development .  | B-10         |

## Appendix C

#### **RISC Microcode from RAM**

| C.1   | Signaling System #7 Controller | C-1 |

|-------|--------------------------------|-----|

| C.1.1 | Performance                    | C-2 |

| C.2   | Multiple GCI Controller        | C-3 |

| C.2.1 | Typical Application            | C-3 |

| C.2.2 | MGCI Controller Key Features   | C-3 |

| C.2.3 | Performance                    |     |

| C.3   | ATOM1/ATM Controller           | C-4 |

| C.3.1 | Key Features                   | C-4 |

| C.3.2 | Performance                    |     |

|       |                                |     |

MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

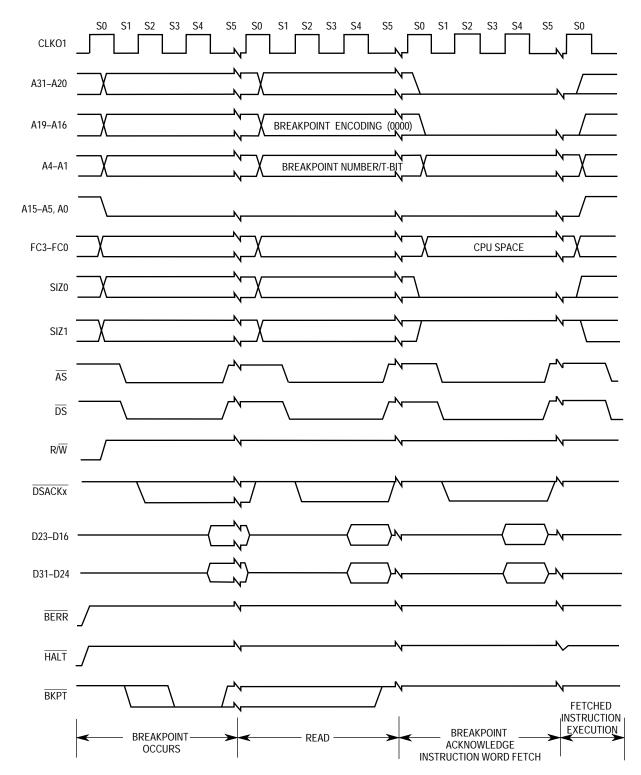

Figure 4-24. Breakpoint Acknowledge Cycle Timing (Opcode Returned)

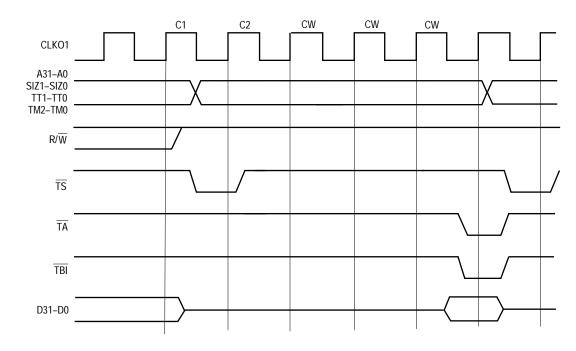

Figure 4-41. MC68EC040 Internal Registers Read Cycle

## 4.6.8 Show Cycles

The QUICC can perform data transfers with its internal modules without using the external bus, but when debugging, it is desirable to have address and data information appear on the external bus. These external bus cycles, called show cycles, are distinguished by the fact that  $\overline{AS}$  is not asserted externally.  $\overline{DS}$  is used to signal address strobe timing in show cycles.

After reset, show cycles are disabled and must be enabled by writing to the SHEN bits in the module configuration register. When show cycles are disabled, the address bus, function codes, size, and read/write signals continue to reflect internal bus activity. However,  $\overline{AS}$  and  $\overline{DS}$  are not asserted externally, and the external data bus remains in a high impedance state. When show cycles are enabled,  $\overline{DS}$  indicates address strobe timing and the external data bus contains data. The following paragraphs are a state-by-state description of show cycles, and Figure 4-45 illustrates a show cycle timing diagram. Refer to Section 10 Electrical Characteristics for specific timing information.

State 0 – During state 0, the address and function codes become valid, R/W is driven to indicate a show read or write cycle, and the size pins indicate the number of bytes to transfer. During a read, the addressed peripheral is driving the data bus, and the user must take care to avoid bus conflicts.

State 41 – One-half clock cycle later,  $\overline{DS}$  (rather than  $\overline{AS}$ ) is asserted to indicate that address information is valid.

State 42– No action occurs in state 42. The bus controller remains in state 42 (wait states will be inserted) until the internal read cycle is complete.

State 43– When  $\overline{\text{DS}}$  is negated, show data is valid on the next falling edge of the system clock. The external data bus drivers are enabled so that data becomes valid on the external bus as soon as it is available on the internal bus.

State 0 – The address, function codes, read/write, and size pins change to begin the next cycle. Data from the preceding cycle is valid through state 0.

| Mnemonic    | Description                      | Mnemonic    | Description                       |

|-------------|----------------------------------|-------------|-----------------------------------|

| ABCD        | Add Decimal with Extend          | MOVEA       | Move Address                      |

| ADD         | Add                              | MOVE CCR    | Move Condition Code Register      |

| ADDA        | Add Address                      | MOVE SR     | Move to/from Status Register      |

| ADDI        | Add Immediate                    | MOVE USP    | Move User Stack Pointer           |

| ADDQ        | Add Quick                        | MOVEC       | Move Control Register             |

| AND         | Logical AND                      | MOVEM       | Move Multiple Registers           |

| ANDI        | Logical AND Immediate            | MOVEP       | Move Peripheral Data              |

| ASL         | Arithmetic Shift Left            | MOVEQ       | Move Quick                        |

| ASR         | Arithmetic Shift Right           | MOVES       | Move Alternate Address Space      |

| Всс         | Branch Conditionally (16 Tests)  | MULS        | Signed Multiply                   |

| BCHG        | Bit Test and Change              | MULU        | Unsigned Multiply                 |

| BCLR        | Bit Test and Clear               | NBCD        | Negate Decimal with Extend        |

| BGND        | Enter Background Mode            | NEG         | Negate                            |

| ВКРТ        | Breakpoint                       | NEGX        | Negate with Extend                |

| BRA         | Branch Always                    | NOP         | No Operation                      |

| BSET        | Bit Test and Set                 | NOT         | Ones Complement                   |

| BSR         | Branch to Subroutine             | OR          | Logical Inclusive OR              |

| BTST        | Bit Test                         | ORI         | Logical Inclusive OR Immediate    |

| СНК         | Check Register against Bounds    | PEA         | Push Effective Address            |

| CHK2        | Check Register against Upper and | RESET       | Reset External Devices            |

|             | Lower Bounds                     | ROL, ROR    | Rotate Left and Right             |

| CLR         | Clear Operand                    | ROXL, ROXR  | Rotate with Extend Left and Right |

| CMP         | Compare                          | RTD         | Return and Deallocate             |

| СМРА        | Compare Address                  | RTE         | Return from Exception             |

| CMPI        | Compare Immediate                | RTR         | Return and Restore                |

| СМРМ        | Compare Memory                   | RTS         | Return from Subroutine            |

| CMP2        | Compare Register against Upper   | SBCD        | Subtract Decimal with Extend      |

|             | and Lower Bounds                 | Scc         | Set Conditionally                 |

| DBcc        | Test Condition, Decrement and    | STOP        | Stop                              |

|             | Branch (16 Tests)                | SUB         | Subtract                          |

| DIVS, DIVSL | Signed Divide                    | SUBA        | Subtract Address                  |

| DIVU, DIVUL | Unsigned Divide                  | SUBI        | Subtract Immediate                |

| EOR         | Logical Exclusive OR             | SUBQ        | Subtract Quick                    |

| EORI        | Logical Exclusive OR Immediate   | SUBX        | Subtract with Extend              |

| EXG         | Exchange Registers               | SWAP        | Swap Data Register Halves         |

| EXT, EXTB   | Sign Extend                      | TAS         | Test and Set Operand              |

| LLEGAL      | Take Illegal Instruction Trap    | TBLS, TBLSN | Table Lookup and Interpolate,     |

| JMP         | Jump                             |             | Signed                            |

| JSR         | Jump to Subroutine               | TBLU, TBLUN | Table Lookup and Interpolate,     |

| _EA         | Load Effective Address           |             | Unsigned                          |

| LINK        | Link and Allocate                | TRAPcc      | Trap Conditionally (16 Tests)     |

| PSTOP       | Low-Power Stop                   | TRAPV       | Trap on Overflow                  |

| LSL, LSR    | Logical Shift Left and Right     | TST         | Test                              |

| MOVE        | Move                             | UNLK        | Unlink                            |

#### Table 5-1. Instruction Set

| X<br>(Subroutine) | X<br>(Instruction) | Y   |

|-------------------|--------------------|-----|

| 0                 | 0                  | 0   |

| 1                 | 256                | 16  |

| 2                 | 512                | 32  |

| 3                 | 768                | 48  |

| 4                 | 1024               | 64  |

| 5                 | 1280               | 80  |

| 6                 | 1536               | 96  |

| 7                 | 1792               | 112 |

| 8                 | 2048               | 128 |

| 9                 | 2304               | 112 |

| 10                | 2560               | 96  |

| 11                | 2816               | 80  |

| 12                | 3072               | 64  |

| 13                | 3328               | 48  |

| 14                | 3584               | 32  |

| 15                | 3840               | 16  |

| 16                | 4096               | 0   |

#### Table 5-15. T8-Bit Independent Variable Entries

The first column is the value passed to the subroutine, the second column is the value expected by the table instruction, and the third column is the result returned by the subroutine.

The following value has been calculated for independent variable X:

| 31       | 16 | 15 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

|----------|----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| NOT USED |    | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

Since X is an 8-bit value, the upper four bits are used as a table offset, and the lower four bits are used as an interpolation fraction. The following results are obtained from the sub-routine:

Table Entry Offset  $\Rightarrow$  Dx [4:7] = \$B = 11

Interpolation Fraction  $\Rightarrow$  Dx [0:3] = \$D = 13

Thus, Y is calculated as follows:

Y = 80 + (13 (64 - 80)) / 16 = 67

If the 8-bit value for X were used directly by the table instruction, interpolation would be incorrectly performed between entries 0 and 1. Data must be shifted to the left four places before use:

LSL.W #4, Dx

#### MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

## 5.5.2 Processing of Specific Exceptions

The following paragraphs provide details concerning sources of specific exceptions, how each arises, and how each is processed.

**5.5.2.1 RESET.** Assertion of RESET by external hardware or assertion of the internal RE-SET signal by an internal module causes a reset exception. The reset exception has the highest priority of any exception. Reset is used for system initialization and for recovery from catastrophic failure. When the reset exception is recognized, it aborts any processing in progress, and that processing cannot be recovered. Reset performs the following operations:

- 1. Clears T0 and T1 in the SR to disable tracing

- 2. Sets the S-bit in the SR to establish supervisor privilege

- 3. Sets the interrupt priority mask to the highest priority level (%111)

- 4. Initializes the VBR to zero (\$0000000)

- 5. Generates a vector number to reference the reset exception vector

- 6. Loads the first long word of the vector into the interrupt SP

- 7. Loads the second long word of the vector into the PC

- 8. Fetches and initiates decode of the first instruction to be executed

Figure 5-11 is a flowchart of the reset exception

After initial instruction prefetches, normal program execution begins at the address in the PC. The reset exception does not save the value of either the PC or the SR.

If a bus error or address error occurs during reset exception processing, a double bus fault occurs, the processor halts, and the HALT signal is asserted to indicate the halted condition.

Execution of the RESET instruction does not cause a reset exception nor does it affect any internal CPU register. The SIM60 registers and the module control register in each internal peripheral module (DMA, timers, and serial modules) are not affected. All other internal peripheral module registers are reset the same as for a hardware reset. The external devices connected to the RESET signal are reset at the completion of the reset instruction

**5.5.2.2 BUS ERROR.** A bus error exception occurs when an assertion of the BERR signal is acknowledged. The BERR signal can be asserted by one of three sources:

- 1. External logic by assertion of the BERR input pin

- 2. Direct assertion of the internal BERR signal by an internal module

- 3. Direct assertion of the internal BERR signal by the on-chip hardware watchdog after detecting a no-response condition

Bus error exception processing begins when the processor attempts to use information from an aborted bus cycle.

The pointers provided by this register indicate the SI RAM entry word offset that is currently in progress. The register is cleared at reset.

| 31 | 30 | 29 | 28    | 27 | 26    | 25 | 24 | 23 | 22 | 21 | 20    | 19 | 18 | 17 | 16 |   |

|----|----|----|-------|----|-------|----|----|----|----|----|-------|----|----|----|----|---|

| _  | _  | V  |       |    | RbPTR |    |    | _  | —  | V  | RaPTR |    |    |    |    |   |

| 15 | 14 | 13 | 12    | 11 | 10    | 9  | 8  | 7  | 6  | 5  | 4     | 3  | 2  | 1  | 0  | _ |

| _  | _  | V  | TbPTR |    |       |    |    | _  | _  | V  | TaPTR |    |    |    |    |   |

In all cases, the value in the TxPTR or RxPTR increments by one for each entry (i.e., 16-bit SI RAM word) that is processed by the SI. Since each TxPTR and RxPTR is 5 bits each, the values in each TxPTR and RxPTR can range from 0 to 31, corresponding to 32 different SI RAM entries.

The full pointer range may not necessarily be used. For instance, if the last bit is set in the fifth SI RAM entry, then the pointer will only reflect values from 0 to 4. Once the fifth entry is processed by the SI, the pointer is reset to 0.

The V-bit in each entry shows that the entry is valid. This information is particularly useful if the PTR value happens to be zero. Additionally, the V-bits save the user from having to read both the SIRP and the SISTR to obtain the needed information.

The pointer values are described based on the four possible ways the SI RAM can be configured.

**7.8.5.6.1 SIRP When RDM = 00 (One Static TDM).** In this case, since 64 entries cannot be signified with a single 5-bit pointer, two 5-bit pointers are used—one for the first 32 entries and one for the second 32 entries.

RaPTR and RbPTR contain the address of the RAM entry currently active. When the SI services entries 1–32, RaPTR will be incremented, and RbPTR will be continuously cleared. When the SI services entries 33–64, RaPTR will be continuously cleared, and RbPTR will be incremented.

TaPTR and TbPTR contain the address of the Tx entry currently active. When the SI services entries 1–32, TaPTR will be incremented, and TbPTR will be continuously cleared. When the SI services entries 33–64, TaPTR will be continuously cleared, and TbPTR will be incremented.

**7.8.5.6.2 SIRP When RDM = 01 (One Dynamic TDM).** •For the receiver, either RaPTR or RbPTR is used, depending on which portion of the SI Rx RAM is currently active. For the transmitter, either TaPTR or TbPTR is used, depending on which portion of the SI Tx RAM is currently active.

If its V-bit is set, RaPTR contains the address of the Rx entry currently active. The SI RAM receive address block in use is 0-63, and CRORa = 0 in SISTR.

If its V-bit is set, RbPTR contains the address of the Rx entry currently active. The SI RAM receive address block in use is 64-127, and CRORa = 1 in SISTR.

If its V-bit is set, TaPTR contains the address of the Tx entry currently active. The SI RAM transmit address block in use is 128-191, and CROTa = 0 in SISTR.

## NOTE

The 1:2 ratio of the SyncCLK to the serial clock does not apply when the DPLL is used to recover the clock in the  $8\times$ ,  $16\times$ , or  $32\times$  modes. The synchronization actually occurs internally after the receive clock is generated by the DPLL; therefore, even the fastest DPLL clock generation (the  $8\times$  option) easily meets the required 1:2 ratio clocking limit.

## 7.10.13 Clock Glitch Detection

A clock glitch occurs when an input clock signal transitions between a one and zero state twice, within a small enough time period to violate the minimum high/low time specification of the input clock. Spikes are one type of glitch. Additionally, glitches can occur when excessive noise is present on a slowly rising/falling signal.

Glitched clocks are a worry to many communications systems. Not only can they cause systems to experience errors, they can potentially cause errors to occur without even being detected by the system. Systems that supply an external clock to a serial channel are often susceptible to glitches from situations such as noise, connecting/disconnecting the physical cable from the application board, or excessive ringing on the clock lines.

The SCCs on the QUICC have a special circuit designed to detect glitches that may occur in the system. The glitch circuit is designed to detect glitches that could cause the SCC to transition to the wrong state. This status information can be used to alert the system of a problem at the physical layer.

The glitch detect circuit is not a specification test. Thus, if the user develops a circuit that does not meet the input clocking specifications for the SCCs, erroneous data may be received/transmitted that is not indicated by the glitch detection logic. Conversely, if a glitch indication is signaled, it does not guarantee that erroneous data was received/transmitted.

Regardless of whether the DPLL is used, the received clock is passed through a noise filter that eliminates any noise spikes that affect a single sample. This sampling is enabled with the GDE bit of the GSMR.

If a spike is detected, a maskable receive or transmit glitched clock interrupt is generated in the event register of the SCC channel. Although the user may choose to reset the SCC receiver or transmitter or to continue operation, he should keep statistics on clock glitches for later evaluation. In addition, the glitched status indication may be used as a debugging aid during the early phases of prototype testing.

## 7.10.14 Disabling the SCCs on the Fly

If an SCC is not needed for a period of time, it may be disabled and reenabled later. In this case, a sequence of operations is followed.

These sequences ensure that any buffers in use will be properly closed and that new data will be transferred to/from a new buffer. Such a sequence is required if the parameters that must be changed are not allowed to be changed dynamically. If the register or bit description

## rial Communication Contr**Erregiscale Semiconductor, Inc.**

IADDR1–4. These four registers are used in the hash table function of the individual addressing mode. The user may write zeros to these values after reset and before the Ethernet channel is enabled to disable all individual hash address recognition functions. The SET GROUP ADDRESS command is used to enable the hash table.

TADDR. This parameter allows the user to add and delete addresses from the individual and group hash tables. After placing an address in TADDR, the user would then issue the SET GROUP ADDRESS command. TADDR\_L is the lowest order word, and TADDR\_H is the highest order word.

**7.10.23.9 ETHERNET PROGRAMMING MODEL.** The host configures SCC to operate as an Ethernet controller by the MODE bits in the GSMR.

The receive errors (collision, overrun, nonoctet aligned frame, short frame, frame too long, and CRC error) are reported through the Rx BD. The transmit errors (underrun, heartbeat, late collision, retransmission limit, and carrier sense lost) are reported through the Tx BD.

Several bit fields in the GSMR must be programmed to special values for Ethernet. See the GSMR for more details. The user should program the DSR as shown below. The 6 bytes of preamble programmed in the GSMR, in combination with the programming of the DSR shown below, causes 8 bytes of preamble on transmit (including the 1-byte start delimiter with the value \$D5).

| 15          | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------|----|----|----|----|----|---|---|---|-------------|---|---|---|---|---|---|--|--|

| SYN2 = \$D5 |    |    |    |    |    |   |   |   | SYN1 = \$55 |   |   |   |   |   |   |  |  |

**7.10.23.10 ETHERNET COMMAND SET.** Ethernet: Ethernet Command SetThe following transmit and receive commands are issued to the CR.

#### NOTE

Before issuing the CP RESET command, configure the TENA (RTS) pin to be an input. See step 3 of 7.10.23.23 SCC Ethernet Example. for more information.

**7.10.23.10.1 Transmit Commands.** The following paragraphs describe the Ethernet transmit commands.

STOP TRANSMIT Command. When used with the Ethernet controller, this command violates specified behavior of an Ethernet/IEEE 802.3 station. It should not be used.

GRACEFUL STOP TRANSMIT Command. The channel GRACEFUL STOP TRANSMIT command is used to stop transmission in an orderly way. It stops transmission after the current frame has completed transmission or undergoes a collision (immediately if there is no frame being transmitted). The GRA bit in the SCCE will be set once transmission has stopped. After transmission ceases, the Ethernet transmit parameters, including BDs, may be modified by the user. The TBPTR will point to the next Tx BD in the table. Transmission will begin once the R-bit of the next BD is set and the RESTART TRANSMIT command is issued.

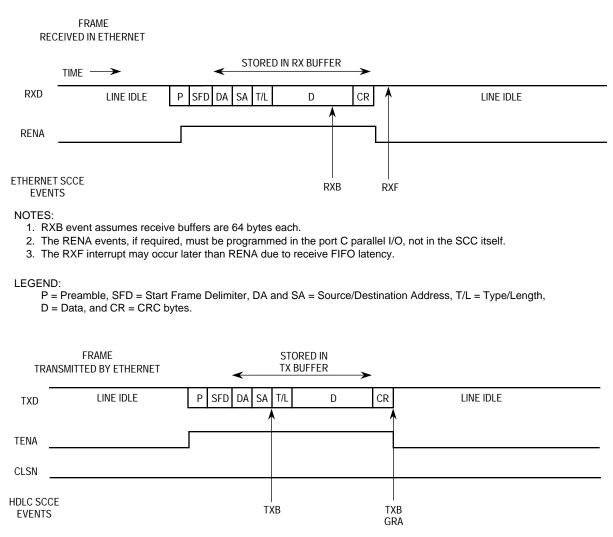

NOTES:

1. TXB events assume the frame required two transmit buffers.

2. The GRA event assumes a GRACEFUL STOP TRANSMIT command was issued during frame transmission.

3. The TENA or CLSN events, if required, must be programmed in the port C parallel I/O, not in the SCC itself.

#### Figure 7-72. Ethernet Interrupt Events Example;

**7.10.23.21 ETHERNET MASK REGISTER (SCCM).** The SCCM is referred to as the Ethernet mask register when the SCC is operating as an Ethernet controller. It is a 16-bit readwrite register that has the same bit formats as the Ethernet event register. If a bit in the Ethernet mask register is a one, the corresponding interrupt in the event register will be enabled. If the bit is zero, the corresponding interrupt in the event register will be masked. This register is cleared upon reset.

**7.10.23.22 ETHERNET STATUS REGISTER (SCCS).** This register is not valid for the Ethernet protocol. The current state of the RENA and CLSN signals may be read in port C.

#### R—Ready

- 0 = The data buffer associated with this BD is not ready for transmission. The user is free to manipulate this BD or its associated data buffer. The CP clears this bit after the buffer has been transmitted or after an error condition is encountered.

- 1 = The data buffer, which has been prepared for transmission by the user, has not been transmitted or is currently being transmitted. No fields of this BD may be written by the user once this bit is set.

## Bits 14, 10, 8-2-Reserved

W—Wrap (Final BD in Table)

- 0 = This is not the last BD in the Tx BD table.

- 1 = This is the last BD in the Tx BD table. After this buffer has been used, the CP will receive incoming data into the first BD in the table (the BD pointed to by TBASE). The number of Tx BDs in this table is programmable, and is determined only by the W-bit and the overall space constraints of the dual-port RAM.

### I—Interrupt

- 0 = No interrupt is generated after this buffer has been serviced.

- 1 = The TXB or TXE bit in the event register is set when this buffer is serviced. TXB and TXE can cause interrupts if they are enabled.

### L-Last

- 0 = This buffer does not contain the last character of the message.

- 1 = This buffer contains the last character of the message.

### CM—Continuous Mode

This bit is valid only when the SPI is configured as a master; it should be written as a zero in slave mode.

- 0 = Normal operation.

- 1 = The R-bit is not cleared by the CP after this BD is closed, allowing the associated data buffer to be retransmitted automatically when the CP next accesses this BD.

The following status bits are written by the SPI after it has finished transmitting the associated data buffer.

### UN-Underrun

The SPI encountered a transmitter underrun condition while transmitting the associated data buffer. This error condition is valid only when the SPI is configured as a slave.

### ME—Multi-Master Error

This buffer was closed because the SPISEL pin was asserted when the SPI was operating as a master. This indicates a synchronization problem between multiple masters on the SPI bus.

## rial Peripheral Interface (Spreescale Semiconductor, Inc.

- 12. Write \$00000020 to the CIMR to allow the SPI to generate a system interrupt. (The CICR should also be initialized.)

- 13. Write \$0370 to SPMODE to enable normal operation (not loopback), master mode, SPI enabled, 8-bit characters, and the fastest speed possible.

- 14. Write PBDAT bit 0 with zero to assert the SPI select pin.

- 15. Set the STR bit in the SPCOM to start the transfer.

## NOTE

After 5 bytes have been transmitted, the Tx BD is closed. Additionally, the receive buffer is closed after 5 bytes have been received because the L-bit of the Tx BD was set.

## 7.12.7 SPI Slave Example

The following list is an initialization sequence for use of the SPI as a slave. It is very similar to the SPI master example except that the SPISEL pin is used, rather than a general-purpose I/O pin.

- 1. The SDCR (SDMA Configuration Register) should be initialized to \$0740, rather than being left at its default value of \$0000.

- 2. Configure the port B pins to enable the SPIMOSI, SPIMISO, SPISEL, and SPICLK pins. Write PBPAR bits 0, 1, 2, and 3 with ones. Write PBDIR bits 0, 1, 2, and 3 with ones. Write PBODR bits 0, 1, 2, and 3 with zeros.

- 3. Write RBASE and TBASE in the SPI parameter RAM to point to the Rx BD and Tx BD in the dual-port RAM. Assuming one Rx BD at the beginning of dual-port RAM and one Tx BD following that Rx BD, write RBASE with \$0000 and TBASE with \$0008.

- 4. Program the CR to execute the INIT RX & TX PARAMS command for this channel. For instance, to execute this command for SCC1, write \$0001 to the CR. This command causes the RBPTR and TBPTR parameters of the serial channel to be updated with the new values just programmed into RBASE and TBASE.

- 5. Write RFCR with \$18 and TFCR with \$18 for normal operation.

- 6. Write MRBLR with the maximum number of bytes per receive buffer. For this case, assume 16 bytes, so MRBLR = \$0010.

- Initialize the Rx BD. Assume the Rx data buffer is at \$00001000 in main memory. Write \$B000 to Rx\_BD\_Status. Write \$0000 to Rx\_BD\_Length (not required done for instructional purposes only). Write \$00001000 to Rx\_BD\_Pointer.

- 8. Initialize the Tx BD. Assume the Tx data buffer is at \$00002000 in main memory and contains five 8-bit characters. Write \$B800 to Tx\_BD\_Status. Write \$0005 to Tx\_BD\_Length. Write \$00002000 to Tx\_BD\_Pointer.

- 9. Write \$FF to the SPIE to clear any previous events.

- 10. Write \$37 to the SPIM to enable all possible SPI interrupts.

- 11. Write \$00000020 to the CIMR to allow the SPI to generate a system interrupt. (The

## rallel Interface Port (PIP) Freescale Semiconductor, Inc.

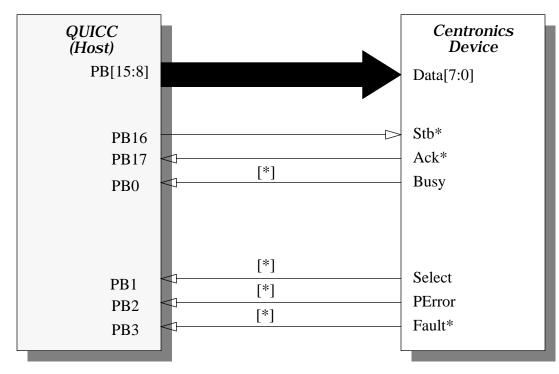

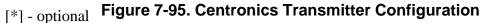

Figure 7-95. Centronics Receiver

7.13.8.1 CENTRONICS CONTROLLER KEY FEATURES. Super-set of the Centronics standard

• 8-bit or 16-Bit Data Transfer

## 'M Interrupt Controller (CIFreescale Semiconductor, Inc.

The CPIC prioritizes all interrupt sources based upon their assigned priority level. The highest priority interrupt request is presented to the CPU32+ core for servicing. After the vector number corresponding to this interrupt is passed to the CPU32+ core during an interrupt acknowledge cycle, that interrupt request is cleared. If there are remaining interrupt requests, they are then prioritized, and another interrupt request may be presented to the CPU32+ core.

The 3-bit mask in the CPU32+ status register ensures that a subsequent interrupt request at a higher interrupt priority level will suspend handling of a lower priority interrupt. The mask indicates the current processor priority, and interrupts are inhibited for all priority levels less than or equal to the current processor priority.

The CISR and the mask register in the CPU32+ core can be used together to allow a higher priority interrupt within the same interrupt level to be presented to the CPU32+ core before the servicing of a lower priority interrupt is completed. Each bit in the CISR corresponds to a CPM interrupt source. During an interrupt acknowledge cycle for a CPM interrupt, the inservice bit in the CISR is set by the CPIC for that interrupt source. The setting of the bit prevents any subsequent CPM interrupt requests at this priority level or lower (within the CPIC interrupt table), until the servicing of the current interrupt has completed and the in-service bit is cleared by the user. (Pending interrupts for these sources are still set in the CPIC during this time).

Thus, in the interrupt service routine for the CPM interrupts, the user can lower the core's mask to the next lower level (the level being serviced minus 1) to allow higher priority interrupts within this level to generate an interrupt request. This capability provides nesting of interrupt requests for CPM interrupt level sources in a similar manner as the CPU32+ core's interrupt mask provides nesting of interrupt requests for the seven interrupt priority levels.

## 7.15.3 Masking Interrupt Sources in the CPM

By programming the CPM interrupt mask register (CIMR), the user may mask the CPM interrupts to prevent an interrupt request to the CPU32+ core. Each bit in the CIMR corresponds to one of the CPM interrupt sources. To enable an interrupt, write a one to the corresponding CIMR bit.

When a masked CPM interrupt source has a pending interrupt request, the corresponding bit in the CIPR is still set, even though the interrupt is not generated to the CPU32+ core. By masking all interrupt sources in the CIMR, the user may implement a polling interrupt servicing scheme for the CPM interrupts.

When a CPM interrupt source has multiple interrupting events, the user can individually mask these events by programming a mask register within that block. Table 7-22 indicates the interrupt sources that have multiple interrupting events. Figure 7-100 shows an example of how the masking occurs, using an SCC as an example.

## <sup>M</sup> Interrupt Controller (Cl**Freescale Semiconductor, Inc.**

- 3. Decide which events in the SCCE1 will be handled in this handler and clear those bits as soon as possible. (SCCE bits are cleared by writing ones.)

- 4. Handle events in the SCC1 Rx or Tx BD tables.

- 5. Clear the SCC1 bit in the CISR.

- 6. Execute the RTE instruction. If any unmasked bits in SCCE1 remain at this time (either not cleared by the software or set by the QUICC during the execution of this handler), this interrupt source will be made pending again immediately following the RTE instruction.

The AM27–AM11 bits should be programmed to determine the block size of the chip select or  $\overline{RASx}$  line. This should be the total number of bytes in each memory array except for the EEPROM, which should be 32 Kbytes, rather than 8 Kbytes.

FCM3–FCM0 may be set to all ones to allow the chip select or  $\overline{RASx}$  line to assert on all function codes except CPU space (interrupt acknowledge). It is advisable to program FCM3–FCM0 to ones, at least during the initial stages of debugging.

BCYC1–BCYC0 is not applicable.

PGME should be set to enable page mode and cleared otherwise.

SPS1–SPS0 should be cleared (32-bit SRAM port).

DSSEL should be set only if this is a DRAM bank.

## 9.8.4 Interfacing Multiple QUICCs to an MC68EC030

It is possible to interface multiple QUICCs to an MC68EC030. The first QUICC can be configured as previously shown in this subsection. Additional QUICCs should be configured as noted in the following list:

- The additional QUICCs should have their CONFIG2–CONFIG0 pins configured for slave mode, global chip select *disabled*, and MBAR at \$003FF04.

- The MBAR of the additional QUICCs should be programmed using the MBARE pin and MBARE register as described in the Section 6 System Integration Module (SIM60).

- An external bus arbiter is required to take the bus request of the additional QUICC (which is an output because of the CONFIG2–CONFIG0 pins) and prioritize it with the other QUICCs, present it to the MC68EC030, and issue a bus grant to the appropriate QUICC.

- An external interrupt prioritizer is required to determine which QUICC IOUT2–IOUT0 pins are currently routed to the MC68EC030. Alternatively, the additional QUICC should have its interrupts brought out on a single RQOUT pin, which is routed to one of the original QUICC interrupt inputs. This would eliminate the external logic.

## 9.8.5 Using a Higher Speed MC68EC030 Master with the QUICC

It is possible to interface an MC68EC030 and QUICC through an asynchronous bus. This should allow an external master to operate at higher frequencies than those of the QUICC with minimal effort. As of this writing, the QUICC top frequency is 25 MHz; whereas, MC68EC030s are available up to 40 MHz. One potentially attractive option for a designer would be to consider disabling the CPU32+ core and increasing system performance by adding a 40-MHz MC68EC030 asynchronously. While this option is available, it is important for the designer to consider what effects a higher speed MC68EC030 would ultimately have on system cost and performance over using the QUICC CPU32+ at a lower frequency.

For the designer to take full advantage of a high-speed MC68EC030, it will be necessary to add additional glue to that shown in Figure 9-27. The additional circuitry takes the form of a DRAM controller, which is used instead of using the QUICC memory controller. The need for the additional logic is twofold. First, if the QUICC memory controller capabilities are used, all memory accesses would be at the clock rate of 25 MHz. In addition, since the

## INDEX

#### Α

A/D Converters 7-312 A/D Field 5-68 A/D Register 5-70, 5-71 A26-A0 2-1 A31-A28 2-1 Accessing the HDLC Bus 7-192 Achieving Synchronization in Transparent Mode 7-223 ACK 7-333 Address Ethernet Address Recognition 7-252 Address Bus 2-1 Address Error Exception 5-42, 5-46 Address Multiplexing 6-58 Address Register 5-6, 5-7 Address Strobe 4-4 ADI B-9 A-Line 5-44, 5-56, 5-59 Alternate Function Code 5-6 AMUX 2-7, 2-9, 6-48, 6-49 AppleTalk 1-10, 7-116, 7-117, 7-170, 7-196 AppleTalk Controller 7-196 AppleTalk Memory Map and Programming Model 7-198 Connecting the QUICC to LocalTalk 7-199 GSMR Programming 7-199 HDLC Frames 7-196 LocalTalk 7-196 LocalTalk Frame Format 7-197 PSMR Programming 7-200 QUICC AppleTalk Hardware Connection 7-198 AppleTalk Controller 7-196 AppleTalk Memory Map and Programming Model 7-198 **Applications 9-1** Arbitration Level 6-33 Arbitration Synchronous Timing Mode 6-31

Architectural Approach 1-6 Architecture Overview 1-4 AS 2-8, 2-13, 4-3, 6-30, 6-63, 7-41, 7-44, 7-58 Asynchronous 4-20 Asynchronous Protocols 7-134 ATEMP 5-62, 5-72 Auto Baud 7-166 Auto Buffer 7-34 Auto Buffer 7-34 Auto Buffer Example 7-56 Autovector 4-6, 4-38 AVEC 2-8, 4-6, 4-38, 4-41, 6-8, 6-26, 6-48 AVECO 6-26, 6-48 AVR 6-34

#### В

B0 5-49, 5-51, 5-52, 5-53, 5-54, 5-57 B1 5-49, 5-51, 5-53 Background 5-14, 5-26, 5-34 Background Processing State 5-59 Bank Parity 6-62 Base Address 3-1 BCLRI 4-58, 6-25, 6-33 BCLRIID 6-25 BCLRO 2-9, 2-10, 6-25, 6-31, 6-33, 7-44, 7-51, 7-58 BCR 7-31 **BDLE 7-204** BDLE-BISYNC DLE Register 7-208 BERR 2-10, 4-5, 4-20, 4-41, 7-51 BERR Signal 5-40 BG 2-9, 2-10, 4-49, 4-53, 6-26, 6-31, 6-32, 7-44 BGACK 2-9, 4-49, 6-26, 6-31, 7-44 BGND 5-60, 5-61, 5-62 **Bidirectional Centronics 7-331** Big-Endian 7-126, 7-321 BISYNC 7-114, 7-115, 7-200 BISYNC Channel Frame Reception 7-202

MC68356 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com