#### NXP USA Inc. - MC68360VR25L Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | CPU32+                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 25MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                  |

| RAM Controllers                 | DRAM                                                                 |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10Mbps (1)                                                           |

| SATA                            | -                                                                    |

| USB                             | -                                                                    |

| Voltage - I/O                   | 5.0V                                                                 |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                      |

| Security Features               | -                                                                    |

| Package / Case                  | 357-BBGA                                                             |

| Supplier Device Package         | 357-PBGA (25x25)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68360vr25l |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Paragraph<br>Number | Title                                                     | Page<br>Number |

|---------------------|-----------------------------------------------------------|----------------|

| 9.4.2.7             | EEPROM                                                    |                |

| 9.4.2.8             | DRAM SIMM                                                 |                |

| 9.4.2.9             | DRAM Devices                                              |                |

| 9.4.3               | Software Configuration                                    |                |

| 9.4.3.1             | Basic Initialization                                      |                |

| 9.4.3.2             | Configuring the Memory Controller.                        |                |

| 9.4.4               | Interfacing Multiple QUICCs to an MC68EC040               |                |

| 9.5                 | Selecting Cache Modes on the MC68EC040                    |                |

| 9.5.1               | The Algorithm                                             |                |

| 9.5.2               | Protection                                                |                |

| 9.5.3               | MC68EC040 Cache Behavior                                  |                |

| 9.5.4               | Enabling the Caching Modes                                |                |

| 9.6                 | Interfacing the QUICC to the 53C90 scsi controller        |                |

| 9.6.1               | SCSI General Overview                                     |                |

| 9.6.2               | Physical Interface                                        |                |

| 9.6.3               | Logical Interface                                         |                |

| 9.6.4               | Functional Description                                    |                |

| 9.6.5               | Hardware Configuration                                    |                |

| 9.6.5.1             | Clocking Strategy.                                        |                |

| 9.6.5.2             | Reset Strategy                                            |                |

| 9.6.5.3             | Read/Write timing                                         |                |

| 9.6.5.4             | Interrupt Handling                                        |                |

| 9.6.5.5             | IDMA1 Setup and Timing.                                   |                |

| 9.6.5.6             | QUICC I/O Ports                                           |                |

| 9.6.6               | Active SCSI Terminations                                  |                |

| 9.6.7               | Software Configuration                                    |                |

| 9.6.7.1             | Configuring IDMA1                                         |                |

| 9.6.7.2             | Configuring The Memory Controller.                        |                |

| 9.7                 | Using the QUICC as a TAP Controller for Board Self-Test   |                |

| 9.7.1               | Board Layout                                              |                |

| 9.7.2               | Board Testing                                             |                |

| 9.7.3               | Microcontroller Interface                                 |                |

| 9.7.4               | Test Pattern Generation                                   |                |

| 9.8                 | Interfacing an MC68EC030 Master to the QUICC In Slave Mod |                |

| 9.8.1               | MC68EC030 to QUICC Interface                              |                |

| 9.8.1.1             | MC68EC030 Reads and Writes to QUICC                       |                |

| 9.8.1.2             | Clocking Strategy.                                        |                |

| 9.8.1.3             | Reset Strategy                                            |                |

| 9.8.1.4             | Interrupts                                                |                |

| 9.8.1.5             | Bus Arbitration                                           |                |

| 9.8.1.6             | Breakpoint Generation                                     |                |

| 9.8.1.7             | Bus Monitor Function                                      |                |

| 9.8.1.8             | Spurious Interrupt Monitor                                |                |

| 9.8.1.9             | Software Watchdog                                         |                |

| 9.8.1.10            | Periodic Interval Timer                                   | 9-79           |

#### MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

tire word access will be retried. This is true even if the relinquish and retry was asserted on the second access and the first 8-bit access was completed normally.

Figure 4-32. Late Retry Sequence

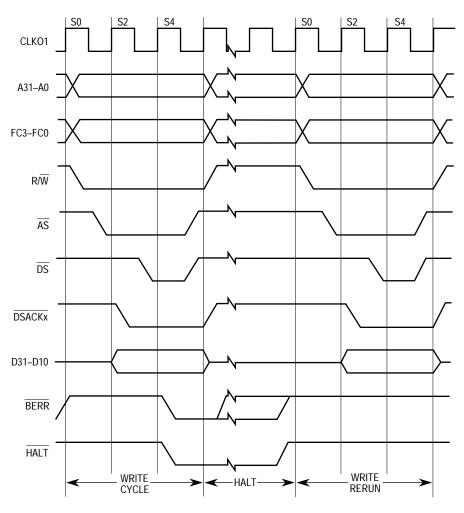

# 4.5.3 Halt Operation

When HALT is asserted and BERR is not asserted, the QUICC halts external bus activity at the next bus cycle boundary (see Figure 4-33). HALT by itself does not terminate a bus cycle. HALT affects external bus cycles only; thus, a program that does not require use of the external bus may continue executing until it requires use of the external bus.

Negating and reasserting HALT in accordance with the correct timing requirements provides a single step (bus cycle to bus cycle) operation. The single-cycle mode allows the user to proceed through (and debug) external QUICC operations, one bus cycle at a time. Since the occurrence of a bus error while HALT is asserted causes a retry operation, the user must anticipate retry cycles while debugging in the single-cycle mode. The single-step operation and the software trace capability allow the system debugger to trace single bus cycles, single instructions, or changes in program flow.

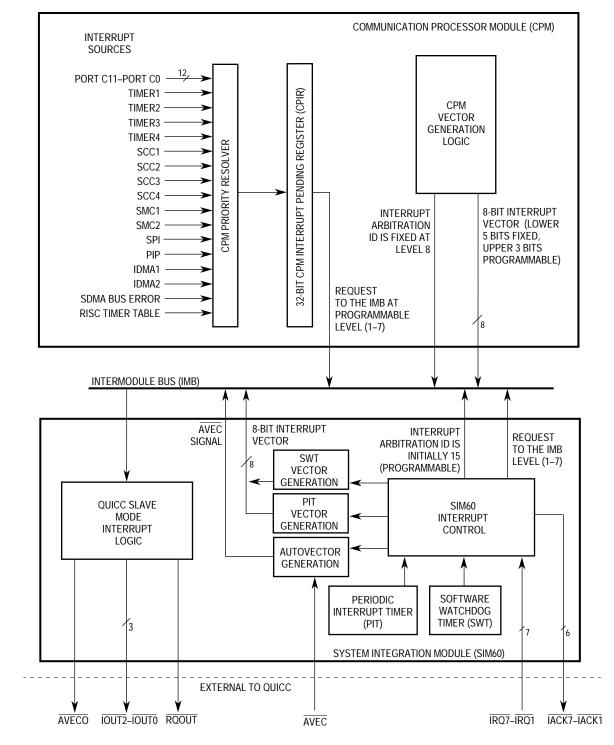

Figure 6-3. QUICC Interrupt Structure

In the interrupt arbitration process, the module places its arbitration ID on the IMB. The arbitration ID ranges in value from 0 to 15. The SIM60 interrupt controller arbitration ID is initialized to 15 (the highest value), but may be lowered if desired. The higher arbitration value always wins.

stem Integration Module (Emerscale Semiconductor, Inc.

### DE—Destination Access Bus Error

The buffer was closed due to a bus error on the destination access. An interrupt (BED) will be generated, regardless of the I-bit. The RISC will clear the V-bit of this BD.

### DA—Done Asserted During Transfer

The buffer was closed due to the assertion of DONEx. An interrupt (DONE) will be generated, regardless of the I-bit. The RISC will clear the V-bit of this BD.

### Data Length

The data length is the number of bytes that the IDMA should transfer from/to this BD's data buffer. The data length should be programmed to a value greater than zero.

### Source Buffer Pointer

The source buffer pointer contains the address of the associated source data buffer. The buffer may reside in either internal or external memory.

### NOTE

In single address mode when the source is a device, this field is ignored. In dual address mode when the source is a device, this field should contain the device address.

### **Destination Buffer Pointer**

The destination buffer pointer contains the address of the associated destination data buffer. The buffer may reside in either internal or external memory.

### NOTE

In single address mode when the destination is a device, this field is ignored. In dual address mode when the destination is a device, this field should contain the device address.

**7.6.4.2.3 IDMA Commands (INIT\_IDMA).** This command causes the RISC controller to reinitialize its IDMA internal state to the condition it had after a system reset. The IDMA BD pointer is reinitialized to the top of BD ring. When in the auto buffer and buffer chaining modes, the IDMA can be reset by setting the RST bit in the CMR and issuing the INIT\_IDMA command. The INIT\_IDMA command should only be executed in conjunction with the setting of the RST bit in the CMR.

**7.6.4.3 STARTING THE IDMA.** Once the channel has been initialized with all parameters required for a transfer operation, it is started by setting the STR bit in the CMR. After the channel has been started, any register that describes the current operation may be read but not modified (SAPR, DAPR, FCR, or BCR).

Once STR has been set, the channel is active and either accepts operand transfer requests in external mode or generates requests automatically in internal mode. When the first valid external request is recognized, the IDMA arbitrates for the bus. The DREQx input is ignored until STR is set.

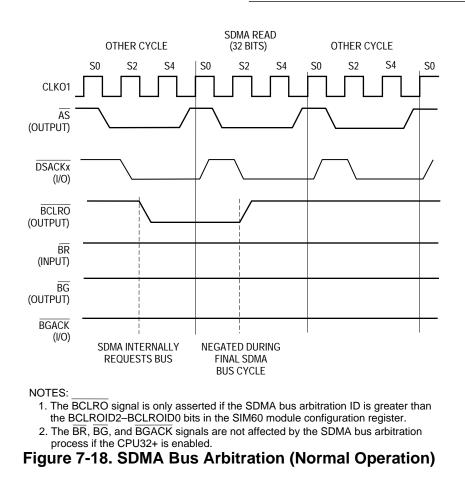

The relative priority between the two IDMAs and the SDMA channels is user programmable. Regardless of system configuration, if the IDMA is a bus master when a higher priority SDMA channel needs to transfer over the bus, the SDMA will steal cycles from the IDMA with no arbitration overhead.

When the QUICC is in slave mode (CPU32+ is disabled) the SDMA can steal cycles from the IDMA with no arbitration overhead. See Section 4 Bus Operation for diagrams of bus arbitration by an internal master in slave mode.

# 7.7.2 SDMA Registers

The SDMA channels have one configuration register; otherwise, they are controlled transparently to the user, through the configuration of the SCCs, SMCs, and SPI. The only useraccessible registers associated with the SDMA are the SDMA configuration register (SDCR), SDMA address register (SDAR), a read-only register used for diagnostics in case of an SDMA bus error, and the SDMA status register (SDSR).

**7.7.2.1 SDMA CONFIGURATION REGISTER (SDCR).** The 16-bit SDCR is used to configure all 14 SDMA channels. It is always readable and writable in the supervisor mode, although writing the SDCR is not recommended unless the CP is disabled. SDCR is cleared at reset.

**7.8.5.3 SI CLOCK ROUTE REGISTER (SICR).** The 32-bit SICR is used to define the SCC clock sources. The clock source can be one of the four baud rate generators or an input from a bank of clock pins. The SICR appears to the user as a memory-mapped, read-write register and is cleared at reset.

| 31  | 30  | 29 | 28   | 27 | 26 | 25   | 24 | 23  | 22  | 21 | 20   | 19 | 18   | 17   | 16 |  |

|-----|-----|----|------|----|----|------|----|-----|-----|----|------|----|------|------|----|--|

| GR4 | SC4 |    | R4CS |    |    | T4CS |    | GR3 | SC3 |    | R3CS |    | T3CS |      |    |  |

| 15  | 14  | 13 | 12   | 11 | 10 | 9    | 8  | 7   | 6   | 5  | 4    | 3  | 2    | 1    | 0  |  |

| GR2 | SC2 |    | R2CS |    |    | T2CS |    | GR1 | SC1 |    | R1CS |    |      | T1CS |    |  |

GRx—Grant Support of SCCx

- 0 = SCCx transmitter does not support the grant mechanism. The grant is always asserted internally.

- 1 = SCCx transmitter supports the grant mechanism as determined by the GMx bit of its channel.

### SCx—SCCx Connection

- 0 = SCCx is not connected to the multiplexed SI but is either connected directly to the NMSIx pins or is not used. The choice of general-purpose I/O port pins versus SCCn pins is made in the parallel I/O control register.

- 1 = SCCx is connected to the multiplexed SI. The NMSIx receive pins are available for other purposes.

### RxCS—Receive Clock Source for SCCx

These bits are ignored when the SCCx is connected to the TSA (SCx = 1).

- 000 = SCCx receive clock is BRG1.

- 001 = SCCx receive clock is BRG2.

- 010 = SCCx receive clock is BRG3.

- 011 = SCCx receive clock is BRG4.

- 100 = SCCx receive clock for x = 1,2 is CLK1 and for x = 3,4 is CLK5.

- 101 = SCCx receive clock for x = 1,2 is CLK2 and for x = 3,4 is CLK6.

- 110 = SCCx receive clock for x = 1,2 is CLK3 and for x = 3,4 is CLK7.

- 111 = SCCx receive clock for x = 1,2 is CLK4 and for x = 3,4 is CLK8.

TxCS—Transmit Clock Source for SCCx

These bits are ignored when SCCx is connected to the TSA (SCx = 1).

- 000 = SCCx transmit clock is BRG1.

- 001 = SCCx transmit clock is BRG2.

- 010 = SCCx transmit clock is BRG3.

- 011 = SCCx transmit clock is BRG4.

- 100 = SCCx transmit clock for x = 1,2 is CLK1 and for x = 3,4 is CLK5.

- 101 = SCCx transmit clock for x = 1,2 is CLK2 and for x = 3,4 is CLK6.

- 110 = SCCx transmit clock for x = 1,2 is CLK3 and for x = 3,4 is CLK7.

- 111 = SCCx transmit clock for x = 1,2 is CLK4 and for x = 3,4 is CLK8.

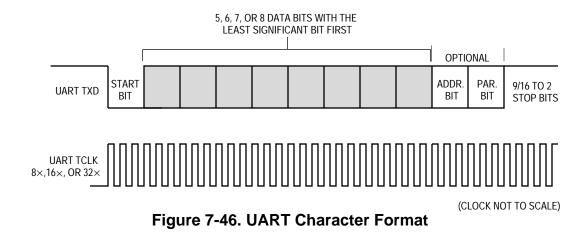

Since the transmitter and receiver work asynchronously, there is no need to connect transmit and receive clocks. Instead, the receiver oversamples the incoming data stream (usually by a factor of 16) and uses some of these samples to determine the bit value. Traditionally the middle three samples of the sixteen samples are used. Two UARTs can communicate using a system like this if parameters, such as the parity scheme and character length, are the same for both transmitter and receiver.

When data is not transmitted in the UART protocol, a continuous stream of ones is transmitted, called the idle condition. Since the start bit is always a zero, the receiver can detect when real data is once again present on the line. UART also specifies an all-zeros character called a break, which is used to abort a character transfer sequence.

Many different protocols have been defined using asynchronous characters, but the most popular of these is the RS-232 standard. RS-232 specifies standard baud rates, handshaking protocols, and mechanical/electrical details. Another popular standard using the same character format is RS-485, which defines a balanced line system allowing longer cables than RS-232 links. Synchronous protocols like HDLC are sometimes defined to run over asynchronous links. Other protocols like Profibus extend the UART protocol to include LAN-oriented features such as token passing.

All the standards provide handshaking signals, but some systems require just three physical lines: transmit data, receive data, and ground.

Many proprietary standards have been built around the asynchronous character frame, and some even implement a multidrop configuration. In multidrop systems, more than two stations may be present on a network, with each having a specific address. Frames made up of many characters may be broadcast, with the first character acting as a destination address. To allow this, the UART frame is extended by one bit to distinguish between an address character and the normal data characters.

Additionally, a synchronous form of the UART protocol exists where start and stop bits are still present, but a clock is provided with each bit, so the oversampling technique is not required. This mode is called "isochronous" operation or, more often, synchronous UART.

### rial Communication Contr**Erectscale Semiconductor, Inc.**

In normal UART mode with  $16 \times$  oversampling, the FSB bits (14–11) in the DSR are decoded as follows:

- 1111 = Last Transmitted Stop Bit 16/16 (the default value after reset)

- 1110 = Last Transmitted Stop Bit 15/16

- 1101 = Last Transmitted Stop Bit 14/16

- 1100 = Last Transmitted Stop Bit 13/16

- 1011 = Last Transmitted Stop Bit 12/16

- 1010 = Last Transmitted Stop Bit 11/16

- 1001 = Last Transmitted Stop Bit 10/16

- 1000 = Last Transmitted Stop Bit 9/16

- 0xxx = Invalid. Do not use.

When the UART is configured for  $32 \times$  oversampling, the FSB bits (14–11) in the DSR are decoded as follows:

- 1111 = Last Transmitted Stop Bit 32/32 (the default value after reset)

- 1110 = Last Transmitted Stop Bit 31/32

- 1101 = Last Transmitted Stop Bit 30/32

- 1100 = Last Transmitted Stop Bit 29/32

- 1011 = Last Transmitted Stop Bit 28/32

- 1010 = Last Transmitted Stop Bit 27/32

- 1001 = Last Transmitted Stop Bit 26/32

- 1000 = Last Transmitted Stop Bit 25/32

- 0111 = Last Transmitted Stop Bit 24/32

- 0110 = Last Transmitted Stop Bit 23/32

- 0101 = Last Transmitted Stop Bit 22/320101 = Last Transmitted Stop Bit 22/32

- 0100 = Last Transmitted Stop Bit 22/320100 = Last Transmitted Stop Bit 21/32

- 0100 = Last Transmitted Stop Bit 21/320011 = Last Transmitted Stop Bit 20/32

- 0011 = Last Transmitted Stop Bit 20/320010 = Last Transmitted Stop Bit 19/32

- 0010 = Last Transmitted Stop Bit 19/32

- 0001 = Last Transmitted Stop Bit 18/32

- 0000 = Last Transmitted Stop Bit 17/32

When the UART is configured for  $8\times$  oversampling, the FSB bits (14–11) in the DSR are decoded as follows:

- 1111 = Last Transmitted Stop Bit 8/8 (the default value after reset)

- 1110 = Last Transmitted Stop Bit 7/8

- 1101 = Last Transmitted Stop Bit 6/8

- 1100 = Last Transmitted Stop Bit 5/8

- 10xx = Invalid. Do not use.

- 01xx = Invalid. Do not use.

- 00xx = Invalid. Do not use.

The UART receiver can always receive fractional stop bits. The next character's start bit may begin at any time after the three middle samples of the stop bit have been taken.

**7.10.16.14 UART ERROR-HANDLING PROCEDURE.** The UART controller reports character reception and transmission error conditions via the channel BDs, the error counters,

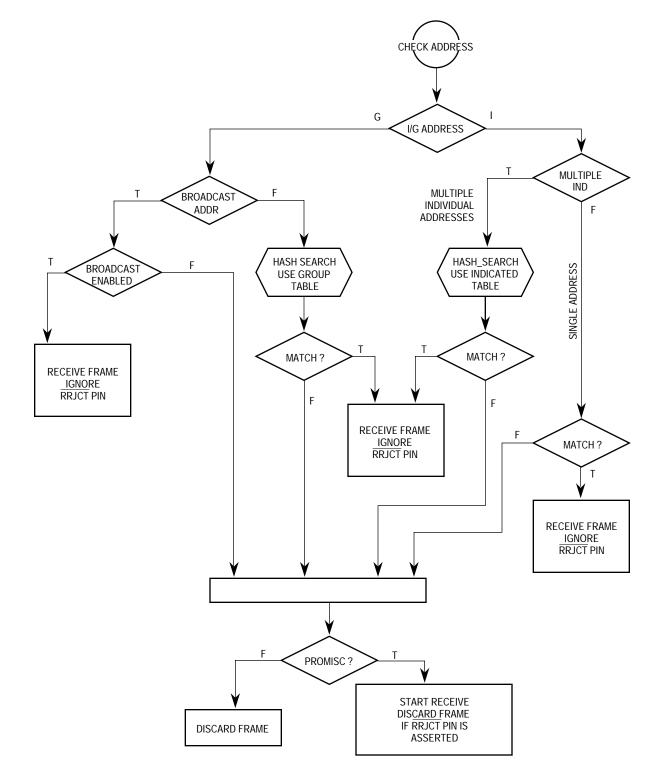

Figure 7-70. Ethernet Address Recognition Flowchart

**7.10.23.12 HASH TABLE ALGORITHM.** The hash table process used in the individual and group hash filtering operates as follows. The Ethernet controller maps any 48-bit address

# 7.11.2 General SMC Mode Register (SMCMR)

The operating mode of each SMC port is defined by the 16-bit, memory-mapped, read-write SMCMR. See the specific SMC protocol for more information on this register.

# 7.11.3 SMC Buffer Descriptors

When the SMCs are configured to operate in GCI mode, the memory structure for the SMCs is pre-defined to be one word long for transmit and one word long for receive. These one-word structures are detailed later when the GCI operation is described in more detail.

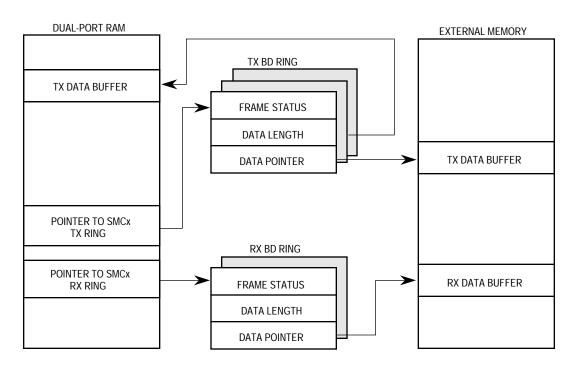

However, in UART and transparent modes of operation, the SMCs have a memory structure that is like that of the SCCs. The data associated with the SMCs is stored in buffers. Each buffer is referenced by BD organized in a buffer descriptor ring located in the dual-port RAM (see Figure 7-74).

Figure 7-74. SMC Memory Structure

The BD ring allows the user to define buffers for transmission and buffers for reception. Each BD ring forms a circular queue. The CP confirms reception and transmission (or indicates error conditions) using the BDs to inform the processor that the buffers have been serviced.

The actual buffers may reside in either external memory or internal memory. Data buffers may reside in the parameter area of an SCC or SMC if that channel is not enabled.

# 7.11.4 SMC Parameter RAM

Each SMC parameter RAM area begins at the same offset from each SMC base area. The protocol-specific portions of the SMC parameter RAM are discussed in the specific protocol

**7.11.7.5 SMC UART RECEPTION PROCESSING.** When the CPU32+ core enables the SMC receiver in UART mode, it will enter hunt mode, waiting for the first character to arrive. Once the first character arrives, the first Rx BD is checked by the CP to see if it is empty. It then begins storing characters in the associated data buffer.

When the data buffer has been filled or the MAX\_IDL timer has expired (assuming it was enabled), the SMC clears the E-bit in the BD and generates an interrupt if the I-bit in the BD is set. If the incoming data exceeds the length of the data buffer, the SMC will fetch the next BD in the table and, if it is empty, will continue to transfer data to this BD's associated data buffer.

If the CM bit is set in the Rx BD, the E-bit will not be cleared, allowing the associated data buffer to be overwritten automatically when the CP next accesses this data buffer.

**7.11.7.6 SMC UART PROGRAMMING MODEL.** An SMC configured as a UART uses the same data structure as in the other modes. The SMC UART data structure supports multibuffer operation. The SMC UART allows the user to transmit break and preamble sequences. Overrun, parity, and framing errors are reported via the BDs. In its simplest form, the SMC UART can function in a character-oriented environment. Each character is transmitted with accompanying stop bits and parity (as configured by the user), and received into separate 1-byte buffers. Reception of each buffer may generate a maskable interrupt.

Many applications may want to take advantage of the message-oriented capabilities supported by the SMC UART by using linked buffers (in either receive or transmit). In this case, data is handled in a message-oriented environment; users can work on entire messages rather than operating on a character-by-character basis. A message may span several linked buffers. Each message can be both transmitted and received as a linked list of buffers without any intervention from the CPU32+, which achieves both ease in programming and significant savings in processor overhead.

In the message-oriented environment, the idle sequence is used as the message delimiter. The transmitter is able to generate an idle sequence before starting a new message, and the receiver is able to close a buffer upon detection of idle sequence.

**7.11.7.7 SMC UART COMMAND SET.** The following transmit and receive commands are issued to the CR.

**7.11.7.7.1 Transmit Commands.** The following paragraphs describe the SMC UART transmit commands.

**STOP TRANSMIT Command**. The channel STOP TRANSMIT command disables the transmission of characters on the transmit channel. If this command is received by the SMC UART controller during message transmission, transmission of that message is aborted. The SMC UART completes transmission of any data already transferred to its FIFO and shift register (up to two characters) and then stops transmitting data. The TBPTR is not advanced when this command is issued.

The SMC UART transmitter will transmit a programmable number of break sequences and then start to transmit idles. The number of break sequences (which may be zero) should be

- SM—SMC Mode

- 00 = GCI or SCIT support

- 01 = Reserved

- 10 = UART

- 11 = Totally transparent operation (must be selected for SMC transparent operation)

- DM—Diagnostic Mode

- 00 = Normal operation

- 01 = Local loopback mode

- 10 = Echo mode

- 11 = Reserved

TEN—SMC Transmit Enable

- 0 = SMC transmitter disabled

- 1 = SMC transmitter enabled

### NOTES

Once the SMC transmit enable bit is cleared, the bit must not be reenabled for at least 3 serial clocks.

REN—SMC Receive Enable

0 = SMC receiver disabled

1 = SMC receiver enabled

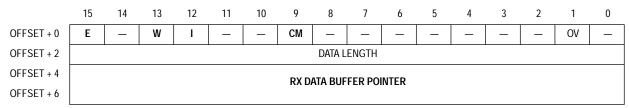

**7.11.10.11 SMC TRANSPARENT RECEIVE BUFFER DESCRIPTOR (RX BD).** The CP reports information about the received data for each buffer using Rx BDs. The CP closes the current buffer, generates a maskable interrupt, and starts to receive data into the next buffer after one of the following events:

- 1. Detecting an overrun error

- 2. Detecting a full receive buffer

- 3. Issuing the ENTER HUNT MODE command

NOTE : Entries in boldface must be initialized by the user

- E—Empty

- 0 = The data buffer associated with this Rx BD has been filled with received data, or data reception has been aborted due to an error condition. The CPU32+ core is free to examine or write to any fields of this Rx BD. The CP will not use this BD again while the E-bit remains zero.

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|----|----|----|----|----|----|---|---|------------|---|---|---|---|---|---|---|--|

| OFFSET + 0 | Е  | R  |    |    |    |    |   |   | CHARACTER1 |   |   |   |   |   |   |   |  |

| OFFSET + 2 | Е  | R  |    |    |    |    |   |   | CHARACTER2 |   |   |   |   |   |   |   |  |

| OFFSET + 4 | Е  | R  |    |    |    |    |   |   | CHARACTER3 |   |   |   |   |   |   |   |  |

| OFFSET + 6 |    |    |    |    |    |    |   |   |            |   |   |   |   |   |   |   |  |

| OFFSET + E  | E | R |  |  |  | CHARACTER8 |

|-------------|---|---|--|--|--|------------|

| OFFSET + 10 | 1 | 1 |  |  |  | RCCM       |

| OFFSET +1 2 |   |   |  |  |  | RCCR       |

### CHARACTER1-8—Control Character Values

These fields define control characters that should be compared to the incoming character. For less than 8 bits characters, the msb bits should be zero.

### E—End of Table

- 0 = This entry is valid. The lower 8 bits will be checked against the incoming character.

- 1 = The entry is not valid. This must be the last entry in the Control Characters Table.

### NOTE

In tables with 8 control characters this bit is always 0.

### R—Reject character

- 0 = The character is not rejected but written into the receive buffer. The buffer is then closed and a new receive buffer is used if there is more data in the message. A maskable (I Bit in the Receive BD) interrupt is generated.

- 1 = If this character is recognized it will not be written to the receive buffer. Instead, it is written to the Received Control Characters Register (RCCR) and a maskable interrupt is generated. The current buffer is not closed when a control character is received with R set.

### RCCM—Received Control Character Mask

The value in this register is used to mask the comparison of CHARACTER1 through CHARACTER8. The lower eight bits of RCCM correspond to the lower eight bits of CHARACTER1-8, and are decoded as follows.

- 0 = Mask this bit in the comparison of the incoming character, and CHARACTER1 through CHARACTER8.

- 1 = The address comparison on this bit proceeds normally. No masking takes place.

### NOTE

The two most significant bits (bit 15 and bit 14) of RCCM must be set, or erratic operation may occur during the control character recognition process.

| Name    | Bit Number | Name      | Bit Number | Name     | Bit Number |  |

|---------|------------|-----------|------------|----------|------------|--|

| g1.cntl | 2          | g10.cntl  | 32         | pbhl.ctl | 155        |  |

| g2.cntl | 5          | add.cntl  | 59         | pblh.ctl | 159        |  |

| g3.cntl | 8          | addh.cntl | 83         | pchh.ctl | 170        |  |

| g4.cntl | 13         | g11.cnt   | 89         | pchl.ctl | 174        |  |

| g5.cntl | 16         | db.ctl    | 110        | pclh.ctl | 179        |  |

| g6.cntl | 18         | pahh.ctl  | 131        | g12.cntl | 188        |  |

| g7.cntl | 23         | pahl.ctl  | 136        | g13.cntl | 191        |  |

| g8.cntl | 27         | palh.ctl  | 141        | g14.cntl | 194        |  |

| g9.cntl | 29         | pbhh.ctl  | 150        |          |            |  |

Table 8-1. Boundary Scan Control Bits

The boundary scan bit definitions are listed in Table 8-2.

The first column in the table defines the bit's ordinal position in the boundary scan register. The shift register cell nearest TDO (i.e., first to be shifted out) is defined as bit 0; the last bit to be shifted out is 195.

The second column references one of the four QUICC cell types depicted in Figure 8-3 through , which describe the cell structure for each type.

The third column lists the pin name for all pin-related cells or defines the name of bidirectional control register bits.

The fourth column lists the pin type for convenience, where TS-Output indicates a threestateable output pin, I/O indicates a bidirectional pin, and OD-I/O denotes an open-drain bidirectional pin.

The last column indicates the associated boundary scan register control bit for bidirectional, three-state, and open-drain output pins.

Bidirectional pins include a single scan cell for data (IO.Cell) as depicted in Figure 8-6. These bits are controlled by the cell shown in Figure 8-5. The value of the control bit determines whether the bidirectional pin is an input or an output. One or more bidirectional data cells can be serially connected to a control cell as shown in Figure 8-7. Note that, when sampling the bidirectional data cells, the cell data can be interpreted only after examining the IO control cell to determine pin direction, and also note that the control cell captures the value of the following cell.

NOTE: All timing is shown with respect to 0.8-V and 2.0-V levels.

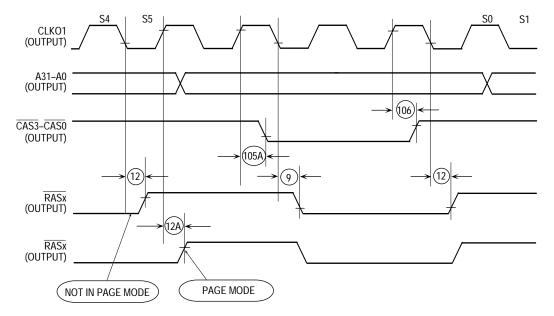

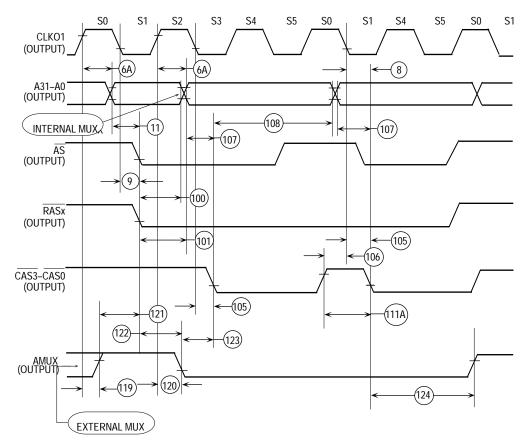

### Figure 10-22. DRAM: Refresh Cycle

NOTE: All timing is shown with respect to 0.8-V and 2.0-V levels.

#### Figure 10-23. DRAM: Page-Mode—Page-Hit

MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

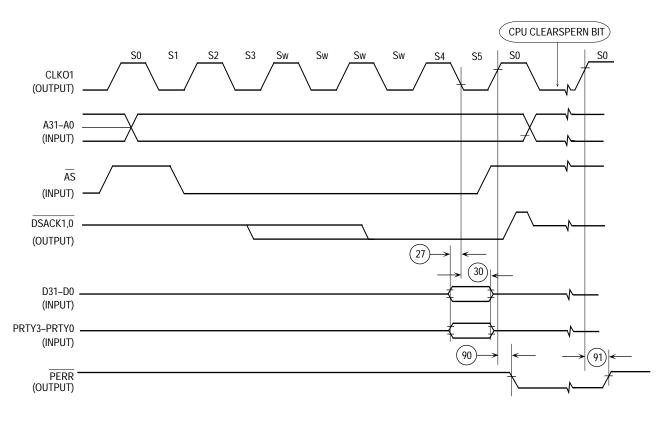

### Figure 10-38. External MC68030/MC68360 Parity Bits Timing Diagram

# 10.15 040 BUS TYPE SLAVE MODE BUS ARBITRATION AC ELECTRICAL SPECIFICATIONS

I

(The electrical specifications in this document are preliminary. See Figure 10-39)

|                  |                                                           | 3.3 V c | or 5.0 V | 5.    | Unit |    |

|------------------|-----------------------------------------------------------|---------|----------|-------|------|----|

| Num.             | Characteristic                                            | 25.0    | MHz      | 33.34 |      |    |

|                  |                                                           | Min     | Max      | Min   | Max  |    |

| 231              | Address, Transfer Attributes High Impedance to Clock High | 7       | —        | 6     | —    | ns |

| 232 <sup>1</sup> | Clock High to BG Low                                      | —       | 20       | —     | 15   | ns |

| 233              | Clock High to BG High                                     | 4       | 20       | 4     | 15   | ns |

| 234              | BB High to Clock High (040 output)                        | 7       | —        | 6     | —    | ns |

| 235              | BB High Impedance to Clock High (040 output)              | 0       | —        | 0     | —    | ns |

| 236              | Clock High to BB Low (360 output)                         | -       | 20       |       | 15   | ns |

| 237              | Clock High to BB High (360 output)                        | -       | 20       | —     | 15   | ns |

| 238              | Clock Low to BB High Impedance (360 output)               | —       | 20       | _     | 15   | ns |

NOTES:

1. BG remains low until either the SDMA or the IDMA requests the external bus.

#### MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

# 11.3 PIN ASSIGNMENT-241-LEAD PIN GRID ARRAY (PGA)

| т | O<br>PA15  | O<br>PA12 | O<br>PA9  | O<br>PA6             | O<br>PA3   | O<br>PA2  | O<br>PB17 | O<br>PB15 | O<br>PB12 | O<br>PB11 | O<br>PB8 | O<br>PB5 | O<br>PB2        | O<br>PC11               | O<br>PC9               | O<br>PC6                       | O<br>PC5                       | O<br>PC2                      |

|---|------------|-----------|-----------|----------------------|------------|-----------|-----------|-----------|-----------|-----------|----------|----------|-----------------|-------------------------|------------------------|--------------------------------|--------------------------------|-------------------------------|

| S | O<br>D2    | O<br>D0   | O<br>PA13 | O<br>PA10            | O<br>PA7   | O<br>PA5  | O<br>PA1  | O<br>PB16 | O<br>PB13 | O<br>PB10 | O<br>PB7 | O<br>PB4 | O<br>PB1        | O<br>PC10               | O<br>PC7               | O<br>PC3                       | O<br>PC1                       | O<br>IRQ2                     |

| R | O<br>D4    | ()<br>D3  | ()<br>D1  | O<br>PA14            | O<br>PA11  | O<br>PA8  | O<br>PA4  | O<br>PA0  | )<br>PB14 | )<br>PB9  | O<br>PB6 | O<br>PB3 | O<br>PB0        | O<br>PC8                | O<br>PC4               | O<br>PC0                       | $\frac{\bigcirc}{IRQ3}$        | O<br>IRQ1                     |

| Q | ()<br>D7   | )<br>D6   | O<br>D5   | O<br>GND             | )<br>GND   | )<br>GND  | )<br>Vcc  | )<br>Vcc  | )<br>GND  | )<br>GND  | ⊖<br>Vcc | ⊖<br>Vcc | )<br>GND        | )<br>GND                | )<br>GND               | $\frac{\bigcirc}{IRQ5}$        | $\frac{\bigcirc}{\text{BERR}}$ | O<br>RESETS                   |

| Ρ | )<br>D10   | ()<br>D9  | )<br>D8   | O<br>GND             | O<br>VCC   | )<br>GND  |           |           | O<br>NC   |           |          |          | O<br>Vcc        | )<br>GND                | )<br>GND               | $\frac{\bigcirc}{\text{HALT}}$ | $\frac{\bigcirc}{RMC}$         | O<br>PERR                     |

| N | ○<br>D13   | )<br>D12  | ()<br>D11 | O<br>GND             | )<br>GND   |           |           |           |           |           |          |          |                 | )<br>GND                | )<br>GND               | $\frac{\bigcirc}{AVEC}$        | )<br>TDO                       | O<br>TMS                      |

| М | ○<br>D16   | )<br>D15  | )<br>D14  | O<br>GND             |            |           |           |           |           |           |          |          |                 |                         | O<br>Vcc               | O<br>TD1                       | О<br>тск                       | O<br>RESETH                   |

| L | )<br>D19   | )<br>D18  | ()<br>D17 | ⊖<br>v <sub>cc</sub> |            |           |           |           |           |           |          |          |                 |                         | )<br>GND               | $\frac{\bigcirc}{TRST}$        | O<br>BKPT                      | O<br>IRQ6                     |

| К | O<br>CLKO2 | O<br>Vcc  | )<br>GND  |                      |            | LK        |           | MC        | 68360/N   | AC68EN    | 1360     |          |                 | ⊖<br>Vcc                | O<br>Vcc               | $\bigcirc$ IRQ4                | O<br>BGACH                     | $\overline{K} = \frac{O}{BG}$ |

| J | O<br>CLKO1 | ()<br>D20 | ()<br>D22 | )<br>GND             | O<br>Vcc   |           |           | (         | BOTTO     | M VIEV    | V)       |          |                 | O<br>GND                | )<br>GND               | O<br>IFETCH                    | O<br>NC1                       | $\frac{O}{BR}$                |

| Н | ○<br>D21   | ()<br>D23 | ()<br>D25 | O<br>GND             |            |           |           |           |           |           |          |          |                 |                         | O<br>GNDs2             | O<br>NC2                       |                                | O = OE                        |

| G | O<br>D24   | )<br>D26  | )<br>D28  | O<br>Vcc             |            |           |           |           |           |           |          |          |                 |                         | O<br>Vcc               | O<br>IPIPE0                    | $\frac{O}{AS}$                 | O<br>IPIPE1                   |

| F | O<br>D27   | )<br>D29  | )<br>D31  | O<br>GND             | )<br>GND   |           |           |           |           |           |          |          |                 | ⊖<br>Vcc                | )<br>GND               |                                | O<br>PRTY1                     | O<br>I PRTY0                  |

| E | )<br>D30   | O<br>FC3  | O<br>FC0  |                      | O<br>CCSYN | -         | -         |           | O<br>GND  | _         | _        | _        | O<br>Vcc        | O<br>GNDs1              | O<br>Vcc               | O<br>NC3                       | O<br>DSACK1                    | O<br>I PRTY3                  |

| D | O<br>FC2   | O<br>FC1  | ()<br>A30 | ⊖<br>XFC             | O<br>Vcc   | O<br>GND  | O<br>GND  | O<br>Vcc  | O<br>Vcc  | O<br>GND  | )<br>GND | O<br>GND | )<br>GND        | O<br>Vcc                | )<br>GND               | $\frac{O}{CAS0}$               | O<br>R/W                       | O<br>DSACK0                   |

| С | )<br>SIZ1  | ()<br>A29 |           | O<br>MODCK           |            | ()<br>A23 | )<br>A20  | ()<br>A17 | ○<br>A14  | ()<br>A8  | O<br>A4  | O<br>A0  | $\frac{O}{CS7}$ | $\frac{O}{CS4}$         | $\frac{O}{CS1}$        | $\frac{\bigcirc}{CAS3}$        | )<br>Freez                     | E DS                          |

| В | )<br>SIZO  |           |           | O<br>GND             | ()<br>A25  | ()<br>A22 | ()<br>A19 | ()<br>A16 | ()<br>A13 | ()<br>A10 | ()<br>A7 | ○<br>A5  | O<br>A1         | $\frac{\bigcirc}{IRQ7}$ | $\frac{\bigcirc}{CS5}$ | $\frac{\bigcirc}{CS2}$         | $\frac{\bigcirc}{CAS2}$        | O<br>CAS1                     |

| A |            | O<br>XTAL | O<br>NC3  | ○<br>A26             | ()<br>A24  | ()<br>A21 | ()<br>A18 | ()<br>A15 | ()<br>A12 | ()<br>A11 | ()<br>A9 | ()<br>A6 | O<br>A3         | ()<br>A2                |                        | $\frac{\bigcirc}{CS6}$         | $\frac{\bigcirc}{CS3}$         | CSO                           |

| L | 1          | 2         | 3         | 4                    | 5          | 6         | 7         | 8         | 9         | 10        | 11       | 12       | 13              | 14                      | 15                     | 16                             | 17                             | 18                            |

NOTE: Pin P9 "NC" is for guide purposes only.

PCDIR 7-369 PCPAR 7-369 PCSO 7-369 PEPAR 6-48, 9-11, 9-15, 9-49 Periodic Interrupt Request Level Encoding 6-37 Periodic Interrupt Timer 6-5, 6-10 **PICR 6-37** Pin Differences 6-26 PIP 7-332, 7-338, 7-341, 7-364 BUSY signal 7-335 Centronics 7-336 I/O Pins 7-333 Interlocked Data Transfers 7-333 Parallel Interface Port 7-331 PIP Block Diagram 7-332 Port B 7-333 Port B Pin Functions 7-363 Port B Registers 7-357, 7-365 Port E 6-23 Programming Model 7-338 Pulse Data Transfers 7-334 Pulsed Handshake Timing 7-336 PIP Block Diagram 7-332 **PIPC 7-339** PIPE 7-341 **PIPM 7-342** PIT 6-10 **PITR 6-38** PLL 6-14 PLL Power Pins 6-19 PLLCR 6-12, 6-40 Port A 7-359 Port A Examples 7-361 Port A Registers 7-360 Port B 7-333 Port B Example 7-366 Port B Pin Functions 7-363 Port B Registers 7-357, 7-365 Port C Registers 7-368 Port D 6-22 Port E 6-23 Port Sizes 4-8 Postincrement 5-5, 5-12 Power-On Reset 9-3 Predecrement 5-5, 5-12 Prefetch Controller 5-84

Prefetch Faults 5-51 Priority of the RISC 7-3 Privilege Violation 5-56 **PROFIBUS C-6** Profibus 7-142 **Program Control Instructions 5-24** Program Counter 5-2, 5-56, 5-58, 9-13 Programmer's Model 6-27 Programming Model 6-64, 7-317, 7-338 Programming SI RAM Entries 7-72 Programming the BISYNC Controller 7-217 Promiscuous 7-220, 7-257 **PRTY 2-6** PSMR 7-120, 7-156, 7-175, 7-178, 7-210, 7-228.7-256 PSMR Programming 7-196, 7-200 PTPR 7-341 Pulse Data Transfers 7-334 Pulsed Handshake Timing 7-336

## Q

- Q.921 A-1

- QUad Integrated Communication Controller 1-1, 9 QUADS B-6 QUICC AppleTalk Hardware Connection 7-198 QUICC Block Diagram 1-4, 11 QUICC Ethernet Serial CAM Interface 7-244 QUICC Functional Signal Groups 2-2 QUICC Internal Clock Signals 6-15 QUICC Interrupt Structure 7-372 QUICC Key Features 1-1 QUICC Memory Map 3-1, 3-2, 6-4 QUICC System Configuration 6-55

### R

R/W 4-3 R/W Field 5-68 RA 2-10 RAM DRAM Banks 6-58 SI RAM 7-68 SPI Parameter RAM Memory Map 7-320 SRAM Banks 6-56

TRST 2-12 TS 6-27, 6-60, 6-63, 6-68, 9-32 TXD 7-101, 7-358 VCC 2-13 **VCCCLK 6-19** VCCSYN 2-13, 6-19 WE 2-9, 4-27, 6-48 WE3-WE0 2-1 XFC 2-11, 6-19 XTAL 2-10, 2-11 SIM (System Integration Module) Breakpoint Logic 6-20 Bus Monitor 6-4, 6-8 Clock Generation 6-12 CSNT40 6-73 **CSNTQ 6-73 Double Bus Fault Monitor 6-4 DRAM Controller Overview 6-58** External Bus Interface Control 6-21 Freeze Support 6-11 General-Purpose Chip-Select Overview 6-56 Interrupt Generation 6-6 Interrupt Structure 6-7 Low Power in Normal Operation 6-12 Low-Power Stop 6-11 **MBAR 6-1** Memory Controller 6-50 **Option Register 6-74** Periodic Interrupt Timer 6-5, 6-10 Programming Model 6-64 **QUICC** Internal clock signals 6-15 QUICC Memory Map 6-4 **QUICC System Configuration 6-55 Reset Status 6-3** SIM40 6-1 Simultaneous SIM60 Interrupt Sources 6-8 Slave (Disable CPU32+) Mode 6-23 Software Watchdog Timer 6-5 Spurious Interrupt Monitor 6-5, 6-8 System Configuration 6-5 System Configuration and Protection 6-3 **TRLXQ 6-74** SIM40 6-1 SIM60 1-5, 4-20, 6-1, 6-12 SIMCLK 6-18

SIMODE 7-78 Simple Driver Module B-2 Simultaneous SIM60 Interrupt Sources 6-8 Single Address Mode 7-48 Single Address Transfer Example 7-48 Single Buffer 7-34 SIRP 7-88 **SISTR 7-87** SIZ 2-8, 4-3, 4-8, 4-25 Slave 7-314 Slave Disable CPU32+) Mode 6-23 Slave Mode 2-14, 7-316 BR 9-50 Burst EPROM 9-38 Burst SRAM 9-41 Bus Arbitration 4-55, 9-35 Bus Clear 6-25 **Bus Exceptions 4-59** Cache Modes on the MC68EC040 9-51 Disable CPU32+ 6-23 **DRAM Devices 9-46 DRAM SIMM 9-45 EEPROM 9-45 EPROM 9-38** Flash EPROM 9-41 Global Chip Select 6-25 GMR 9-49 Interfacing Multiple QUICCs to an MC68EC040 9-51 Interrupts 6-26, 9-34 MC68EC040 to QUICC Interface 9-32 Memory Interfaces 9-37 OR 9-50 **PEPAR 9-49** Pin Differences 6-26 Reset Strategy 9-34 Software Configuration 9-48 **SRAM 9-41** Strategy 9-34 Slave Mode 6-26, 9-31 SMC 7-99, 7-103, 7-276, 7-291, 7-305, A-2 C/I Channel 7-307 C/I Channel Receive Buffer Descriptor 7-310 C/I Channel Transmit Buffer 7-311 Character Length 7-282, 7-298 Commands in GCI Mode 7-307

MC68356 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com