Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

Application enacific microcontrollers are engineered to

| Details                 |                                                                                |

|-------------------------|--------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                       |

| Applications            | Touchscreen Controller                                                         |

| Core Processor          | M8C                                                                            |

| Program Memory Type     | FLASH (16kB)                                                                   |

| Controller Series       | CY8CT                                                                          |

| RAM Size                | 2K x 8                                                                         |

| Interface               | I <sup>2</sup> C, SPI, UART/USART, USB                                         |

| Number of I/O           | 28                                                                             |

| Voltage - Supply        | 1.8V                                                                           |

| Operating Temperature   | -40°C ~ 85°C                                                                   |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 32-VFQFN Exposed Pad                                                           |

| Supplier Device Package | 32-QFN                                                                         |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8ctmg201a-32lqxit |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 213.47 STK_PP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |      | 21.3.46 CUR PP    | 234 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-------------------|-----|

| 213.48 IDX_PP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |      | <b>-</b>          |     |

| 213.49 MVR_PP       238         213.51 I2C_CFG       239         213.52 I2C_SCR       240         213.52 I2C_DR       241         213.52 I2C_DR       241         213.54 INT_CLR0       242         213.55 INT_CLR1       244         213.56 INT_CLR2       246         213.57 INT_MSK2       248         213.59 INT_MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.62 INT_MSK0       250         213.63 CPU_F       254         213.64 IDAC_D       256         213.65 CPU_SCR1       257         213.66 CPU_SCR0       258         214 Bank1 Registers       259         214.1 PRIXDM0       259         214.2 PRIXDM1       260         214.3 SPLCFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 PWAC       265         214.8 TMP_DRx       266         214.9 USB_MSC_CR       265         214.10 OUT_PO       268         214.11 OC_FG1       277         214.12 OV_T_CR       277 <th></th> <th></th> <th>21.3.48 IDX PP</th> <th>236</th>                                                                                                                                                                                                   |            |      | 21.3.48 IDX PP    | 236 |

| 213.50 MWV PP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |      | <del>-</del>      |     |

| 21.3.51 I2C_CFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | <del>-</del>      |     |

| 213.55 IZC_DR 241 213.54 INT_CLR0 242 213.55 INT_CLR1 244 213.56 INT_CLR2 246 213.57 INT_MSK2 248 213.56 INT_KSK1 249 213.59 INT_MSK0 250 213.59 INT_MSK0 250 213.60 INT_SW_EN 251 213.61 INT_VC 252 213.62 RES_WDT 253 213.63 CPU_F 254 213.64 IDAC_D 256 213.65 CPU_SCR1 257 213.66 CPU_SCR0 258 214 Bank 1 Registers 259 214.1 PRTxDM0 259 214.2 PRTxDM1 260 214.3 SPL_CFG 261 214.4 USB_CR1 262 214.5 PMAx_WA 263 214.6 PMAx_RA 264 214.7 EPx_CR0 265 214.9 USB_MISC_CR 267 214.10 UST_PO 268 214.11 ECO_ENBUS 269 214.12 ECO_TRIM 270 214.13 IND_CRX 270 214.14 IO_CFG1 277 214.14 IO_CFG1 277 214.14 IO_CFG1 277 214.15 OUT_PO 268 214.15 OUT_PO 276 214.15 OUT_PO 276 214.19 USB_MISC_CR 277 214.10 OC_CR0 277 214.12 USL_DCFG 276 214.22 IND_TR 288 214.22 IND_TR 279 214.22 IND_TR 279 214.22 IND_TR 279 214.22 IND_TR 288 214.23 IND_TR 288 214.24 SIP_CFG 288 214.25 SIP_CFG2 288 214.25 SIP_CFG2 288 214.25 SIP_CFG3 285 214.27 IMO_TR1 286  Section F: Glossary |            |      |                   |     |

| 213.54 INT_CLR0       242         213.55 INT_CLR1       244         213.55 INT_CLR2       246         213.57 INT_MSK2       248         213.58 INT_MSK0       249         213.59 INT_MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.63 INT_SW_EN       251         213.63 INT_SW_EN       253         213.63 CPU_F       254         213.64 IDAC_D       256         213.65 CPU_SCR1       257         213.66 CPU_SCR0       258         214.1 PRIXDMO       259         214.1 PRIXDMO       259         214.2 PRIXDM1       260         214.3 SPI_CFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 EPX_CR0       265         214.8 TMP_DRx       266         214.9 USB_MISC_CR       267         214.10 UOT_P0       268         214.11 ECO_TRIM       270         214.12 ECO_TRIM       270         214.13 MUX_CRX       271         214.14 IO_CFG1       272         214.19 OC_FG2       275                                                                                                                                                                                                                                                    |            |      | 21.3.52 I2C_SCR   | 240 |

| 213.55 INT_CLR1       244         213.56 INT_CLR2       248         213.57 INT_MSK2       248         213.58 INT_MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.62 RES_WDT       253         213.63 CPU_F       254         213.66 CPU_SCR1       257         213.66 CPU_SCR1       257         213.66 CPU_SCR0       258         214 Bank 1 Registers       259         214.1 PRTXDM0       259         214.2 PRTXDM1       260         214.3 SPL_CFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 EPx_CR0       265         214.8 TMP_DRX       266         214.9 USB_MISC_CR       267         214.10 OUT_P0       268         214.11 ECO_ENBUS       269         214.12 ECO_TRIM       270         214.13 MUX_CRX       271         214.14 O.CFG1       272         214.15 OUT_P1       273         214.16 O_CFG2       275         214.17 OSC_CR0       276         214.18 ECO_CFGG       275 <th></th> <th></th> <th>21.3.53 I2C_DR</th> <th>241</th>                                                                                                                                                                                        |            |      | 21.3.53 I2C_DR    | 241 |

| 213.56 INT_CLR2       246         213.57 INT_MSK2       248         213.58 INT_MSK1       249         213.59 INT_MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.62 RES_WDT       253         213.63 CPU_F       253         213.64 IDAC_D       256         213.65 CPU_SCR1       257         213.66 CPU_SCR0       258         214 Bank 1 Registers       259         214.1 PRTXDM0       259         214.2 PRTxDM1       260         214.3 SPI_CFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 EPX_CR0       265         214.8 TMP_DRX       266         214.9 USB_MISC_CR       267         214.10 OUT_PO       268         214.11 ECO_ENBUS       269         214.12 ECO_TRIM       270         214.13 MUX_CRx       271         214.14 IO_CFG1       272         214.18 ECO_CFG       275         214.19 OSC_CR2       275         214.19 OSC_CR2       275         214.19 OSC_CR2       276 <th></th> <th></th> <th>21.3.54 INT_CLR0</th> <th>242</th>                                                                                                                                                                                      |            |      | 21.3.54 INT_CLR0  | 242 |

| 213.57 INT MSK1       248         213.58 INT_MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.62 RES_WDT       253         213.63 CPU_F       254         213.63 LDAC D       256         213.65 CPU_SCR1       257         213.66 CPU_SCR0       258         214 Bank 1 Registers       259         214.1 PRTXDM0       259         214.2 PRTXDM1       260         214.3 SPI_CFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 EPx_CR0       265         214.8 TMP_DRX       266         214.9 USB_MISC_CR       267         214.10 OUT_PO       268         214.11 ECO_ENBUS       269         214.12 ECO_TRIM       270         214.13 MUX_CRX       271         214.15 OUT_P1       273         214.16 IO_CFG1       277         214.19 OSC_CRO       275         214.19 OSC_CRO       275         214.19 OSC_CRO       276         214.19 OSC_CRO       276         214.19 OSC_CRO       277                                                                                                                                                                                                                                                    |            |      | 21.3.55 INT_CLR1  | 244 |

| 213.58 INT_MSK0       250         213.59 INT_MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.62 RES_WDT       253         213.63 CPU_F       254         213.64 IDAC_D       256         213.65 CPU_SCR1       257         213.66 CPU_SCR0       258         214 Bank 1 Registers       259         214.1 PRTxDM0       259         214.2 PRTxDM1       260         214.3 SPI_CFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 EPX_CR0       265         214.8 TMP_DRx       266         214.9 USB_MISC_CR       267         214.10 OUT_P0       288         214.11 ECO_ENBUS       269         214.12 ECO_TRIM       270         214.13 MUX_CRx       271         214.19 OUT_P1       273         214.19 OSC_CR0       275         214.19 OSC_CR0       276         214.19 GO_CFG2       277         214.19 GO_CFG2       278         214.21 WIT_CR       279         214.22 IMO_TR       280                                                                                                                                                                                                                                                      |            |      | 21.3.56 INT_CLR2  | 246 |

| 213.59 INT MSK0       250         213.60 INT_SW_EN       251         213.61 INT_VC       252         213.62 RES_WDT       253         213.63 CPU_F       254         213.64 IDAC_D       256         213.65 CPU_SCR0       256         213.66 CPU_SCR0       258         214.8 Bank 1 Registers       259         214.1 PRTXDM0       259         214.2 PRTXDM1       250         214.3 SPI_CFG       261         214.4 USB_CR1       262         214.5 PMAx_WA       263         214.6 PMAx_RA       264         214.7 EPx_CR0       265         214.8 TMP_DRx       266         214.9 USB_MISC_CR       267         214.10 OUT_PO       268         214.11 ECO_ENBUS       269         214.12 ECO_TRIM       270         214.13 MUX_CRX       271         214.14 IO_CFG1       272         214.15 OUT_P1       273         214.16 IO_CFG2       275         214.17 OSC_CR0       276         214.18 ECO_CFG       277         214.19 OSC_CR2       278         214.21 VLT_CMP       280         214.22 IMO_TR       281                                                                                                                                                                                                                                                    |            |      | 21.3.57 INT_MSK2  | 248 |

| 21.3.60 INT_WC       251         21.3.61 INT_VC       252         21.3.62 RES_WDT       253         21.3.63 CPU_F       254         21.3.65 CPU_SCR1       256         21.3.65 CPU_SCR0       258         21.4.86 CPU_SCR0       258         21.4.1 PRTXDM0       259         21.4.2 PRTXDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPX_CR0       265         21.4.8 TMP_DRX       266         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.19 OSC_CR0       276         21.4.19 OSC_CR2       275         21.4.19 OSC_CR2       275         21.4.19 OSC_CR2       275         21.4.19 OSC_CR2       278         21.4.21 WT_CRP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR                                                                                                                                                                                                                                               |            |      | 21.3.58 INT_MSK1  | 249 |

| 21.361 INT_VC       252         21.362 RES_WDT       253         21.363 CPU_F       254         21.364 IDAC_D       256         21.365 CPU_SCR0       258         21.366 CPU_SCR0       258         21.4 Bank 1 Registers       259         21.4.1 PRTXDM0       259         21.4.2 PRTXDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.19 OSC_CR2       276         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG3       285         21.4.27 IMO_TR1                                                                                                                                                                                                                                              |            |      | 21.3.59 INT_MSK0  | 250 |

| 21,362 RES_WDT       253         21,363 CPU_F       254         21,364 IDAC_D       256         21,365 CPU_SCR1       257         21,366 CPU_SCR0       258         21.4 Bank 1 Registers       259         21.4.1 PRTxDM0       259         21.4.2 PRTXDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPX_CR0       265         21.4.8 TMP_DRX       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.19 OSC_CR2       278         21.4.20 IVT_CR       280         21.4.21 WIT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3 <th></th> <th></th> <th>21.3.60 INT_SW_EN</th> <th>251</th>                                                                                                                                                                             |            |      | 21.3.60 INT_SW_EN | 251 |

| 21.3.63 CPU_F       254         21.3.65 CPU_SCR1       256         21.3.65 CPU_SCR0       258         21.4 Bank 1 Registers       259         21.4.1 PRTxDM0       259         21.4.1 PRTxDM1       260         21.4.2 PRTxDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_WA       263         21.4.8 TMP_DRx       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_PO       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.18 ECO_CFG       276         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.25 SLP_CFG2       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286                                                                                                                                                                                                                                                          |            |      | 21.3.61 INT_VC    | 252 |

| 21.3.64 IDAC_D       256         21.3.65 CPU_SCR1       257         21.3.66 CPU_SCR0       258         21.4 Bank 1 Registers       259         21.4.1 PRTxDM0       259         21.4.2 PRTxDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAX_WA       263         21.4.6 PMAX_RA       264         21.4.7 EPX_CR0       265         21.4.8 TMP_DRX       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       275         21.4.19 OSC_CR2       275         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 IWO_TR       280         21.4.22 IMO_TR       281         21.4.25 SLP_CFG2       284         21.4.25 SLP_CFG3       285         21.4.27 IMO_TR1       286                                                                                                                                                                                                                                                          |            |      | 21.3.62 RES_WDT   | 253 |

| 21.3.65 CPU_SCR1       257         21.3.66 CPU_SCR0       258         21.4 Bank 1 Registers       259         21.4.1 PRTxDM0       259         21.4.2 PRTxDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 UOT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 O_CFG2       275         21.4.18 ECO_CFG       276         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286                                                                                                                                                                                                                                                                                           |            |      | 21.3.63 CPU_F     | 254 |

| 21.4 Bank 1 Registers       259         21.4.1 PRTxDM0       259         21.4.2 PRTxDM1       260         21.4.3 SPL CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 WLT_CMP       280         21.4.22 ILO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG2       283         21.4.25 SLP_CFG3       283         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                |            |      | 21.3.64 IDAC_D    | 256 |

| 21.4 Bank 1 Registers       259         21.4.1 PRTXDM0       259         21.4.2 PRTXDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAX_WA       263         21.4.6 PMAX_RA       264         21.4.7 EPX_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 IMO_TR       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                  |            |      | 21.3.65 CPU_SCR1  | 257 |

| 21.4.1 PRTxDM0       259         21.4.2 PRTxDM1       260         21.4.3 SPL_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.18 ECO_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR0       276         21.4.20 VLT_CR       279         21.4.21 INO_TR       280         21.4.23 ILO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG       283         21.4.26 SLP_CFG       283         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                  |            |      | 21.3.66 CPU_SCR0  | 258 |

| 21.4.2 PRTXDM1       260         21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAX_WA       263         21.4.6 PMAX_RA       264         21.4.7 EPX_CR0       265         21.4.8 TMP_DRX       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_OMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG       283         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                             | :          | 21.4 | Bank 1 Registers  | 259 |

| 21.4.3 SPI_CFG       261         21.4.4 USB_CR1       262         21.4.5 PMAX_WA       263         21.4.6 PMAX_RA       264         21.4.7 EPX_CR0       265         21.4.8 TMP_DRX       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.18 ECO_CFG       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG       283         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | 21.4.1 PRTxDM0    | 259 |

| 21.4.4 USB_CR1       262         21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | 21.4.2 PRTxDM1    | 260 |

| 21.4.5 PMAx_WA       263         21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.18 ECO_CFG       276         21.4.19 OSC_CR0       276         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 WLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG2       284         21.4.25 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |      | 21.4.3 SPI_CFG    | 261 |

| 21.4.6 PMAx_RA       264         21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG       283         21.4.25 SLP_CFGG       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | 21.4.4 USB_CR1    | 262 |

| 21.4.7 EPx_CR0       265         21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.25 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       284         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |      | 21.4.5 PMAx_WA    | 263 |

| 21.4.8 TMP_DRx       266         21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |      |                   |     |

| 21.4.9 USB_MISC_CR       267         21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |      |                   |     |

| 21.4.10 OUT_P0       268         21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       281         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      | <del>-</del>      |     |

| 21.4.11 ECO_ENBUS       269         21.4.12 ECO_TRIM       270         21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |      |                   |     |

| 21.4.12 ECO_TRIM       270         21.4.13 MUX_CRX       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |      | <del>-</del>      |     |

| 21.4.13 MUX_CRx       271         21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |      |                   |     |

| 21.4.14 IO_CFG1       272         21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |      |                   |     |

| 21.4.15 OUT_P1       273         21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |      | <del>-</del>      |     |

| 21.4.16 IO_CFG2       275         21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 IVLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |      |                   |     |

| 21.4.17 OSC_CR0       276         21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |      | <b>-</b>          |     |

| 21.4.18 ECO_CFG       277         21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |      | <del>-</del>      |     |

| 21.4.19 OSC_CR2       278         21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | <b>-</b>          |     |

| 21.4.20 VLT_CR       279         21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286            Section F: Glossary       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | <b>–</b>          |     |

| 21.4.21 VLT_CMP       280         21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |      | <b>-</b>          |     |

| 21.4.22 IMO_TR       281         21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286    Section F: Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |      |                   |     |

| 21.4.23 ILO_TR       282         21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |      | <b>-</b>          |     |

| 21.4.24 SLP_CFG       283         21.4.25 SLP_CFG2       284         21.4.26 SLP_CFG3       285         21.4.27 IMO_TR1       286         Section F: Glossary       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      | <b>–</b>          |     |

| 21.4.25 SLP_CFG2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |      | <b>—</b>          |     |

| 21.4.26 SLP_CFG3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |      | <b>=</b>          |     |

| 21.4.27 IMO_TR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |      | <b>=</b>          |     |

| Section F: Glossary 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |      | <b>–</b>          |     |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |      | 21.4.27 INIO_1R1  | 286 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Section F: | Glo  | ssarv             | 287 |

| ***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |      | •                 |     |

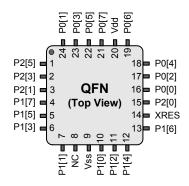

# 1.1.2 CY8CTMG200-24LQXI, CY8CTMG200A-24LQXI, CY8CTST200-24LQXI, CY8CTST200A-24LQXI PSoC 24-Pin Part Pinout

Table 1-2. 24-Pin QFN Part Pinout \*\*

| Pin | Ту      | pe     | Name  | Description                                        |

|-----|---------|--------|-------|----------------------------------------------------|

| No. | Digital | Analog | Name  | Description                                        |

| 1   | Ю       | I      | P2[5] | XTAL Out                                           |

| 2   | 10      | I      | P2[3] | XTAL In                                            |

| 3   | 10      | I      | P2[1] |                                                    |

| 4   | IOHR    | ı      | P1[7] | I2C SCL, SPI SS                                    |

| 5   | IOHR    | I      | P1[5] | I2C SDA, SPI MISO                                  |

| 6   | IOHR    | I      | P1[3] | SPI CLK                                            |

| 7   | IOHR    | I      | P1[1] | TC CLK*, I2C SCL, SPI MOSI                         |

| 8   |         |        | NC    | No connection                                      |

| 9   | Pov     | wer    | Vss   | Ground pin                                         |

| 10  | IOHR    | I      | P1[0] | TC DATA*, I2C SDA, SPI CLK                         |

| 11  | IOHR    | I      | P1[2] |                                                    |

| 12  | IOHR    | I      | P1[4] | EXTCLK                                             |

| 13  | IOHR    | I      | P1[6] |                                                    |

| 14  | Inp     | out    | XRES  | Active high external reset with internal pull down |

| 15  | Ю       | I      | P2[0] |                                                    |

| 16  | IOH     | I      | P0[0] |                                                    |

| 17  | IOH     | I      | P0[2] |                                                    |

| 18  | IOH     | I      | P0[4] |                                                    |

| 19  | IOH     | I      | P0[6] |                                                    |

| 20  | Pov     | wer    | Vdd   | Power pin                                          |

| 21  | IOH     | I      | P0[7] |                                                    |

| 22  | IOH     | I      | P0[5] |                                                    |

| 23  | IOH     | I      | P0[3] | Integrating input                                  |

| 24  | IOH     | I      | P0[1] | Integrating input                                  |

#### CY8CTMG200-24LQXI, CY8CTMG200A-24LQXI, CY8CTST200-24LQXI, CY8CTST200-24LQXI PSoC Device

**LEGEND** A = Analog, I = Input, O = Output, H = 5 mA High Output Drive, R = Regulated Output Option.

- \* These are the ISSP pins, which are not High Z at POR (Power On Reset).

- \*\* The center pad on the QFN package must be connected to ground (Vss) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

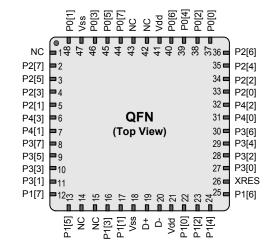

# 1.1.4 CY8CTMG200-48LTXI, CY8CTMG200A-48LTXI, CY8CTST200-48LTXI, CY8CTST200A-48LTXI, CY8CTMG201-48LTXI, CY8CTMG201A-48LTXI PSoC 48-Pin Part Pinout

Table 1-4. 48-Pin Part Pinout \*\*

| iabi       | Table 1-4. 40-1 III I alt i illout |        |       |                                                    |  |  |  |  |

|------------|------------------------------------|--------|-------|----------------------------------------------------|--|--|--|--|

| Pin<br>No. | Digital                            | Analog | Name  | Description                                        |  |  |  |  |

| 1          |                                    |        | NC    | No connection                                      |  |  |  |  |

| 2          | Ю                                  | ı      | P2[7] |                                                    |  |  |  |  |

| 3          | Ю                                  | ı      | P2[5] | XTAL Out                                           |  |  |  |  |

| 4          | Ю                                  | I      | P2[3] | XTAL In                                            |  |  |  |  |

| 5          | Ю                                  | I      | P2[1] |                                                    |  |  |  |  |

| 6          | Ю                                  | ı      | P4[3] |                                                    |  |  |  |  |

| 7          | Ю                                  | ı      | P4[1] |                                                    |  |  |  |  |

| 8          | Ю                                  | I      | P3[7] |                                                    |  |  |  |  |

| 9          | Ю                                  | ı      | P3[5] |                                                    |  |  |  |  |

| 10         | Ю                                  | ı      | P3[3] |                                                    |  |  |  |  |

| 11         | Ю                                  | ı      | P3[1] |                                                    |  |  |  |  |

| 12         | IOHR                               | ı      | P1[7] | I2C SCL, SPI SS                                    |  |  |  |  |

| 13         | IOHR                               | ı      | P1[5] | I2C SDA, SPI MISO                                  |  |  |  |  |

| 14         |                                    |        | NC    | No connection                                      |  |  |  |  |

| 15         |                                    |        | NC    | No connection                                      |  |  |  |  |

| 16         | IOHR                               | ı      | P1[3] | SPI CLK                                            |  |  |  |  |

| 17         | IOHR                               | ı      | P1[1] | TC CLK*, I2C SCL, SPI MOSI                         |  |  |  |  |

| 18         | Pov                                | ver    | Vss   | Ground pin                                         |  |  |  |  |

| 19         | Ю                                  |        | D +   | USB PHY                                            |  |  |  |  |

| 20         | Ю                                  |        | D -   | USB PHY                                            |  |  |  |  |

| 21         | Pov                                | ver    | Vdd   | Power pin                                          |  |  |  |  |

| 22         | IOHR                               | ı      | P1[0] | TC DATA*, I2C SDA, SPI CLK                         |  |  |  |  |

| 23         | IOHR                               | -      | P1[2] |                                                    |  |  |  |  |

| 24         | IOHR                               | -      | P1[4] | EXTCLK                                             |  |  |  |  |

| 25         | IOHR                               | ı      | P1[6] |                                                    |  |  |  |  |

| 26         | Inp                                | ut     | XRES  | Active high external reset with internal pull down |  |  |  |  |

| 27         | 10                                 | -      | P3[0] |                                                    |  |  |  |  |

| 28         | 10                                 | ı      | P3[2] |                                                    |  |  |  |  |

| 29         | 10                                 | ı      | P3[4] |                                                    |  |  |  |  |

| 30         | 10                                 | ı      | P3[6] |                                                    |  |  |  |  |

CY8CTMG200-48LTXI, CY8CTMG200A-48LTXI, CY8CTST200-48LTXI, CY8CTST200A-48LTXI, CY8CTMG201-48LTXI PSoC Devices

| 29 | Ю   | I | P3[4] |            |          |                  |       |                   |

|----|-----|---|-------|------------|----------|------------------|-------|-------------------|

| 30 | Ю   | I | P3[6] | -          | Pin ital |                  |       |                   |

| 31 | Ю   | ı | P4[0] | Pin<br>No. | Digit    | Analog           | Name  | Description       |

| 32 | 0   | - | P4[2] |            | a        | Ā                |       |                   |

| 33 | Ю   | ı | P2[0] | 41         | Pov      | wer              | Vdd   | Power pin         |

| 34 | Ю   | ı | P2[2] | 42         |          | NC No connection |       | No connection     |

| 35 | Ю   | ı | P2[4] | 43         |          |                  | NC    | No connection     |

| 36 | Ю   | ı | P2[6] | 44         | IOH      | I                | P0[7] |                   |

| 37 | IOH | ı | P0[0] | 45         | IOH      | ı                | P0[5] |                   |

| 38 | IOH | ı | P0[2] | 46         | IOH      | ı                | P0[3] | Integrating input |

| 39 | IOH | I | P0[4] | 47         | Pov      | wer              | Vss   | Ground pin        |

| 40 | IOH | ı | P0[6] | 48         | IOH      | ı                | P0[1] | Integrating input |

LEGEND A = Analog, I = Input, O = Output, NC = No Connection, H = 5 mA High Output Drive, R = Regulated Output Option.

<sup>\*</sup> ISSP pin which is not High Z at POR (Power On Reset).

<sup>\*\*</sup> The center pad on the QFN package must be connected to ground (Vss) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

with any value, all pending and posted interrupts are cleared by asserting the clear line for each interrupt.

For additional information, refer to the INT\_VC register on page 252.

# 5.3.9 Related Registers

■ CPU\_F on page 254.

#### 6.2.4 IO CFG1 Register

| Address | Name    | Bit 7   | Bit 6 | Bit 5 | Bit 4  | Bit 3           | Bit 2             | Bit 1  | Bit 0 | Access |

|---------|---------|---------|-------|-------|--------|-----------------|-------------------|--------|-------|--------|

| 1,DCh   | IO_CFG1 | StrongP |       | Rang  | e[1:0] | P1_LOW_<br>THRS | SPICLK_<br>ON_P10 | REG_EN | IOINT | RW:00  |

The Input/Output Configuration Register 1 (IO\_CFG1) configures the Port 1 output regulator and set the Interrupt mode for all GPIO.

**Bit 7: StrongP.** Setting this bit increases the drive strength and edge ratio for high outputs.