Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                     |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 24MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 24K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | •                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100rct6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 Description

The STM32F100xx value line family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 24 MHz frequency, high-speed embedded memories (Flash memory up to 512 Kbytes and SRAM up to 32 Kbytes), a flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more) and an extensive range of enhanced peripherals and I/Os connected to two APB buses. All devices offer standard communication interfaces (up to two I<sup>2</sup>Cs, three SPIs, one HDMI CEC, up to three USARTs and 2 UARTS), one 12-bit ADC, two 12-bit DACs, up to 9 general-purpose 16-bit timers and an advanced-control PWM timer.

The STM32F100xx high-density value line family operates in the –40 to +85 °C and –40 to +105 °C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F100xx value line family includes devices in three different packages ranging from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F100xx value line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

## 2.1 Device overview

|                          | Table 2. 51      |                                                                                                  |        |     |             |                    | Jounto  | 1           |     |     |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------|--------|-----|-------------|--------------------|---------|-------------|-----|-----|

| Peripheral               |                  | STM32F100Rx                                                                                      |        |     | STM32F100Vx |                    |         | STM32F100Zx |     |     |

| Flash - Kbytes           |                  | 256                                                                                              | 384    | 512 | 256         | 384                | 512     | 256         | 384 | 512 |

| SRAM - Kbytes            |                  | 24                                                                                               | 32     | 32  | 24          | 32                 | 32      | 24          | 32  | 32  |

| FSMC                     |                  |                                                                                                  | No     |     |             | Yes <sup>(1)</sup> |         |             | Yes |     |

| Timers                   | Advanced-control |                                                                                                  | 1      |     |             | 1                  |         |             | 1   |     |

| Timers                   | General-purpose  | 10                                                                                               |        |     |             | 10                 |         |             | 10  |     |

|                          | SPI              |                                                                                                  | 3      |     |             | 3                  |         |             | 3   |     |

|                          | l <sup>2</sup> C | 2                                                                                                |        |     | 2           |                    |         | 2           |     |     |

| Communication interfaces | USART            | 3                                                                                                |        |     | 3           |                    | 3       |             |     |     |

|                          | UART             | 2                                                                                                |        |     | 2           |                    | 2       |             |     |     |

|                          | CEC              | 1                                                                                                |        |     | 1           |                    | 1       |             |     |     |

| 12-bit synchroniz        |                  | 1                                                                                                |        |     | 1           |                    | 1       |             |     |     |

| number of chann          | els              | 16 channels                                                                                      |        |     | 16 channels |                    |         | 16 channels |     |     |

| GPIOs                    |                  | 51                                                                                               |        |     | 80          |                    | 112     |             |     |     |

| 12-bit DAC               |                  | 2                                                                                                |        |     | 2           |                    |         | 2           |     |     |

| Number of chann          | nels             | 2                                                                                                |        |     | 2           |                    |         | 2           |     |     |

| CPU frequency            |                  | 24 MHz                                                                                           |        |     |             |                    |         |             |     |     |

| Operating voltage        |                  | 2.0 to 3.6 V                                                                                     |        |     |             |                    |         |             |     |     |

| Operating temperatures   |                  | Ambient operating temperature: -40 to +85 °C /-40 to +10<br>Junction temperature: -40 to +125 °C |        |     |             | :o +105 °          | С       |             |     |     |

| Packages                 |                  |                                                                                                  | LQFP64 |     | LQFP100     |                    | LQFP144 |             |     |     |

## Table 2. STM32F100xx features and peripheral counts

1. For the LQFP100 package, only FSMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory.

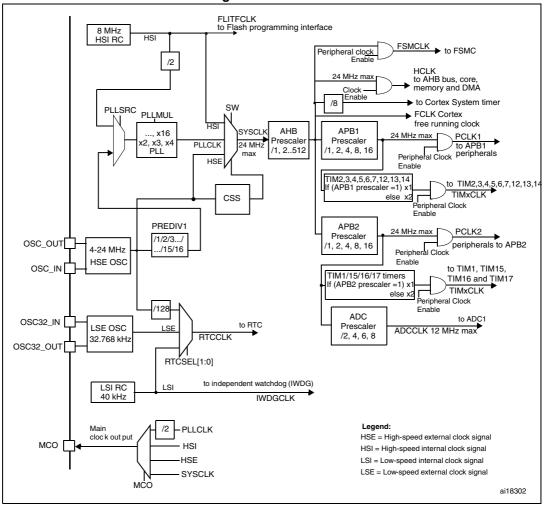

Figure 2. Clock tree

1. To obtain an ADC conversion time of 1.2  $\mu s,$  APB2 must be at 24 MHz.

|         | Pins    |        | <b>3</b>          |                     |                          |                                                  | Alternate function                                                                | ons <sup>(4)</sup>       |

|---------|---------|--------|-------------------|---------------------|--------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                           | Remap                    |

| 66      | 44      | -      | PE13              | I/O                 | FT                       | PE13                                             | FSMC_D10                                                                          | TIM1_CH3                 |

| 67      | 45      | -      | PE14              | I/O                 | FT                       | PE14                                             | FSMC_D11                                                                          | TIM1_CH4                 |

| 68      | 46      | -      | PE15              | I/O                 | FT                       | PE15                                             | FSMC_D12                                                                          | TIM1_BKIN                |

| 69      | 47      | 29     | PB10              | I/O                 | FT                       | PB10                                             | I2C2_SCL/USART3_TX <sup>(8)</sup>                                                 | TIM2_CH3 /<br>HDMI_CEC   |

| 70      | 48      | 30     | PB11              | I/O                 | FT                       | PB11                                             | I2C2_SDA/USART3_RX <sup>(8)</sup>                                                 | TIM2_CH4                 |

| 71      | 49      | 31     | V <sub>SS_1</sub> | S                   | -                        | V <sub>SS_1</sub>                                | -                                                                                 | -                        |

| 72      | 50      | 32     | V <sub>DD_1</sub> | S                   | -                        | V <sub>DD_1</sub>                                | -                                                                                 | -                        |

| 73      | 51      | 33     | PB12              | I/O                 | FT                       | PB12                                             | SPI2_NSS/<br>I2C2_SMBA/<br>USART3_CK <sup>(8)</sup> /<br>TIM1_BKIN <sup>(8)</sup> | TIM12_CH1                |

| 74      | 52      | 34     | PB13              | I/O                 | FT                       | PB13                                             | SPI2_SCK/<br>USART3_CTS <sup>(8)</sup> /<br>TIM1_CH1N                             | TIM12_CH2                |

| 75      | 53      | 35     | PB14              | I/O                 | FT                       | PB14                                             | SPI2_MISO/TIM1_CH2N<br>USART3_RTS <sup>(8)</sup> /                                | TIM15_CH1                |

| 76      | 54      | 36     | PB15              | I/O                 | FT                       | PB15                                             | SPI2_MOSI/<br>TIM1_CH3N <sup>(8)</sup> /<br>TIM15_CH1N                            | TIM15_CH2                |

| 77      | 55      | -      | PD8               | I/O                 | FT                       | PD8                                              | FSMC_D13                                                                          | USART3_TX                |

| 78      | 56      | -      | PD9               | I/O                 | FT                       | PD9                                              | FSMC_D14                                                                          | USART3_RX                |

| 79      | 57      | -      | PD10              | I/O                 | FT                       | PD10                                             | FSMC_D15                                                                          | USART3_CK                |

| 80      | 58      | -      | PD11              | I/O                 | FT                       | PD11                                             | FSMC_A16                                                                          | USART3_CTS               |

| 81      | 59      | -      | PD12              | I/O                 | FT                       | PD12                                             | FSMC_A17                                                                          | TIM4_CH1 /<br>USART3_RTS |

| 82      | 60      | -      | PD13              | I/O                 | FT                       | PD13                                             | FSMC_A18                                                                          | TIM4_CH2                 |

| 83      | -       | -      | V <sub>SS_8</sub> | S                   | -                        | V <sub>SS_8</sub>                                | -                                                                                 | -                        |

| 84      | -       | -      | V <sub>DD_8</sub> | S                   | -                        | $V_{DD_8}$                                       | -                                                                                 | -                        |

| 85      | 61      | -      | PD14              | I/O                 | FT                       | PD14                                             | FSMC_D0                                                                           | TIM4_CH3                 |

| 86      | 62      | -      | PD15              | I/O                 | FT                       | PD15                                             | FSMC_D1                                                                           | TIM4_CH4                 |

| 87      | -       | -      | PG2               | I/O                 | FT                       | PG2                                              | FSMC_A12                                                                          | -                        |

| 88      | -       | -      | PG3               | I/O                 | FT                       | PG3                                              | FSMC_A13                                                                          | -                        |

| 89      | -       | -      | PG4               | I/O                 | FT                       | PG4                                              | FSMC_A14                                                                          | -                        |

| 90      | -       | -      | PG5               | I/O                 | FT                       | PG5                                              | FSMC_A15                                                                          | -                        |

## Table 4. High-density STM32F100xx pin definitions (continued)

|         | Pins    |        |                    |                     |                          |                                                  | Alternate functions                                                           | ons <sup>(4)</sup>                     |

|---------|---------|--------|--------------------|---------------------|--------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name           | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                       | Remap                                  |

| 120     | -       | -      | V <sub>SS_10</sub> | S                   | -                        | V <sub>SS_10</sub>                               | -                                                                             | -                                      |

| 121     | -       | -      | $V_{DD_{10}}$      | S                   | -                        | $V_{DD_{10}}$                                    | -                                                                             | -                                      |

| 122     | 87      | -      | PD6                | I/O                 | FT                       | PD6                                              | FSMC_NWAIT                                                                    | USART2_RX                              |

| 123     | 88      | -      | PD7                | I/O                 | FT                       | PD7                                              | FSMC_NE1                                                                      | USART2_CK                              |

| 124     | -       | -      | PG9                | I/O                 | FT                       | PG9                                              | FSMC_NE2                                                                      | -                                      |

| 125     | -       | -      | PG10               | I/O                 | FT                       | PG10                                             | FSMC_NE3                                                                      | -                                      |

| 126     | -       | -      | PG11               | I/O                 | FT                       | PG11                                             | -                                                                             | -                                      |

| 127     | -       | -      | PG12               | I/O                 | FT                       | PG12                                             | FSMC_NE4                                                                      | -                                      |

| 128     | -       | -      | PG13               | I/O                 | FT                       | PG13                                             | FSMC_A24                                                                      | -                                      |

| 129     | -       | -      | PG14               | I/O                 | FT                       | PG14                                             | FSMC_A25                                                                      | -                                      |

| 130     | -       | -      | V <sub>SS_11</sub> | S                   | -                        | V <sub>SS_11</sub>                               | -                                                                             | -                                      |

| 131     | -       | -      | V <sub>DD_11</sub> | S                   | -                        | V <sub>DD_11</sub>                               | -                                                                             | -                                      |

| 132     | -       | -      | PG15               | I/O                 | FT                       | PG15                                             | -                                                                             | -                                      |

| 133     | 89      | 55     | PB3/               | I/O                 | FT                       | JTDO                                             | SPI3_SCK                                                                      | PB3/TRACESWO<br>TIM2_CH2 /<br>SPI1_SCK |

| 134     | 90      | 56     | PB4                | I/O                 | FT                       | NJTRST                                           | SPI3_MISO                                                                     | TIM3_CH1<br>SPI1_MISO                  |

| 135     | 91      | 57     | PB5                | I/O                 | -                        | PB5                                              | I2C1_SMBA/ SPI3_MOSI<br>TIM16_BKIN                                            | TIM3_CH2 /<br>SPI1_MOSI                |

| 136     | 92      | 58     | PB6                | I/O                 | FT                       | PB6                                              | I2C1_SCL <sup>(8)</sup> / TIM4_CH1 <sup>(8)</sup> /<br>TIM16_CH1N             | USART1_TX                              |

| 137     | 93      | 59     | PB7                | I/O                 | FT                       | PB7                                              | I2C1_SDA <sup>(8)</sup> / FSMC_NADV /<br>TIM4_CH2 <sup>(8)</sup> / TIM17_CH1N | USART1_RX                              |

| 138     | 94      | 60     | BOOT0              | Ι                   | -                        | BOOT0                                            | -                                                                             | -                                      |

| 139     | 95      | 61     | PB8                | I/O                 | FT                       | PB8                                              | TIM4_CH3 <sup>(8)</sup> /TIM16_CH1 /<br>HDMI_CEC                              | I2C1_SCL                               |

| 140     | 96      | 62     | PB9                | I/O                 | FT                       | PB9                                              | TIM4_CH4 <sup>(8)</sup> / TIM17_CH1                                           | I2C1_SDA                               |

| 141     | 97      | -      | PE0                | I/O                 | FT                       | PE0                                              | TIM4_ETR / FSMC_NBL0                                                          | -                                      |

| 142     | 98      | -      | PE1                | I/O                 | FT                       | PE1                                              | FSMC_NBL1                                                                     | -                                      |

| 143     | 99      | 63     | V <sub>SS_3</sub>  | S                   | -                        | V <sub>SS_3</sub>                                | -                                                                             | -                                      |

| 144     | 100     | 64     | V <sub>DD_3</sub>  | S                   | -                        | V <sub>DD_3</sub>                                | -                                                                             |                                        |

#### Table 4. High-density STM32F100xx pin definitions (continued)

1. I = input, O = output, S = supply.

2. FT = 5 V tolerant.

| Symbol         | Parameter                          | Conditions                           | Min | Мах | Unit |  |  |

|----------------|------------------------------------|--------------------------------------|-----|-----|------|--|--|

|                | Power dissipation at $T_A =$       | LQFP144                              | -   | 666 |      |  |  |

| P <sub>D</sub> | 85 °C for suffix 6 or $T_A =$      | LQFP100                              | -   | 434 | mW   |  |  |

|                | 105 °C for suffix 7 <sup>(2)</sup> | LQFP64                               | -   | 444 |      |  |  |

| ΤΑ             | Ambient temperature for 6          | Maximum power dissipation            | -40 | 85  | °C   |  |  |

|                | suffix version                     | Low power dissipation <sup>(3)</sup> | -40 | 105 | C    |  |  |

|                | Ambient temperature for 7          | Maximum power dissipation            | -40 | 105 | °C   |  |  |

|                | suffix version                     | Low power dissipation <sup>(3)</sup> | -40 | 125 | °C   |  |  |

| TJ             | lunction tomporature range         | 6 suffix version                     | -40 | 105 | °C   |  |  |

|                | Junction temperature range         | 7 suffix version                     | -40 | 125 | C    |  |  |

Table 9. General operating conditions (continued)

1. When the ADC is used, refer to *Table 51: ADC characteristics*.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_Jmax$  (see Section 6.5: Thermal characteristics on page 100).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Section 6.5: Thermal characteristics on page 100).

## 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for  $T_A$ .

| Table 10. Operating conditions at power-up / power-uown |                                |     |     |      |  |  |

|---------------------------------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol Parameter                                        |                                | Min | Мах | Unit |  |  |

| tunn                                                    | V <sub>DD</sub> rise time rate | 0   | 8   | us/V |  |  |

| tvdd                                                    | V <sub>DD</sub> fall time rate | 20  | ∞   | μ5/ν |  |  |

#### Table 10. Operating conditions at power-up / power-down

Note: It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation

|                                |                                                                                                                                                   |                                                                                                                                             | <u> </u>                                     |                                              | M                                            |                          |                            |      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------|----------------------------|------|

| Symbol                         | Parameter                                                                                                                                         | Conditions                                                                                                                                  | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.0 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.4 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 3.3 V | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit |

| Supply current<br>in Stop mode | Supply current                                                                                                                                    | Regulator in Run mode,<br>Low-speed and high-speed<br>internal RC oscillators and<br>high-speed oscillator OFF (no<br>independent watchdog) | -                                            | -                                            | 31                                           | 320                      | 670                        |      |

|                                | Regulator in Low-Power mode,<br>Low-speed and high-speed<br>internal RC oscillators and<br>high-speed oscillator OFF (no<br>independent watchdog) | -                                                                                                                                           | -                                            | 24                                           | 305                                          | 650                      |                            |      |

| I <sub>DD</sub>                | I <sub>DD</sub><br>Supply current<br>in Standby<br>mode                                                                                           | Low-speed internal RC<br>oscillator and independent<br>watchdog ON                                                                          | -                                            | -                                            | 3.2                                          | -                        | -                          | μA   |

| in                             |                                                                                                                                                   | Low-speed internal RC<br>oscillator ON, independent<br>watchdog OFF                                                                         | -                                            | -                                            | 3.1                                          | -                        | -                          |      |

|                                |                                                                                                                                                   | Low-speed internal RC<br>oscillator and independent<br>watchdog OFF, low-speed<br>oscillator and RTC OFF                                    | -                                            | -                                            | 2.2                                          | 3.9                      | 5.7                        |      |

| I <sub>DD_VBAT</sub>           | Backup<br>domain supply<br>current                                                                                                                | Low-speed oscillator and RTC<br>ON                                                                                                          | 1.0                                          | 1.2                                          | 1.4                                          | 2                        | 2.3                        |      |

1. Typical values are measured at  $T_A = 25$  °C.

## Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled except if it is explicitly mentioned

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

The parameters given in *Table 17* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6.

| Pe                | ripheral                 | Typical consumption at 25 °C | Unit   |

|-------------------|--------------------------|------------------------------|--------|

|                   | DMA1                     | 12.50                        |        |

|                   | DMA2                     | 8.33                         |        |

| AHB (up to 24MHz) | FSMC                     | 28.33                        | µA/MHz |

|                   | CRC                      | 1.25                         |        |

|                   | BusMatrix <sup>(1)</sup> | 16.67                        |        |

#### Table 19. Peripheral current consumption

#### Wakeup time from low-power mode

The wakeup times given in *Table 26* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| t (1)                               | Wakeup from Stop mode (regulator in run mode)       | 3.6 | 110  |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  | μs   |

Table 26. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

## 5.3.8 PLL characteristics

The parameters given in *Table 27* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol               | Parameter                      |                    | Unit |                    |      |

|----------------------|--------------------------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| £                    | PLL input clock <sup>(2)</sup> | 1                  | 8.0  | 24                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40                 | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -    | 24                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | -    | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | -    | 300                | ps   |

#### Table 27. PLL characteristics

1. Based on device characterization, not tested in production.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL\_OUT}$ .

### 5.3.9 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

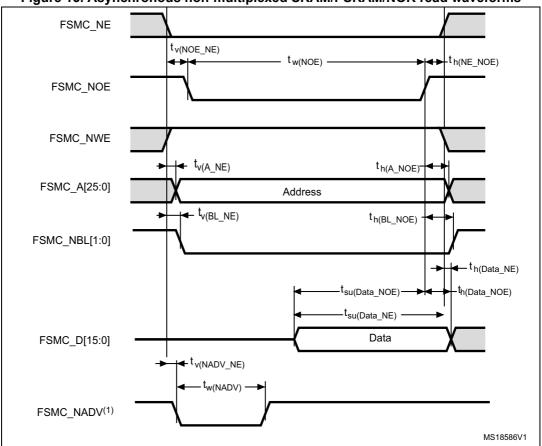

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

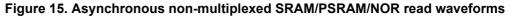

Figure 17. Asynchronous multiplexed PSRAM/NOR read waveforms

| Table 32. Asynchronous | multiplexed PSRAM/NOR | read timings <sup>(1)(2)</sup> |

|------------------------|-----------------------|--------------------------------|

|------------------------|-----------------------|--------------------------------|

| Symbol                    | Parameter                                                 | Min                      | Max                      | Unit |

|---------------------------|-----------------------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                          | 7T <sub>HCLK</sub> – 2   | 7T <sub>HCLK</sub> + 2   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                              | 3T <sub>HCLK</sub> – 0.5 | 3T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                         | 4T <sub>HCLK</sub> – 1   | 4T <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                   | -1                       | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                              | -                        | 0                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                             | 3                        | 5                        | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                        | T <sub>HCLK</sub> –1.5   | T <sub>HCLK</sub> + 1.5  | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | T <sub>HCLK</sub>        | -                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                     | T <sub>HCLK</sub>        | -                        | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high                     | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                             | -                        | 0                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                          | 2T <sub>HCLK</sub> + 24  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                          | 2T <sub>HCLK</sub> + 25  | -                        | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high                        | 0                        | -                        | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high                        | 0                        | -                        | ns   |

1. C<sub>L</sub> = 15 pF.

2. Preliminary values.

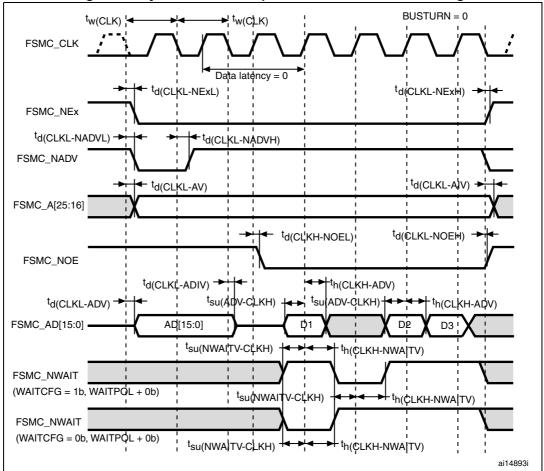

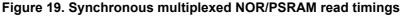

#### Synchronous waveforms and timings

*Figure 19* through *Figure 22* represent synchronous waveforms and *Table 35* through *Table 37* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F10xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

Figure 20. Synchronous multiplexed PSRAM write timings

## 5.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 38*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                    | Level/Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 24 MHz, LQFP144<br>package, conforms to<br>IEC 61000-4-2                             | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, T_A = +25 ^{\circ}\text{C},$<br>$f_{HCLK} = 24 \text{ MHz}, \text{LQFP144}$<br>package, conforms to<br>IEC 61000-4-4 | 4A          |

Table 38. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## 5.3.14 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under the conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol                                  | Parameter                                                            | Conditions                                                         | Min                                | Тур | Мах                                | Unit |

|-----------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------|-----|------------------------------------|------|

| V <sub>IL</sub>                         | Standard I/O input low<br>level voltage                              |                                                                    | -0.3                               | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  |      |

|                                         | I/O FT <sup>(1)</sup> input low level voltage                        | -                                                                  | -0.3                               | -   | 0.32*(V <sub>DD</sub> -2 V)+0.75 V |      |

|                                         | Standard I/O input<br>high level voltage                             |                                                                    | 0.41*(V <sub>DD</sub> -2 V) +1.3 V | -   | V <sub>DD</sub> +0.3               | V    |

| V <sub>IH</sub>                         | I/O FT <sup>(1)</sup> input high<br>level voltage                    | $V_{DD} > 2 V$                                                     | 0.42*/\/ 2\+1.\/                   | _   | 5.5                                |      |

|                                         |                                                                      | $V_{DD} \leq 2 V$                                                  | 0.42*(V <sub>DD</sub> –2)+1 V      | -   | 5.2                                |      |

| V <sub>hys</sub>                        | Standard I/O Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> | -                                                                  | 200                                | -   | -                                  | mV   |

|                                         | I/O FT Schmitt trigger voltage hysteresis <sup>(2)</sup>             |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>  | -   | -                                  | mV   |

| Input leakage<br>current <sup>(4)</sup> | Input leakage                                                        | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                  | -   | ±1                                 |      |

|                                         | current <sup>(4)</sup>                                               | V <sub>IN</sub> = 5 V<br>I/O FT                                    | -                                  | -   | 3                                  | μA   |

| R <sub>PU</sub>                         | Weak pull-up<br>equivalent resistor <sup>(5)</sup>                   | $V_{IN} = V_{SS}$                                                  | 30                                 | 40  | 50                                 | kΩ   |

| R <sub>PD</sub>                         | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                 | $V_{IN} = V_{DD}$                                                  | 30                                 | 40  | 50                                 | kΩ   |

| C <sub>IO</sub>                         | I/O pin capacitance                                                  | -                                                                  | -                                  | 5   | -                                  | pF   |

1. FT = 5V tolerant. To sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by design, not tested in production.

3. With a minimum of 100 mV.

4. Leakage could be higher than max. if negative current is injected on adjacent pins.

5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 23* and *Figure 24* for standard I/Os, and in *Figure 25* and *Figure 26* for 5 V tolerant I/Os.

### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                         | Conditions                                             | Min                  | Max | Unit |

|--------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output Low level voltage for an I/O pin when 8 pins are sunk at the same time     | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA, | -                    | 0.4 | · v  |

| V <sub>OH</sub> <sup>(3)</sup> | Output High level voltage for an I/O pin when 8 pins are sourced at the same time | $1_{O} - 40$ mA,<br>2.7 V < V <sub>DD</sub> < 3.6 V    | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time     | TTL port <sup>(2)</sup><br>I <sub>IO</sub> = +8 mA     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time | $2.7 V < V_{DD} < 3.6 V$                               | 2.4                  | -   |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time     | l <sub>IO</sub> = +20 mA <sup>(4)</sup>                | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time | 2.7 V < V <sub>DD</sub> < 3.6 V                        | V <sub>DD</sub> -1.3 | -   | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time     | I <sub>IO</sub> = +6 mA <sup>(4)</sup>                 | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time | 2 V < V <sub>DD</sub> < 2.7 V                          | V <sub>DD</sub> -0.4 | -   | v    |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 7* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 7 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data, not tested in production.

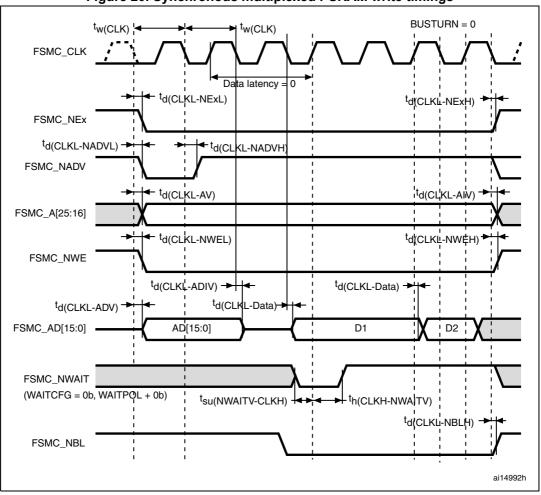

Figure 29. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

| f <sub>SCL</sub> (kHz) <sup>(3)</sup> | I2C_CCR value           |

|---------------------------------------|-------------------------|

|                                       | R <sub>P</sub> = 4.7 kΩ |

| 400                                   | 0x8011                  |

| 300                                   | 0x8016                  |

| 200                                   | 0x8021                  |

| 100                                   | 0x0064                  |

| 50                                    | 0x00C8                  |

| 20                                    | 0x01F4                  |

## Table 49. SCL frequency ( $f_{PCLK1}$ = 24 MHz, $V_{DD}$ = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed,

2. For speeds around 400 kHz, the tolerance on the achieved speed is of ±2%. For other speed ranges, the tolerance on the achieved speed ±1%. These variations depend on the accuracy of the external components used to design the application.

3. Guaranteed by design, not tested in production.

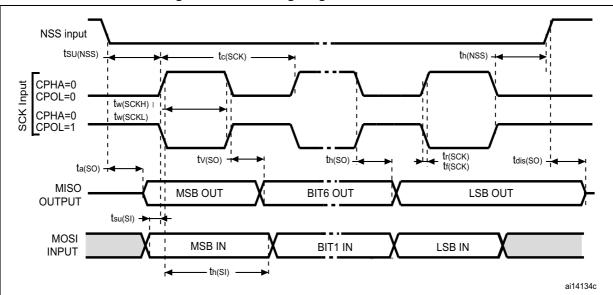

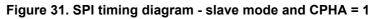

#### **SPI interface characteristics**

Unless otherwise specified, the parameters given in *Table 50* are preliminary values derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Refer to Section 5.3.13: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                            | Parameter                           | Conditions                                            | Min                | Мах                | Unit |  |

|-------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|--------------------|--------------------|------|--|

| f <sub>SCK</sub>                                                  | ODL ala ala fas musa ava            | Master mode                                           | -                  | 12                 |      |  |

| 1/t <sub>c(SCK)</sub>                                             | SPI clock frequency                 | Slave mode                                            | -                  | 12                 | MHz  |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                        | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            |                    | 8                  | ns   |  |

| DuCy(SCK)                                                         | SPI slave input clock<br>duty cycle | Slave mode                                            | 30                 | 70                 | %    |  |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                               | NSS setup time                      | Slave mode                                            | 4t <sub>PCLK</sub> | -                  |      |  |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                | NSS hold time                       | Slave mode                                            | 2t <sub>PCLK</sub> | -                  |      |  |

| $\begin{array}{c}t_{w(SCKH)}^{(1)}\\t_{w(SCKL)}^{(1)}\end{array}$ | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 24 MHz,<br>presc = 4 | 50                 | 60                 |      |  |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)                | Data input setup time               | Master mode                                           | 5                  | -                  |      |  |

|                                                                   |                                     | Slave mode                                            | 5                  | -                  |      |  |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                 | Data input hold time                | Master mode                                           | 5                  | -                  |      |  |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                 |                                     | Slave mode                                            | 4                  | -                  | ns   |  |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                              | Data output access time             | Slave mode, f <sub>PCLK</sub> = 24 MHz                | 0                  | 3t <sub>PCLK</sub> |      |  |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                            | Data output disable time            | Slave mode                                            | 2                  | 10                 |      |  |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                 | Data output valid time              | Slave mode (after enable edge)                        | -                  | 25                 |      |  |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                 | Data output valid time              | Master mode (after enable edge)                       | -                  | 5                  |      |  |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                 |                                     | Slave mode (after enable edge)                        | 15                 | -                  |      |  |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                 | Data output hold time               | Master mode (after enable edge)                       | 2                  | -                  |      |  |

1. Preliminary values.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

Figure 30. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

# 7 Ordering information scheme

| Example:                                        | STM32 F 100 V | с т | 6 | В | xxx |

|-------------------------------------------------|---------------|-----|---|---|-----|

|                                                 |               |     |   |   |     |

| Device family                                   |               |     |   |   |     |

| STM32 = ARM-based 32-bit microcontroller        |               |     |   |   |     |

| Product type                                    |               |     |   |   |     |

| F = General-purpose                             |               |     |   |   |     |

|                                                 |               |     |   |   |     |

| Device subfamily                                |               |     |   |   |     |

| 100 = value line                                |               |     |   |   |     |

|                                                 |               |     |   |   |     |

| Pin count                                       |               |     |   |   |     |

| R = 64 pins                                     |               |     |   |   |     |

| V = 100 pins                                    |               |     |   |   |     |

| Z = 144 pins                                    |               |     |   |   |     |

|                                                 |               |     |   |   |     |

| Flash memory size                               |               |     |   |   |     |

| C = 256 Kbytes of Flash memory                  |               |     |   |   |     |

| D = 384 Kbytes of Flash memory                  |               |     |   |   |     |

| E = 512 Kbytes of Flash memory                  |               |     |   |   |     |

| Package                                         |               |     |   |   |     |

| T = LQFP                                        |               |     | 1 |   |     |

| Temperature range                               |               |     |   |   |     |

| 6 = Industrial temperature range, -40 to 85 °C  |               |     | ] |   |     |

| 7 = Industrial temperature range, –40 to 105 °C |               |     |   |   |     |

|                                                 |               |     |   |   |     |

| Internal code                                   |               |     |   |   |     |

| В                                               |               |     |   |   |     |

| Options                                         |               |     |   |   |     |

| xxx = programmed parts                          |               |     |   |   |     |

#### Table 61. Ordering information scheme

TR = tape and real

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.