Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status Active                    |                                |

|------------------------------------------|--------------------------------|

|                                          |                                |

| Core Processor ARM® Corte                | x®-M3                          |

| Core Size 32-Bit Single                  | -Core                          |

| Speed 24MHz                              |                                |

| Connectivity I <sup>2</sup> C, IrDA, LIN | bus, SPI, UART/USART           |

| Peripherals DMA, PDR, P                  | OR, PVD, PWM, Temp Sensor, WDT |

| Number of I/O 51                         |                                |

| Program Memory Size 384KB (384K          | x 8)                           |

| Program Memory Type FLASH                |                                |

| EEPROM Size -                            |                                |

| RAM Size 32K x 8                         |                                |

| Voltage - Supply (Vcc/Vdd) 2V ~ 3.6V     |                                |

| Data Converters A/D 16x12b;              | D/A 2x12b                      |

| Oscillator Type Internal                 |                                |

| Operating Temperature -40°C ~ 85°C       | C (TA)                         |

| Mounting Type Surface Mount              | nt                             |

| Package / Case 64-LQFP                   |                                |

| Supplier Device Package 64-LQFP (10)     | (10)                           |

|                                          |                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F100xC, STM32F100xD and STM32F100xE value line microcontrollers. In the rest of the document, the STM32F100xC, STM32F100xD and STM32F100xE are referred to as high-density value line devices.

This STM32F100xC, STM32F100xD and STM32F100xE datasheet should be read in conjunction with the STM32F100xx high-density ARM<sup>®</sup>-based 32-bit MCUs *reference manual (RM0059)*. For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F100xx high-density value line Flash programming manual (PM0072)*. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the http://infocenter.arm.com.

either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output or the RTC alarm.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), a IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 2.2.15 DMA

The flexible 12-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The two DMA controllers support circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, DAC,  $I^2C$ , USART, all timers and ADC.

# 2.2.16 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are ten 16-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low power RC oscillator or the high-speed external clock divided by 128. The internal low power RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural crystal deviation. The RTC features a 32-bit programmable counter for long term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

# 2.2.17 Timers and watchdogs

The STM32F100xx devices include an advanced-control timer, nine general-purpose timers, two basic timers and two watchdog timers.

Table 3 compares the features of the advanced-control, general-purpose and basic timers.

## Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## SysTick timer

This timer is dedicated for OS, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

# 2.2.18 l<sup>2</sup>C bus

The I<sup>2</sup>C bus interface can operate in multimaster and slave modes. It can support standard and fast modes.

It supports dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded. The interface can be served by DMA and it supports SM Bus 2.0/PM Bus.

# 2.2.19 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F100xx value line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The available USART interfaces communicate at up to 3 Mbit/s. They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART interfaces can be served by the DMA controller.

# 2.2.20 Universal asynchronous receiver transmitter (UART)

The STM32F100xx value line embeds 2 universal asynchronous receiver transmitters (UART4, and UART5).

The available UART interfaces support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability.

The UART interfaces can be served by the DMA controller.

# 2.2.21 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 12 Mbit/s in slave and master modes in fullduplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits.

The SPIs can be served by the DMA controller.

DocID15081 Rev 10

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- up to 10-bit output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F100xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

# 2.2.26 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

# 2.2.27 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

|         | Pins    |        |                   |                     | _                        |                                                  | Alternate function                                                 | ons <sup>(4)</sup>         |

|---------|---------|--------|-------------------|---------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                            | Remap                      |

| 91      | -       | -      | PG6               | I/O                 | FT                       | PG6                                              | -                                                                  | -                          |

| 92      | -       | -      | PG7               | I/O                 | FT                       | PG7                                              | -                                                                  | -                          |

| 93      | -       | -      | PG8               | I/O                 | FT                       | PG8                                              | -                                                                  | -                          |

| 94      | -       | -      | V <sub>SS_9</sub> | S                   | -                        | V <sub>SS_9</sub>                                | -                                                                  | -                          |

| 95      | -       | -      | V <sub>DD_9</sub> | S                   | -                        | V <sub>DD_9</sub>                                | -                                                                  | -                          |

| 96      | 63      | 37     | PC6               | I/O                 | FT                       | PC6                                              | -                                                                  | TIM3_CH1                   |

| 97      | 64      | 38     | PC7               | I/O                 | FT                       | PC7                                              | -                                                                  | TIM3_CH2                   |

| 98      | 65      | 39     | PC8               | I/O                 | FT                       | PC8                                              | TIM13_CH1                                                          | TIM3_CH3                   |

| 99      | 66      | 40     | PC9               | I/O                 | FT                       | PC9                                              | TIM14_CH1                                                          | TIM3_CH4                   |

| 100     | 67      | 41     | PA8               | I/O                 | FT                       | PA8                                              | USART1_CK/<br>TIM1_CH1 <sup>(8)</sup> /MCO                         | -                          |

| 101     | 68      | 42     | PA9               | I/O                 | FT                       | PA9                                              | USART1_TX <sup>(8)</sup> /<br>TIM1_CH2 <sup>(8)</sup> / TIM15_BKIN | -                          |

| 102     | 69      | 43     | PA10              | I/O                 | FT                       | PA10                                             | USART1_RX <sup>(8)</sup> /<br>TIM1_CH3 <sup>(8)</sup> / TIM17_BKIN | -                          |

| 103     | 70      | 44     | PA11              | I/O                 | FT                       | PA11                                             | USART1_CTS / TIM1_CH4 <sup>(8)</sup>                               | -                          |

| 104     | 71      | 45     | PA12              | I/O                 | FT                       | PA12                                             | USART1_RTS / TIM1_ETR <sup>(8)</sup>                               | -                          |

| 105     | 72      | 46     | PA13              | I/O                 | FT                       | JTMS-SWDIO                                       | -                                                                  | -                          |

| 106     | 73      | -      |                   |                     |                          | Not connected                                    |                                                                    | -                          |

| 107     | 74      | 47     | V <sub>SS_2</sub> | S                   | -                        | V <sub>SS_2</sub>                                | -                                                                  | -                          |

| 108     | 75      | 48     | V <sub>DD_2</sub> | S                   | -                        | V <sub>DD_2</sub>                                | -                                                                  | -                          |

| 109     | 76      | 49     | PA14              | I/O                 | FT                       | JTCK-SWCLK                                       | -                                                                  | -                          |

| 110     | 77      | 50     | PA15              | I/O                 | FT                       | JTDI                                             | SPI3_NSS                                                           | TIM2_CH1_ETR /<br>SPI1_NSS |

| 111     | 78      | 51     | PC10              | I/O                 | FT                       | PC10                                             | UART4_TX                                                           | USART3_TX                  |

| 112     | 79      | 52     | PC11              | I/O                 | FT                       | PC11                                             | UART4_RX                                                           | USART3_RX                  |

| 113     | 80      | 53     | PC12              | I/O                 | FT                       | PC12                                             | UART5_TX                                                           | USART3_CK                  |

| 114     | 81      | -      | PD0               | I/O                 | FT                       | PD0                                              | FSMC_D2 <sup>(9)</sup>                                             | -                          |

| 115     | 82      | -      | PD1               | I/O                 | FT                       | PD1                                              | FSMC_D3 <sup>(9)</sup>                                             | -                          |

| 116     | 83      | 54     | PD2               | I/O                 | FT                       | PD2                                              | TIM3_ETR/UART5_RX                                                  | -                          |

| 117     | 84      | -      | PD3               | I/O                 | FT                       | PD3                                              | FSMC_CLK                                                           | USART2_CTS                 |

| 118     | 85      | -      | PD4               | I/O                 | FT                       | PD4                                              | FSMC_NOE                                                           | USART2_RTS                 |

| 119     | 86      | -      | PD5               | I/O                 | FT                       | PD5                                              | FSMC_NWE                                                           | USART2_TX                  |

Table 4. High-density STM32F100xx pin definitions (continued)

|         | Pins    |        |                    |                     |                          |                                                  | Alternate functions                                                           | ons <sup>(4)</sup>                     |

|---------|---------|--------|--------------------|---------------------|--------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name           | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                       | Remap                                  |

| 120     | -       | -      | V <sub>SS_10</sub> | S                   | -                        | V <sub>SS_10</sub>                               | -                                                                             | -                                      |

| 121     | -       | -      | $V_{DD_{10}}$      | S                   | -                        | $V_{DD_{10}}$                                    | -                                                                             | -                                      |

| 122     | 87      | -      | PD6                | I/O                 | FT                       | PD6                                              | FSMC_NWAIT                                                                    | USART2_RX                              |

| 123     | 88      | -      | PD7                | I/O                 | FT                       | PD7                                              | FSMC_NE1                                                                      | USART2_CK                              |

| 124     | -       | -      | PG9                | I/O                 | FT                       | PG9                                              | FSMC_NE2                                                                      | -                                      |

| 125     | -       | -      | PG10               | I/O                 | FT                       | PG10                                             | FSMC_NE3                                                                      | -                                      |

| 126     | -       | -      | PG11               | I/O                 | FT                       | PG11                                             | -                                                                             | -                                      |

| 127     | -       | -      | PG12               | I/O                 | FT                       | PG12                                             | FSMC_NE4                                                                      | -                                      |

| 128     | -       | -      | PG13               | I/O                 | FT                       | PG13                                             | FSMC_A24                                                                      | -                                      |

| 129     | -       | -      | PG14               | I/O                 | FT                       | PG14                                             | FSMC_A25                                                                      | -                                      |

| 130     | -       | -      | V <sub>SS_11</sub> | S                   | -                        | V <sub>SS_11</sub>                               | -                                                                             | -                                      |

| 131     | -       | -      | V <sub>DD_11</sub> | S                   | -                        | V <sub>DD_11</sub>                               | -                                                                             | -                                      |

| 132     | -       | -      | PG15               | I/O                 | FT                       | PG15                                             | -                                                                             | -                                      |

| 133     | 89      | 55     | PB3/               | I/O                 | FT                       | JTDO                                             | SPI3_SCK                                                                      | PB3/TRACESWO<br>TIM2_CH2 /<br>SPI1_SCK |

| 134     | 90      | 56     | PB4                | I/O                 | FT                       | NJTRST                                           | SPI3_MISO                                                                     | TIM3_CH1<br>SPI1_MISO                  |

| 135     | 91      | 57     | PB5                | I/O                 | -                        | PB5                                              | I2C1_SMBA/ SPI3_MOSI<br>TIM16_BKIN                                            | TIM3_CH2 /<br>SPI1_MOSI                |

| 136     | 92      | 58     | PB6                | I/O                 | FT                       | PB6                                              | I2C1_SCL <sup>(8)</sup> / TIM4_CH1 <sup>(8)</sup> /<br>TIM16_CH1N             | USART1_TX                              |

| 137     | 93      | 59     | PB7                | I/O                 | FT                       | PB7                                              | I2C1_SDA <sup>(8)</sup> / FSMC_NADV /<br>TIM4_CH2 <sup>(8)</sup> / TIM17_CH1N | USART1_RX                              |

| 138     | 94      | 60     | BOOT0              | Ι                   | -                        | BOOT0                                            | -                                                                             | -                                      |

| 139     | 95      | 61     | PB8                | I/O                 | FT                       | PB8                                              | TIM4_CH3 <sup>(8)</sup> /TIM16_CH1 /<br>HDMI_CEC                              | I2C1_SCL                               |

| 140     | 96      | 62     | PB9                | I/O                 | FT                       | PB9                                              | TIM4_CH4 <sup>(8)</sup> / TIM17_CH1                                           | I2C1_SDA                               |

| 141     | 97      | -      | PE0                | I/O                 | FT                       | PE0                                              | TIM4_ETR / FSMC_NBL0                                                          | -                                      |

| 142     | 98      | -      | PE1                | I/O                 | FT                       | PE1                                              | FSMC_NBL1                                                                     | -                                      |

| 143     | 99      | 63     | V <sub>SS_3</sub>  | S                   | -                        | V <sub>SS_3</sub>                                | -                                                                             | -                                      |

| 144     | 100     | 64     | V <sub>DD_3</sub>  | S                   | -                        | V <sub>DD_3</sub>                                | -                                                                             |                                        |

# Table 4. High-density STM32F100xx pin definitions (continued)

1. I = input, O = output, S = supply.

2. FT = 5 V tolerant.

| Symbol                               | Ratings                                                                 | Max.    | Unit |  |  |

|--------------------------------------|-------------------------------------------------------------------------|---------|------|--|--|

| I <sub>VDD</sub>                     | Total current into $V_{DD}/V_{DDA}$ power lines (source) <sup>(1)</sup> | 150     |      |  |  |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 150     |      |  |  |

| 1                                    | Output current sunk by any I/O and control pin                          | 25      |      |  |  |

| Ι <sub>ΙΟ</sub>                      | Output current source by any I/Os and control pin                       | -25     | mA   |  |  |

| L (2)                                | Injected current on five volt tolerant pins <sup>(3)</sup>              | -5 / +0 |      |  |  |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ± 5     |      |  |  |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25    |      |  |  |

#### Table 7. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See Note: on page 85.

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

# 5.3 Operating conditions

# 5.3.1 General operating conditions

#### Table 9. General operating conditions

| Symbol                          | Parameter                                  | Conditions                 | Min | Max | Unit |

|---------------------------------|--------------------------------------------|----------------------------|-----|-----|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency               | -                          | 0   | 24  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency              | -                          | 0   | 24  | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency              | -                          | 0   | 24  |      |

| V <sub>DD</sub>                 | Standard operating voltage                 | -                          | 2   | 3.6 | V    |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used) | Must be the same potential | 2   | 3.6 | V    |

| V DDA` '                        | Analog operating voltage<br>(ADC used)     | as V <sub>DD</sub>         | 2.4 | 3.6 | V    |

| V <sub>BAT</sub>                | Backup operating voltage                   | -                          | 1.8 | 3.6 | V    |

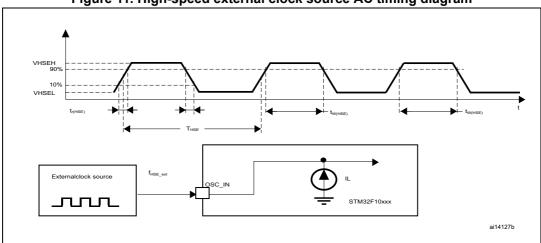

Figure 11. High-speed external clock source AC timing diagram

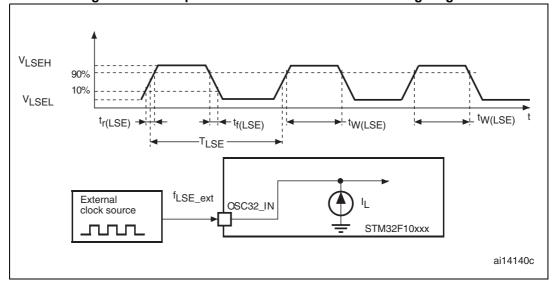

Figure 12. Low-speed external clock source AC timing diagram

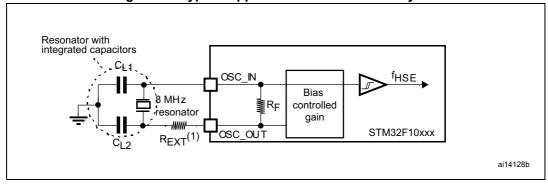

# High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol              | Parameter            | Conditions | Min | Тур | Max | Unit |

|---------------------|----------------------|------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub> | Oscillator frequency | -          | 4   | 8   | 24  | MHz  |

| R <sub>F</sub>      | Feedback resistor    | -          | -   | 200 | -   | kΩ   |

| Symbol                   | Parameter                                                                                     | Conditions                                                                      | Min | Тур | Max | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| $C_{L1} \\ C_{L2}^{(3)}$ | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(4)}$ | R <sub>S</sub> = 30 Ω                                                           | -   | 30  | -   | pF   |

| i <sub>2</sub>           | HSE driving current                                                                           | V <sub>DD</sub> = 3.3 V<br>V <sub>IN</sub> = V <sub>SS</sub> with 30 pF<br>load | -   | -   | 1   | mA   |

| 9 <sub>m</sub>           | Oscillator transconductance                                                                   | Startup                                                                         | 25  | -   | -   | mA/V |

| t <sub>SU(HSE)</sub>     | Startup time                                                                                  | $V_{DD}$ is stabilized                                                          | -   | 2   | -   | ms   |

Table 22. HSE 4-24 MHz oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Based on characterization, not tested in production.

- 3. It is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator. C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

- 4. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

1.  $R_{\text{EXT}}$  value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 23*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which

DocID15081 Rev 10

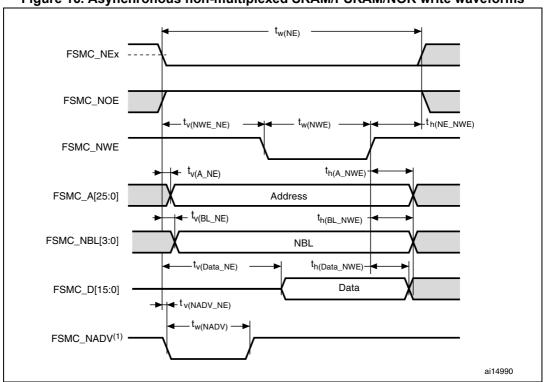

Figure 16. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

# Table 31. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings<sup>(1)(2)</sup>

| Symbol                   | Parameter                               | Min                     | Мах                     | Unit |

|--------------------------|-----------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                        | 3T <sub>HCLK</sub> – 1  | 3T <sub>HCLK</sub> + 2  | ns   |

| $t_{v(NWE_NE)}$          | FSMC_NEx low to FSMC_NWE low            | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                       | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid            | -                       | 7.5                     | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high   | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid           | -                       | 1.5                     | ns   |

| $t_{h(BL_NWE)}$          | FSMC_BL hold time after FSMC_NWE high   | T <sub>HCLK</sub> – 0.5 | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | FSMC_NEx low to Data valid              | -                       | T <sub>HCLK</sub> + 7   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high      | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low           | -                       | 5.5                     | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                      | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

1. C<sub>L</sub> = 15 pF.

2. Preliminary values.

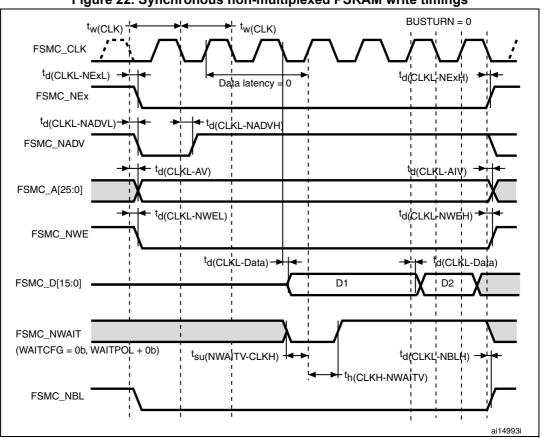

Figure 22. Synchronous non-multiplexed PSRAM write timings

Table 37. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                       | Parameter                                  | Min  | Max | Unit |

|------------------------------|--------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                            | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)      | -    | 2   | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)     | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low              | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high             | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | 2    | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>    | FSMC_CLK low to FSMC_NWE low               | -    | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 1    | -   | ns   |

| t <sub>d(CLKL-Data)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK low | -    | 6   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 7    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high       | 2    | -   | ns   |

| t <sub>d(CLKL-NBLH)</sub>    | FSMC_CLK low to FSMC_NBL high              | 1    | -   | ns   |

1. C<sub>L</sub> = 15 pF.

2. Preliminary values.

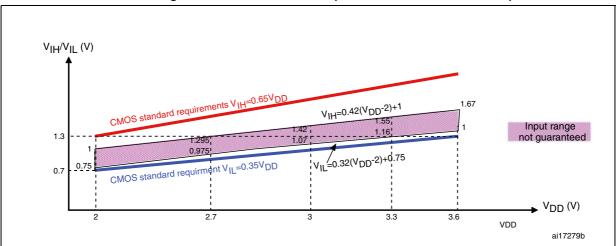

Figure 25. 5 V tolerant I/O input characteristics - CMOS port

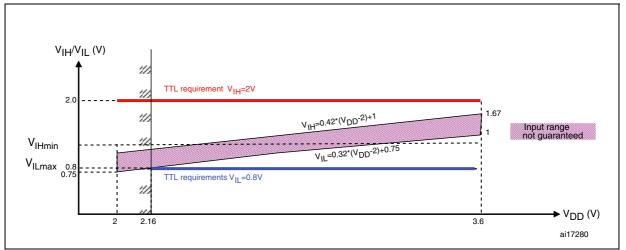

Figure 26. 5 V tolerant I/O input characteristics - TTL port

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed VOL/VOH) except PC13, PC14 and PC15 it can sink or source up to +/-3mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 7*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 7*).

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 45*, respectively.

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                             | Мах                | Unit |  |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|--|

| 10                                         | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                 | 2 <sup>(3)</sup>   | MHz  |  |

|                                            | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 125 <sup>(3)</sup> | 20   |  |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | CL = 30 μr, v <sub>DD</sub> = 2 v to 3.0 v             | 125 <sup>(3)</sup> | ns   |  |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V               | 10 <sup>(3)</sup>  | MHz  |  |

| 01                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C <sub>I</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 25 <sup>(3)</sup>  | – ns |  |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | CL- 30 μr, VDD - 2 V 10 3.0 V                          | 25 <sup>(3)</sup>  |      |  |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V               | 24                 | MHz  |  |

|                                            | t <sub>f(IO)</sub> out  | Output high to low level fall time                                    | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 5 <sup>(3)</sup>   |      |  |

|                                            |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 8 <sup>(3)</sup>   | )    |  |

| 11                                         |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  | ]    |  |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   | ns   |  |

|                                            |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V             | 8 <sup>(3)</sup>   | 1    |  |

|                                            |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |  |

| -                                          | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                      |                    | ns   |  |

Table 45. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F100xx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure* 27.

3. Guaranteed by design, not tested in production.

| Symbol                           | Parameter                                          | Conditions                                            | Min                                                                        | Тур                | Мах                | Unit               |

|----------------------------------|----------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                       | -                                                     | 2.4                                                                        | -                  | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                         | -                                                     | 2.4                                                                        | -                  | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin          | -                                                     | -                                                                          | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                                | -                                                     | 0.6                                                                        | -                  | 12                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                      | -                                                     | 0.05                                                                       | -                  | 1                  | MHz                |

| <b>f</b> (2)                     |                                                    | f <sub>ADC</sub> = 12 MHz                             | -                                                                          | -                  | 823                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                         | -                                                     | -                                                                          | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                           | -                                                     | 0 (V <sub>SSA</sub> tied to ground)                                        | -                  | V <sub>REF+</sub>  | V                  |

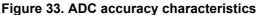

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                           | See <i>Equation 1</i> and <i>Table 52</i> for details | -                                                                          | -                  | 50                 | kΩ                 |

| $R_{ADC}^{(2)}$                  | Sampling switch resistance                         | -                                                     | -                                                                          | -                  | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                 | -                                                     | -                                                                          | -                  | 8                  | pF                 |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibratian time                                   | f <sub>ADC</sub> = 12 MHz                             | 5.9                                                                        |                    |                    | μs                 |

| <sup>I</sup> CAL <sup>(=)</sup>  | Calibration time                                   | -                                                     | 83                                                                         |                    |                    | 1/f <sub>ADC</sub> |

| + (2)                            | Injection trigger conversion                       | f <sub>ADC</sub> = 12 MHz                             | -                                                                          | -                  | 0.214              | μs                 |

| $t_{lat}^{(2)}$                  | latency                                            | -                                                     | -                                                                          | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| <b>•</b> (2)                     | Regular trigger conversion                         | f <sub>ADC</sub> = 12 MHz                             | -                                                                          | -                  | 0.143              | μs                 |

| t <sub>latr</sub> (2)            | latency                                            | -                                                     | -                                                                          | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>    |                                                    | f <sub>ADC</sub> = 12 MHz                             | 0.125                                                                      | -                  | 17.1               | μs                 |

|                                  | Sampling time                                      |                                                       | 1.5                                                                        | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                      | -                                                     | 0                                                                          | 0                  | 1                  | μs                 |

|                                  | <b>T</b> ( )                                       | f <sub>ADC</sub> = 12 MHz                             | 1.17                                                                       | -                  | 21                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time<br>(including sampling time) | -                                                     | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                    | 1/f <sub>ADC</sub> |

1. Preliminary values.

2. Guaranteed by design, not tested in production.

3.  $V_{\mathsf{REF}}\text{+}$  is internally connected to  $V_{\mathsf{DDA}}$

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 51.

# Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{r_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The above formula (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

DocID15081 Rev 10

Note: Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.13 does not affect the ADC accuracy.

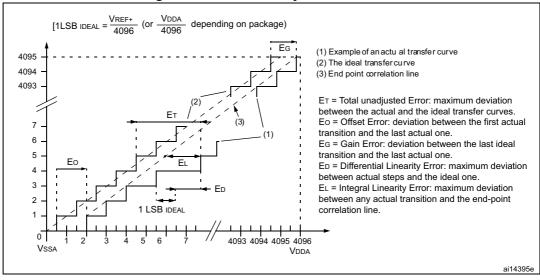

#### Figure 34. Typical connection diagram using the ADC

1. Refer to *Table 51* for the values of R<sub>AIN</sub>, R<sub>ADC</sub> and C<sub>ADC</sub>.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

## General PCB design guidelines

Power supply decoupling should be performed as shown in Figure 35 or Figure 36, depending on whether  $V_{\text{REF+}}$  is connected to  $V_{\text{DDA}}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

# 6 Package characteristics

# 6.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

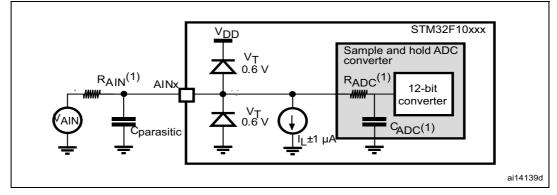

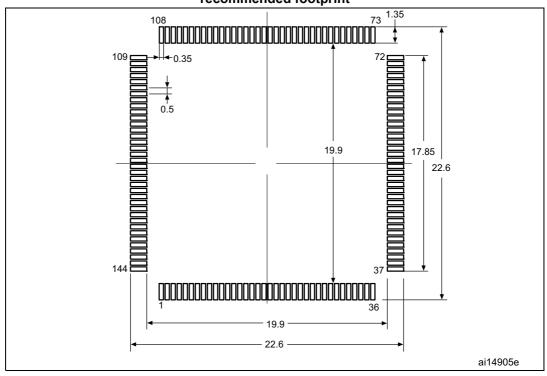

# 6.2 LQFP144 package information

Figure 38. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| E      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

# Table 57. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat packagemechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

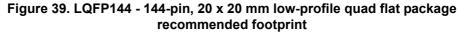

## **Device marking for LQFP144**

The following figure shows the device marking for the LQFP144 package.

#### Figure 40.LQFP144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

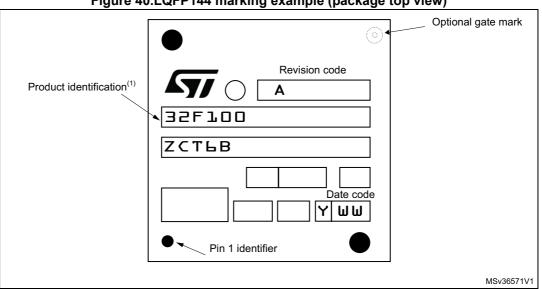

#### **Device marking for LQFP64**

The following figure shows the device marking for the LQFP64 package.

Figure 46.LQFP64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 09-Oct-2008 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 31-Mar-2009 | 2        | <ul> <li>I/O information clarified on page 1.</li> <li>Table 5: High-density STM32F100xx pin definitions modified.</li> <li>Figure 5: Memory map on page 26 modified.</li> <li>Note modified in Table 13: Maximum current consumption in Run mode, code with data processing running from Flash and Table 15: Maximum current consumption in Sleep mode, code running from Flash or RAM.</li> <li>Table 20: High-speed external user clock characteristics and Table 21: Low-speed user external clock characteristics modified. ACCHSI max values modified in Table 24: HSI oscillator characteristics.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|             |          | Note modified in Table 13: Maximum current consumption in Run<br>mode, code with data processing running from Flash and Table 15:<br>Maximum current consumption in Sleep mode, code running from<br>Flash or RAM.<br>Figure 10, Figure 11 and Figure 12 show typical curves (titles<br>changed).<br>Small text changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 01-Sep-2010 | 3        | Major revision of whole document.<br>Added LQFP144 package and additional peripherals (SPI3, UART4,<br>UART, TIM5, 12, 14, 13, FSMC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 18-Oct-2010 | 4        | Updated Power consumption data in <i>Table 13</i> to <i>Table 16</i><br>Updated <i>Section 5.3.11: EMC characteristics on page 68</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 11-Apr-2011 | 5        | Added Section 2.2.6: LCD parallel interface on page 13<br>In Table 4 on page 24 moved TIM15_BKIN and TIM17_BKIN from<br>remap to default column. Updated description of PA3, PA5 and PF6<br>to PF10.<br>Updated footnotes below Table 6: Voltage characteristics on page 37<br>and Table 7: Current characteristics on page 38<br>Added VBAT values in Table 16: Typical and maximum current<br>consumptions in Stop and Standby modes on page 44<br>Updated tw min in Table 20: High-speed external user clock<br>characteristics on page 50<br>Updated startup time in Table 23: LSE oscillator characteristics (fLSE<br>= 32.768 kHz) on page 53<br>Added HSI clock accuracy values in Table 24: HSI oscillator<br>characteristics on page 54<br>Updated FSMC Synchronous waveforms and timings on page 62<br>Updated Table 43: I/O static characteristics on page 71<br>Added Section 5.3.13: I/O current injection characteristics on<br>page 70<br>Corrected TTL and CMOS designations in Table 44: Output voltage<br>characteristics on page 74 |  |  |

| Table 62. | Document | revision | history |

|-----------|----------|----------|---------|

|-----------|----------|----------|---------|