# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                   |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                             |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 24K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100vct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                 | Table 5. Timer leature comparison |                         |                                       |                        |                             |                          |  |  |  |

|---------------------------------|-----------------------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|--|--|--|

| Timer                           | Counter resolution                | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |

| TIM1                            | 16-bit                            | Up,<br>down,<br>up/down | 16 bits                               | Yes                    | 4                           | Yes                      |  |  |  |

| TIM2,<br>TIM3,<br>TIM4,<br>TIM5 | 16-bit                            | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |  |  |  |

| TIM12                           | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | No                     | 2                           | No                       |  |  |  |

| TIM13,<br>TIM14                 | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | No                     | 1                           | No                       |  |  |  |

| TIM15                           | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 2                           | Yes                      |  |  |  |

| TIM16,<br>TIM17                 | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 1                           | Yes                      |  |  |  |

| TIM6,<br>TIM7                   | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |  |  |  |

Table 3. Timer feature comparison

## Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on 6 channels. It has complementary PWM outputs with programmable inserted dead times. It can also be seen as a complete general-purpose timer. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard TIM timers which have the same architecture. The advanced control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

## General-purpose timers (TIM2..5, TIM12..17)

There are ten synchronizable general-purpose timers embedded in the STM32F100xx devices (see *Table 3* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

DocID15081 Rev 10

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- up to 10-bit output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F100xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 2.2.26 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

## 2.2.27 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

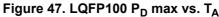

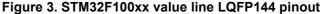

## 3 Pinouts and pin descriptions

|         | Pins    |        | <b>3</b>          |                     |                          |                                                  | Alternate function                                                                | ons <sup>(4)</sup>       |

|---------|---------|--------|-------------------|---------------------|--------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                           | Remap                    |

| 66      | 44      | -      | PE13              | I/O                 | FT                       | PE13                                             | FSMC_D10                                                                          | TIM1_CH3                 |

| 67      | 45      | -      | PE14              | I/O                 | FT                       | PE14                                             | FSMC_D11                                                                          | TIM1_CH4                 |

| 68      | 46      | -      | PE15              | I/O                 | FT                       | PE15                                             | FSMC_D12                                                                          | TIM1_BKIN                |

| 69      | 47      | 29     | PB10              | I/O                 | FT                       | PB10                                             | I2C2_SCL/USART3_TX <sup>(8)</sup>                                                 | TIM2_CH3 /<br>HDMI_CEC   |

| 70      | 48      | 30     | PB11              | I/O                 | FT                       | PB11                                             | I2C2_SDA/USART3_RX <sup>(8)</sup>                                                 | TIM2_CH4                 |

| 71      | 49      | 31     | V <sub>SS_1</sub> | S                   | -                        | V <sub>SS_1</sub>                                | -                                                                                 | -                        |

| 72      | 50      | 32     | V <sub>DD_1</sub> | S                   | -                        | V <sub>DD_1</sub>                                | -                                                                                 | -                        |

| 73      | 51      | 33     | PB12              | I/O                 | FT                       | PB12                                             | SPI2_NSS/<br>I2C2_SMBA/<br>USART3_CK <sup>(8)</sup> /<br>TIM1_BKIN <sup>(8)</sup> | TIM12_CH1                |

| 74      | 52      | 34     | PB13              | I/O                 | FT                       | PB13                                             | SPI2_SCK/<br>USART3_CTS <sup>(8)</sup> /<br>TIM1_CH1N                             | TIM12_CH2                |

| 75      | 53      | 35     | PB14              | I/O                 | FT                       | PB14                                             | SPI2_MISO/TIM1_CH2N<br>USART3_RTS <sup>(8)</sup> /                                | TIM15_CH1                |

| 76      | 54      | 36     | PB15              | I/O                 | FT                       | PB15                                             | SPI2_MOSI/<br>TIM1_CH3N <sup>(8)</sup> /<br>TIM15_CH1N                            | TIM15_CH2                |

| 77      | 55      | -      | PD8               | I/O                 | FT                       | PD8                                              | FSMC_D13                                                                          | USART3_TX                |

| 78      | 56      | -      | PD9               | I/O                 | FT                       | PD9                                              | FSMC_D14                                                                          | USART3_RX                |

| 79      | 57      | -      | PD10              | I/O                 | FT                       | PD10                                             | FSMC_D15                                                                          | USART3_CK                |

| 80      | 58      | -      | PD11              | I/O                 | FT                       | PD11                                             | FSMC_A16                                                                          | USART3_CTS               |

| 81      | 59      | -      | PD12              | I/O                 | FT                       | PD12                                             | FSMC_A17                                                                          | TIM4_CH1 /<br>USART3_RTS |

| 82      | 60      | -      | PD13              | I/O                 | FT                       | PD13                                             | FSMC_A18                                                                          | TIM4_CH2                 |

| 83      | -       | -      | V <sub>SS_8</sub> | S                   | -                        | V <sub>SS_8</sub>                                | -                                                                                 | -                        |

| 84      | -       | -      | V <sub>DD_8</sub> | S                   | -                        | $V_{DD_8}$                                       | -                                                                                 | -                        |

| 85      | 61      | -      | PD14              | I/O                 | FT                       | PD14                                             | FSMC_D0                                                                           | TIM4_CH3                 |

| 86      | 62      | -      | PD15              | I/O                 | FT                       | PD15                                             | FSMC_D1                                                                           | TIM4_CH4                 |

| 87      | -       | -      | PG2               | I/O                 | FT                       | PG2                                              | FSMC_A12                                                                          | -                        |

| 88      | -       | -      | PG3               | I/O                 | FT                       | PG3                                              | FSMC_A13                                                                          | -                        |

| 89      | -       | -      | PG4               | I/O                 | FT                       | PG4                                              | FSMC_A14                                                                          | -                        |

| 90      | -       | -      | PG5               | I/O                 | FT                       | PG5                                              | FSMC_A15                                                                          | -                        |

## Table 4. High-density STM32F100xx pin definitions (continued)

|         | Pins    |        |                   |                     | _                        |                                                  | Alternate function                                                 | ons <sup>(4)</sup>         |

|---------|---------|--------|-------------------|---------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                            | Remap                      |

| 91      | -       | -      | PG6               | I/O                 | FT                       | PG6                                              | -                                                                  | -                          |

| 92      | -       | -      | PG7               | I/O                 | FT                       | PG7                                              | -                                                                  | -                          |

| 93      | -       | -      | PG8               | I/O                 | FT                       | PG8                                              | -                                                                  | -                          |

| 94      | -       | -      | V <sub>SS_9</sub> | S                   | -                        | V <sub>SS_9</sub>                                | -                                                                  | -                          |

| 95      | -       | -      | V <sub>DD_9</sub> | S                   | -                        | V <sub>DD_9</sub>                                | -                                                                  | -                          |

| 96      | 63      | 37     | PC6               | I/O                 | FT                       | PC6                                              | -                                                                  | TIM3_CH1                   |

| 97      | 64      | 38     | PC7               | I/O                 | FT                       | PC7                                              | -                                                                  | TIM3_CH2                   |

| 98      | 65      | 39     | PC8               | I/O                 | FT                       | PC8                                              | TIM13_CH1                                                          | TIM3_CH3                   |

| 99      | 66      | 40     | PC9               | I/O                 | FT                       | PC9                                              | TIM14_CH1                                                          | TIM3_CH4                   |

| 100     | 67      | 41     | PA8               | I/O                 | FT                       | PA8                                              | USART1_CK/<br>TIM1_CH1 <sup>(8)</sup> /MCO                         | -                          |

| 101     | 68      | 42     | PA9               | I/O                 | FT                       | PA9                                              | USART1_TX <sup>(8)</sup> /<br>TIM1_CH2 <sup>(8)</sup> / TIM15_BKIN | -                          |

| 102     | 69      | 43     | PA10              | I/O                 | FT                       | PA10                                             | USART1_RX <sup>(8)</sup> /<br>TIM1_CH3 <sup>(8)</sup> / TIM17_BKIN | -                          |

| 103     | 70      | 44     | PA11              | I/O                 | FT                       | PA11                                             | USART1_CTS / TIM1_CH4 <sup>(8)</sup>                               | -                          |

| 104     | 71      | 45     | PA12              | I/O                 | FT                       | PA12                                             | USART1_RTS / TIM1_ETR <sup>(8)</sup>                               | -                          |

| 105     | 72      | 46     | PA13              | I/O                 | FT                       | JTMS-SWDIO                                       | -                                                                  | -                          |

| 106     | 73      | -      |                   |                     |                          | Not connected                                    |                                                                    | -                          |

| 107     | 74      | 47     | V <sub>SS_2</sub> | S                   | -                        | V <sub>SS_2</sub>                                | -                                                                  | -                          |

| 108     | 75      | 48     | V <sub>DD_2</sub> | S                   | -                        | V <sub>DD_2</sub>                                | -                                                                  | -                          |

| 109     | 76      | 49     | PA14              | I/O                 | FT                       | JTCK-SWCLK                                       | -                                                                  | -                          |

| 110     | 77      | 50     | PA15              | I/O                 | FT                       | JTDI                                             | SPI3_NSS                                                           | TIM2_CH1_ETR /<br>SPI1_NSS |

| 111     | 78      | 51     | PC10              | I/O                 | FT                       | PC10                                             | UART4_TX                                                           | USART3_TX                  |

| 112     | 79      | 52     | PC11              | I/O                 | FT                       | PC11                                             | UART4_RX                                                           | USART3_RX                  |

| 113     | 80      | 53     | PC12              | I/O                 | FT                       | PC12                                             | UART5_TX                                                           | USART3_CK                  |

| 114     | 81      | -      | PD0               | I/O                 | FT                       | PD0                                              | FSMC_D2 <sup>(9)</sup>                                             | -                          |

| 115     | 82      | -      | PD1               | I/O                 | FT                       | PD1                                              | FSMC_D3 <sup>(9)</sup>                                             | -                          |

| 116     | 83      | 54     | PD2               | I/O                 | FT                       | PD2                                              | TIM3_ETR/UART5_RX                                                  | -                          |

| 117     | 84      | -      | PD3               | I/O                 | FT                       | PD3                                              | FSMC_CLK                                                           | USART2_CTS                 |

| 118     | 85      | -      | PD4               | I/O                 | FT                       | PD4                                              | FSMC_NOE                                                           | USART2_RTS                 |

| 119     | 86      | -      | PD5               | I/O                 | FT                       | PD5                                              | FSMC_NWE                                                           | USART2_TX                  |

Table 4. High-density STM32F100xx pin definitions (continued)

|      | Table 5. FSMC pir | n definition (continued) | -                      |  |

|------|-------------------|--------------------------|------------------------|--|

| Dine | F                 | SMC                      | LQFP100 <sup>(1)</sup> |  |

| Pins | NOR/PSRAM/SRAM    | NOR/PSRAM Mux            |                        |  |

| PG0  | A10               | -                        | -                      |  |

| PG1  | A11               | -                        | -                      |  |

| PE7  | D4                | DA4                      | Yes                    |  |

| PE8  | D5                | DA5                      | Yes                    |  |

| PE9  | D6                | DA6                      | Yes                    |  |

| PE10 | D7                | DA7                      | Yes                    |  |

| PE11 | D8                | DA8                      | Yes                    |  |

| PE12 | D9                | DA9                      | Yes                    |  |

| PE13 | D10               | DA10                     | Yes                    |  |

| PE14 | D11               | DA11                     | Yes                    |  |

| PE15 | D12               | DA12                     | Yes                    |  |

| PD8  | D13               | DA13                     | Yes                    |  |

| PD9  | D14               | DA14                     | Yes                    |  |

| PD10 | D15               | DA15                     | Yes                    |  |

| PD11 | A16               | A16                      | Yes                    |  |

| PD12 | A17               | A17                      | Yes                    |  |

| PD13 | A18               | A18                      | Yes                    |  |

| PD14 | D0                | DA0                      | Yes                    |  |

| PD15 | D1                | DA1                      | Yes                    |  |

| PG2  | A12               | -                        | -                      |  |

| PG3  | A13               | -                        | -                      |  |

| PG4  | A14               | -                        | -                      |  |

| PG5  | A15               | -                        | -                      |  |

| PG6  | -                 | -                        | -                      |  |

| PG7  | -                 | -                        | -                      |  |

| PD0  | D2                | DA2                      | Yes                    |  |

| PD1  | D3                | DA3                      | Yes                    |  |

| PD3  | CLK               | CLK                      | Yes                    |  |

| PD4  | NOE               | NOE                      | Yes                    |  |

| PD5  | NWE               | NWE                      | Yes                    |  |

| PD6  | NWAIT             | NWAIT                    | Yes                    |  |

| PD7  | NE1               | NE1                      | Yes                    |  |

| PG9  | NE2               | NE2                      | -                      |  |

## Table 5. FSMC pin definition (continued)

| ······································ |                |                          |     |  |  |  |

|----------------------------------------|----------------|--------------------------|-----|--|--|--|

| Dine                                   | F              | – LQFP100 <sup>(1)</sup> |     |  |  |  |

| Pins                                   | NOR/PSRAM/SRAM | NOR/PSRAM Mux            |     |  |  |  |

| PG10                                   | NE3            | NE3                      | -   |  |  |  |

| PG11                                   | -              | -                        | -   |  |  |  |

| PG12                                   | NE4            | NE4                      | -   |  |  |  |

| PG13                                   | A24            | A24                      | -   |  |  |  |

| PG14                                   | A25            | A25                      | -   |  |  |  |

| PB7                                    | NADV           | NADV                     | Yes |  |  |  |

| PE0                                    | NBL0           | NBL0                     | Yes |  |  |  |

| PE1                                    | NBL1           | NBL1                     | Yes |  |  |  |

#### Table 5. FSMC pin definition (continued)

1. Ports F and G are not available in devices delivered in 100-pin packages.

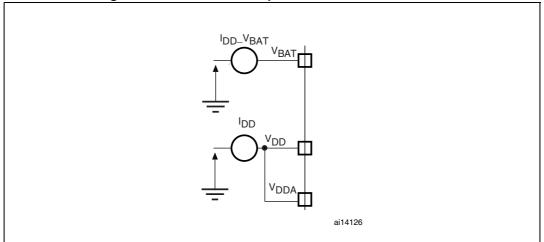

## 5.1.7 Current consumption measurement

#### Figure 10. Current consumption measurement scheme

## 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 6: Voltage characteristics*, *Table 7: Current characteristics*, and *Table 8: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                          | Min                  | Max                                           | Unit |

|-----------------------------------|----------------------------------------------------------------------------------|----------------------|-----------------------------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{\left(1\right)}$ | -0.3                 | 4.0                                           |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five volt tolerant pin                                          | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +4.0                          | V    |

| VIN'                              | Input voltage on any other pin                                                   | V <sub>SS</sub> -0.3 | 4.0                                           |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DD</sub> power pins                          | -                    | 50                                            |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                                 | -                    | 50                                            | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                               |                      | 3.12: Absolute<br>ngs (electrical<br>itivity) | -    |

#### Table 6. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 7: Current characteristics* for the maximum allowed injected current values.

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                               | Parameter                                        | Conditions                  | Min                | Тур  | Max  | Unit |

|--------------------------------------|--------------------------------------------------|-----------------------------|--------------------|------|------|------|

|                                      |                                                  | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 | V    |

|                                      |                                                  | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 | V    |

|                                      |                                                  | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 | V    |

|                                      |                                                  | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 | V    |

|                                      |                                                  | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 | V    |

|                                      |                                                  | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 | V    |

|                                      |                                                  | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 | V    |

| V                                    | Programmable voltage<br>detector level selection | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

| V <sub>PVD</sub>                     |                                                  | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | V    |

|                                      |                                                  | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 | V    |

|                                      |                                                  | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 | V    |

|                                      |                                                  | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 | V    |

|                                      |                                                  | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  | V    |

|                                      |                                                  | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | V    |

|                                      |                                                  | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    | V    |

|                                      |                                                  | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                   | -                           | -                  | 100  | -    | mV   |

| V                                    | Power on/power down                              | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| V <sub>POR/PDR</sub> Pow<br>rese     | reset threshold                                  | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                   | -                           | -                  | 40   | -    | mV   |

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                              | -                           | 1.5                | 2.5  | 4.5  | ms   |

1. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

2. Guaranteed by design, not tested in production.

|                 |                                  |                                              |                   | Typical                                   | values <sup>(1)</sup>    |      |

|-----------------|----------------------------------|----------------------------------------------|-------------------|-------------------------------------------|--------------------------|------|

| Symbol          | Parameter                        | Conditions                                   | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |                                  |                                              | 24 MHz            | 14.1                                      | 9.5                      |      |

|                 |                                  |                                              | 16 MHz            | 10                                        | 6.85                     |      |

|                 |                                  |                                              | 8 MHz             | 5.8                                       | 4.05                     |      |

|                 |                                  | Running on high-speed external clock with an | 4 MHz             | 3.6                                       | 2.65                     |      |

|                 | Supply<br>current in<br>Run mode | 8 MHz crystal <sup>(3)</sup>                 | 2 MHz             | 2.3                                       | 1.85                     | - mA |

|                 |                                  |                                              | 1 MHz             | 1.7                                       | 1.46                     |      |

|                 |                                  |                                              | 500 kHz           | 1.4                                       | 1.3                      |      |

|                 |                                  |                                              | 125 kHz           | 1.15                                      | 1.1                      |      |

| I <sub>DD</sub> |                                  |                                              | 24 MHz            | 13.4                                      | 8.7                      |      |

|                 |                                  |                                              | 16 MHz            | 9.3                                       | 6.2                      |      |

|                 |                                  |                                              | 8 MHz             | 5.2                                       | 3.45                     |      |

|                 |                                  | Running on high-speed                        | 4 MHz             | 2.95                                      | 2.1                      |      |

|                 |                                  | internal RC (HSI)                            | 2 MHz             | 1.7                                       | 1.3                      | -    |

|                 |                                  |                                              | 1 MHz             | 1.1                                       | 0.9                      |      |

|                 |                                  |                                              | 500 kHz           | 0.8                                       | 0.7                      |      |

|                 |                                  |                                              | 125 kHz           | 0.6                                       | 0.55                     |      |

Table 17. Typical current consumption in Run mode, code with data processing<br/>running from Flash

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA for the ADC and of 0.5 mA for the DAC analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

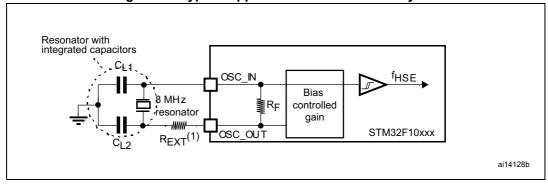

3. An 8 MHz crystal is used as the external clock source. The AHB prescaler is used to reduce the frequency when  $f_{HCLK} < 8$  MHz, the PLL is used when  $f_{HCLK} > 8$  MHz.

| Symbol                   | Parameter                                                                                     | Conditions                                                                      | Min | Тур | Max | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| $C_{L1} \\ C_{L2}^{(3)}$ | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(4)}$ | R <sub>S</sub> = 30 Ω                                                           | -   | 30  | -   | pF   |

| i <sub>2</sub>           | HSE driving current                                                                           | V <sub>DD</sub> = 3.3 V<br>V <sub>IN</sub> = V <sub>SS</sub> with 30 pF<br>load | -   | -   | 1   | mA   |

| 9 <sub>m</sub>           | Oscillator transconductance                                                                   | Startup                                                                         | 25  | -   | -   | mA/V |

| t <sub>SU(HSE)</sub>     | Startup time                                                                                  | $V_{DD}$ is stabilized                                                          | -   | 2   | -   | ms   |

Table 22. HSE 4-24 MHz oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Based on characterization, not tested in production.

- 3. It is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator. C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

- 4. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

1.  $R_{EXT}$  value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 23*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which

DocID15081 Rev 10

| Symbol                       | Parameter                                         | Min  | Мах | Unit |

|------------------------------|---------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                                   | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)             | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)            | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                     | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high                    | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)          | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625)        | 2    | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>    | FSMC_CLK high to FSMC_NOE low                     | -    | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                     | 0.5  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid               | -    | 12  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid             | 0    | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>    | FSMC_A/D[15:0] valid data before FSMC_CLK<br>high | 6    | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>     | FSMC_A/D[15:0] valid data after FSMC_CLK high     | 0    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high             | 8    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high              | 2    | -   | ns   |

Table 34. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 15 pF.

2. Preliminary values.

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device is monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                                    | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/24 MHz | Unit |

|------------------|------------|---------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|                  |            | $V = 2.6 V = 25^{\circ}C$                                                                                     | 0.1 MHz to 30 MHz           | 16                                                         |      |

| 6                | 10         | eak level V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25°C,<br>LQFP144 package<br>compliant with SAE<br>J1752/3 | 30 MHz to 130 MHz           | 25                                                         | dBµV |

| S <sub>EMI</sub> | Peak level |                                                                                                               | 130 MHz to 1GHz             | 25                                                         |      |

|                  |            |                                                                                                               | SAE EMI Level               | 4                                                          | -    |

## 5.3.12 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Table 40. ESD absolute maximum ratings |

|----------------------------------------|

|----------------------------------------|

| Symbol                | Ratings                                               | Conditions                                           | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \ ^{\circ}C$<br>conforming to JESD22-A114 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \ ^{\circ}C$<br>conforming to JESD22-C101 | П     | 500                             | V    |

1. Based on characterization results, not tested in production.

## Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD78 IC latch-up standard.

| Γ | Symbol | Parameter             | Conditions                           | Class      |

|---|--------|-----------------------|--------------------------------------|------------|

|   | LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78 | II level A |

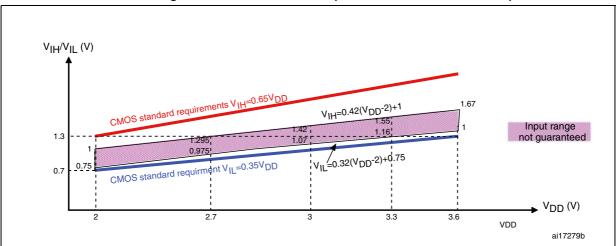

Figure 25. 5 V tolerant I/O input characteristics - CMOS port

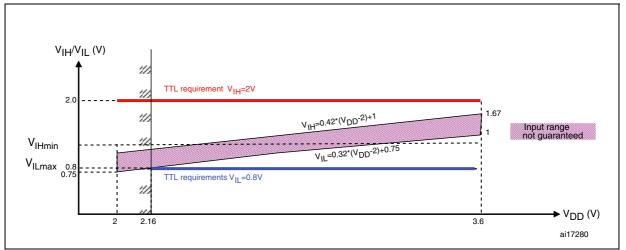

Figure 26. 5 V tolerant I/O input characteristics - TTL port

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed VOL/VOH) except PC13, PC14 and PC15 it can sink or source up to +/-3mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 7*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 7*).

|                                            | _                                       | Standard r | node l <sup>2</sup> C <sup>(1)</sup> | Fast mode |                    |      |  |

|--------------------------------------------|-----------------------------------------|------------|--------------------------------------|-----------|--------------------|------|--|

| Symbol                                     | Parameter                               | Min Max    |                                      | Min Max   |                    | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7        | -                                    | 1.3       | -                  |      |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0        | -                                    | 0.6       | -                  | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250        | -                                    | 100       | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0          | -                                    | 0         | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -          | 1000                                 | -         | 300                | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -          | 300                                  | -         | 300                |      |  |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0        | -                                    | 0.6       | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7        | -                                    | 0.6       | -                  | μs   |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0        | -                                    | 0.6       | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7        | -                                    | 1.3       | -                  | μs   |  |

| Cb                                         | Capacitive load for each bus line       | -          | 400                                  | -         | 400                | pF   |  |

Table 48. I<sup>2</sup>C characteristics

1. Guaranteed by design, not tested in production.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.125               | 0.4                       |

| 7.5                     | 0.625               | 5.9                       |

| 13.5                    | 1.125               | 11.4                      |

| 28.5                    | 2.375               | 25.2                      |

| 41.5                    | 3.45                | 37.2                      |

| 55.5                    | 4.625               | 50                        |

| 71.5                    | 5.96                | NA                        |

| 239.5                   | 20                  | NA                        |

## Table 52. $R_{AIN}$ max for $f_{ADC} = 12 \text{ MHz}^{(1)}$

1. Guaranteed by design, not tested in production.

| Symbol | Parameter                    | Test conditions                                                                        | Тур  | Max  | Unit |

|--------|------------------------------|----------------------------------------------------------------------------------------|------|------|------|

| ET     | Total unadjusted error       | $f_{PCLK2} = 24 \text{ MHz},$                                                          | ±1.5 | ±2.5 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 12 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V | ±1   | ±2   |      |

| EG     | Gain error                   | $V_{REF+} = V_{DDA}$                                                                   | ±0.5 | ±1.5 | LSB  |

| ED     | Differential linearity error | T <sub>A</sub> = 25 °C                                                                 | ±1.5 | ±2   |      |

| EL     | Integral linearity error     | Measurements made after<br>ADC calibration                                             | ±1.5 | ±2   |      |

| Table 53. ADC accuracy - limi | ted test conditions <sup>(1)(2)</sup> |

|-------------------------------|---------------------------------------|

|-------------------------------|---------------------------------------|

1. ADC DC accuracy values are measured after internal calibration.

2. Preliminary values.

| Table | 54. ADC | accuracy <sup>(1) (2) (3)</sup> |

|-------|---------|---------------------------------|

|-------|---------|---------------------------------|

| Symbol | Parameter                    | Test conditions                                                     | Тур  | Max  | Unit |

|--------|------------------------------|---------------------------------------------------------------------|------|------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 24 MHz,                                        | ±2   | ±5   |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 12 MHz, R <sub>AIN</sub> < 10 kΩ,                | ±1.5 | ±2.5 |      |

| EG     | Gain error                   | $V_{DDA} = 2.4 V$ to 3.6 V<br>T <sub>A</sub> = Full operating range | ±1.5 | ±3   | LSB  |

| ED     | Differential linearity error | Measurements made after                                             | ±1.5 | ±2.5 |      |

| EL     | Integral linearity error     | ADC calibration                                                     | ±1.5 | ±4.5 | 1    |

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

3. Preliminary values.

Note:

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

| Symbol                               | Parameter                                                                                                                                                       | Min | Тур | Max <sup>(1)</sup> | Unit | Comments                                                                                                                                                                         |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                      | Offset error                                                                                                                                                    |     | -   | ±10                | mV   | Given for the DAC in 12-bit configuration                                                                                                                                        |  |

| Offset <sup>(1)</sup>                | (difference between measured value<br>at Code (0x800) and the ideal value =                                                                                     | -   | -   | ±3                 | LSB  | Given for the DAC in 10-bit at<br>V <sub>REF+</sub> = 3.6 V                                                                                                                      |  |

|                                      | V <sub>REF+</sub> /2)                                                                                                                                           | -   | -   | ±12                | LSB  | Given for the DAC in 12-bit at<br>V <sub>REF+</sub> = 3.6 V                                                                                                                      |  |

| Gain<br>error <sup>(1)</sup>         | Gain error                                                                                                                                                      | -   | -   | ±0.5               | %    | Given for the DAC in 12-bit configuration                                                                                                                                        |  |

| t <sub>SETTLING</sub> <sup>(1)</sup> | Settling time (full scale: for a 10-bit<br>input code transition between the<br>lowest and the highest input codes<br>when DAC_OUT reaches final value<br>±1LSB | -   | 3   | 4                  | μs   | $C_{LOAD} \le 50 \text{ pF}, \text{ R}_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                             |  |

| Update<br>rate <sup>(1)</sup>        | Max frequency for a correct<br>DAC_OUT change when small<br>variation in the input code (from code i<br>to i+1LSB)                                              | -   | -   | 1                  | MS/s | $C_{LOAD} \le 50 \text{ pF}, \text{ R}_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                             |  |

| <sup>t</sup> wakeup <sup>(1)</sup>   | Wakeup time from off state (Setting the ENx bit in the DAC Control register)                                                                                    | -   | 6.5 | 10                 | μs   | $\label{eq:loss} \begin{array}{l} C_{LOAD} \leq 50 \text{ pF}, \ R_{LOAD} \geq 5 \ k\Omega \\ \text{input code between lowest and} \\ \text{highest possible ones.} \end{array}$ |  |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio (to V <sub>DDA</sub> )<br>(static DC measurement                                                                                   | -   | -67 | -40                | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                                                                                 |  |

Table 55. DAC characteristics (continued)

1. Preliminary values.

2. Quiescent mode refer to the state of the DAC keeping steady value on the output, so no dynamic consumption is involved.

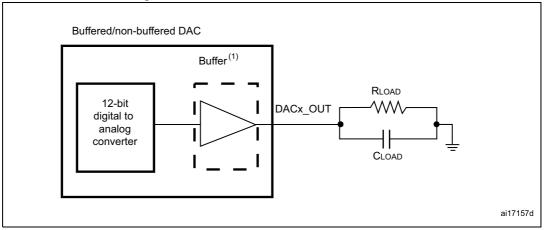

## Figure 37. 12-bit buffered /non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Max   | Min                   | Тур    | Мах    |

| E3     | -           | 12.000 | -     | -                     | 0.4724 | -      |

| е      | -           | 0.500  | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -     | -                     | 0.0394 | -      |

| k      | 0.0°        | 3.5°   | 7.0°  | 0.0°                  | 3.5°   | 7.0°   |

| CCC    | -           | -      | 0.080 | -                     | -      | 0.0031 |

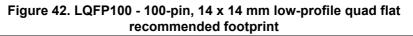

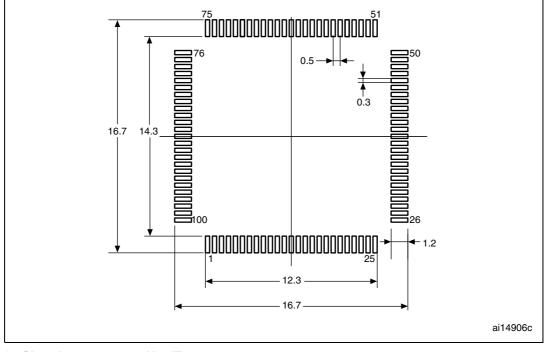

## Table 58. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

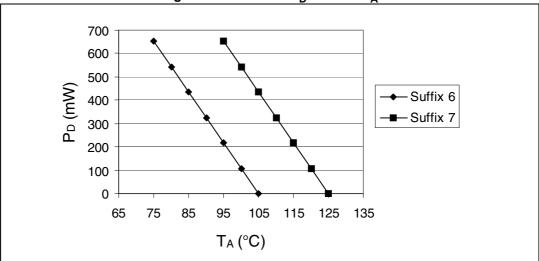

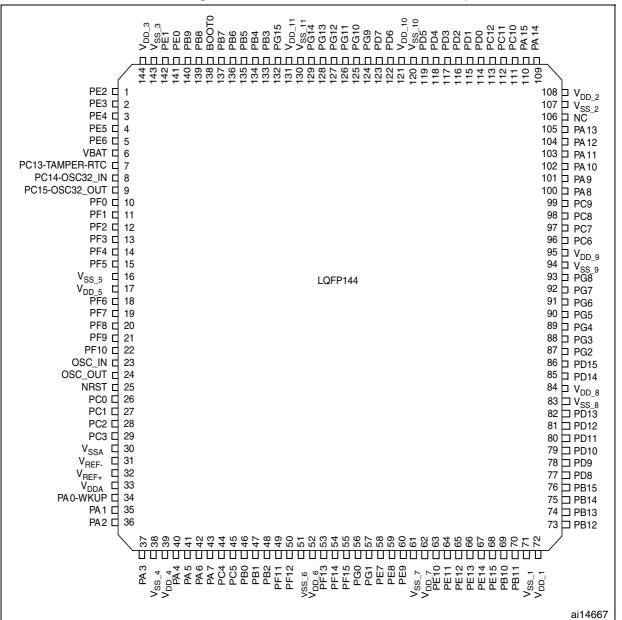

## 6.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 9: General operating conditions on page 38*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}\!/\!\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                          | Value | Unit |

|-----------------|------------------------------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP 144 - 20 × 20 mm / 0.5 mm pitch        | 35    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP 100 - 14 × 14 mm / 0.5 mm pitch | 40    | °C/W |

|                 | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch         | 49    |      |

#### Table 60. Package thermal characteristics

## 6.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

Using the values obtained in *Table 60*  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 40 °C/W

$$T_{Jmax} = 115 \text{ °C} + (40 \text{ °C/W} \times 134 \text{ mW}) = 115 \text{ °C} + 5.4 \text{ °C} = 120.4 \text{ °C}$$

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 61: Ordering information scheme*).