Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 24MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100vet6btr |

# **Contents**

| 2 | Desc | cription |                                                                 | . 10 |

|---|------|----------|-----------------------------------------------------------------|------|

|   | 2.1  | Device   | overview                                                        | 11   |

|   | 2.2  | Overvi   | ew                                                              | . 14 |

|   |      | 2.2.1    | ARM® Cortex®-M3 core with embedded Flash and SRAM               | 14   |

|   |      | 2.2.2    | Embedded Flash memory                                           | 14   |

|   |      | 2.2.3    | CRC (cyclic redundancy check) calculation unit                  | 14   |

|   |      | 2.2.4    | Embedded SRAM                                                   | 14   |

|   |      | 2.2.5    | FSMC (flexible static memory controller)                        | 14   |

|   |      | 2.2.6    | LCD parallel interface                                          | 14   |

|   |      | 2.2.7    | Nested vectored interrupt controller (NVIC)                     | 15   |

|   |      | 2.2.8    | External interrupt/event controller (EXTI)                      | 15   |

|   |      | 2.2.9    | Clocks and startup                                              | 15   |

|   |      | 2.2.10   | Boot modes                                                      | 15   |

|   |      | 2.2.11   | Power supply schemes                                            | 16   |

|   |      | 2.2.12   | Power supply supervisor                                         | 16   |

|   |      | 2.2.13   | Voltage regulator                                               | 16   |

|   |      | 2.2.14   | Low-power modes                                                 | 16   |

|   |      | 2.2.15   | DMA                                                             | 17   |

|   |      | 2.2.16   | RTC (real-time clock) and backup registers                      | 17   |

|   |      | 2.2.17   | Timers and watchdogs                                            | 17   |

|   |      | 2.2.18   | I <sup>2</sup> C bus                                            | 20   |

|   |      | 2.2.19   | Universal synchronous/asynchronous receiver transmitter (USART) | 20   |

|   |      | 2.2.20   | Universal asynchronous receiver transmitter (UART)              | 20   |

|   |      | 2.2.21   | Serial peripheral interface (SPI)                               | 20   |

|   |      | 2.2.22   | GPIOs (general-purpose inputs/outputs)                          | 21   |

|   |      | 2.2.23   | Remap capability                                                | 21   |

|   |      | 2.2.24   | ADC (analog-to-digital converter)                               | 21   |

|   |      | 2.2.25   | DAC (digital-to-analog converter)                               | 21   |

|   |      | 2.2.26   | Temperature sensor                                              | 22   |

|   |      | 2.2.27   | Serial wire JTAG debug port (SWJ-DP)                            | 22   |

| 3 | Pino | uts and  | pin descriptions                                                | . 23 |

# List of tables

| Table 1.               | Device summary                                                                      | 1  |

|------------------------|-------------------------------------------------------------------------------------|----|

| Table 2.               | STM32F100xx features and peripheral counts                                          |    |

| Table 3.               | Timer feature comparison                                                            |    |

| Table 4.               | High-density STM32F100xx pin definitions                                            |    |

| Table 5.               | FSMC pin definition                                                                 |    |

| Table 6.               | Voltage characteristics                                                             |    |

| Table 7.               | Current characteristics                                                             |    |

| Table 8.               | Thermal characteristics                                                             |    |

| Table 9.               | General operating conditions                                                        |    |

| Table 10.              | Operating conditions at power-up / power-down                                       |    |

| Table 11.              | Embedded reset and power control block characteristics                              |    |

| Table 12.              | Embedded internal reference voltage                                                 |    |

| Table 13.              | Maximum current consumption in Run mode, code with data processing                  |    |

| T-61- 44               | running from Flash                                                                  | 42 |

| Table 14.              | Maximum current consumption in Run mode, code with data processing running from RAM | 42 |

| Table 15.              | STM32F100xxB maximum current consumption in Sleep mode, code                        |    |

| T-51- 40               | running from Flash or RAM                                                           |    |

| Table 16.              | Typical and maximum current consumptions in Stop and Standby modes                  | 44 |

| Table 17.              | Typical current consumption in Run mode, code with data processing                  | 45 |

| Table 40               | running from Flash                                                                  |    |

| Table 18.              | Typical current consumption in Sleep mode, code running from Flash or RAM           |    |

| Table 19.              | Peripheral current consumption                                                      |    |

| Table 20.              | High-speed external user clock characteristics                                      |    |

| Table 21.              | Low-speed external user clock characteristics                                       |    |

| Table 22.              | HSE 4-24 MHz oscillator characteristics                                             |    |

| Table 23.              | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                      |    |

| Table 24.              | HSI oscillator characteristics                                                      |    |

| Table 25.              | LSI oscillator characteristics                                                      |    |

| Table 26.              | Low-power mode wakeup timings                                                       |    |

| Table 27.              | PLL characteristics                                                                 |    |

| Table 28.              | Flash memory characteristics                                                        |    |

| Table 29.              | Flash memory endurance and data retention                                           |    |

| Table 30.              | Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings                            |    |

| Table 31.              | Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings                           |    |

| Table 32.              | Asynchronous multiplexed PSRAM/NOR read timings                                     |    |

| Table 33.<br>Table 34. | , ,                                                                                 |    |

| Table 34.              | Synchronous multiplexed NOR/PSRAM read timings                                      |    |

| Table 35.              | Synchronous non-multiplexed NOR/PSRAM read timings                                  |    |

| Table 30.              | Synchronous non-multiplexed PSRAM write timings                                     |    |

| Table 37.              | EMS characteristics                                                                 |    |

| Table 39.              | EMI characteristics                                                                 |    |

| Table 39.              | ESD absolute maximum ratings                                                        |    |

| Table 40.              | Electrical sensitivities                                                            |    |

| Table 41.              | I/O current injection susceptibility                                                |    |

| Table 42.              | I/O static characteristics                                                          |    |

| Table 43.              | Output voltage characteristics                                                      |    |

| Table 44.              | Output voltage characteristics                                                      | /4 |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F100xC, STM32F100xD and STM32F100xE value line microcontrollers. In the rest of the document, the STM32F100xC, STM32F100xD and STM32F100xE are referred to as high-density value line devices.

This STM32F100xC, STM32F100xD and STM32F100xE datasheet should be read in conjunction with the STM32F100xx high-density ARM®-based 32-bit MCUs *reference manual (RM0059)*. For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F100xx high-density value line Flash programming manual (PM0072)*. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the http://infocenter.arm.com.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated for OS, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

# 2.2.18 I<sup>2</sup>C bus

The I<sup>2</sup>C bus interface can operate in multimaster and slave modes. It can support standard and fast modes.

It supports dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

The interface can be served by DMA and it supports SM Bus 2.0/PM Bus.

#### 2.2.19 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F100xx value line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The available USART interfaces communicate at up to 3 Mbit/s. They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART interfaces can be served by the DMA controller.

# 2.2.20 Universal asynchronous receiver transmitter (UART)

The STM32F100xx value line embeds 2 universal asynchronous receiver transmitters (UART4, and UART5).

The available UART interfaces support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability.

The UART interfaces can be served by the DMA controller.

### 2.2.21 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 12 Mbit/s in slave and master modes in full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits.

The SPIs can be served by the DMA controller.

**577**

Table 4. High-density STM32F100xx pin definitions (continued)

|         | Pins    |        |                   |                     | (;                       |                                                  | Alternate function                                                        | ons <sup>(4)</sup>       |

|---------|---------|--------|-------------------|---------------------|--------------------------|--------------------------------------------------|---------------------------------------------------------------------------|--------------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                   | Remap                    |

| 40      | 29      | 20     | PA4               | I/O                 | 1                        | PA4                                              | SPI1_NSS <sup>(8)</sup> /<br>USART2_CK <sup>(8)</sup><br>DAC_OUT1/ADC_IN4 | -                        |

| 41      | 30      | 21     | PA5               | I/O                 | 1                        | PA5                                              | SPI1_SCK <sup>(8)</sup><br>DAC_OUT2/ADC_IN5                               | -                        |

| 42      | 31      | 22     | PA6               | I/O                 | i                        | PA6                                              | SPI1_MISO <sup>(8)</sup> /<br>ADC_IN6 /<br>TIM3_CH1 <sup>(8)</sup>        | TIM1_BKIN /<br>TIM16_CH1 |

| 43      | 32      | 23     | PA7               | I/O                 | 1                        | PA7                                              | SPI1_MOSI <sup>(8)</sup> /<br>ADC_IN7 /<br>TIM3_CH2 <sup>(8)</sup>        | TIM1_CH1N/<br>TIM17_CH1  |

| 44      | 33      | 24     | PC4               | I/O                 | 1                        | PC4                                              | ADC_IN14 / TIM12_CH1                                                      | -                        |

| 45      | 34      | 25     | PC5               | I/O                 | -                        | PC5                                              | ADC_IN15 / TIM12_CH2                                                      | -                        |

| 46      | 35      | 26     | PB0               | I/O                 | -                        | PB0                                              | ADC_IN8/TIM3_CH3                                                          | TIM1_CH2N /<br>TIM13_CH1 |

| 47      | 36      | 27     | PB1               | I/O                 | 1                        | PB1                                              | ADC_IN9/TIM3_CH4 <sup>(8)</sup>                                           | TIM1_CH3N /<br>TIM14_CH1 |

| 48      | 37      | 28     | PB2               | I/O                 | FT                       | PB2/BOOT1                                        | -                                                                         | -                        |

| 49      | -       | 1      | PF11              | I/O                 | FT                       | PF11                                             | -                                                                         | -                        |

| 50      | -       | 1      | PF12              | I/O                 | FT                       | PF12                                             | FSMC_A6                                                                   | -                        |

| 51      | -       | -      | V <sub>SS_6</sub> | S                   | -                        | V <sub>SS_6</sub>                                | -                                                                         | -                        |

| 52      | -       | -      | V <sub>DD_6</sub> | S                   | -                        | V <sub>DD_6</sub>                                | -                                                                         | -                        |

| 53      | -       | ı      | PF13              | I/O                 | FT                       | PF13                                             | FSMC_A7                                                                   | -                        |

| 54      | -       | -      | PF14              | I/O                 | FT                       | PF14                                             | FSMC_A8                                                                   | -                        |

| 55      | -       | 1      | PF15              | I/O                 | FT                       | PF15                                             | FSMC_A9                                                                   | -                        |

| 56      | -       | -      | PG0               | I/O                 | FT                       | PG0                                              | FSMC_A10                                                                  | -                        |

| 57      | -       | 1      | PG1               | I/O                 | FT                       | PG1                                              | FSMC_A11                                                                  | -                        |

| 58      | 38      | -      | PE7               | I/O                 | FT                       | PE7                                              | FSMC_D4                                                                   | TIM1_ETR                 |

| 59      | 39      | -      | PE8               | I/O                 | FT                       | PE8                                              | FSMC_D5                                                                   | TIM1_CH1N                |

| 60      | 40      | -      | PE9               | I/O                 | FT                       | PE9                                              | FSMC_D6                                                                   | TIM1_CH1                 |

| 61      | -       | -      | V <sub>SS_7</sub> | S                   | -                        | V <sub>SS_7</sub>                                | -                                                                         | -                        |

| 62      | -       | -      | V <sub>DD_7</sub> | S                   | _                        | V <sub>DD_7</sub>                                | -                                                                         | -                        |

| 63      | 41      | -      | PE10              | I/O                 | FT                       | PE10                                             | FSMC_D7                                                                   | TIM1_CH2N                |

| 64      | 42      | 1      | PE11              | I/O                 | FT                       | PE11                                             | FSMC_D8                                                                   | TIM1_CH2                 |

| 65      | 43      | -      | PE12              | I/O                 | FT                       | PE12                                             | FSMC_D9                                                                   | TIM1_CH3N                |

Table 5. FSMC pin definition (continued)

|      | FS             | FSMC          |                        |  |  |  |

|------|----------------|---------------|------------------------|--|--|--|

| Pins | NOR/PSRAM/SRAM | NOR/PSRAM Mux | LQFP100 <sup>(1)</sup> |  |  |  |

| PG0  | A10            | -             | -                      |  |  |  |

| PG1  | A11            | -             | -                      |  |  |  |

| PE7  | D4             | DA4           | Yes                    |  |  |  |

| PE8  | D5             | DA5           | Yes                    |  |  |  |

| PE9  | D6             | DA6           | Yes                    |  |  |  |

| PE10 | D7             | DA7           | Yes                    |  |  |  |

| PE11 | D8             | DA8           | Yes                    |  |  |  |

| PE12 | D9             | DA9           | Yes                    |  |  |  |

| PE13 | D10            | DA10          | Yes                    |  |  |  |

| PE14 | D11            | DA11          | Yes                    |  |  |  |

| PE15 | D12            | DA12          | Yes                    |  |  |  |

| PD8  | D13            | DA13          | Yes                    |  |  |  |

| PD9  | D14            | DA14          | Yes                    |  |  |  |

| PD10 | D15            | DA15          | Yes                    |  |  |  |

| PD11 | A16            | A16           | Yes                    |  |  |  |

| PD12 | A17            | A17           | Yes                    |  |  |  |

| PD13 | A18            | A18           | Yes                    |  |  |  |

| PD14 | D0             | DA0           | Yes                    |  |  |  |

| PD15 | D1             | DA1           | Yes                    |  |  |  |

| PG2  | A12            | -             | -                      |  |  |  |

| PG3  | A13            | -             | -                      |  |  |  |

| PG4  | A14            | -             | -                      |  |  |  |

| PG5  | A15            | -             | -                      |  |  |  |

| PG6  | -              | -             | -                      |  |  |  |

| PG7  | -              | -             | -                      |  |  |  |

| PD0  | D2             | DA2           | Yes                    |  |  |  |

| PD1  | D3             | DA3           | Yes                    |  |  |  |

| PD3  | CLK            | CLK           | Yes                    |  |  |  |

| PD4  | NOE            | NOE           | Yes                    |  |  |  |

| PD5  | NWE            | NWE           | Yes                    |  |  |  |

| PD6  | NWAIT          | NWAIT         | Yes                    |  |  |  |

| PD7  | NE1            | NE1           | Yes                    |  |  |  |

| PG9  | NE2            | NE2           | -                      |  |  |  |

# On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- ullet all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6.

Table 19. Peripheral current consumption

| Peripheral        |                          | Typical consumption at 25 °C | Unit   |

|-------------------|--------------------------|------------------------------|--------|

|                   | DMA1                     | 12.50                        |        |

|                   | DMA2                     | 8.33                         |        |

| AHB (up to 24MHz) | FSMC                     | 28.33                        | μΑ/MHz |

|                   | CRC                      | 1.25                         |        |

|                   | BusMatrix <sup>(1)</sup> | 16.67                        |        |

Table 19. Peripheral current consumption (continued)

| Pe                    | ripheral           | Typical consumption at 25 °C | Unit       |

|-----------------------|--------------------|------------------------------|------------|

|                       | APB1-Bridge        | 3.75                         |            |

|                       | TIM2               | 17.08                        |            |

|                       | TIM3               | 17.50                        |            |

|                       | TIM4               | 17.08                        |            |

|                       | TIM5               | 17.08                        |            |

|                       | TIM6               | 4.58                         |            |

|                       | TIM7               | 4.17                         |            |

|                       | TIM12              | 10.42                        |            |

|                       | TIM13              | 7.08                         |            |

|                       | TIM14              | 7.08                         |            |

|                       | SPI2/I2S2          | 4.58                         |            |

| APB1 (up to 24 MHz)   | SPI3/I2S3          | 4.58                         | μΑ/MHz     |

| AFB1 (up to 24 Will2) | USART2             | 12.08                        | μΑνίνιι ιΖ |

|                       | USART3             | 12.08                        |            |

|                       | UART4              | 11.25                        |            |

|                       | UART5              | 10.83                        |            |

|                       | I2C1               | 10.42                        |            |

|                       | I2C2               | 10.42                        |            |

|                       | CEC                | 5.42                         |            |

|                       | DAC <sup>(2)</sup> | 7.92                         |            |

|                       | WWDG               | 2.92                         |            |

|                       | PWR                | 1.25                         |            |

|                       | ВКР                | 2.08                         |            |

|                       | IWDG               | 3.33                         |            |

| Symbol                                            | Parameter                                                                                                        | Conditions                                              | Min | Тур | Max | Unit |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| C <sub>L1</sub><br>C <sub>L2</sub> <sup>(3)</sup> | Recommended load capacitance versus equivalent serial resistance of the crystal (R <sub>S</sub> ) <sup>(4)</sup> | R <sub>S</sub> = 30 Ω                                   | -   | 30  | -   | pF   |

| i <sub>2</sub>                                    | HSE driving current                                                                                              | $V_{DD}$ = 3.3 V<br>$V_{IN}$ = $V_{SS}$ with 30 pF load | -   | -   | 1   | mA   |

| 9 <sub>m</sub>                                    | Oscillator transconductance                                                                                      | Startup                                                 | 25  | -   | 1   | mA/V |

| t <sub>SU(HSE)</sub>                              | Startup time                                                                                                     | V <sub>DD</sub> is stabilized                           | -   | 2   | ı   | ms   |

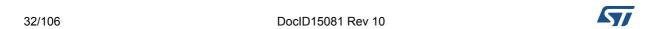

Table 22. HSE 4-24 MHz oscillator characteristics (1)(2)

- 1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Based on characterization, not tested in production.

- 3. It is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator. C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

- 4. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Figure 13. Typical application with an 8 MHz crystal

1.  $R_{\text{EXT}}$  value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 23*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which

is the series combination of  $C_{L1}$  and  $C_{L2}$ .

Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

For further details, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Caution:

To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L$  = 6 pF, and  $C_{stray}$  = 2 pF, then  $C_{L1}$  =  $C_{L2}$  = 8 pF.

Table 23. LSE oscillator characteristics  $(f_{LSE} = 32.768 \text{ kHz})^{(1)}$

| Symbol                                            | Parameter                                                                                                        | Conditions                                 |                         | Min | Тур | Max | Unit |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------|-----|-----|-----|------|

| $R_{F}$                                           | Feedback resistor                                                                                                |                                            | -                       | -   | 5   | -   | МΩ   |

| C <sub>L1</sub><br>C <sub>L2</sub> <sup>(2)</sup> | Recommended load capacitance versus equivalent serial resistance of the crystal (R <sub>S</sub> ) <sup>(3)</sup> | R <sub>S</sub> = 30 KΩ                     |                         | -   | -   | 15  | pF   |

| l <sub>2</sub>                                    | LSE driving current                                                                                              | $V_{DD} = 3.3 \text{ V}$ $V_{IN} = V_{SS}$ |                         | -   | -   | 1.4 | μΑ   |

| 9 <sub>m</sub>                                    | Oscillator transconductance                                                                                      | -                                          |                         | 5   | -   | -   | μA/V |

|                                                   | Startup time                                                                                                     | V <sub>DD</sub> is<br>stabilized           | T <sub>A</sub> = 50 °C  | -   | 1.5 | -   | S    |

|                                                   |                                                                                                                  |                                            | T <sub>A</sub> = 25 °C  | -   | 2.5 | -   |      |

|                                                   |                                                                                                                  |                                            | T <sub>A</sub> = 10 °C  | -   | 4   | -   |      |

| , (4)                                             |                                                                                                                  |                                            | T <sub>A</sub> = 0 °C   | -   | 6   | -   |      |

| t <sub>SU(LSE)</sub> <sup>(4)</sup>               |                                                                                                                  |                                            | T <sub>A</sub> = -10 °C | -   | 10  | -   |      |

|                                                   |                                                                                                                  |                                            | T <sub>A</sub> = -20 °C | -   | 17  | -   |      |

|                                                   |                                                                                                                  |                                            | T <sub>A</sub> = -30 °C | -   | 32  | -   |      |

|                                                   |                                                                                                                  |                                            | T <sub>A</sub> = -40 °C | -   | 60  | -   |      |

<sup>1.</sup> Based on characterization, not tested in production.

<sup>2.</sup> Refer to the note and caution paragraphs above the table.

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768 kHz. Refer to crystal manufacturer for more details

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

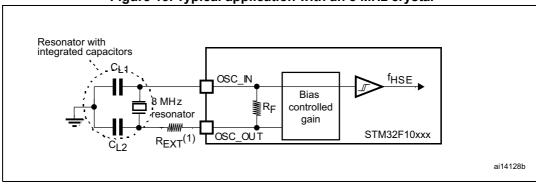

Figure 15. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

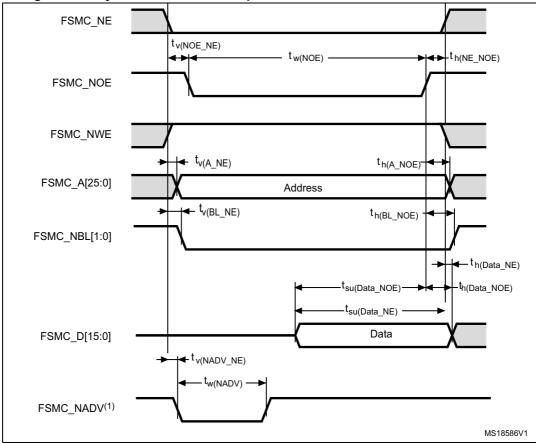

Figure 18. Asynchronous multiplexed PSRAM/NOR write waveforms

Table 33. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                              | Min                     | Max                     | Unit |

|---------------------------|--------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                       | 5T <sub>HCLK</sub> – 1  | 5T <sub>HCLK</sub> + 2  | ns   |

| t <sub>v(NWE_NE)</sub>    | FSMC_NEx low to FSMC_NWE low                           | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> + 1  | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low time                                      | 2T <sub>HCLK</sub> – 1  | 2T <sub>HCLK</sub> + 2  | ns   |

| t <sub>h(NE_NWE)</sub>    | FSMC_NWE high to FSMC_NE high hold time                | T <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                           | -                       | 7                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                          | 3                       | 5                       | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                     | T <sub>HCLK</sub> – 1   | T <sub>HCLK</sub> + 1   | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after FSMC_NADV high | T <sub>HCLK</sub> – 3   | -                       | ns   |

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high                  | 4T <sub>HCLK</sub>      | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                          | -                       | 1.6                     | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high                  | T <sub>HCLK</sub> – 1.5 | -                       | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid                           | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high                     | T <sub>HCLK</sub> – 5   | -                       | ns   |

<sup>1.</sup>  $C_L = 15 pF$ .

<sup>2.</sup> Preliminary values.

#### 5.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 38*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                    | Level/Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}=3.3$ V, $T_{A}=+25$ °C, $f_{HCLK}=24$ MHz, LQFP144 package, conforms to IEC 61000-4-2 | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}=3.3$ V, $T_{A}=+25$ °C, $f_{HCLK}=24$ MHz, LQFP144 package, conforms to IEC 61000-4-4 | 4A          |

Table 38. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### 5.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 42

Table 42. I/O current injection susceptibility

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

| I <sub>INJ</sub> | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

|                  | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

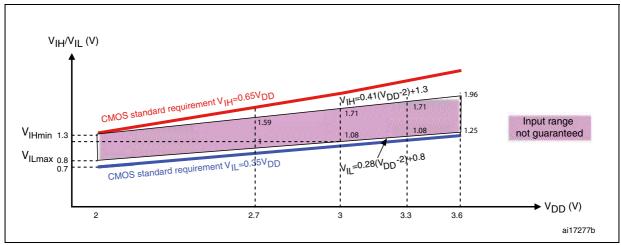

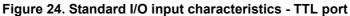

Figure 23. Standard I/O input characteristics - CMOS port

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 45*, respectively.

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Table 45. I/O AC characteristics<sup>(1)</sup>

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                                      | Max                | Unit |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--------------------|------|

| 10                                         | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$   | 2 <sup>(3)</sup>   | MHz  |

|                                            | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | C = 50 pE V = 2 V to 2 6 V                                      | 125 <sup>(3)</sup> | 20   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 125 <sup>(3)</sup> | ns   |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 10 <sup>(3)</sup>  | MHz  |

| 01                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | C <sub>I</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 25 <sup>(3)</sup>  | 20   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | - C <sub>L</sub> = 30 μr, ν <sub>DD</sub> = 2 ν to 3.6 ν        | 25 <sup>(3)</sup>  | ns   |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 24                 | MHz  |

|                                            | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 5 <sup>(3)</sup>   |      |

|                                            |                         |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 8 <sup>(3)</sup>   |      |

| 11                                         |                         |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 2.7 \text{ V}$   | 12 <sup>(3)</sup>  |      |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | C <sub>L</sub> = 30 pF, V <sub>DD</sub> = 2.7 V to 3.6 V        | 5 <sup>(3)</sup>   | ns   |

|                                            |                         |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 2.7 V          | 12 <sup>(3)</sup>  |      |

| -                                          | t <sub>EXTIPW</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                               | 10 <sup>(3)</sup>  | ns   |

The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F100xx reference manual for a description of GPIO Port configuration register.

<sup>2.</sup> The maximum frequency is defined in Figure 27.

<sup>3.</sup> Guaranteed by design, not tested in production.

#### SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 50* are preliminary values derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Refer to Section 5.3.13: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

Table 50. SPI characteristics

| Symbol                                               | Parameter                        | Conditions                                            | Min                | Max                | Unit |

|------------------------------------------------------|----------------------------------|-------------------------------------------------------|--------------------|--------------------|------|

| f <sub>SCK</sub>                                     | SPI clock frequency              | Master mode                                           | -                  | 12                 | MHz  |

| 1/t <sub>c(SCK)</sub>                                |                                  | Slave mode                                            | -                  | 12                 |      |

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time     | Capacitive load: C = 30 pF                            |                    | 8                  | ns   |

| DuCy(SCK)                                            | SPI slave input clock duty cycle | Slave mode                                            | 30                 | 70                 | %    |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time                   | Slave mode                                            | 4t <sub>PCLK</sub> | -                  |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                    | Slave mode                                            | 2t <sub>PCLK</sub> | -                  |      |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 24 MHz,<br>presc = 4 | 50                 | 60                 |      |

| t <sub>su(MI)</sub> (1)                              | Data input setup time            | Master mode                                           | 5                  | -                  |      |

| $t_{su(MI)}^{(1)}$                                   |                                  | Slave mode                                            | 5                  | -                  |      |

| t <sub>h(MI)</sub> (1)                               | Data input hold time             | Master mode                                           | 5                  | -                  |      |

| t <sub>h(SI)</sub> <sup>(1)</sup>                    | Data input noid time             | Slave mode                                            | 4                  | -                  | ns   |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time          | Slave mode, f <sub>PCLK</sub> = 24 MHz                | 0                  | 3t <sub>PCLK</sub> |      |

| $t_{dis(SO)}^{(1)(3)}$                               | Data output disable time         | Slave mode                                            | 2                  | 10                 |      |

| t <sub>v(SO)</sub> (1)                               | Data output valid time           | Slave mode (after enable edge)                        | -                  | 25                 |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time           | Master mode (after enable edge)                       | -                  | 5                  |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    |                                  | Slave mode (after enable edge)                        | 15                 | -                  |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time            | Master mode (after enable edge)                       | 2                  | -                  |      |

<sup>1.</sup> Preliminary values.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

| Table 51 | ADC | characteristics |

|----------|-----|-----------------|

|          |     |                 |

| Symbol                           | Parameter                                       | Conditions                              | Min                                                                        | Тур                | Max                | Unit               |

|----------------------------------|-------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| $V_{DDA}$                        | Power supply                                    | -                                       | 2.4                                                                        | -                  | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                      | -                                       | 2.4                                                                        | -                  | $V_{DDA}$          | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin       | -                                       | -                                                                          | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μΑ                 |

| f <sub>ADC</sub>                 | ADC clock frequency                             | -                                       | 0.6                                                                        | -                  | 12                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                   | -                                       | 0.05                                                                       | -                  | 1                  | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                      | f <sub>ADC</sub> = 12 MHz               | -                                                                          | -                  | 823                | kHz                |

|                                  |                                                 | -                                       | -                                                                          | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                        | -                                       | 0 (V <sub>SSA</sub> tied to ground)                                        | -                  | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                        | See Equation 1 and Table 52 for details | -                                                                          | -                  | 50                 | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                      | -                                       | -                                                                          | -                  | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor              | -                                       | -                                                                          | -                  | 8                  | pF                 |

| <b>4</b> (2)                     | Calibration time                                | f <sub>ADC</sub> = 12 MHz               | 5.9                                                                        |                    |                    | μs                 |

| t <sub>CAL</sub> <sup>(2)</sup>  |                                                 | -                                       | 83                                                                         |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)             | Injection trigger conversion latency            | f <sub>ADC</sub> = 12 MHz               | -                                                                          | -                  | 0.214              | μs                 |

| lat'-'                           |                                                 | -                                       | -                                                                          | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                      | f <sub>ADC</sub> = 12 MHz               | -                                                                          | -                  | 0.143              | μs                 |

|                                  | latency                                         | -                                       | -                                                                          | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>    | Sampling time                                   | f _ 40 MH=                              | 0.125                                                                      | -                  | 17.1               | μs                 |

|                                  |                                                 | $f_{ADC} = 12 \text{ MHz}$              | 1.5                                                                        | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                   | -                                       | 0                                                                          | 0                  | 1                  | μs                 |

|                                  | Total conversion time                           | f <sub>ADC</sub> = 12 MHz               | 1.17                                                                       | -                  | 21                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time (including sampling time) | -                                       | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                    | 1/f <sub>ADC</sub> |

- 1. Preliminary values.

- 2. Guaranteed by design, not tested in production.

- 3.  $V_{REF+}$  is internally connected to  $V_{DDA}$

- 4. For external triggers, a delay of  $1/f_{PCLK2}$  must be added to the latency specified in *Table 51*.

Equation 1:

$$R_{AIN}$$

max formula:  $T_S$

$$R_{AIN} < \frac{T_S}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The above formula (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

# 5.3.20 Temperature sensor characteristics

Table 56. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max       | Unit  |

|---------------------------------------|------------------------------------------------|------|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6       | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>        | Voltage at 25°C                                | 1.32 | 1.41 | 1.50      | V     |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                   | 4    | -    | 10        | μs    |

| T <sub>S_temp</sub> <sup>(3)(2)</sup> | ADC sampling time when reading the temperature | -    | -    | 17.1      | μs    |

<sup>1.</sup> Guaranteed by characterization, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> Shortest sampling time can be determined in the application by multiple iterations.

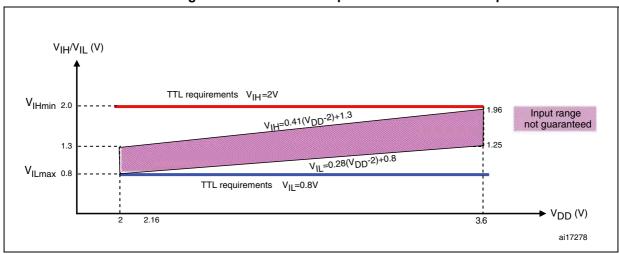

Figure 39. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

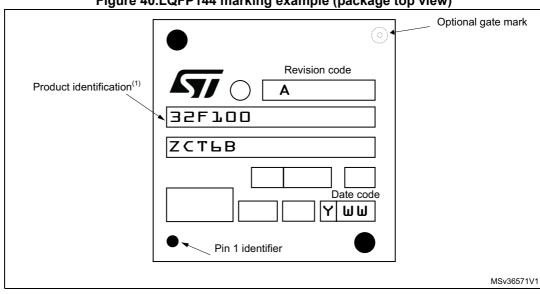

#### **Device marking for LQFP144**

The following figure shows the device marking for the LQFP144 package.

Figure 40.LQFP144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.