Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                              |

| Number of I/O              | 112                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 144-LQFP                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100zet7b |

## **Contents**

| 2 | Des  | cription |                                                                 | . 10 |

|---|------|----------|-----------------------------------------------------------------|------|

|   | 2.1  | Device   | overview                                                        | 11   |

|   | 2.2  | Overvi   | ew                                                              | . 14 |

|   |      | 2.2.1    | ARM® Cortex®-M3 core with embedded Flash and SRAM               | 14   |

|   |      | 2.2.2    | Embedded Flash memory                                           | 14   |

|   |      | 2.2.3    | CRC (cyclic redundancy check) calculation unit                  | 14   |

|   |      | 2.2.4    | Embedded SRAM                                                   | 14   |

|   |      | 2.2.5    | FSMC (flexible static memory controller)                        | 14   |

|   |      | 2.2.6    | LCD parallel interface                                          | 14   |

|   |      | 2.2.7    | Nested vectored interrupt controller (NVIC)                     | 15   |

|   |      | 2.2.8    | External interrupt/event controller (EXTI)                      | 15   |

|   |      | 2.2.9    | Clocks and startup                                              | 15   |

|   |      | 2.2.10   | Boot modes                                                      | 15   |

|   |      | 2.2.11   | Power supply schemes                                            | 16   |

|   |      | 2.2.12   | Power supply supervisor                                         | 16   |

|   |      | 2.2.13   | Voltage regulator                                               | 16   |

|   |      | 2.2.14   | Low-power modes                                                 | 16   |

|   |      | 2.2.15   | DMA                                                             | 17   |

|   |      | 2.2.16   | RTC (real-time clock) and backup registers                      | 17   |

|   |      | 2.2.17   | Timers and watchdogs                                            | 17   |

|   |      | 2.2.18   | I <sup>2</sup> C bus                                            | 20   |

|   |      | 2.2.19   | Universal synchronous/asynchronous receiver transmitter (USART) | 20   |

|   |      | 2.2.20   | Universal asynchronous receiver transmitter (UART)              | 20   |

|   |      | 2.2.21   | Serial peripheral interface (SPI)                               | 20   |

|   |      | 2.2.22   | GPIOs (general-purpose inputs/outputs)                          | 21   |

|   |      | 2.2.23   | Remap capability                                                | 21   |

|   |      | 2.2.24   | ADC (analog-to-digital converter)                               | 21   |

|   |      | 2.2.25   | DAC (digital-to-analog converter)                               | 21   |

|   |      | 2.2.26   | Temperature sensor                                              | 22   |

|   |      | 2.2.27   | Serial wire JTAG debug port (SWJ-DP)                            | 22   |

| 3 | Pino | outs and | pin descriptions                                                | . 23 |

## List of tables

| Table 45. | I/O AC characteristics                                               | 75  |

|-----------|----------------------------------------------------------------------|-----|

| Table 46. | NRST pin characteristics                                             |     |

| Table 47. | TIMx characteristics                                                 |     |

| Table 48. | I <sup>2</sup> C characteristics                                     |     |

| Table 49. | SCL frequency (f <sub>PCLK1</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V) |     |

| Table 50. | SPI characteristics                                                  |     |

| Table 51. | ADC characteristics                                                  |     |

| Table 52. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 12 MHz                   |     |

| Table 53. | ADC accuracy - limited test conditions                               |     |

| Table 54. | ADC accuracy                                                         |     |

| Table 55. | DAC characteristics                                                  |     |

| Table 56. | TS characteristics                                                   |     |

| Table 57. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package          |     |

|           | mechanical data                                                      | 92  |

| Table 58. | LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package          |     |

|           | mechanical data                                                      | 94  |

| Table 59. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package            |     |

|           | mechanical data                                                      | 97  |

| Table 60. | Package thermal characteristics                                      |     |

| Table 61. | Ordering information scheme                                          |     |

| Table 62  | Document revision history                                            | 104 |

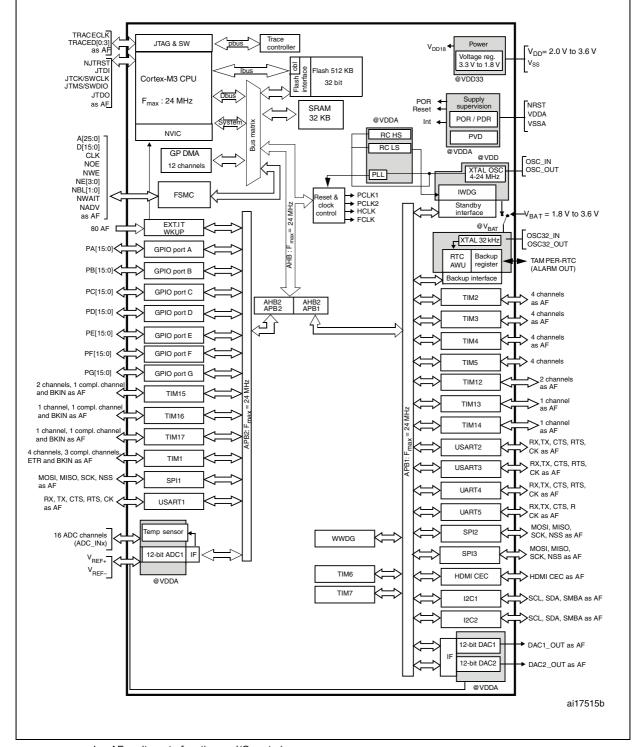

Figure 1. STM32F100xx value line block diagram

- 1. AF = alternate function on I/O port pin.

- 2.  $T_A = -40$  °C to +85 °C (junction temperature up to 105 °C) or  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

577

## 2.2 Overview

## 2.2.1 ARM® Cortex®-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F100xx value line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

## 2.2.2 Embedded Flash memory

Up to 512 Kbytes of embedded Flash memory is available for storing programs and data.

#### 2.2.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.2.4 Embedded SRAM

Up to 32 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

#### 2.2.5 FSMC (flexible static memory controller)

The FSMC is embedded in the high-density value line family. It has four Chip Select outputs supporting the following modes: SRAM, PSRAM, and NOR.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- No read FIFO

- Code execution from external memory

- No boot capability

- The targeted frequency is HCLK/2, so external access is at 12 MHz when HCLK is at 24 MHz

#### 2.2.6 LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to

# HDMI (high-definition multimedia interface) consumer electronics control (CEC)

The STM32F100xx value line embeds a HDMI-CEC controller that provides hardware support of consumer electronics control (CEC) (Appendix supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead.

## 2.2.22 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

#### 2.2.23 Remap capability

This feature allows the use of a maximum number of peripherals in a given application. Indeed, alternate functions are available not only on the default pins but also on other specific pins onto which they are remappable. This has the advantage of making board design and port usage much more flexible.

For details refer to *Table 4: High-density STM32F100xx pin definitions*; it shows the list of remappable alternate functions and the pins onto which they can be remapped. See the STM32F100xx reference manual for software considerations.

## 2.2.24 ADC (analog-to-digital converter)

The 12-bit analog to digital converter has up to 16 external channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 2.2.25 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in noninverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- up to 10-bit output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F100xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 2.2.26 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V < V<sub>DDA</sub> < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

#### 2.2.27 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

Table 4. High-density STM32F100xx pin definitions (continued)

|         | Pins    |        | Table 41 mgm      |                     |                          |                                                  | Alternate function                                                                   | ons <sup>(4)</sup> |

|---------|---------|--------|-------------------|---------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|--------------------|

| LQFP144 | LQFP100 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I/O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                              | Remap              |

| 14      | -       | -      | PF4               | I/O                 | FT                       | PF4                                              | FSMC_A4                                                                              | -                  |

| 15      | -       | -      | PF5               | I/O                 | FT                       | PF5                                              | FSMC_A5                                                                              | -                  |

| 16      | 10      | -      | V <sub>SS_5</sub> | S                   | -                        | V <sub>SS_5</sub>                                | -                                                                                    | -                  |

| 17      | 11      |        | $V_{DD\_5}$       | S                   | 1                        | $V_{DD_5}$                                       | -                                                                                    | -                  |

| 18      | -       | -      | PF6               | I/O                 | -                        | PF6                                              | -                                                                                    | -                  |

| 19      | -       | -      | PF7               | I/O                 | -                        | PF7                                              | -                                                                                    | -                  |

| 20      | -       | -      | PF8               | I/O                 | 1                        | PF8                                              | -                                                                                    | -                  |

| 21      | -       | -      | PF9               | I/O                 | -                        | PF9                                              | -                                                                                    | -                  |

| 22      | -       | -      | PF10              | I/O                 | -                        | PF10                                             | -                                                                                    | -                  |

| 23      | 12      | 5      | OSC_IN            | I                   | -                        | OSC_IN                                           | -                                                                                    | PD0 <sup>(7)</sup> |

| 24      | 13      | 6      | OSC_OUT           | 0                   | -                        | OSC_OUT                                          | -                                                                                    | PD1 <sup>(7)</sup> |

| 25      | 14      | 7      | NRST              | I/O                 | -                        | NRST                                             | -                                                                                    | -                  |

| 26      | 15      | 8      | PC0               | I/O                 | -                        | PC0                                              | ADC_IN10                                                                             | -                  |

| 27      | 16      | 9      | PC1               | I/O                 | -                        | PC1                                              | ADC_IN11                                                                             | -                  |

| 28      | 17      | 10     | PC2               | I/O                 | -                        | PC2                                              | ADC_IN12                                                                             | -                  |

| 29      | 18      | 11     | PC3               | I/O                 | -                        | PC3                                              | ADC_IN13                                                                             | -                  |

| 30      | 19      | 12     | V <sub>SSA</sub>  | S                   | -                        | V <sub>SSA</sub>                                 | -                                                                                    | -                  |

| 31      | 20      |        | $V_{REF}$         | S                   | 1                        | $V_{REF}$                                        | -                                                                                    | -                  |

| 32      | 21      | -      | V <sub>REF+</sub> | S                   | 1                        | V <sub>REF+</sub>                                | -                                                                                    | -                  |

| 33      | 22      | 13     | $V_{DDA}$         | S                   | -                        | $V_{DDA}$                                        | -                                                                                    | -                  |

| 34      | 23      | 14     | PA0-WKUP          | I/O                 | 1                        | PA0                                              | WKUP/USART2_CTS <sup>(8)</sup> ADC_IN0 TIM2_CH1_ETR TIM5_CH1                         | -                  |

| 35      | 24      | 15     | PA1               | I/O                 | ı                        | PA1                                              | USART2_RTS <sup>(8)</sup><br>ADC_IN1/<br>TIM5_CH2/TIM2_CH2 <sup>(8)</sup>            | -                  |

| 36      | 25      | 16     | PA2               | I/O                 | -                        | PA2                                              | USART2_TX <sup>(8)</sup> /TIM5_CH3<br>ADC_IN2/ TIM15_CH1<br>TIM2_CH3 <sup>(8)</sup>  | -                  |

| 37      | 26      | 17     | PA3               | I/O                 | -                        | PA3                                              | USART2_RX <sup>(8)</sup> /TIM5_CH4<br>ADC_IN3/TIM2_CH4 <sup>(8)</sup> /<br>TIM15_CH2 | -                  |

| 38      | 27      | 18     | V <sub>SS_4</sub> | S                   | -                        | V <sub>SS_4</sub>                                | -                                                                                    | -                  |

| 39      | 28      | 19     | V <sub>DD_4</sub> | S                   | -                        | $V_{DD\_4}$                                      | -                                                                                    | -                  |

## 5.1.6 Power supply scheme

Figure 9. Power supply scheme  $V_{\mathsf{BAT}}$ Backup circuitry (OSC32K,RTC, Wake-up logic Backup registers) Ю GP I/Os Logic Kernel logic (CPU, Digital & Memories)  $V_{DD}$ 1/2/3/4/5 Regulator VSS 5 × 100 nF + 1 × 4.7 µF 1/2/3/4/5  $V_{DDA}$ VREF+ Analog:  $V_{REF}$ ADC/DAC RCs, PLL  $V_{SSA}$ ai14125e

**Caution:** In *Figure* 9, the 4.7  $\mu$ F capacitor must be connected to  $V_{DD3}$ .

577

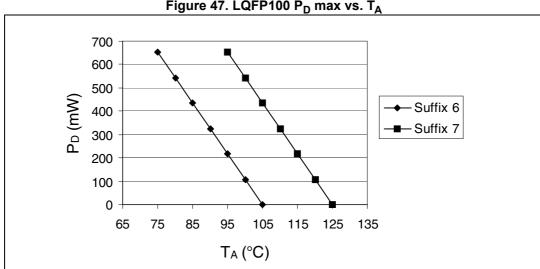

**Symbol Parameter Conditions** Min Max Unit LQFP144 666 Power dissipation at T<sub>A</sub> = 85 °C for suffix 6 or  $T_A = 105$  °C for suffix  $7^{(2)}$  $P_D$ LQFP100 434 mW LQFP64 444 Maximum power dissipation -40 85 Ambient temperature for 6 °C suffix version Low power dissipation<sup>(3)</sup> -40 105 TA Maximum power dissipation -40 105 Ambient temperature for 7 °C suffix version Low power dissipation<sup>(3)</sup> -40 125 -40 105 6 suffix version °C TJ Junction temperature range 7 suffix version -40 125

Table 9. General operating conditions (continued)

- 1. When the ADC is used, refer to Table 51: ADC characteristics.

- If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Section 6.5: Thermal characteristics on page 100).

- In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Section 6.5: Thermal characteristics on page 100).

Note: It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation

## 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

Table 10. Operating conditions at power-up / power-down

| Symbol | Parameter                      | Min | Max | Unit  |

|--------|--------------------------------|-----|-----|-------|

| t      | V <sub>DD</sub> rise time rate | 0   | ∞   | µs/V  |

| ι√DD   | V <sub>DD</sub> fall time rate | 20  | ∞   | μ5/ ν |

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Table 11. Embedded reset and power control block characteristics

| Symbol                               | Parameter                | Conditions                  | Min                | Тур  | Max  | Unit |

|--------------------------------------|--------------------------|-----------------------------|--------------------|------|------|------|

|                                      |                          | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 | V    |

|                                      |                          | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 | V    |

|                                      |                          | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 | V    |

|                                      |                          | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 | V    |

|                                      |                          | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 | V    |

|                                      |                          | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 | V    |

|                                      |                          | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 | V    |

|                                      | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

| $V_{PVD}$                            | detector level selection | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | V    |

|                                      |                          | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 | V    |

|                                      |                          | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 | V    |

|                                      |                          | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 | V    |

|                                      |                          | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  | V    |

|                                      |                          | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | V    |

|                                      |                          | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    | V    |

|                                      |                          | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis           | -                           | -                  | 100  | -    | mV   |

|                                      | Power on/power down      | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| $V_{POR/PDR}$                        | reset threshold          | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis           | -                           | -                  | 40   | -    | mV   |

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization      | -                           | 1.5                | 2.5  | 4.5  | ms   |

<sup>1.</sup> The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR}/\mbox{PDR}}$  value.

577

<sup>2.</sup> Guaranteed by design, not tested in production.

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- ullet all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6.

Table 19. Peripheral current consumption

| Pe                | ripheral                 | Typical consumption at 25 °C | Unit   |

|-------------------|--------------------------|------------------------------|--------|

|                   | DMA1                     | 12.50                        |        |

|                   | DMA2                     | 8.33                         |        |

| AHB (up to 24MHz) | FSMC                     | 28.33                        | μΑ/MHz |

|                   | CRC                      | 1.25                         |        |

|                   | BusMatrix <sup>(1)</sup> | 16.67                        |        |

Table 19. Peripheral current consumption (continued)

| Pe                    | ripheral           | Typical consumption at 25 °C | Unit       |

|-----------------------|--------------------|------------------------------|------------|

|                       | APB1-Bridge        | 3.75                         |            |

|                       | TIM2               | 17.08                        |            |

|                       | TIM3               | 17.50                        |            |

|                       | TIM4               | 17.08                        |            |

|                       | TIM5               | 17.08                        |            |

|                       | TIM6               | 4.58                         |            |

|                       | TIM7               | 4.17                         |            |

|                       | TIM12              | 10.42                        |            |

|                       | TIM13              | 7.08                         |            |

|                       | TIM14              | 7.08                         |            |

|                       | SPI2/I2S2          | 4.58                         |            |

| APB1 (up to 24 MHz)   | SPI3/I2S3          | 4.58                         | μΑ/MHz     |

| AFB1 (up to 24 Will2) | USART2             | 12.08                        | μΑνίνιι ιΖ |

|                       | USART3             | 12.08                        |            |

|                       | UART4              | 11.25                        |            |

|                       | UART5              | 10.83                        |            |

|                       | I2C1               | 10.42                        |            |

|                       | I2C2               | 10.42                        |            |

|                       | CEC                | 5.42                         |            |

|                       | DAC <sup>(2)</sup> | 7.92                         |            |

|                       | WWDG               | 2.92                         |            |

|                       | PWR                | 1.25                         |            |

|                       | ВКР                | 2.08                         |            |

|                       | IWDG               | 3.33                         |            |

| Symbol                                                               | Parameter                                           | Conditions                       | Min                | Тур | Max                | Unit |

|----------------------------------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                                                 | User external clock source frequency <sup>(1)</sup> |                                  | 1                  | 8   | 24                 | MHz  |

| V <sub>HSEH</sub>                                                    | OSC_IN input pin high level voltage <sup>(1)</sup>  |                                  | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                                                    | OSC_IN input pin low level voltage <sup>(1)</sup>   | -                                | V <sub>SS</sub>    | -   | 0.3V <sub>DD</sub> | V    |

| $\begin{matrix} t_{w(\text{HSE})} \\ t_{w(\text{HSE})} \end{matrix}$ | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5                  | ı   | -                  | ns   |

| $t_{r(HSE)} \ t_{f(HSE)}$                                            | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -                  | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>                                                 | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -                  | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                                                | Duty cycle <sup>(1)</sup>                           | -                                | 45                 | -   | 55                 | %    |

| ΙL                                                                   | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -   | ±1                 | μA   |

Table 20. High-speed external user clock characteristics

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under the ambient temperature and supply voltage conditions summarized in *Table 9*.

Symbol **Parameter Conditions** Min Тур Max Unit User external clock source 1000 32.768 kHz f<sub>LSE\_ext</sub> frequency<sup>(1)</sup> OSC32\_IN input pin high level  $V_{LSEH}$  $0.7V_{DD}$  $V_{DD} \\$ voltage<sup>(1)</sup> ٧ OSC32 IN input pin low level  $0.3V_{DD}$  $V_{LSEL}$  $V_{SS}$ voltage<sup>(1)</sup> t<sub>w(LSE)</sub> OSC32\_IN high or low time<sup>(1)</sup> 450 t<sub>w(LSE)</sub> ns t<sub>r(LSE)</sub> OSC32 IN rise or fall time<sup>(1)</sup> 50  $t_{f(LSE)}$ OSC32 IN input capacitance<sup>(1)</sup> 5 pF C<sub>in(LSE)</sub> Duty cycle<sup>(1)</sup> DuCy<sub>(LSE)</sub> 30 70 %

$V_{SS} \leq V_{IN} \leq V_{DD}$

±1

μΑ

Table 21. Low-speed external user clock characteristics

$I_{\mathsf{L}}$

OSC32 IN Input leakage current

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>1.</sup> Guaranteed by design, not tested in production.

Table 34. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

| Symbol                       | Parameter                                      | Min  | Max | Unit |

|------------------------------|------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                                | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)          | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)         | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                  | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high                 | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)       | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625)     | 2    | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>    | FSMC_CLK high to FSMC_NOE low                  | -    | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                  | 0.5  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid            | -    | 12  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid          | 0    | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>    | FSMC_A/D[15:0] valid data before FSMC_CLK high | 6    | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>     | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high          | 8    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high           | 2    | -   | ns   |

<sup>1.</sup>  $C_L = 15 pF$ .

<sup>2.</sup> Preliminary values.

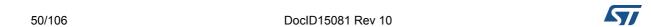

Figure 22. Synchronous non-multiplexed PSRAM write timings

Table 37. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                       | Parameter                                  | Min  | Max | Unit |

|------------------------------|--------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                            | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)      | -    | 2   | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)     | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low              | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high             | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | 2    | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>    | FSMC_CLK low to FSMC_NWE low               | -    | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 1    | -   | ns   |

| t <sub>d(CLKL-Data)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK low | -    | 6   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 7    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high       | 2    | -   | ns   |

| t <sub>d(CLKL-NBLH)</sub>    | FSMC_CLK low to FSMC_NBL high              | 1    | -   | ns   |

<sup>1.</sup> C<sub>L</sub> = 15 pF.

<sup>2.</sup> Preliminary values.

#### 5.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 38*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                    | Level/Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}=3.3$ V, $T_{A}=+25$ °C, $f_{HCLK}=24$ MHz, LQFP144 package, conforms to IEC 61000-4-2 | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}=3.3$ V, $T_{A}=+25$ °C, $f_{HCLK}=24$ MHz, LQFP144 package, conforms to IEC 61000-4-4 | 4A          |

Table 38. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

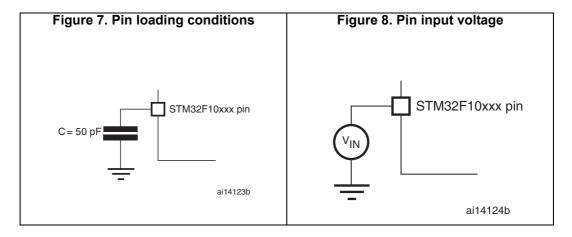

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 45*, respectively.

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Table 45. I/O AC characteristics<sup>(1)</sup>

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                                      | Max                | Unit |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--------------------|------|

| 10                                         | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$   | 2 <sup>(3)</sup>   | MHz  |

|                                            | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | C = 50 pE V = 2 V to 2 6 V                                      | 125 <sup>(3)</sup> | - ns |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 125 <sup>(3)</sup> |      |

| 01                                         | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 10 <sup>(3)</sup>  | MHz  |

|                                            | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | C <sub>I</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 25 <sup>(3)</sup>  | ns   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | - C <sub>L</sub> = 30 μr, ν <sub>DD</sub> = 2 ν to 3.6 ν        | 25 <sup>(3)</sup>  |      |

| 11                                         | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 24                 | MHz  |

|                                            | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 5 <sup>(3)</sup>   |      |

|                                            |                         |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 2.7 \text{ V}$   | 12 <sup>(3)</sup>  |      |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | C <sub>L</sub> = 30 pF, V <sub>DD</sub> = 2.7 V to 3.6 V        | 5 <sup>(3)</sup>   | ns   |

|                                            |                         |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 2.7 V          | 12 <sup>(3)</sup>  |      |

| -                                          | t <sub>EXTIPW</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                               | 10 <sup>(3)</sup>  | ns   |

The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F100xx reference manual for a description of GPIO Port configuration register.

<sup>2.</sup> The maximum frequency is defined in Figure 27.

<sup>3.</sup> Guaranteed by design, not tested in production.

#### 5.3.16 TIMx characteristics

The parameters given in *Table 47* are guaranteed by design.

Refer to Section 5.3.13: I/O current injection characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                           | Conditions <sup>(1)</sup>     | Min  | Max                     | Unit                 |

|------------------------|-------------------------------------|-------------------------------|------|-------------------------|----------------------|

| t <sub>res(TIM)</sub>  | Timer resolution time               | -                             | 1    | -                       | t <sub>TIMxCLK</sub> |

|                        | Time resolution time                | f <sub>TIMxCLK</sub> = 24 MHz | 41.7 | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock                |                               | 0    | f <sub>TIMxCLK</sub> /2 | MHz                  |

|                        | frequency on CHx <sup>(2)</sup>     | f <sub>TIMxCLK</sub> = 24 MHz | 0    | 12                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                    | -                             | -    | 16                      | bit                  |

| tcounter               | 16-bit counter clock period         | -                             | 1    | 65536                   | t <sub>TIMxCLK</sub> |

|                        | when the internal clock is selected | f <sub>TIMxCLK</sub> = 24 MHz | i    | 2730                    | μs                   |

| t <sub>MAX_COUNT</sub> | Maximum possible count              | -                             | -    | 65536 × 65536           | t <sub>TIMxCLK</sub> |

|                        | iviaximum possible count            | f <sub>TIMxCLK</sub> = 24 MHz | -    | 178                     | s                    |

Table 47. TIMx characteristics

#### 5.3.17 Communications interfaces

#### I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 48* are preliminary values derived from tests performed under the ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

The STM32F100xx value line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 48*. Refer also to *Section 5.3.13: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4, TIM5, TIM15, TIM16 and TIM17 timers

<sup>2.</sup> CHx is used as a general term to refer to CH1 to CH4 for TIM1, TIM2, TIM3, TIM4 and TIM5, to the CH1 to CH2 for TIM15, and to CH1 for TIM16 and TIM17.

## **Device marking for LQFP100**

The following figure shows the device marking for the LQFP100 package.

Product identification<sup>(1)</sup>

STM32F100

Revision code

Pin 1 identifier

Optional gate mark

Revision code

Pin 1 identifier

Figure 43.LQFP100 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

MSv36572V1

Using the values obtained in  $Table 60 T_{Jmax}$  is calculated as follows:

For LQFP100, 40 °C/W

$$T_{Jmax}$$

= 115 °C + (40 °C/W × 134 mW) = 115 °C + 5.4 °C = 120.4 °C

This is within the range of the suffix 7 version parts ( $-40 < T_J < 125$  °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see Table 61: Ordering information scheme).

Figure 47. LQFP100 P<sub>D</sub> max vs. T<sub>A</sub>