Welcome to **E-XFL.COM**

# **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Data ila                        |                                                                           |

|---------------------------------|---------------------------------------------------------------------------|

| Details                         |                                                                           |

| Product Status                  | Obsolete                                                                  |

| Core Processor                  | ARM® Cortex®-A5                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 600MHz                                                                    |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                    |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                                       |

| Graphics Acceleration           | Yes                                                                       |

| Display & Interface Controllers | LCD, Touchscreen                                                          |

| Ethernet                        | 10/100Mbps (1)                                                            |

| ATA                             | -                                                                         |

| SB                              | USB 2.0 (3)                                                               |

| oltage - I/O                    | 1.2V, 1.8V, 3.3V                                                          |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                         |

| ecurity Features                | AES, SHA, TDES, TRNG                                                      |

| ackage / Case                   | 361-TFBGA                                                                 |

| upplier Device Package          | 361-TFBGA (16x16)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d42a-cur |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 13.5.14 L2CC Raw Interrupt Status Register

Name:L2CC\_RISR Address:0x00A0021C Access:Read-only

| 31     | 30    | 29    | 28    | 27    | 26    | 25    | 24     |

|--------|-------|-------|-------|-------|-------|-------|--------|

| _      | ı     | _     | ı     | -     | ı     | 1     | _      |

| 23     | 22    | 21    | 20    | 19    | 18    | 17    | 16     |

| _      | -     | _     | -     | -     | -     | 1     | _      |

| 15     | 14    | 13    | 12    | 11    | 10    | 9     | 8      |

| _      | 1     | _     | 1     | -     | 1     | 1     | DECERR |

| 7      | 6     | 5     | 4     | 3     | 2     | 1     | 0      |

| SLVERR | ERRRD | ERRRT | ERRWD | ERRWT | PARRD | PARRT | ECNTR  |

**ECNTR: Event Counter 1/0 Overflow Increment**

PARRT: Parity Error on L2 Tag RAM, Read

PARRD: Parity Error on L2 Data RAM, Read

ERRWT: Error on L2 Tag RAM, Write ERRWD: Error on L2 Data RAM, Write

ERRRT: Error on L2 Tag RAM, Read ERRRD: Error on L2 Data RAM, Read

SLVERR: SLVERR from L3 memory DECERR: DECERR from L3 memory

0: No interrupt has been generated.

1: The input lines have triggered an interrupt.

# 28.6.39 PIO Additional Interrupt Modes Mask Register

Name:PIO\_AIMMR

Address:0xFC06A0B8 (PIOA), 0xFC06B0B8 (PIOB), 0xFC06C0B8 (PIOC), 0xFC0680B8 (PIOD), 0xFC06D0B8 (PIOE)

Access:Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# P0-P31: IO Line Index

Selects the IO event type triggering an interrupt.

0: The interrupt source is a both-edge detection event.

1: The interrupt source is described by the registers PIO\_ELSR and PIO\_FRLHSR.

Table 30-4: SMC Multiplexed Signal Translation

|                        |             | Signal Name |           |

|------------------------|-------------|-------------|-----------|

|                        | 16-b        | oit Bus     | 8-bit Bus |

| Device Type            | 1 x 16-bit  | 2 x 8-bit   | 1 x 8-bit |

| Byte Access Type (BAT) | Byte Select | Byte Write  | _         |

| NBS0_A0                | NBS0        | _           | A0        |

| NWE_NWR0               | NWE         | NWR0        | NWE       |

| NBS1_NWR1              | NBS1        | NWR1        | _         |

| A1                     | A1          | A1          | A1        |

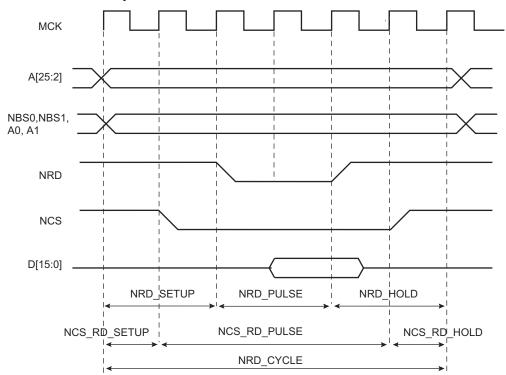

#### 30.10 Standard Read and Write Protocols

In the following sections, the Byte Access Type is not considered. Byte select lines (NBS0 to NBS1) always have the same timing as the A address bus. NWE represents either the NWE signal in byte select access type or one of the byte write lines (NWR0 to NWR1) in byte write access type. NWR0 to NWR1 have the same timings and protocol as NWE. In the same way, NCS represents one of the NCS[0..3] chip select lines.

#### 30.10.1 Read Waveforms

The read cycle is shown on Figure 30-7.

The read cycle starts with the address setting on the memory address bus, i.e.,:

{A[25:2], A1, A0} for 8-bit devices

{A[25:2], A1} for 16-bit devices

Figure 30-7: Standard Read Cycle

# Table 32-37: 16 bpp 4:2:2 interleaved Mode 3

| Mem addr     | 0x3 | }  |    |     |      |    |    |    | 0x2 | )  |    |     |       |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |       |   |   |   |

|--------------|-----|----|----|-----|------|----|----|----|-----|----|----|-----|-------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|-------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27   | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19    | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3     | 2 | 1 | 0 |

| Pixel 16 bpp |     |    |    | Y1[ | 7:0] |    |    |    |     |    |    | Cb0 | [7:0] |    |    |    |     |    |    | Y0[ | 7:0] |    |   |   |     |   |   | Cr0 | [7:0] |   |   |   |

# 32.6.5.3 4:2:2 Semiplanar Mode Frame Buffer Memory Mapping

# Table 32-38: 4:2:2 Semiplanar Luminance Memory Mapping, Little Endian Organization for Byte 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | 3  |    |     |      |    |    |    | 0x2 | )  |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |      |   |   |   |

|--------------|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27   | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| Pixel 16 bpp |     |    |    | Y3[ | 7:0] |    |    |    |     |    |    | Y2[ | 7:0] |    |    |    |     |    |    | Y1[ | 7:0] |    |   |   |     |   |   | Y0[ | 7:0] |   |   |   |

# Table 32-39: 4:2:2 Semiplanar Chrominance Memory Mapping, Little Endian Organization for Byte 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | }  |    |     |       |    |    |    | 0x2 |    |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |       |   |   |   |

|--------------|-----|----|----|-----|-------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|-------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27    | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3     | 2 | 1 | 0 |

| Pixel 16 bpp |     |    |    | Cb2 | [7:0] |    |    |    |     |    |    | Cr2 | 7:0] |    |    |    |     |    |    | Cb0 | 7:0] |    |   |   |     |   |   | Cr0 | [7:0] |   |   |   |

# 32.6.5.4 4:2:2 Planar Mode Frame Buffer Memory Mapping

# Table 32-40: 4:2:2 Planar Mode Luminance Memory Mapping, Little Endian Organization for Byte 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | }  |    |     |      |    |    |    | 0x2 | )  |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |      |   |   |   |

|--------------|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27   | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| Pixel 16 bpp |     |    |    | Y3[ | 7:0] |    |    |    |     |    |    | Y2[ | 7:0] |    |    |    |     |    |    | Y1[ | 7:0] |    |   |   |     |   |   | Y0[ | 7:0] |   |   |   |

# Table 32-41: 4:2:2 Planar Mode Chrominance Memory Mapping, Little Endian Organization for Byte 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | }  |    |     |      |    |    |    | 0x2 | )  |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |      |   |   |   |

|--------------|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27   | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| Pixel 16 bpp |     |    |    | C3[ | 7:0] |    |    |    |     |    |    | C2[ | 7:0] |    |    |    |     |    |    | C1[ | 7:0] |    |   |   |     |   |   | C0[ | 7:0] |   |   |   |

# 32.6.5.5 4:2:0 Planar Mode Frame Buffer Memory Mapping

In Planar Mode, the three video components Y, Cr and Cb are split into three memory areas and stored in a raster-scan order. These three memory planes are contiguous and always aligned on a 32-bit boundary.

# Table 32-42: 4:2:0 Planar Mode Luminance Memory Mapping, Little Endian Organization for Byte 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | 3  |    |     |      |    |    |    | 0x2 |    |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |      |   |   |   |

|--------------|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27   | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| Pixel 12 bpp |     |    |    | Y3[ | 7:0] |    |    |    |     |    |    | Y2[ | 7:0] |    |    |    |     |    |    | Y1[ | 7:0] |    |   |   |     |   |   | Y0[ | 7:0] |   |   |   |

#### 32.6.12.3 YUV Mode Fetch Performance

Table 32-51: Single Stream for 0 Wait State Memory

|             | Pixels/Cycle         | Rotation Peak Random Men  | nory Access (pixels/cycle) | Scaling Burst Mode or                 |

|-------------|----------------------|---------------------------|----------------------------|---------------------------------------|

| YUV Mode    | Memory<br>Burst Mode | Rotation Optimization (1) | Normal Mode                | Rotation Optimization Is<br>Available |

| 32 bpp AYUV | 2                    | 1                         | 0.2                        | Supported                             |

| 16 bpp 422  | 4                    | Not Supported             | Not Supported              | Supported                             |

Note 1: Rotation optimization = AHB lock asserted on consecutive single access

Table 32-52: Multiple Stream for 0 Wait State Memory

|                         |                      | Rotation Peak Random Mem  |                                 | Scaling Burst Mode or                 |

|-------------------------|----------------------|---------------------------|---------------------------------|---------------------------------------|

| YUV Mode                | Memory Burst<br>Mode | Rotation Optimization     | Normal Mode                     | Rotation Optimization Is<br>Available |

| 16 bpp 422 semiplanar   | 8 Y, 4 UV            | 1 Y, 1 UV (2 streams)     | 0.2 Y 0.2 UV (2 streams)        | Supported                             |

| 16 bpp 422 planar       | 8 Y, 8 U, 8 V        | 1 Y, 1 U, 1 V (3 streams) | 0.2 Y, 0.2 U, 0.2 V (3 streams) | Supported                             |

| 12 bpp 4:2:0 semiplanar | 8 Y, 4 UV            | 1 Y, 1 UV (2 streams)     | 0.2 Y 0.2 UV (2 streams)        | Supported                             |

| 12 bpp 4:2:0 planar     | 8 Y, 8 U, 8 V        | 1 Y, 1 U, 1 V (3 streams) | 0.2 Y, 0.2 U, 0.2 V (3 streams) | Supported                             |

**Note:** In order to provide more bandwidth, when multiple streams are used to transfer Y, UV, U or V components, two AHB interfaces are recommended or multiple AXI ID are required.

Table 32-53: YUV Planar Overall Performance 1 AHB Interface for 0 Wait State Memory

|                         | _                    | Rotation Peak Random Men | Scaling Burst Mode or |                                       |

|-------------------------|----------------------|--------------------------|-----------------------|---------------------------------------|

| YUV Mode                | Memory Burst<br>Mode | Rotation Optimization    | Normal Mode           | Rotation Optimization Is<br>Available |

| 16 bpp 422 semiplanar   | 4                    | 0.66                     | 0.132                 | Supported                             |

| 16 bpp 422 planar       | 4                    | 0.5                      | 0.1                   | Supported                             |

| 12 bpp 4:2:0 semiplanar | 5.32                 | 0.8                      | 0.16                  | Supported                             |

| 12 bpp 4:2:0 planar     | 5.32                 | 0.66                     | 0.132                 | Supported                             |

**Note:** In order to provide more bandwidth, when multiple streams are used to transfer Y, UV, U or V components, two AHB interfaces are recommended or multiple AXI ID are required.

#### 32.6.13 Input FIFO

The LCD module includes one input FIFO per overlay. These input FIFOs are used to buffer the AHB burst and serialize the stream of pixels.

# **32.6.14 Output FIFO**

The LCD module includes one output FIFO that stores the blended pixel.

© 2017 Microchip Technology Inc. DS60001525A-page 635

# **SAMA5D4 SERIES**

# 32.7.5 LCD Controller Configuration Register 4

Name: LCDC\_LCDCFG4 Address:0xF0000010 Access: Read/Write

| 31 | 30  | 29 | 28 | 27 | 26 | 25  | 24 |  |  |

|----|-----|----|----|----|----|-----|----|--|--|

| _  | _   | _  | _  | _  |    | RPF |    |  |  |

| 23 | 22  | 21 | 20 | 19 | 18 | 17  | 16 |  |  |

|    | RPF |    |    |    |    |     |    |  |  |

|    |     |    |    |    |    |     |    |  |  |

| 15 | 14  | 13 | 12 | 11 | 10 | 9   | 8  |  |  |

| _  | _   | _  | _  | _  |    | PPL |    |  |  |

|    |     |    |    |    |    |     | _  |  |  |

| 7  | 6   | 5  | 4  | 3  | 2  | 1   | 0  |  |  |

|    | PPL |    |    |    |    |     |    |  |  |

#### **RPF: Number of Active Row Per Frame**

Number of active lines in the frame. The frame height is equal to (RPF+1) lines.

#### **PPL: Number of Pixels Per Line**

Number of pixel in the frame. The number of active pixels in the frame is equal to (PPL+1) pixels.

# **SAMA5D4 SERIES**

# 32.7.52 Overlay 1 Configuration Register 7

Name: LCDC\_OVR1CFG7 Address:0xF0000188 Access: Read/Write

| 31 | 30   | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|----|------|----|----|----|----|----|----|--|--|

| _  | _    | _  | _  | _  | -  | ı  | -  |  |  |

| 23 | 22   | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|    | RKEY |    |    |    |    |    |    |  |  |

| 15 | 14   | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|    |      |    | GK | EY |    |    |    |  |  |

| 7  | 6    | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|    | BKEY |    |    |    |    |    |    |  |  |

#### **RKEY: Red Color Component Chroma Key**

Reference Red chroma key used to match the Red color of the current overlay.

# **GKEY: Green Color Component Chroma Key**

Reference Green chroma key used to match the Green color of the current overlay.

# **BKEY: Blue Color Component Chroma Key**

Reference Blue chroma key used to match the Blue color of the current overlay.

# 32.7.91 High End Overlay V DMA Head Register

Name: LCDC\_HEOVHEAD

Address:0xF000037C

Access: Read/Write

| 31 | 30 | 29 | 28  | 27  | 26 | 25 | 24 |

|----|----|----|-----|-----|----|----|----|

|    |    |    | VHE | EAD |    |    |    |

| 23 | 22 | 21 | 20  | 19  | 18 | 17 | 16 |

|    |    |    | VHE | EAD |    |    |    |

| 15 | 14 | 13 | 12  | 11  | 10 | 9  | 8  |

|    |    |    | VHE | EAD |    |    |    |

| 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0  |

|    |    |    | VHE | EAD |    |    |    |

# **VHEAD: DMA Head Pointer**

The Head Pointer points to a new descriptor.

# 32.7.140 High End Overlay CLUT Register x

Name: LCDC\_HEOCLUTx [x=0..255]

Address:0xF0001200 Access: Read/Write

| 31 | 30 | 29 | 28  | 27  | 26 | 25 | 24 |

|----|----|----|-----|-----|----|----|----|

|    |    |    | ACI | _UT |    |    |    |

| 23 | 22 | 21 | 20  | 19  | 18 | 17 | 16 |

|    |    |    | RCI | LUT |    |    |    |

| 15 | 14 | 13 | 12  | 11  | 10 | 9  | 8  |

|    |    |    | GCI | LUT |    |    |    |

| 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0  |

|    |    |    | BCI | _UT |    |    |    |

#### **BCLUT: Blue Color Entry**

This field indicates the 8-bit width Blue color of the color lookup table.

# **GCLUT: Green Color Entry**

This field indicates the 8-bit width Green color of the color lookup table.

#### **RCLUT: Red Color Entry**

This field indicates the 8-bit width Red color of the color lookup table.

# **ACLUT: Alpha Color Entry**

This field indicates the 8-bit width Alpha channel of the color lookup table.

#### 35.6.14.3 Entering Attached State

When no device is connected, the USB FSDP and FSDM signals are tied to GND by 15 K $\Omega$  pull-downs integrated in the hub downstream ports. When a device is attached to an hub downstream port, the device connects a 1.5 K $\Omega$  pull-up on FSDP. The USB bus line goes into IDLE state, FSDP is pulled-up by the device 1.5 K $\Omega$  resistor to 3.3V and FSDM is pulled-down by the 15 K $\Omega$  resistor to GND of the host.

After pull-up connection, the device enters the powered state. The transceiver remains disabled until bus activity is detected.

In case of low power consumption need, the device can be stopped. When the device detects the VBUS, the software must enable the USB transceiver by enabling the EN\_UDPHS bit in UDPHS\_CTRL register.

The software can detach the pull-up by setting DETACH bit in UDPHS\_CTRL register.

#### 35.6.14.4 From Powered State to Default State (Reset)

After its connection to a USB host, the USB device waits for an end-of-bus reset. The unmasked flag ENDRESET is set in the UDPHS\_IEN register and an interrupt is triggered.

Once the ENDRESET interrupt has been triggered, the device enters Default State. In this state, the UDPHS software must:

- Enable the default endpoint, setting the EPT\_ENABL flag in the UDPHS\_EPTCTLENB[0] register and, optionally, enabling the interrupt for endpoint 0 by writing 1 in EPT\_0 of the UDPHS\_IEN register. The enumeration then begins by a control transfer.

- · Configure the Interrupt Mask Register which has been reset by the USB reset detection

- · Enable the transceiver.

In this state, the EN\_UDPHS bit in UDPHS\_CTRL register must be enabled.

#### 35.6.14.5 From Default State to Address State (Address Assigned)

After a Set Address standard device request, the USB host peripheral enters the address state.

**Warning**: before the device enters address state, it must achieve the Status IN transaction of the control transfer, i.e., the UDPHS device sets its new address once the TX\_COMPLT flag in the UDPHS\_EPTCTL[0] register has been received and cleared.

To move to address state, the driver software sets the DEV\_ADDR field and the FADDR\_EN flag in the UDPHS\_CTRL register.

#### 35.6.14.6 From Address State to Configured State (Device Configured)

Once a valid Set Configuration standard request has been received and acknowledged, the device enables endpoints corresponding to the current configuration. This is done by setting the BK\_NUMBER, EPT\_TYPE, EPT\_DIR and EPT\_SIZE fields in the UDPHS\_EPTCFGx registers and enabling them by setting the EPT\_ENABL flag in the UDPHS\_EPTCTLENBx registers, and, optionally, enabling corresponding interrupts in the UDPHS\_IEN register.

#### 35.6.14.7 Entering Suspend State (Bus Activity)

When a Suspend (no bus activity on the USB bus) is detected, the DET\_SUSPD signal in the UDPHS\_STA register is set. This triggers an interrupt if the corresponding bit is set in the UDPHS\_IEN register. This flag is cleared by writing to the UDPHS\_CLRINT register. Then the device enters Suspend mode.

In this state bus powered devices must drain less than 500 µA from the 5V VBUS. As an example, the microcontroller switches to slow clock, disables the PLL and main oscillator, and goes into Idle mode. It may also switch off other devices on the board.

The UDPHS device peripheral clocks can be switched off. Resume event is asynchronously detected.

#### 35.6.14.8 Receiving a Host Resume

In Suspend mode, a resume event on the USB bus line is detected asynchronously, transceiver and clocks disabled (however the pull-up should not be removed).

Once the resume is detected on the bus, the signal WAKE\_UP in the UDPHS\_INTSTA is set. It may generate an interrupt if the corresponding bit in the UDPHS\_IEN register is set. This interrupt may be used to wake up the core, enable PLL and main oscillators and configure clocks.

#### 35.6.14.9 Sending an External Resume

In Suspend State it is possible to wake up the host by sending an external resume.

The device waits at least 5 ms after being entered in Suspend State before sending an external resume.

The device must force a K state from 1 to 15 ms to resume the host.

# 37.8.48 GMAC Broadcast Frames Transmitted Register

Name:GMAC\_BCFT

Address:0xF802010C (0), 0xFC02810C (1)

Access: Read-only

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|----|----|----|----|----|----|----|----|

|    |    |    | BF | TX |    |    |    |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|    |    |    | BF | TX |    |    |    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|    |    |    | BF | TX |    |    |    |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | ·  |    | BF | TX |    |    |    |

#### **BFTX: Broadcast Frames Transmitted without Error**

Broadcast frames transmitted without error. This register counts the number of broadcast frames successfully transmitted without error, i.e., no underrun and not too many retries. Excludes pause frames.

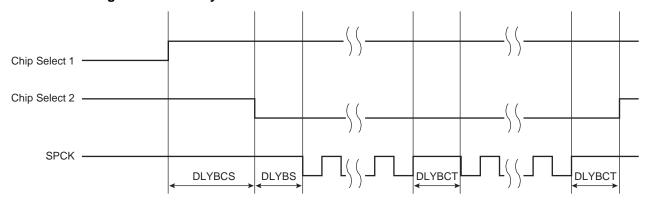

Figure 39-9: Programmable Delays

#### 39.7.3.5 Peripheral Selection

The serial peripherals are selected through the assertion of the NPCS0 to NPCS3 signals. By default, all NPCS signals are high before and after each transfer.

- Fixed Peripheral Select Mode: SPI exchanges data with only one peripheral.

Fixed Peripheral Select mode is enabled by clearing the PS bit in the SPI\_MR. In this case, the current peripheral is defined by the PCS field in the SPI\_MR and the PCS field in the SPI\_TDR has no effect.

- Variable Peripheral Select Mode: Data can be exchanged with more than one peripheral without having to reprogram the NPCS field in the SPI\_MR.

Variable Peripheral Select mode is enabled by setting the PS bit in the SPI\_MR. The PCS field in the SPI\_TDR is used to select the current peripheral. This means that the peripheral selection can be defined for each new data. The value to write in the SPI\_TDR has the following format:

[xxxxxxx(7-bit) + LASTXFER(1-bit)<sup>(1)</sup>+ xxxx(4-bit) + PCS (4-bit) + DATA (8 to 16-bit)] with PCS equals the chip select to assert, as defined in Section 39.8.4 "SPI Transmit Data Register" and LASTXFER bit at 0 or 1 depending on the CSAAT bit.

Note 1: Optional

CSAAT, LASTXFER and CSNAAT bits are discussed in Section 39.7.3.9 "Peripheral Deselection with DMA".

If LASTXFER is used, the command must be issued after writing the last character. Instead of LASTXFER, the user can use the SPIDIS command. After the end of the DMA transfer, it is necessary to wait for the TXEMPTY flag and then write SPIDIS into the SPI Control Register (SPI\_CR). This does not change the configuration register values). The NPCS is disabled after the last character transfer. Then, another DMA transfer can be started if the SPIEN has previously been written in the SPI\_CR.

#### 39.7.3.6 SPI Direct Access Memory Controller (DMAC)

In both Fixed and Variable modes, the Direct Memory Access Controller (DMAC) can be used to reduce processor overhead.

The fixed peripheral selection allows buffer transfers with a single peripheral. Using the DMAC is an optimal means, as the size of the data transfer between the memory and the SPI is either 8 bits or 16 bits. However, if the peripheral selection is modified, the SPI\_MR must be reprogrammed.

The variable peripheral selection allows buffer transfers with multiple peripherals without reprogramming the SPI\_MR. Data written in the SPI\_TDR is 32 bits wide and defines the real data to be transmitted and the destination peripheral. Using the DMAC in this mode requires 32-bit wide buffers, with the data in the LSBs and the PCS and LASTXFER fields in the MSBs. However, the SPI still controls the number of bits (8 to 16) to be transferred through MISO and MOSI lines with the chip select configuration registers. This is not the optimal means in terms of memory size for the buffers, but it provides a very effective means to exchange data with several peripherals without any intervention of the processor.

#### 39.7.3.7 Peripheral Chip Select Decoding

The user can program the SPI to operate with up to 15 slave peripherals by decoding the four chip select lines, NPCS0 to NPCS3 with an external decoder/demultiplexer (refer to Figure 39-10). This can be enabled by setting the PCSDEC bit in the SPI\_MR.

When operating without decoding, the SPI makes sure that in any case only one chip select line is activated, i.e., one NPCS line driven low at a time. If two bits are defined low in a PCS field, only the lowest numbered chip select is driven low.

When operating with decoding, the SPI directly outputs the value defined by the PCS field on the NPCS lines of either SPI\_MR or SPI\_TDR (depending on PS).

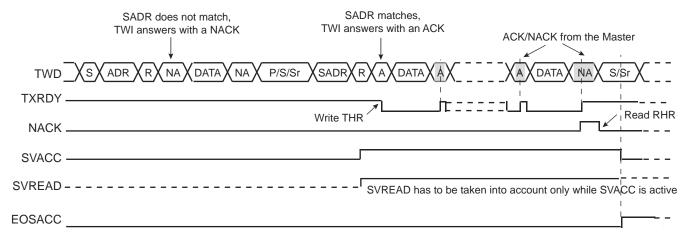

#### 40.7.5.4 Data Transfer

· Read Operation

The Read mode is defined as a data requirement from the master.

After a START or a REPEATED START condition is detected, the decoding of the address starts. If the slave address (SADR) is decoded, SVACC is set and SVREAD indicates the direction of the transfer.

Until a STOP or REPEATED START condition is detected, TWI continues sending data loaded in the TWI\_THR.

If a STOP condition or a REPEATED START + an address different from SADR is detected, SVACC is reset.

Figure 40-22 describes the write operation.

Figure 40-22: Read Access Ordered by a Master

Note 1: When SVACC is low, the state of SVREAD becomes irrelevant.

- 2: TXRDY is reset when data has been transmitted from TWI\_THR to the internal shifter and set when this data has been acknowledged or non acknowledged.

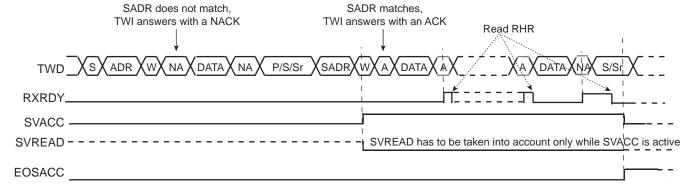

- · Write Operation

The Write mode is defined as a data transmission from the master.

After a START or a REPEATED START, the decoding of the address starts. If the slave address is decoded, SVACC is set and SVREAD indicates the direction of the transfer (SVREAD is low in this case).

Until a STOP or REPEATED START condition is detected, TWI stores the received data in the TWI\_RHR.

If a STOP condition or a REPEATED START + an address different from SADR is detected, SVACC is reset.

Figure 40-23 describes the write operation.

Figure 40-23: Write Access Ordered by a Master

Note 1: When SVACC is low, the state of SVREAD becomes irrelevant.

2: RXRDY is set when data has been transmitted from the internal shifter to the TWI\_RHR and reset when this data is read.

# 41.9.3 SSC Receive Clock Mode Register

Name:SSC\_RCMR

Address:0xF8008010 (0), 0xFC014010 (1)

Access:Read/Write

| 31 | 30 | 29  | 28      | 27  | 26   | 25 | 24 |

|----|----|-----|---------|-----|------|----|----|

|    |    |     | PER     | IOD |      |    |    |

| 23 | 22 | 21  | 20      | 19  | 18   | 17 | 16 |

|    |    |     | STT     | DLY |      |    |    |

| 15 | 14 | 13  | 12      | 11  | 10   | 9  | 8  |

| _  | _  | _   | STOP    |     | STAF | RT |    |

| 7  | 6  | 5   | 4       | 3   | 2    | 1  | 0  |

| CI | ⟨G | CKI | CKO CKS |     |      | KS |    |

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

#### **CKS: Receive Clock Selection**

| Value | Name | Description     |  |  |  |

|-------|------|-----------------|--|--|--|

| 0     | MCK  | Divided Clock   |  |  |  |

| 1     | TK   | TK Clock signal |  |  |  |

| 2     | RK   | RK pin          |  |  |  |

# **CKO: Receive Clock Output Mode Selection**

| Value | Name       | Description                                                   |  |  |  |

|-------|------------|---------------------------------------------------------------|--|--|--|

| 0     | NONE       | None, RK pin is an input                                      |  |  |  |

| 1     | CONTINUOUS | Continuous Receive Clock, RK pin is an output                 |  |  |  |

| 2     | TRANSFER   | Receive Clock only during data transfers, RK pin is an output |  |  |  |

#### **CKI: Receive Clock Inversion**

- 0: The data inputs (Data and Frame Sync signals) are sampled on Receive Clock falling edge. The Frame Sync signal output is shifted out on Receive Clock rising edge.

- 1: The data inputs (Data and Frame Sync signals) are sampled on Receive Clock rising edge. The Frame Sync signal output is shifted out on Receive Clock falling edge.

CKI affects only the Receive Clock and not the output clock signal.

#### **CKG: Receive Clock Gating Selection**

| Value | Name       | Description                           |  |  |  |

|-------|------------|---------------------------------------|--|--|--|

| 0     | CONTINUOUS | None                                  |  |  |  |

| 1     | EN_RF_LOW  | Receive Clock enabled only if RF Low  |  |  |  |

| 2     | EN_RF_HIGH | Receive Clock enabled only if RF High |  |  |  |

© 2017 Microchip Technology Inc. DS60001525A-page 1231

# 41.9.14 SSC Interrupt Enable Register

Name:SSC\_IER

Address:0xF8008044 (0), 0xFC014044 (1)

Access:Write-only

| 31 | 30 | 29    | 28    | 27    | 26    | 25      | 24    |

|----|----|-------|-------|-------|-------|---------|-------|

| _  | _  | -     | _     | -     | _     | _       | -     |

| 23 | 22 | 21    | 20    | 19    | 18    | 17      | 16    |

| _  | _  | _     | _     | _     | -     | -       | _     |

|    |    |       |       |       |       |         |       |

| 15 | 14 | 13    | 12    | 11    | 10    | 9       | 8     |

| _  | _  | -     | _     | RXSYN | TXSYN | CP1     | CP0   |

|    |    |       |       |       |       |         |       |

| 7  | 6  | 5     | 4     | 3     | 2     | 1       | 0     |

| _  | _  | OVRUN | RXRDY | -     | _     | TXEMPTY | TXRDY |

#### **TXRDY: Transmit Ready Interrupt Enable**

0: No effect.

1: Enables the Transmit Ready Interrupt.

# **TXEMPTY: Transmit Empty Interrupt Enable**

0: No effect.

1: Enables the Transmit Empty Interrupt.

#### **RXRDY: Receive Ready Interrupt Enable**

0: No effect.

1: Enables the Receive Ready Interrupt.

# **OVRUN: Receive Overrun Interrupt Enable**

0: No effect.

1: Enables the Receive Overrun Interrupt.

# **CP0: Compare 0 Interrupt Enable**

0: No effect.

1: Enables the Compare 0 Interrupt.

#### **CP1: Compare 1 Interrupt Enable**

0: No effect.

1: Enables the Compare 1 Interrupt.

# **TXSYN: Tx Sync Interrupt Enable**

0: No effect.

1: Enables the Tx Sync Interrupt.

# **RXSYN: Rx Sync Interrupt Enable**

0: No effect.

1: Enables the Rx Sync Interrupt.

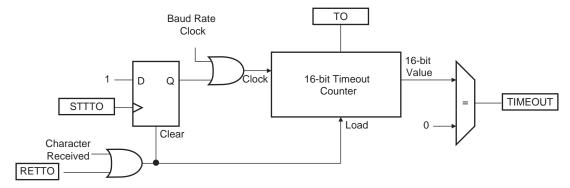

Figure 44-23: Receiver Timeout Block Diagram

Table 44-10 gives the maximum timeout period for some standard baud rates.

Table 44-10: Maximum Timeout Period

| Baud Rate (bit/s) | Bit Time (µs) | Timeout (ms) |

|-------------------|---------------|--------------|

| 600               | 1,667         | 109,225      |

| 1,200             | 833           | 54,613       |

| 2,400             | 417           | 27,306       |

| 4,800             | 208           | 13,653       |

| 9,600             | 104           | 6,827        |

| 14,400            | 69            | 4,551        |

| 19,200            | 52            | 3,413        |

| 28,800            | 35            | 2,276        |

| 38,400            | 26            | 1,704        |

| 56,000            | 18            | 1,170        |

| 57,600            | 17            | 1,138        |

| 200,000           | 5             | 328          |

#### 44.6.3.12 Framing Error

The receiver is capable of detecting framing errors. A framing error happens when the stop bit of a received character is detected at level 0. This can occur if the receiver and the transmitter are fully desynchronized.

A framing error is reported in US\_CSR.FRAME. FRAME is asserted in the middle of the stop bit as soon as the framing error is detected. It is cleared by writing a '1' to US\_CR.RSTSTA.

# **SAMA5D4 SERIES**

# **CLKO: Clock Output Select**

- 0: The USART does not drive the SCK pin.

- 1: The USART drives the SCK pin if USCLKS does not select the external clock SCK.

#### **WRDBT: Wait Read Data Before Transfer**

- 0: The character transmission starts as soon as a character is written into US\_THR (assuming TXRDY was set).

- 1: The character transmission starts when a character is written and only if RXRDY flag is cleared (Receive Holding Register has been read).

# 46.7.1 TC Channel Control Register

Name:TC\_CCRx [x=0..2]

Access:Write-only

| 31 | 30 | 29 | 28 | 27 | 26    | 25     | 24    |

|----|----|----|----|----|-------|--------|-------|

| _  | _  | _  | _  | _  | -     | -      | _     |

| 23 | 22 | 21 | 20 | 19 | 18    | 17     | 16    |

| _  | _  | _  | -  | -  | -     | -      | _     |

| 15 | 14 | 13 | 12 | 11 | 10    | 9      | 8     |

| _  | _  | _  | _  | _  | _     | _      | _     |

| 7  | 6  | 5  | 4  | 3  | 2     | 1      | 0     |

| _  | _  | _  | _  | _  | SWTRG | CLKDIS | CLKEN |

#### **CLKEN: Counter Clock Enable Command**

0: No effect.

1: Enables the clock if CLKDIS is not 1.

# **CLKDIS: Counter Clock Disable Command**

0: No effect.

1: Disables the clock.

# **SWTRG: Software Trigger Command**

0: No effect.

1: A software trigger is performed: the counter is reset and the clock is started.

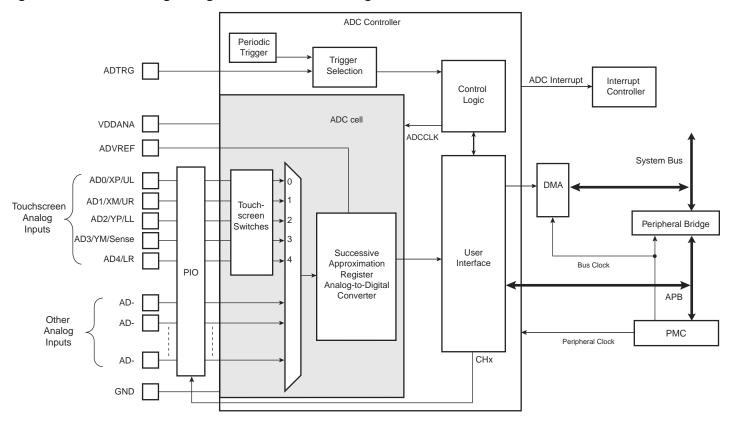

# 48.3 Block Diagram

Figure 48-1: Analog-to-Digital Converter Block Diagram with Touchscreen Mode

# 48.4 Signal Description

Table 48-1: ADC Pin Description

| Pin Name | Description           |  |  |

|----------|-----------------------|--|--|

| VDDANA   | Analog Power Supply   |  |  |

| ADVREF   | Reference Voltage     |  |  |

| AD0-AD4  | Analog input Channels |  |  |

| ADTRG    | External Trigger      |  |  |

DS60001525A-page 1490

# **SAMA5D4 SERIES**

# 51.5.7 TDES Key 1 Word Register x

Name: TDES\_KEY1WRx Address:0xFC04C020 Access:Write-only

| 31    | 30 | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

|-------|----|----|----|----|----|----|----|--|--|--|

| KEY1W |    |    |    |    |    |    |    |  |  |  |

| 23    | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

| KEY1W |    |    |    |    |    |    |    |  |  |  |

| 15    | 14 | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

| KEY1W |    |    |    |    |    |    |    |  |  |  |

| 7     | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

| KEY1W |    |    |    |    |    |    |    |  |  |  |

# KEY1W: Key 1 Word

The two 32-bit Key 1 Word registers are used to set the 64-bit cryptographic key used for encryption/decryption.

KEY1W0 refers to the first word of the key and KEY1W1 to the last one.

These registers are write-only to prevent the key from being read by another application.

In XTEA mode, the key is defined on 128 bits. These registers contain the 64 LSB bits of the encryption/decryption key.