Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | H8SX                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 35MHz                                                                           |

| Connectivity               | SCI, SmartCard                                                                  |

| Peripherals                | DMA, PWM, WDT                                                                   |

| Number of I/O              | 82                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 120-TQFP                                                                        |

| Supplier Device Package    | 120-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df61656cn35ftv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

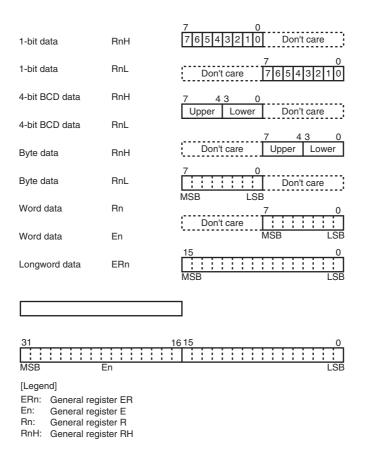

# 2.6 Data Formats

The H8SX CPU can process 1-bit, 4-bit BCD, 8-bit (byte), 16-bit (word), and 32-bit (longword) data.

Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

### 2.6.1 General Register Data Formats

Figure 2.12 shows the data formats in general registers.

RENESAS

| Bit | Bit Name | Initial<br>value | R/W    | Description                                                                                                                                                                                                                           |  |  |  |

|-----|----------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2   | TGFC     | 0                | R/(W)* | Input Capture/Output Compare Flag C                                                                                                                                                                                                   |  |  |  |

|     |          |                  |        | Status flag that indicates the occurrence of TGRC input capture or compare match in channels 0 and 3.                                                                                                                                 |  |  |  |

|     |          |                  |        | In channels 1, 2, 4, and 5, bit 2 is reserved. It is always read as 0 and cannot be modified.                                                                                                                                         |  |  |  |

|     |          |                  |        | [Setting conditions]                                                                                                                                                                                                                  |  |  |  |

|     |          |                  |        | <ul> <li>When TCNT = TGRC while TGRC is functioning as<br/>output compare register</li> </ul>                                                                                                                                         |  |  |  |

|     |          |                  |        | • When TCNT value is transferred to TGRC by input capture signal while TGRC is functioning as input capture register                                                                                                                  |  |  |  |

|     |          |                  |        | [Clearing conditions]                                                                                                                                                                                                                 |  |  |  |

|     |          |                  |        | • When DTC is activated by a TGIC interrupt while the DISEL bit in MRB of DTC is 0                                                                                                                                                    |  |  |  |

|     |          |                  |        | <ul> <li>When 0 is written to TGFC after reading TGFC = 1<br/>(When the CPU is used to clear this flag by writing 0<br/>while the corresponding interrupt is enabled, be sure<br/>to read the flag after writing 0 to it.)</li> </ul> |  |  |  |

| 1   | TGFB     | 0                | R/(W)* | Input Capture/Output Compare Flag B                                                                                                                                                                                                   |  |  |  |

|     |          |                  |        | Status flag that indicates the occurrence of TGRB input capture or compare match.                                                                                                                                                     |  |  |  |

|     |          |                  |        | [Setting conditions]                                                                                                                                                                                                                  |  |  |  |

|     |          |                  |        | <ul> <li>When TCNT = TGRB while TGRB is functioning as<br/>output compare register</li> </ul>                                                                                                                                         |  |  |  |

|     |          |                  |        | <ul> <li>When TCNT value is transferred to TGRB by input<br/>capture signal while TGRB is functioning as input<br/>capture register</li> </ul>                                                                                        |  |  |  |

|     |          |                  |        | [Clearing conditions]                                                                                                                                                                                                                 |  |  |  |

|     |          |                  |        | • When DTC is activated by a TGIB interrupt while the DISEL bit in MRB of DTC is 0                                                                                                                                                    |  |  |  |

|     |          |                  |        | <ul> <li>When 0 is written to TGFB after reading TGFB = 1<br/>(When the CPU is used to clear this flag by writing 0<br/>while the corresponding interrupt is enabled, be sure<br/>to read the flag after writing 0 to it.)</li> </ul> |  |  |  |

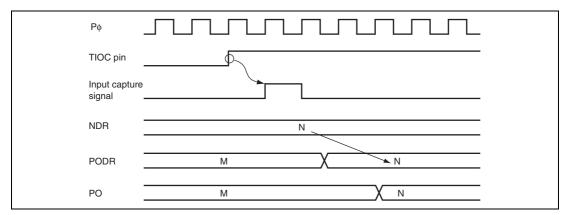

## 11.4.8 Pulse Output Triggered by Input Capture

Pulse output can be triggered by TPU input capture as well as by compare match. If TGRA functions as an input capture register in the TPU channel selected by PCR, pulse output will be triggered by the input capture signal.

Figure 11.11 shows the timing of this output.

## 11.5 Usage Notes

## 11.5.1 Module Stop State Setting

PPG operation can be disabled or enabled using the module stop control register. The initial value is for PPG operation to be halted. Register access is enabled by clearing the module stop state. For details, refer to section 20, Power-Down Modes.

## 11.5.2 Operation of Pulse Output Pins

Pins PO0 to PO15 are also used for other peripheral functions such as the TPU. When output by another peripheral function is enabled, the corresponding pins cannot be used for pulse output. Note, however, that data transfer from NDR bits to PODR bits takes place, regardless of the usage of the pins.

Pin functions should be changed only under conditions in which the output trigger event will not occur.

## (2) Programming Procedure in User Program Mode

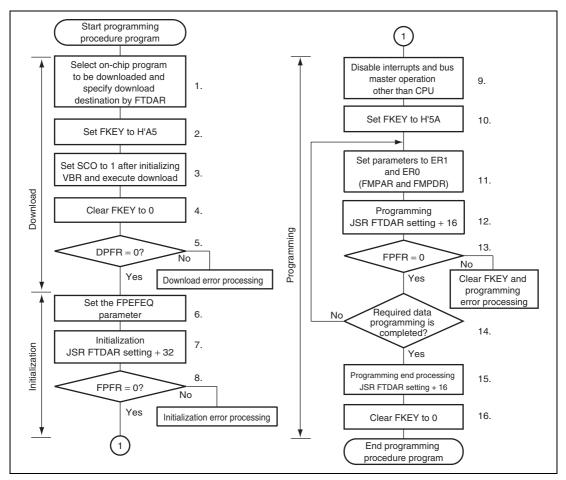

The procedures for download of the on-chip program, initialization, and programming are shown in figure 18.12.

Figure 18.12 Programming Procedure in User Program Mode

| Register<br>Abbreviation | Reset       | Module<br>Stop state | Sleep | All-Module-<br>Clock-Stop | Software<br>Standby | Hardware<br>Standby | Module |

|--------------------------|-------------|----------------------|-------|---------------------------|---------------------|---------------------|--------|

| SRAMCR                   | Initialized | _                    | _     | _                         | _                   | Initialized         | BSC    |

| BROMCR                   | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| MPXCR                    | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| RAMER                    | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| MDCR                     | Initialized | _                    | _     | _                         | _                   | Initialized         | SYSTEM |

| SYSCR                    | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| SCKCR                    | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| SBYCR                    | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| MSTPCRA                  | Initialized | _                    | _     |                           | _                   | Initialized         |        |

| MSTPCRB                  | Initialized |                      |       | _                         | _                   | Initialized         | _      |

| MSTPCRC                  | Initialized |                      | _     |                           |                     | Initialized         | _      |

| SEMR_2                   | Initialized | _                    | _     |                           | _                   | Initialized         | SCI_2  |

| SMR_4                    | Initialized |                      | —     | _                         | —                   | Initialized         | SCI_4  |

| BRR_4                    | Initialized | _                    | _     |                           | _                   | Initialized         |        |

| SCR_4                    | Initialized | _                    |       | _                         | _                   | Initialized         | _      |

| TDR_4                    | Initialized | Initialized          | —     | Initialized               | Initialized         | Initialized         | _      |

| SSR_4                    | Initialized | Initialized          | _     | Initialized               | Initialized         | Initialized         |        |

| RDR_4                    | Initialized | Initialized          | _     | Initialized               | Initialized         | Initialized         |        |

| SCMR_4                   | Initialized |                      | _     | _                         | _                   | Initialized         |        |

| FCCS                     | Initialized | _                    | _     | _                         | _                   | Initialized         | FLASH  |

| FPCS                     | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| FECS                     | Initialized |                      | _     | _                         | _                   | Initialized         |        |

| FKEY                     | Initialized | _                    | _     | _                         | _                   | Initialized         |        |

| FMATS                    | Initialized | _                    |       | _                         | _                   | Initialized         | _      |

| FTDAR                    | Initialized | _                    |       | _                         | _                   | Initialized         | _      |

| TCR_2                    | Initialized |                      | _     |                           |                     | Initialized         | TMR_2  |

| TCR_3                    | Initialized | _                    | _     | _                         | _                   | Initialized         | TMR_3  |

| TCSR_2                   | Initialized | _                    | _     | _                         | _                   | Initialized         | TMR_2  |

| TCSR_3                   | Initialized |                      | _     |                           |                     | Initialized         | TMR_3  |

| TCORA_2                  | Initialized | _                    | _     | _                         | _                   | Initialized         | TMR_2  |

| TCORA_3                  | Initialized | _                    | _     | _                         | _                   | Initialized         | TMR_3  |

| TCORB_2                  | Initialized | _                    | _     | _                         | _                   | Initialized         | TMR_2  |

| TCORB_3                  | Initialized | _                    | _     | _                         | _                   | Initialized         | TMR_3  |