#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                          |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-VFBGA                                                              |

| Supplier Device Package    | 48-BGA (4x4)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg825f8-bga48t |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

divided into two blocks; the main block and the information block. Program code is normally written to the main block. Additionally, the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in the energy modes EM0 and EM1.

#### 2.1.4 Direct Memory Access Controller (DMA)

The Direct Memory Access (DMA) controller performs memory operations independently of the CPU. This has the benefit of reducing the energy consumption and the workload of the CPU, and enables the system to stay in low energy modes when moving for instance data from the USART to RAM or from the External Bus Interface to a PWM-generating timer. The DMA controller uses the PL230  $\mu$ DMA controller licensed from ARM.

#### 2.1.5 Reset Management Unit (RMU)

The RMU is responsible for handling the reset functionality of the EFM32TG.

#### 2.1.6 Energy Management Unit (EMU)

The Energy Management Unit (EMU) manage all the low energy modes (EM) in EFM32TG microcontrollers. Each energy mode manages if the CPU and the various peripherals are available. The EMU can also be used to turn off the power to unused SRAM blocks.

#### 2.1.7 Clock Management Unit (CMU)

The Clock Management Unit (CMU) is responsible for controlling the oscillators and clocks on-board the EFM32TG. The CMU provides the capability to turn on and off the clock on an individual basis to all peripheral modules in addition to enable/disable and configure the available oscillators. The high degree of flexibility enables software to minimize energy consumption in any specific application by not wasting power on peripherals and oscillators that are inactive.

## 2.1.8 Watchdog (WDOG)

The purpose of the watchdog timer is to generate a reset in case of a system failure, to increase application reliability. The failure may e.g. be caused by an external event, such as an ESD pulse, or by a software failure.

## 2.1.9 Peripheral Reflex System (PRS)

The Peripheral Reflex System (PRS) system is a network which lets the different peripheral module communicate directly with each other without involving the CPU. Peripheral modules which send out Reflex signals are called producers. The PRS routes these reflex signals to consumer peripherals which apply actions depending on the data received. The format for the Reflex signals is not given, but edge triggers and other functionality can be applied by the PRS.

## 2.1.10 Inter-Integrated Circuit Interface (I2C)

The  $I^2C$  module provides an interface between the MCU and a serial  $I^2C$ -bus. It is capable of acting as both a master and a slave, and supports multi-master buses. Both standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates all the way from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also provided to allow implementation of an SMBus compliant system. The interface provided to software by the  $I^2C$  module, allows both fine-grained control of the transmission process and close to automatic transfers. Automatic recognition of slave addresses is provided in all energy modes.

# **3 Electrical Characteristics**

## **3.1 Test Conditions**

#### **3.1.1 Typical Values**

The typical data are based on  $T_{AMB}=25^{\circ}C$  and  $V_{DD}=3.0$  V, as defined in Table 3.2 (p. 9), by simulation and/or technology characterisation unless otherwise specified.

#### 3.1.2 Minimum and Maximum Values

The minimum and maximum values represent the worst conditions of ambient temperature, supply voltage and frequencies, as defined in Table 3.2 (p. 9), by simulation and/or technology characterisation unless otherwise specified.

## **3.2 Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings, and functional operation under such conditions are not guaranteed. Stress beyond the limits specified in Table 3.1 (p. 9) may affect the device reliability or cause permanent damage to the device. Functional operating conditions are given in Table 3.2 (p. 9).

| Symbol             | Parameter                         | Condition                              | Min  | Тур | Max                  | Unit |

|--------------------|-----------------------------------|----------------------------------------|------|-----|----------------------|------|

| T <sub>STG</sub>   | Storage tempera-<br>ture range    |                                        | -40  |     | 150 <sup>1</sup>     | °C   |

| Τ <sub>S</sub>     | Maximum soldering temperature     | Latest IPC/JEDEC J-STD-020<br>Standard |      |     | 260                  | °C   |

| V <sub>DDMAX</sub> | External main sup-<br>ply voltage |                                        | 0    |     | 3.8                  | V    |

| V <sub>IOPIN</sub> | Voltage on any I/O pin            |                                        | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

#### Table 3.1. Absolute Maximum Ratings

<sup>1</sup>Based on programmed devices tested for 10000 hours at 150°C. Storage temperature affects retention of preprogrammed calibration values stored in flash. Please refer to the Flash section in the Electrical Characteristics for information on flash data retention for different temperatures.

## **3.3 General Operating Conditions**

## 3.3.1 General Operating Conditions

#### Table 3.2. General Operating Conditions

| Symbol            | Parameter                    | Min  | Тур | Max | Unit |

|-------------------|------------------------------|------|-----|-----|------|

| T <sub>AMB</sub>  | Ambient temperature range    | -40  |     | 85  | °C   |

| V <sub>DDOP</sub> | Operating supply voltage     | 1.98 |     | 3.8 | V    |

| f <sub>APB</sub>  | Internal APB clock frequency |      |     | 32  | MHz  |

| f <sub>AHB</sub>  | Internal AHB clock frequency |      |     | 32  | MHz  |

## **3.4 Current Consumption**

#### Table 3.3. Current Consumption

| Symbol           | Parameter                                                     | Condition                                                                                                          | Min | Тур  | Мах   | Unit       |

|------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|

|                  |                                                               | 32 MHz HFXO, all peripheral clocks disabled, V <sub>DD</sub> = 3.0 V                                               |     | 157  |       | μΑ/<br>MHz |

|                  |                                                               | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 150  | 170   | µA/<br>MHz |

|                  | EM0 current. No prescaling. Running                           | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 153  | 172   | µA/<br>MHz |

| I <sub>EM0</sub> | prime number cal-<br>culation code from<br>Flash. (Production | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 155  | 175   | µA/<br>MHz |

|                  | test condition = 14<br>MHz)                                   | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 157  | 178   | µA/<br>MHz |

|                  |                                                               | 6.6 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 162  | 183   | μΑ/<br>MHz |

|                  |                                                               | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 200  | 240   | μΑ/<br>MHz |

|                  |                                                               | 32 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                      |     | 53   |       | µA/<br>MHz |

|                  |                                                               | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 51   | 57    | µA/<br>MHz |

|                  |                                                               | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 55   | 59    | µA/<br>MHz |

| I <sub>EM1</sub> | EM1 current (Pro-<br>duction test condi-<br>tion = 14 MHz)    | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 56   | 61    | µA/<br>MHz |

|                  | ,                                                             | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 58   | 63    | µA/<br>MHz |

|                  |                                                               | 6.6 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 63   | 68    | µA/<br>MHz |

|                  |                                                               | 1.2 MHz HFRCO. all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 100  | 122   | µA/<br>MHz |

|                  | EM2 current                                                   | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, V <sub>DD</sub> = 3.0 V,<br>T <sub>AMB</sub> =25°C |     | 1.0  | 1.2   | μA         |

| I <sub>EM2</sub> |                                                               | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C               |     | 2.4  | 5.0   | μA         |

| Inno             | EM3 current                                                   | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                    |     | 0.59 | 1.0   | μA         |

| I <sub>EM3</sub> |                                                               | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                    |     | 2.0  | 4.5   | μA         |

| I <sub>EM4</sub> | EM4 current                                                   | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                    |     | 0.02 | 0.055 | μA         |

| •⊂IVI4           |                                                               | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                    |     | 0.25 | 0.70  | μA         |

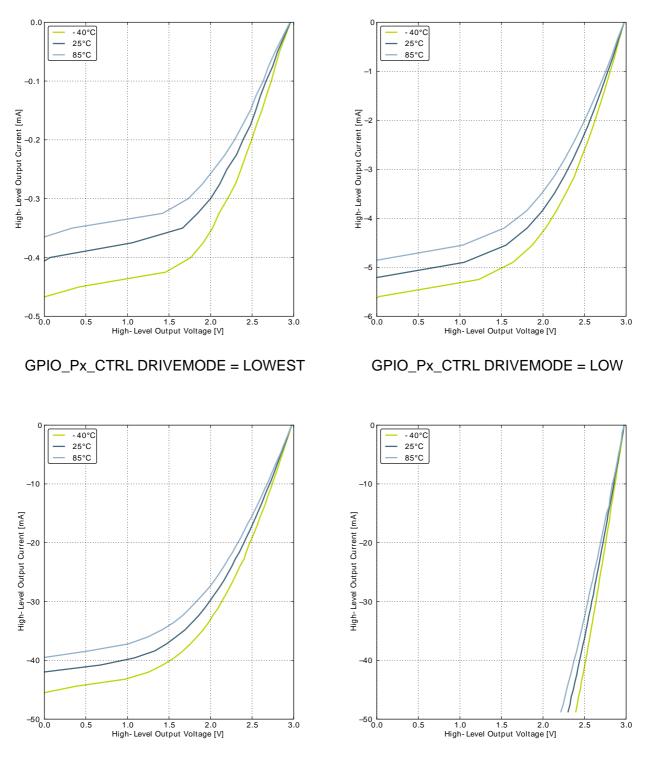

#### Figure 3.7. Typical High-Level Output Current, 3V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

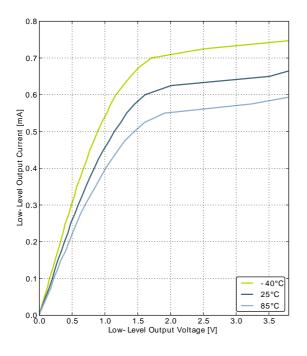

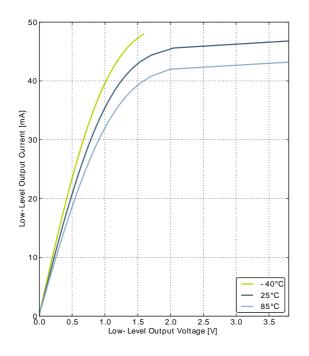

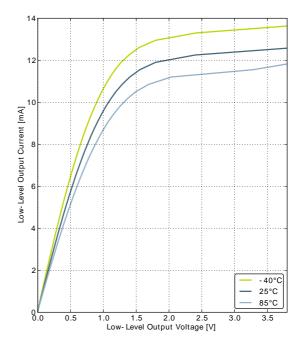

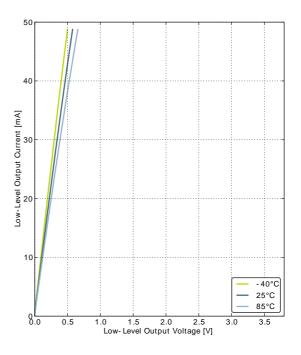

#### Figure 3.8. Typical Low-Level Output Current, 3.8V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = LOW

GPIO\_Px\_CTRL DRIVEMODE = HIGH

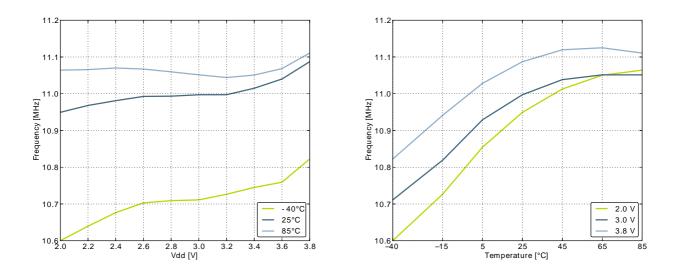

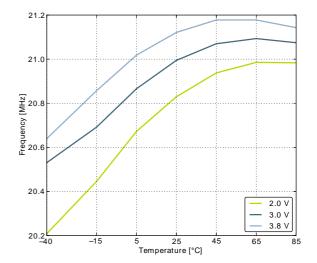

Figure 3.13. Calibrated HFRCO 11 MHz Band Frequency vs Supply Voltage and Temperature

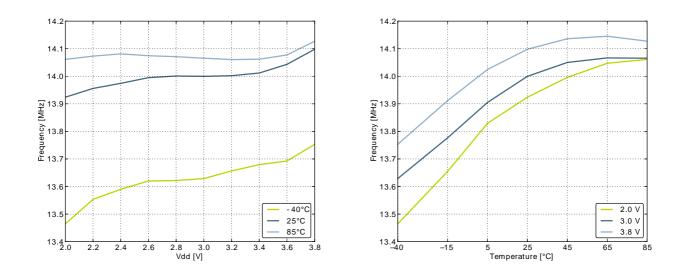

Figure 3.14. Calibrated HFRCO 14 MHz Band Frequency vs Supply Voltage and Temperature

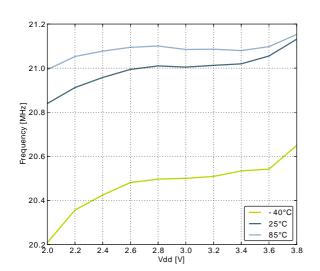

Figure 3.15. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature

| Symbol               | Parameter                               | Condition                                                                | Min | Тур | Max | Unit |

|----------------------|-----------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

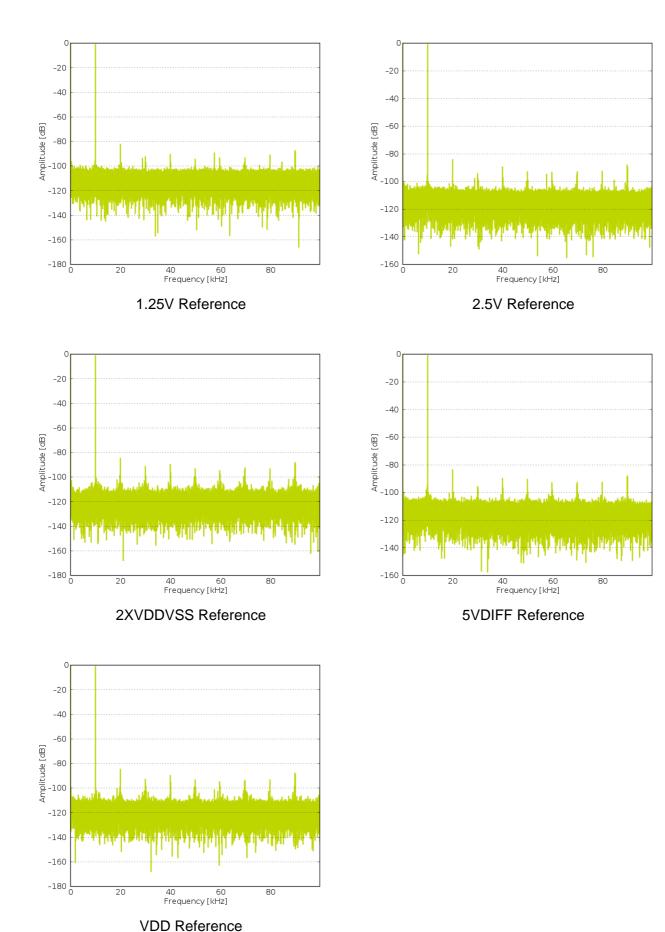

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 63  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 66  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, 5V reference                  |     | 66  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 69  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, 2xV <sub>DD</sub> reference   |     | 70  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, single<br>ended, internal 1.25V refer-<br>ence     |     | 58  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, single<br>ended, internal 2.5V reference           |     | 62  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, single<br>ended, V <sub>DD</sub> reference         |     | 64  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25V reference        |     | 60  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5V reference         |     | 64  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, differen-<br>tial, 5V reference                    |     | 54  |     | dB   |

|                      |                                         | 1 MSamples/s, 12 bit, differential, $V_{DD}$ reference                   |     | 66  |     | dB   |

| SINAD <sub>ADC</sub> | SIgnal-to-Noise<br>And Distortion-ratio | 1 MSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference     |     | 68  |     | dB   |

| SINADADC             | (SINAD)                                 | 200 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 61  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 65  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference          |     | 66  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 63  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 66  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, 5V reference                  |     | 66  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, V <sub>DD</sub> reference     | 62  | 68  |     | dB   |

|                      |                                         | 200 kSamples/s, 12 bit, differ-<br>ential, 2xV <sub>DD</sub> reference   |     | 69  |     | dB   |

| SFDR <sub>ADC</sub>  | Spurious-Free Dy-<br>namic Range (SF-   | 1 MSamples/s, 12 bit, single<br>ended, internal 1.25V refer-<br>ence     |     | 64  |     | dBc  |

|                      | DR)                                     | 1 MSamples/s, 12 bit, single<br>ended, internal 2.5V reference           |     | 76  |     | dBc  |

| Symbol                 | Parameter                                              | Condition                                                                | Min                 | Тур               | Max                | Unit                |

|------------------------|--------------------------------------------------------|--------------------------------------------------------------------------|---------------------|-------------------|--------------------|---------------------|

|                        |                                                        | 1 MSamples/s, 12 bit, single<br>ended, V <sub>DD</sub> reference         |                     | 73                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25V reference        |                     | 66                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5V reference         |                     | 77                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, V <sub>DD</sub> reference       |                     | 76                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference     |                     | 75                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, 5V reference                    |                     | 69                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |                     | 75                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, single<br>ended, internal 2.5V reference         |                     | 75                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference          | 68                  | 76                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |                     | 79                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |                     | 79                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, 5V reference                  |                     | 78                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, $V_{\text{DD}}$ reference          |                     | 79                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, 2xV <sub>DD</sub> reference   |                     | 79                |                    | dBc                 |

| M                      | Offect veltage                                         | After calibration, single ended                                          | -4                  | 0.3               | 4                  | mV                  |

| VADCOFFSET             | Offset voltage                                         | After calibration, differential                                          |                     | 0.3               |                    | mV                  |

|                        |                                                        |                                                                          |                     | -1.92             |                    | mV/°C               |

| TGRAD <sub>ADCTH</sub> | Thermometer out-<br>put gradient                       |                                                                          |                     | -6.3              |                    | ADC<br>Codes/<br>°C |

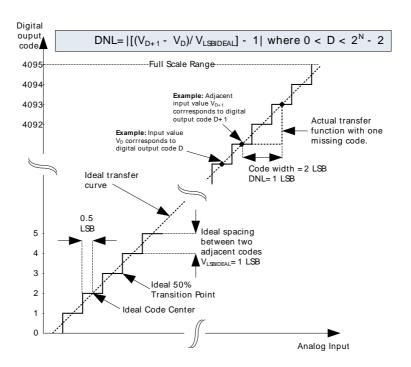

| DNL <sub>ADC</sub>     | Differential non-lin-<br>earity (DNL)                  | V <sub>DD</sub> = 3.0 V, external 2.5V reference                         | -1                  | ±0.7              | 4                  | LSB                 |

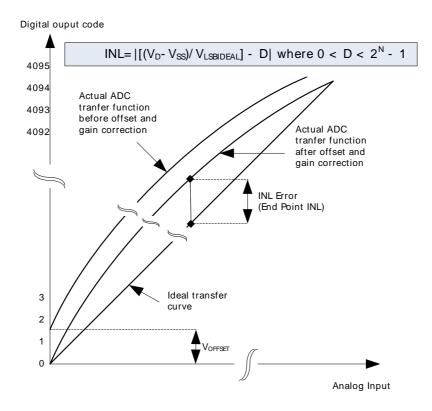

| INL <sub>ADC</sub>     | Integral non-linear-<br>ity (INL), End point<br>method | V <sub>DD</sub> = 3.0 V, external 2.5V reference                         |                     | ±1.2              | ±3                 | LSB                 |

| MC <sub>ADC</sub>      | No missing codes                                       |                                                                          | 11.999 <sup>1</sup> | 12                |                    | bits                |

|                        | <b>0</b>                                               | 1.25V reference                                                          |                     | 0.01 <sup>2</sup> | 0.033 <sup>3</sup> | %/°C                |

| GAIN <sub>ED</sub>     | Gain error drift                                       | 2.5V reference                                                           |                     | 0.01 <sup>2</sup> | 0.03 <sup>3</sup>  | %/°C                |

| 055057                 | or                                                     | 1.25V reference                                                          |                     | 0.2 <sup>2</sup>  | 0.7 <sup>3</sup>   | LSB/°C              |

| OFFSET <sub>ED</sub>   | Offset error drift                                     | 2.5V reference                                                           |                     | 0.2 <sup>2</sup>  | 0.62 <sup>3</sup>  | LSB/°C              |

<sup>1</sup>On the average every ADC will have one missing code, most likely to appear around  $2048 \pm n*512$  where n can be a value in the set {-3, -2, -1, 1, 2, 3}. There will be no missing code around 2048, and in spite of the missing code the ADC will be monotonic

## **EFM<sup>®</sup>32**

at all times so that a response to a slowly increasing input will always be a slowly increasing output. Around the one code that is missing, the neighbour codes will look wider in the DNL plot. The spectra will show spurs on the level of -78dBc for a full scale input for chips that have the missing code issue.

<sup>2</sup>Typical numbers given by abs(Mean) / (85 - 25).

<sup>3</sup>Max number given by (abs(Mean) + 3x stddev) / (85 - 25).

The integral non-linearity (INL) and differential non-linearity parameters are explained in Figure 3.17 (p. 30) and Figure 3.18 (p. 30), respectively.

#### Figure 3.17. Integral Non-Linearity (INL)

Figure 3.18. Differential Non-Linearity (DNL)

## 3.10.1 Typical performance

#### Figure 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C

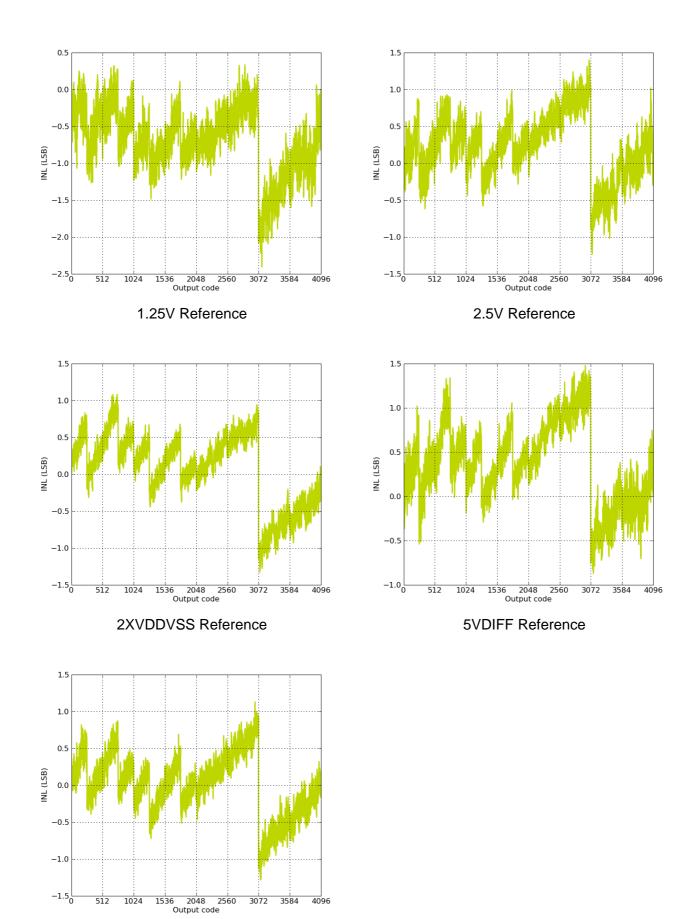

#### Figure 3.20. ADC Integral Linearity Error vs Code, Vdd = 3V, Temp = 25°C

**VDD** Reference

| Symbol                    | Parameter                     | Condition                                                                            | Min             | Тур   | Мах                  | Unit  |

|---------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------|-------|----------------------|-------|

|                           |                               | OPA0/OPA1 BIASPROG=0xF,<br>HALFBIAS=0x0                                              |                 | 16.36 |                      | MHz   |

|                           |                               | OPA0/OPA1 BIASPROG=0x7,<br>HALFBIAS=0x1                                              |                 | 0.81  |                      | MHz   |

|                           | Gain Bandwidth                | OPA0/OPA1 BIASPROG=0x0,<br>HALFBIAS=0x1                                              |                 | 0.11  |                      | MHz   |

| GBW <sub>OPAMP</sub>      | Product                       | OPA2 BIASPROG=0xF,<br>HALFBIAS=0x0                                                   |                 | 2.11  |                      | MHz   |

|                           |                               | OPA2 BIASPROG=0x7,<br>HALFBIAS=0x1                                                   |                 | 0.72  |                      | MHz   |

|                           |                               | OPA2 BIASPROG=0x0,<br>HALFBIAS=0x1                                                   |                 | 0.09  |                      | MHz   |

|                           |                               | BIASPROG=0xF,<br>HALFBIAS=0x0, C <sub>L</sub> =75 pF                                 |                 | 64    |                      | o     |

| PM <sub>OPAMP</sub>       | Phase Margin                  | BIASPROG=0x7,<br>HALFBIAS=0x1, C <sub>L</sub> =75 pF                                 |                 | 58    |                      | 0     |

|                           |                               | BIASPROG=0x0,<br>HALFBIAS=0x1, C <sub>L</sub> =75 pF                                 |                 | 58    |                      | o     |

| R <sub>INPUT</sub>        | Input Resistance              |                                                                                      |                 | 100   |                      | Mohm  |

| 5                         | Load Resistance               | OPA0/OPA1                                                                            | 200             |       |                      | Ohm   |

| R <sub>LOAD</sub>         |                               | OPA2                                                                                 | 2000            |       |                      | Ohm   |

|                           |                               | OPA0/OPA1                                                                            |                 |       | 11                   | mA    |

| I <sub>LOAD_DC</sub>      | Load Current                  | OPA2                                                                                 |                 |       | 1.5                  | mA    |

|                           |                               | OPAxHCMDIS=0                                                                         | V <sub>SS</sub> |       | V <sub>DD</sub>      | V     |

| V <sub>INPUT</sub>        | Input Voltage                 | OPAxHCMDIS=1                                                                         | V <sub>SS</sub> |       | V <sub>DD</sub> -1.2 | V     |

| V <sub>OUTPUT</sub>       | Output Voltage                |                                                                                      | V <sub>SS</sub> |       | V <sub>DD</sub>      | V     |

|                           |                               | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD,<br/>OPAxHCMDIS=0</v<sub></v<sub>     |                 | 6     |                      | mV    |

| V <sub>OFFSET</sub>       | Input Offset Voltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD-1.2,<br/>OPAxHCMDIS=1</v<sub></v<sub> |                 | 1     |                      | mV    |

| V <sub>OFFSET_DRIFT</sub> | Input Offset Voltage<br>Drift |                                                                                      |                 |       | 0.02                 | mV/°C |

|                           |                               | OPA0/OPA1 BIASPROG=0xF,<br>HALFBIAS=0x0                                              |                 | 46.11 |                      | V/µs  |

|                           |                               | OPA0/OPA1 BIASPROG=0x7,<br>HALFBIAS=0x1                                              |                 | 1.21  |                      | V/µs  |

| 00                        | Olaus Data                    | OPA0/OPA1 BIASPROG=0x0,<br>HALFBIAS=0x1                                              |                 | 0.16  |                      | V/µs  |

| SR <sub>OPAMP</sub>       | Slew Rate                     | OPA2 BIASPROG=0xF,<br>HALFBIAS=0x0                                                   |                 | 4.43  |                      | V/µs  |

|                           |                               | OPA2 BIASPROG=0x7,<br>HALFBIAS=0x1                                                   |                 | 1.30  |                      | V/µs  |

|                           |                               | OPA2 BIASPROG=0x0,<br>HALFBIAS=0x1                                                   |                 | 0.16  |                      | V/µs  |

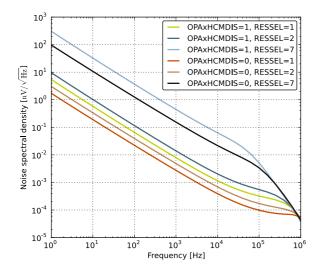

Figure 3.28. OPAMP Voltage Noise Spectral Density (Non-Unity Gain)

## 3.15 LCD

#### Table 3.19. LCD

| Symbol             | Parameter                            | Condition                                                                                                                              | Min | Тур  | Max | Unit |

|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| f <sub>LCDFR</sub> | Frame rate                           |                                                                                                                                        | 30  |      | 200 | Hz   |

| NUM <sub>SEG</sub> | Number of seg-<br>ments supported    |                                                                                                                                        |     | 11×8 |     | seg  |

| V <sub>LCD</sub>   | LCD supply voltage range             | Internal boost circuit enabled                                                                                                         | 2.0 |      | 3.8 | V    |

|                    |                                      | Display disconnected, stat-<br>ic mode, framerate 32 Hz, all<br>segments on.                                                           |     | 250  |     | nA   |

| I <sub>LCD</sub>   | Steady state current consumption.    | Display disconnected, quadru-<br>plex mode, framerate 32<br>Hz, all segments on, bias<br>mode to ONETHIRD in<br>LCD_DISPCTRL register. |     | 550  |     | nA   |

|                    | Steady state Cur-                    | Internal voltage boost off                                                                                                             |     | 0    |     | μA   |

| ILCDBOOST          | rent contribution of internal boost. | Internal voltage boost on,<br>boosting from 2.2 V to 3.0 V.                                                                            |     | 8.4  |     | μA   |

|                    |                                      | VBLEV of LCD_DISPCTRL register to LEVEL0                                                                                               |     | 3.0  |     | V    |

|                    |                                      | VBLEV of LCD_DISPCTRL register to LEVEL1                                                                                               |     | 3.08 |     | V    |

|                    |                                      | VBLEV of LCD_DISPCTRL register to LEVEL2                                                                                               |     | 3.17 |     | V    |

| V                  | Depart Voltage                       | VBLEV of LCD_DISPCTRL register to LEVEL3                                                                                               |     | 3.26 |     | V    |

| V <sub>BOOST</sub> | Boost Voltage                        | VBLEV of LCD_DISPCTRL register to LEVEL4                                                                                               |     | 3.34 |     | V    |

|                    |                                      | VBLEV of LCD_DISPCTRL register to LEVEL5                                                                                               |     | 3.43 |     | V    |

|                    |                                      | VBLEV of LCD_DISPCTRL register to LEVEL6                                                                                               |     | 3.52 |     | V    |

|                    |                                      | VBLEV of LCD_DISPCTRL register to LEVEL7                                                                                               |     | 3.6  |     | V    |

The total LCD current is given by Equation 3.3 (p. 43). I<sub>LCDBOOST</sub> is zero if internal boost is off.

#### Total LCD Current Based on Operational Mode and Internal Boost

$I_{LCDTOTAL} = I_{LCD} + I_{LCDBOOST}$

(3.3)

# **5 PCB Layout and Soldering**

## 5.1 Recommended PCB Layout

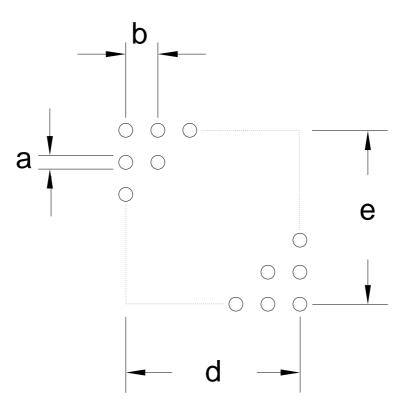

#### Figure 5.1. BGA48 PCB Land Pattern

Table 5.1. BGA48 PCB Land Pattern Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Row name and column number |

|--------|-----------|--------|----------------------------|

| а      | 0.25      | r1     | А                          |

| b      | 0.50      | rn     | G                          |

| d      | 3.00      | c1     | 1                          |

| е      | 3.00      | cn     | 7                          |

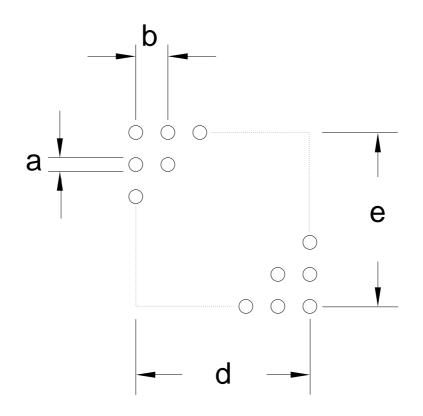

#### Figure 5.2. BGA48 PCB Solder Mask

Table 5.2. BGA48 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.28      |

| b      | 0.50      |

| d      | 3.00      |

| е      | 3.00      |

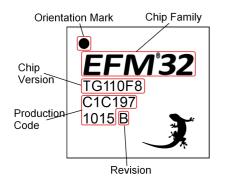

# 6 Chip Marking, Revision and Errata

## 6.1 Chip Marking

In the illustration below package fields and position are shown.

#### Figure 6.1. Example Chip Marking (top view)

## 6.2 Revision

The revision of a chip can be determined from the "Revision" field in Figure 6.1 (p. 57).

## 6.3 Errata

Please see the errata document for EFM32TG825 for description and resolution of device erratas. This document is available in Simplicity Studio and online at: http://www.silabs.com/support/pages/document-library.aspx?p=MCUs--32-bit

Initial preliminary release.

# **B** Contact Information

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: http://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

# silabs.com