Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

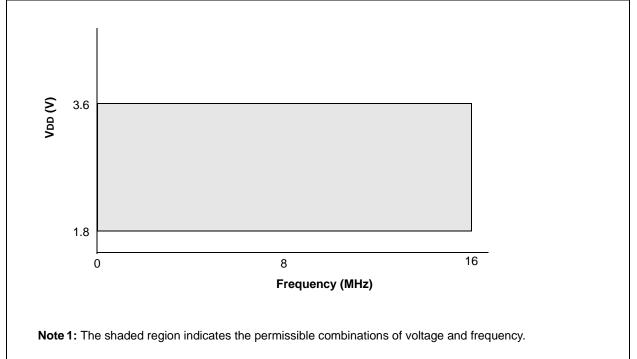

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf720-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-4) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

#### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | -   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                  |                                |                        |                    |  |  |  |  |

|--------------------------|--------------------------------|------------------------|--------------------|--|--|--|--|

| R = Readable bit         | W = Writable bit               | U = Unimplemented bit, | read as '0'        |  |  |  |  |

| -n = Value at POR        | '1' = Bit is set               | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |

| q = Value depends on cor | q = Value depends on condition |                        |                    |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

- bit 1 **POR:** Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

#### bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs)

#### 6.2 **PORTB and TRISB Registers**

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 6-7). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-2 shows how to initialize PORTB.

Reading the PORTB register (Register 6-6) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write-to-a-port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISB register (Register 6-7) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'. Example 6-2 shows how to initialize PORTB.

#### EXAMPLE 6-2: INITIALIZING PORTB

BANKSEL PORTB ; CLRF PORTB ;Init PORTB BANKSEL ANSELB CLRF ANSELB ;Make RB<7:4> digital BANKSEL TRISB ; MOVLW B'11110000';Set RB<7:4> as inputs MOVWF TRISB ;

Note: The ANSELB register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### 6.2.1 ANSELB REGISTER

The ANSELB register (Register 6-10) is used to configure the Input mode of an I/O pin to analog input. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no affect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### 6.2.2 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:4> enable or disable each pull-up (see Register 6-8). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the RABPU bit of the OPTION\_REG register.

#### 6.2.3 INTERRUPT-ON-CHANGE

All of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:4> enable or disable the interrupt function for each pin. Refer to Register 6-9. The interrupt-on-change feature is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the present value is compared with the old value latched on the last read of PORTB to determine which bits have changed or mismatched the old value. The 'mismatch' outputs of the last read are OR'd together to set the PORTB Change Interrupt Flag bit (RABIF) in the INTCON register.

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear the flag bit RABIF.

A mismatch condition will continue to set flag bit RABIF. Reading or writing PORTB will end the mismatch condition and allow flag bit RABIF to be cleared. The latch holding the last read value is not affected by a MCLR nor Brown-out Reset. After these Resets, the RABIF flag will continue to be set if a mismatch is present.

**Note:** When a pin change occurs at the same time as a read operation on PORTB, the RABIF flag will always be set. If multiple PORTB pins are configured for the interrupt-on-change, the user may not be able to identify which pin changed state.

#### REGISTER 6-6: PORTB: PORTB REGISTER

| R/W-x/u                 | R/W-x/u                           | R/W-x/u          | R/W-x/u | U-0                                | U-0 | U-0                | U-0   |  |

|-------------------------|-----------------------------------|------------------|---------|------------------------------------|-----|--------------------|-------|--|

| RB7                     | RB6                               | RB5              | RB4     | _                                  | —   | —                  | _     |  |

| bit 7                   |                                   | -                |         | •                                  |     | •                  | bit 0 |  |

|                         |                                   |                  |         |                                    |     |                    |       |  |

| Legend:                 |                                   |                  |         |                                    |     |                    |       |  |

| R = Readable            | R = Readable bit W = Writable bit |                  | bit     | U = Unimplemented bit, read as '0' |     |                    |       |  |

| -n = Value at POR '1' = |                                   | '1' = Bit is set |         | '0' = Bit is cleared               |     | x = Bit is unknown |       |  |

|                         |                                   |                  |         |                                    |     |                    |       |  |

| bit 7-4                 |                                   | ORTB I/O Pin bi  | t       |                                    |     |                    |       |  |

|                         | 1 = Port pin                      | s > VIH          |         |                                    |     |                    |       |  |

|                         | · ·                               | - \/             |         |                                    |     |                    |       |  |

0 = Port pin is < VIL

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 6-7: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|-----|-----|-----|-------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | —   | —   | —   | —     |

| bit 7  |        |        |        |     |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-4 **TRISB<7:4>:** PORTB Tri-State Control bit 1 = PORTB pin configured as an input (tri-stated) 0 = PORTB pin configured as an output bit 3-0 **Unimplemented:** Read as '0'

#### REGISTER 6-8: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| WPUB7 | WPUB6 | WPUB5 | WPUB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-4 WPUB<7:4>: Weak Pull-up PORTB Control bits

- 1 = Weak pull-up enabled (1,2)

- 0 = Weak pull-up disabled

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Global RABPU bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Legend: |       |       |       |     |     |     |       |

|---------|-------|-------|-------|-----|-----|-----|-------|

| bit 7   |       |       |       |     |     |     | bit 0 |

| IOCB7   | IOCB6 | IOCB5 | IOCB4 | _   | _   | _   | _     |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

#### REGISTER 6-9: IOCB: INTERRUPT-ON-CHANGE PORTB REGISTER

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-4 **IOCB<7:4>:** Interrupt-on-Change PORTB Control bits 1 = Interrupt-on-change enabled<sup>(1)</sup> 0 = Interrupt-on-change disabled

#### bit 3-0 Unimplemented: Read as '0'

**Note 1:** Interrupt-on-change also requires that the RABIE bit of the INTCON register be set.

#### REGISTER 6-10: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|-------|-----|-----|-----|-------|

| —     |     | ANSB5 | ANSB4 | —   |     |     | —     |

| bit 7 |     |       |       |     |     |     | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-4 **ANSB<5:4>**: Analog Select between Analog or Digital Function on Pins RB<5:4>, respectively

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- bit 3-0 Unimplemented: Read as '0'

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry. Weak pull-ups, if available, are unaffected. The corresponding TRIS bit must be set to Input mode by the user, in order to allow external control of the voltage on the pin.

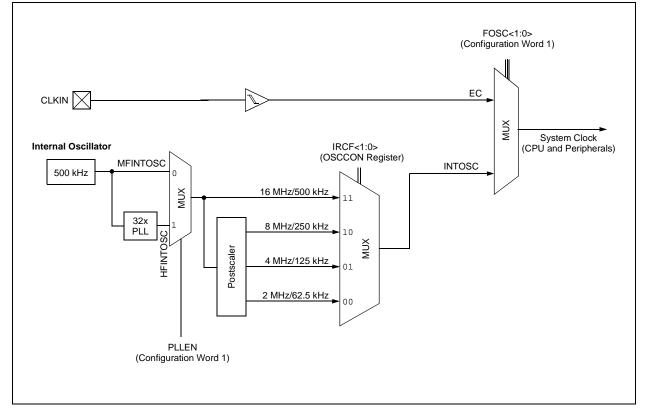

# 7.0 OSCILLATOR MODULE

#### 7.1 Overview

The oscillator module has a variety of clock sources and selection features that allow it to be used in a range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

The system can be configured to use an internal calibrated high-frequency oscillator as clock source, with a choice of selectable speeds via software. In addition, the system can also be configured to use an external clock source via the CLKIN pin.

Clock source modes are configured by the FOSC bits in Configuration Word 1 (CONFIG1). The oscillator module can be configured for one of the following modes of operation.

- 1. EC CLKOUT function on RA4/CLKOUT pin, CLKIN on RA5/CLKIN.

- EC I/O function on RA4/CLKOUT pin, CLKIN on RA5/CLKIN.

- 3. INTOSC CLKOUT function on RA4/CLKOUT pin, I/O function on RA5/CLKIN

- 4. INTOSCIO I/O function on RA4/CLKOUT pin, I/O function on RA5/CLKIN

#### FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

| Name    | Bit 7                                                                      | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3          | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|---------|----------------|--------|--------|--------|---------------------|

| ANSELB  | _                                                                          | —                                                                           | ANSB5   | ANSB4   | —              | —      | _      | —      | 53                  |

| CCP1CON | _                                                                          | —                                                                           | DC1     | B1      | CCP1M3         | CCP1M2 | CCP1M1 | CCP1M0 | 100                 |

| INTCON  | GIE                                                                        | PEIE                                                                        | TMR0IE  | INTE    | RABIE          | TMR0IF | INTF   | RABIF  | 37                  |

| PIE1    | TMR1GIE                                                                    | ADIE                                                                        | RCIE    | TXIE    | SSPIE          | CCP1IE | TMR2IE | TMR1IE | 38                  |

| PIR1    | TMR1GIF                                                                    | ADIF                                                                        | RCIF    | TXIF    | SSPIF          | CCP1IF | TMR2IF | TMR1IF | 39                  |

| PORTB   | RB7                                                                        | RB6                                                                         | RB5     | RB4     | —              | —      |        | —      | 52                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                                                                             |         |         |                |        | 91     |        |                     |

| TMR1L   | Ho                                                                         | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |                |        | 91     |        |                     |

| TRISB   | TRISB7                                                                     | TRISB6                                                                      | TRISB5  | TRISB4  | —              | —      |        | —      | 52                  |

| TRISC   | TRISC7                                                                     | TRISC6                                                                      | TRISC5  | TRISC4  | TRISC3         | TRISC2 | TRISC1 | TRISC0 | 58                  |

| T1CON   | TMR1CS1                                                                    | TMR1CS0                                                                     | T1CKPS1 | T1CKPS0 | —              | T1SYNC | —      | TMR10N | 95                  |

| T1GCON  | TMR1GE                                                                     | T1GPOL                                                                      | T1GTM   | T1GSPM  | T1GGO/<br>DONE | T1GVAL | T1GSS1 | T1GSS0 | 96                  |

| IADLE 13-0. SUMIMART OF REGISTERS ASSOCIATED WITH TIMER | TABLE 13-6: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|---------------------------------------------------------|-------------|---------------------------------------------|

|---------------------------------------------------------|-------------|---------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

#### 16.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit of the PIR1 register. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

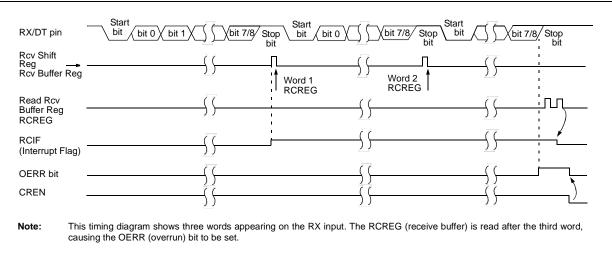

#### 16.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 16.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

# PIC16(L)F720/721

#### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name   | Bit 7   | Bit 6                        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|---------|------------------------------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE                         | TMR0IE | INTE   | RABIE  | TMR0IF | INTF   | RABIF  | 37                  |

| PIE1   | TMR1GIE | ADIE                         | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 38                  |

| PIR1   | TMR1GIF | ADIF                         | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |

| RCREG  |         | AUSART Receive Data Register |        |        |        |        |        |        | 115                 |

| RCSTA  | SPEN    | RX9                          | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 118                 |

| SPBRG  | BRG7    | BRG6                         | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 119                 |

| TRISC  | TRISC7  | TRISC6                       | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 58                  |

| TXSTA  | CSRC    | TX9                          | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 117                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

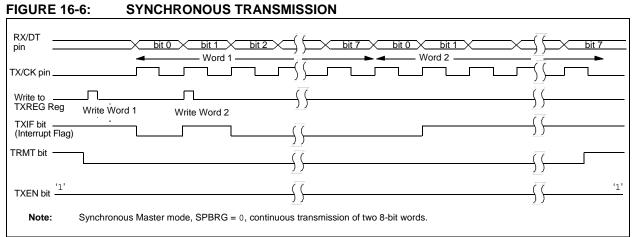

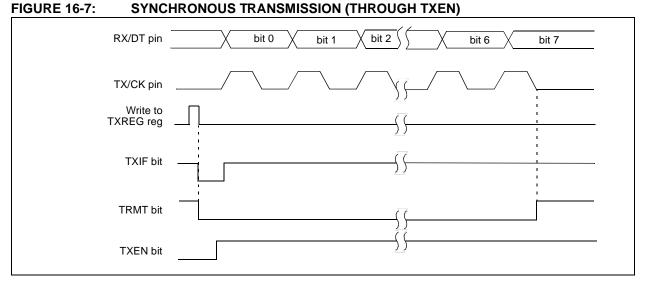

### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7   | Bit 6                         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|---------|-------------------------------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE                          | TMR0IE | INTE   | RABIE  | TMR0IF | INTF   | RABIF  | 37                  |

| PIE1   | TMR1GIE | ADIE                          | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 38                  |

| PIR1   | TMR1GIF | ADIF                          | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |

| RCSTA  | SPEN    | RX9                           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 118                 |

| SPBRG  | BRG7    | BRG6                          | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 119                 |

| TRISC  | TRISC7  | TRISC6                        | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 58                  |

| TXREG  |         | AUSART Transmit Data Register |        |        |        |        | _      |        |                     |

| TXSTA  | CSRC    | TX9                           | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D   | 117                 |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master transmission.

# PIC16(L)F720/721

| FIGURE 16-8:                 | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                                 |

|------------------------------|-------------------------------------------------------------------------------------------|

| RX/DT<br>pin                 | bit 0         bit 2         bit 3         bit 4         bit 5         bit 6         bit 7 |

| TX/CK pin                    |                                                                                           |

| Write to<br>bit SREN         |                                                                                           |

| SREN bit                     |                                                                                           |

| CREN bit                     | ʻ0'                                                                                       |

| RCIF bit<br>(Interrupt) ———— |                                                                                           |

| Read<br>RCREG                | ſ                                                                                         |

| Note: Timing dia             | agram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = 0.            |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON | GIE                          | PEIE   | TMR0IE | INTE   | RABIE  | TMR0IF | INTF   | RABIF  | 37                  |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 38                  |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |

| RCREG  | AUSART Receive Data Register |        |        |        |        |        | 115    |        |                     |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 118                 |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 58                  |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D   | 117                 |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] goto k                                                                                                                                                                    |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                       |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

## 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 22.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

### 23.5 Thermal Considerations

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature-40°C $\leq$ TA $\leq$ +125°C |           |                                           |      |       |                                                                                                                          |  |

|---------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.                                                                                                 | Sym.      | Characteristic                            | Тур. | Units | Conditions                                                                                                               |  |

| TH01 θJA                                                                                                      | θJA       | Thermal Resistance Junction to<br>Ambient | 62.2 | °C/W  | 20-pin PDIP package                                                                                                      |  |

|                                                                                                               |           |                                           | 75.0 | °C/W  | 20-pin SOIC package                                                                                                      |  |

|                                                                                                               |           |                                           | 89.3 | °C/W  | 20-pin SSOP package                                                                                                      |  |

|                                                                                                               |           |                                           | 43.0 | °C/W  | 20-pin QFN 4x4mm package                                                                                                 |  |

| TH02 θJC                                                                                                      | θJC       | Thermal Resistance Junction to<br>Case    | 27.5 | °C/W  | 20-pin PDIP package                                                                                                      |  |

|                                                                                                               |           |                                           | 23.1 | °C/W  | 20-pin SOIC package                                                                                                      |  |

|                                                                                                               |           |                                           | 31.1 | °C/W  | 20-pin SSOP package                                                                                                      |  |

|                                                                                                               |           |                                           | 5.3  | °C/W  | 20-pin QFN 4x4mm package                                                                                                 |  |

| TH03                                                                                                          | Тјмах     | Maximum Junction Temperature              | 150  | °C    |                                                                                                                          |  |

| TH04                                                                                                          | PD        | Power Dissipation                         |      | W     | PD = PINTERNAL + PI/O                                                                                                    |  |

| TH05                                                                                                          | PINTERNAL | Internal Power Dissipation                | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                                                                                     |  |

| TH06                                                                                                          | Ρι/ο      | I/O Power Dissipation                     | _    | W     | $ \begin{array}{l} PI/O = \Sigma \; (IOL \; ^* \; VOL) + \Sigma \; (IOH \; ^* \; (VDD \; \text{-} \\ VOH)) \end{array} $ |  |

| TH07                                                                                                          | Pder      | Derated Power                             |      | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                                                                                |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature; TJ = Junction Temperature

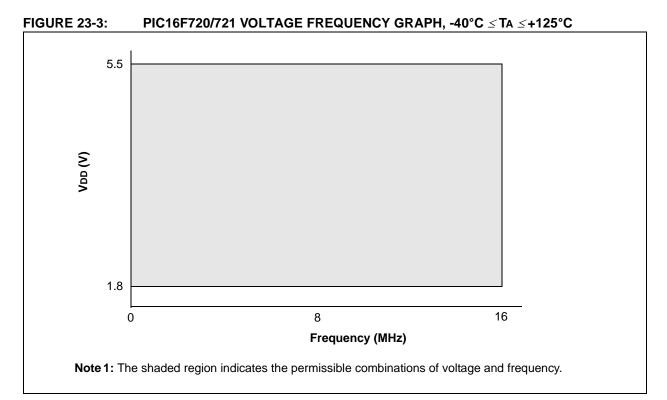

#### 23.7 AC Characteristics: PIC16F720/721-I/E

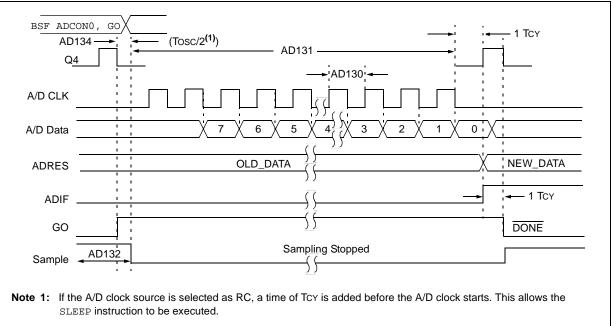

#### TABLE 23-8: PIC16F720/721 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                 |            |      |             |          |                                                       |

|----------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------------|------|-------------|----------|-------------------------------------------------------|

| Param.<br>No.                                                                                                        | Sym. | Characteristic                                                  | Min.       | Тур† | Max.        | Units    | Conditions                                            |

| AD130*                                                                                                               | TAD  | A/D Clock Period                                                | 1.0<br>4.0 |      | 9.0<br>16.0 | μS<br>μS | $V_{DD} > 2.0V^{(2)}$<br>$V_{DD} \le 2.0V^{(2)}$      |

|                                                                                                                      |      | A/D Internal RC Oscillator<br>Period                            | 1.0        | 2.0  | 6.0         | μS       | (ADRC mode)                                           |

| AD131                                                                                                                | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> |            | 10.5 | —           | Tad      | Set GO/DONE bit to new data in A/D<br>Result register |

| AD132*                                                                                                               | TACQ | Acquisition Time                                                |            | 2    | _           | μS       | VDD = 3.0V, EC or INTOSC Clock<br>mode <sup>(3)</sup> |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

- **2**: Setting of 16.0  $\mu$ s TAD not recommended for temperature > 85°C.

- 3: If ADRC mode is selected for use with VDD ≤ 2.0V, longer acquisition times will be required (see Section 9.3 "A/D Acquisition Requirements")

#### FIGURE 23-11: PIC16F720/721 A/D CONVERSION TIMING (NORMAL MODE)

### © 2010-2015 Microchip Technology Inc.

NOTES:

# PIC16(L)F720/721

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | [ <u>X]</u> <sup>(1)</sup><br> <br>Tape and Reel                                                      | X<br> <br>Temperature  | /XX<br>Package | XXX<br>Pattern |    | nples:                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------|------------------------|----------------|----------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Option                                                                                                | Range                  | Tackage        | rattern        |    | PIC16F720-E/P 301 = Extended Temp., PDIP<br>package, QTP pattern #301<br>PIC16F721T-I/SO = Tape and Reel, Industrial<br>Temp., SOIC package                                                                                                                                                                                                                                     |

| Device:               | PIC16F720, PIC16                                                                                      | LF720, PIC16F721       | , PIC16LF721   |                |    |                                                                                                                                                                                                                                                                                                                                                                                 |

| Temperature<br>Range: | $ \begin{array}{rcl} I & = & -40^{\circ}C \text{ to} \\ E & = & -40^{\circ}C \text{ to} \end{array} $ |                        |                |                |    |                                                                                                                                                                                                                                                                                                                                                                                 |

| Package:              | ML = Micro L<br>P = Plastic I<br>SO = SOIC<br>SS = SSOP                                               | ead Frame (QFN)<br>DIP |                |                |    |                                                                                                                                                                                                                                                                                                                                                                                 |

| Pattern:              | 3-Digit Pattern Coo                                                                                   | le for QTP (blank o    | therwise)      |                | No | <ul> <li>te 1: T= Available in tape and reel for all industrial devices except PDIP</li> <li>2: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.</li> </ul> |