# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 12x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf720-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

#### TABLE 1-1: PINOUT DESCRIPTION (CONTINUED)

| Name Function |      | IN    | OUT  | Description            |

|---------------|------|-------|------|------------------------|

| RC4           | RC4  | ST    | CMOS | General purpose I/O.   |

| RC5/CCP1      | RC5  | ST    | CMOS | General purpose I/O.   |

|               | CCP1 | ST    | CMOS | Capture/Compare/PWM 1. |

| RC6/AN8/SS    | RC6  | ST    | CMOS | General purpose I/O.   |

|               | AN8  | AN    | —    | A/D Channel 8 Input.   |

|               | SS   | ST    | —    | Slave Select input.    |

| RC7/AN9/SDO   | RC7  | ST    | CMOS | General purpose I/O.   |

|               | AN9  | AN    | —    | A/D Channel 9 Input.   |

|               | SDO  | —     | CMOS | SPI Data Output.       |

| Vdd           | Vdd  | Power | —    | Positive supply.       |

| Vss           | Vss  | Power | —    | Ground supply.         |

Legend: AN = Analog input or output, CMOS = CMOS compatible input or output, OD = Open Drain, TTL = TTL compatible input, ST = Schmitt Trigger input with CMOS levels, I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C, HV = High Voltage, XTAL = Crystal levels

#### FIGURE 2-3:

## PIC16(L)F720 SPECIAL FUNCTION REGISTERS

| INDF <sup>(*)</sup> | 00h       | INDF <sup>(*)</sup>   | 80h       | INDF <sup>(*)</sup>   | 100h  | INDF <sup>(*)</sup>   | 180h |

|---------------------|-----------|-----------------------|-----------|-----------------------|-------|-----------------------|------|

| TMR0                | 01h       | OPTION_REG            | 81h       | TMR0                  | 101h  | OPTION_REG            | 181h |

| PCL                 | 02h       | PCL                   | 82h       | PCL                   | 102h  | PCL                   | 182h |

| STATUS              | 03h       | STATUS                | 83h       | STATUS                | 103h  | STATUS                | 183h |

| FSR                 | 04h       | FSR                   | 84h       | FSR                   | 104h  | FSR                   | 184h |

| PORTA               | 05h       | TRISA                 | 85h       | -                     | 105h  | ANSELA                | 185h |

| PORTB               | 06h       | TRISB                 | 86h       |                       | 106h  | ANSELB                | 186h |

| PORTC               | 07h       | TRISC                 | 87h       |                       | 107h  | ANSELC                | 187h |

|                     | 08h       |                       | 88h       |                       | 108h  |                       | 188h |

|                     | 09h       |                       | 89h       |                       | 109h  |                       | 189h |

| PCLATH              | 0Ah       | PCLATH                | 8Ah       | PCLATH                | 10Ah  | PCLATH                | 18Ah |

| INTCON              | 0Bh       | INTCON                | 8Bh       | INTCON                | 10Bh  | INTCON                | 18Bh |

| PIR1                | 0Ch       | PIE1                  | 8Ch       | PMDATL                | 10Ch  | PMCON1                | 18Ch |

|                     | 0Dh       |                       | 8Dh       | PMADRL                | 10Dh  | PMCON2                | 18Dh |

| TMR1L               | 0Eh       | PCON                  | 8Eh       | PMDATH                | 10Eh  |                       | 18Eh |

| TMR1H               | 0Fh       | T1GCON                | 8Fh       | PMADRH                | 10Fh  |                       | 18Fh |

| T1CON               | 10h       | OSCCON                | 90h       |                       | 110h  |                       | 190h |

| TMR2                | 11h       | OSCTUNE               | 91h       |                       | 111h  |                       | 191h |

| T2CON               | 12h       | PR2                   | 92h       |                       | 112h  |                       | 192h |

| SSPBUF              | 13h       | SSPADD/SSPMSK         | 93h       |                       | 113h  |                       | 193h |

| SSPCON              | 14h       | SSPSTAT               | 94h       |                       | 114h  |                       | 194h |

| CCPR1L              | 15h       | WPUA                  | 95h       | WPUB                  | 115h  |                       | 195h |

| CCPR1H              | 16h       | IOCA                  | 96h       | IOCB                  | 116h  |                       | 196h |

| CCP1CON             | 17h       |                       | 97h       |                       | 117h  |                       | 197h |

| RCSTA               | 18h       | TXSTA                 | 98h       |                       | 118h  |                       | 198h |

| TXREG               | 19h       | SPBRG                 | 99h       |                       | 119h  |                       | 199h |

| RCREG               | 1Ah       |                       | 9Ah       |                       | 11Ah  |                       | 19Ah |

|                     | 1Bh       |                       | 9Bh       |                       | 11Bh  |                       | 19Bh |

|                     | 1Ch       |                       | 9Ch       |                       | 11Ch  |                       | 19Ch |

|                     | 1Dh       | FVRCON                | 9Dh       |                       | 11Dh  |                       | 19Dh |

| ADRES               | 1Eh       |                       | 9Eh       |                       | 11Eh  |                       | 19Eh |

| ADRES<br>ADCON0     | 1Fh       | ADCON1                | 9Fh       |                       | 11Fh  |                       | 19Eh |

| ADCONU              | 20h       | ADCONT                | A0h       |                       | 120h  |                       | 1A0h |

|                     | 2011      |                       | AUI       |                       | 12011 |                       | TAUT |

| <b>a</b> .          |           | General               |           |                       |       |                       |      |

| General<br>Purpose  |           | Purpose<br>Register   |           |                       |       |                       |      |

| Register            |           | 32 Bytes              |           |                       |       |                       |      |

| 80 Bytes            |           |                       | BFh       |                       |       |                       |      |

| -                   |           |                       | C0h       |                       |       |                       |      |

|                     | 06Fh      |                       | EFh       |                       | 16Fh  |                       | 1EFh |

|                     | 070h      |                       | F0h       |                       | 170h  |                       | 1F0h |

|                     |           | <b>A</b>              |           | 0                     |       | A                     |      |

| Access RAM          |           | Accesses<br>70h – 7Fh |           | Accesses<br>70h – 7Fh | 1     | Accesses<br>70h – 7Fh |      |

|                     |           |                       |           | 7011 - 7111           |       | 701-711               |      |

|                     | 7Fh       |                       | FFh       |                       | 17Fh  |                       | 1FFh |

| BANK 0              |           | BANK 1                |           | BANK 2                |       | BANK 3                |      |

| nan di 📃            | 1.1       |                       |           |                       |       |                       |      |

| gend: =             | : Unimple | emented data memor    | v locatic | ns, read as '0'.      |       |                       |      |

#### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-4) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | -   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                  |                  |                        |                    |

|--------------------------|------------------|------------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR        | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| q = Value depends on cor | ndition          |                        |                    |

| bit 7-2 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

- bit 1 **POR:** Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

#### bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs)

# PIC16(L)F720/721

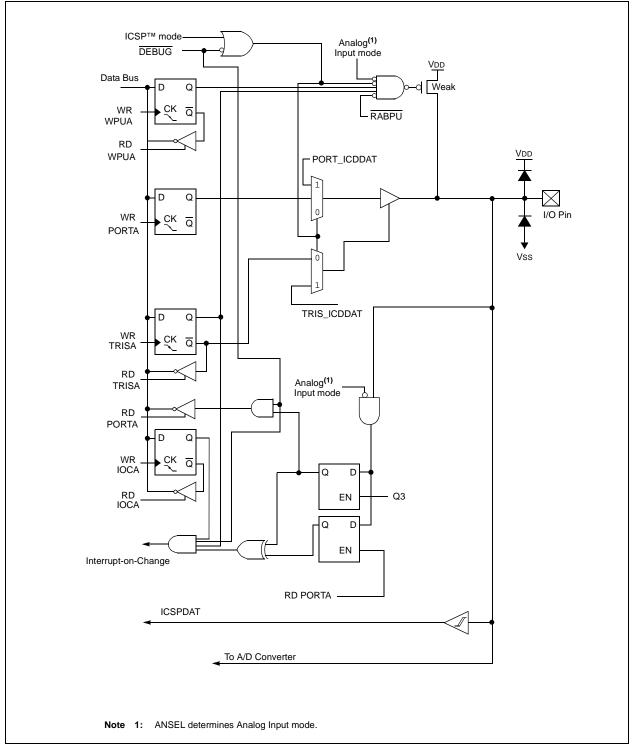

## FIGURE 6-1: BLOCK DIAGRAM OF RA0

## 7.0 OSCILLATOR MODULE

### 7.1 Overview

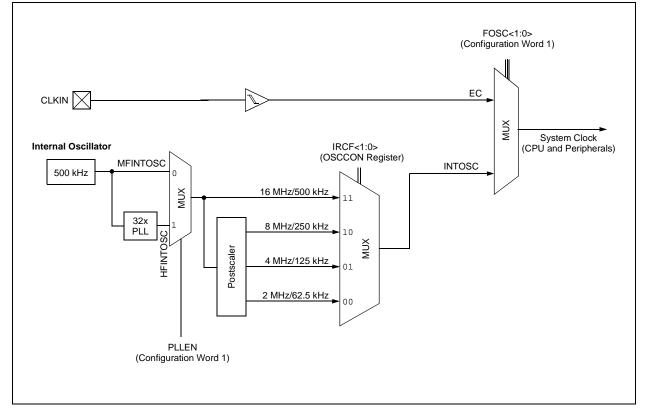

The oscillator module has a variety of clock sources and selection features that allow it to be used in a range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

The system can be configured to use an internal calibrated high-frequency oscillator as clock source, with a choice of selectable speeds via software. In addition, the system can also be configured to use an external clock source via the CLKIN pin.

Clock source modes are configured by the FOSC bits in Configuration Word 1 (CONFIG1). The oscillator module can be configured for one of the following modes of operation.

- 1. EC CLKOUT function on RA4/CLKOUT pin, CLKIN on RA5/CLKIN.

- EC I/O function on RA4/CLKOUT pin, CLKIN on RA5/CLKIN.

- 3. INTOSC CLKOUT function on RA4/CLKOUT pin, I/O function on RA5/CLKIN

- 4. INTOSCIO I/O function on RA4/CLKOUT pin, I/O function on RA5/CLKIN

#### FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-----|-------|-------|-------|-------|---------|-------|

| —     |     | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |     |       |       |       |       |         | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-2 | CHS<3:0>: Analog Channel Select bits                                                                                                                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0000 = AN0                                                                                                                                                                                                                                                |

|         | 0001 = AN1                                                                                                                                                                                                                                                |

|         | 0010 = AN2                                                                                                                                                                                                                                                |

|         | 0011 = AN3                                                                                                                                                                                                                                                |

|         | 0100 = AN4                                                                                                                                                                                                                                                |

|         | 0101 = AN5                                                                                                                                                                                                                                                |

|         | 0110 = AN6                                                                                                                                                                                                                                                |

|         | 0111 = AN7                                                                                                                                                                                                                                                |

|         | 1000 = AN8                                                                                                                                                                                                                                                |

|         | 1001 = AN9                                                                                                                                                                                                                                                |

|         | 1010 = AN10                                                                                                                                                                                                                                               |

|         | 1011 = AN11                                                                                                                                                                                                                                               |

|         | 1110 = Temperature Indicator <sup>(1)</sup>                                                                                                                                                                                                               |

|         | 1111 = Fixed Voltage Reference (FVREF) <sup>(2)</sup>                                                                                                                                                                                                     |

| bit 1   | GO/DONE: A/D Conversion Status bit                                                                                                                                                                                                                        |

|         | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.<br/>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> <li>0 = A/D conversion completed/not in progress</li> </ul> |

| bit 0   | ADON: ADC Enable bit                                                                                                                                                                                                                                      |

| bit 0   | 1 = ADC is enabled                                                                                                                                                                                                                                        |

|         | 0 = ADC is disabled and consumes no operating current                                                                                                                                                                                                     |

| Note 1: | See Section 11.0 "Temperature Indicator Module" for more information.                                                                                                                                                                                     |

| 2:      | See Section 10.0 "Fixed Voltage Reference" for more information.                                                                                                                                                                                          |

|         | 5                                                                                                                                                                                                                                                         |

## 13.6 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, these bits must be set:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 13.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, the clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- TMR1GE bit of the T1GCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 13.8 CCP Capture/Compare Time Base

The CCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 15.0 "Capture/ Compare/PWM (CCP) Module".

## 13.9 CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc/4 to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 9.2.5 "Special Event Trigger".

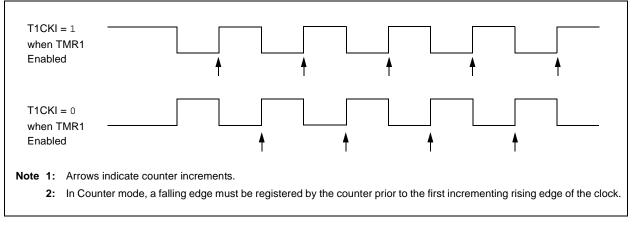

#### FIGURE 13-2: TIMER1 INCREMENTING EDGE

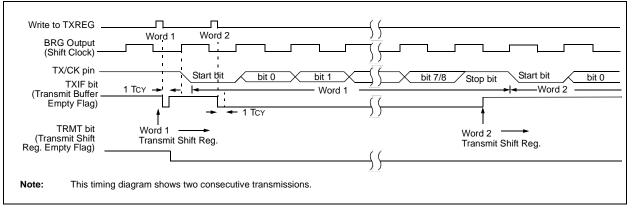

#### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON | GIE                           | PEIE   | TMR0IE | INTE   | RABIE  | TMR0IF | INTF   | RABIF  | 37                  |

| PIE1   | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 38                  |

| PIR1   | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |

| RCSTA  | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 118                 |

| SPBRG  | BRG7                          | BRG6   | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 119                 |

| TRISC  | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 58                  |

| TXREG  | AUSART Transmit Data Register |        |        |        |        |        |        |        |                     |

| TXSTA  | CSRC                          | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 117                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous transmission.

#### 16.1.2 AUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the AUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 16.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

Note: When the SPEN bit is set, the TX/CK I/O pin is automatically configured as an output, regardless of the state of the corresponding TRIS bit and whether or not the AUSART transmitter is enabled. The PORT latch is disconnected from the output driver so it is not possible to use the TX/CK pin as a general purpose output.

# PIC16(L)F720/721

| FIGURE 16-8:                 | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                                 |

|------------------------------|-------------------------------------------------------------------------------------------|

| RX/DT<br>pin                 | bit 0         bit 2         bit 3         bit 4         bit 5         bit 6         bit 7 |

| TX/CK pin                    |                                                                                           |

| Write to<br>bit SREN         |                                                                                           |

| SREN bit                     |                                                                                           |

| CREN bit                     | ʻ0'                                                                                       |

| RCIF bit<br>(Interrupt) ———— |                                                                                           |

| Read<br>RCREG                | ſ                                                                                         |

| Note: Timing dia             | agram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = 0.            |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON | GIE                          | PEIE   | TMR0IE | INTE   | RABIE  | TMR0IF | INTF   | RABIF  | 37                  |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 38                  |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |

| RCREG  | AUSART Receive Data Register |        |        |        |        |        |        |        |                     |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 118                 |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 58                  |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D   | 117                 |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

#### 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

#### 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/ received. It is up to the user to determine which data is to be used and what can be discarded.

#### 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- SDI configured as input

- SDO configured as output

- SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on the RC6/SS pin via the SSSEL bit in the APFCON register.

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

#### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

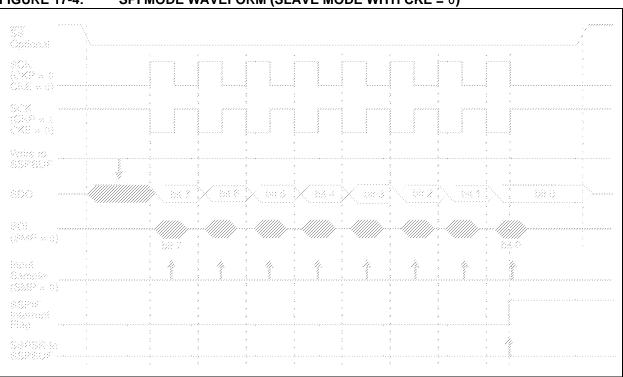

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

# PIC16(L)F720/721

#### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

#### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

x = Bit is unknown

| R/W-x        | R/W-x | R/W-x        | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|--------------|-------|--------------|-------|------------------------------------|-------|-------|-------|--|

| PMA7         | PMA6  | PMA5         | PMA4  | PMA3                               | PMA2  | PMA1  | PMA0  |  |

| bit 7        |       |              |       |                                    |       |       | bit 0 |  |

|              |       |              |       |                                    |       |       |       |  |

| Legend:      |       |              |       |                                    |       |       |       |  |

| R = Readable | bit   | W = Writable | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

'0' = Bit is cleared

#### REGISTER 18-5: PMADRL: PROGRAM MEMORY ADDRESS LOW REGISTER

bit 7-0 PMA<7:0>: Program Memory Read Address bits

'1' = Bit is set

-n = Value at POR

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH PROGRAM MEMORY READ

| Name   | Bit 7                                                       | Bit 6                                              | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on<br>Page |

|--------|-------------------------------------------------------------|----------------------------------------------------|-------|-------|-------|-------|-------|-------|---------------------|

| PMCON1 |                                                             | CFGS                                               | LWLO  | FREE  | —     | WREN  | WR    | RD    | 155                 |

| PMCON2 | Program Memory Control Register 2 (not a physical register) |                                                    |       |       |       |       |       | —     |                     |

| PMADRH | _                                                           | — — Program Memory Read Address Register High Byte |       |       |       |       |       | 156   |                     |

| PMADRL | Program Memory Read Address Register Low Byte               |                                                    |       |       |       |       |       | 157   |                     |

| PMDATH |                                                             | Program Memory Read Data Register High Byte        |       |       |       |       | 156   |       |                     |

| PMDATL | Program Memory Read Data Register Low Byte                  |                                                    |       |       |       |       | 156   |       |                     |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the program memory read.

## 23.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| <u>z. 1ppo</u> |                                      | 1   |                |  |  |  |  |

|----------------|--------------------------------------|-----|----------------|--|--|--|--|

| т              |                                      |     |                |  |  |  |  |

| F              | Frequency                            | Т   | Time           |  |  |  |  |

| Lowerc         | ase letters (pp) and their meanings: |     |                |  |  |  |  |

| pp             |                                      |     |                |  |  |  |  |

| сс             | CCP1                                 | OSC | CLKIN          |  |  |  |  |

| ck             | CLKOUT                               | rd  | RD             |  |  |  |  |

| CS             | CS                                   | rw  | RD or WR       |  |  |  |  |

| di             | SDI                                  | SC  | SCK            |  |  |  |  |

| do             | SDO                                  | SS  | SS             |  |  |  |  |

| dt             | Data in                              | t0  | TOCKI          |  |  |  |  |

| io             | I/O PORT                             | t1  | T1CKI          |  |  |  |  |

| mc             | MCLR                                 | wr  | WR             |  |  |  |  |

| Upperc         | ase letters and their meanings:      |     |                |  |  |  |  |

| S              |                                      |     |                |  |  |  |  |

| F              | Fall                                 | Р   | Period         |  |  |  |  |

| н              | High                                 | R   | Rise           |  |  |  |  |

| 1              | Invalid (High-impedance)             | V   | Valid          |  |  |  |  |

| L              | Low                                  | Z   | High-impedance |  |  |  |  |

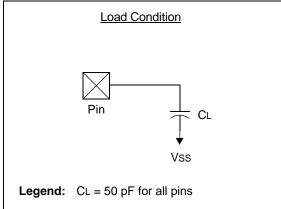

#### FIGURE 23-2: LOAD CONDITIONS

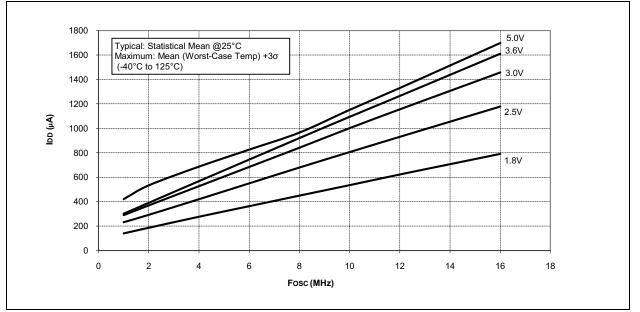

## 24.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

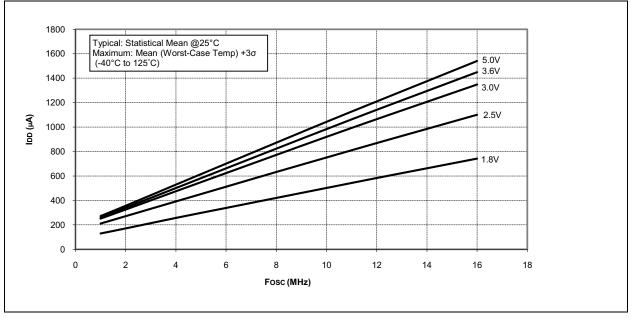

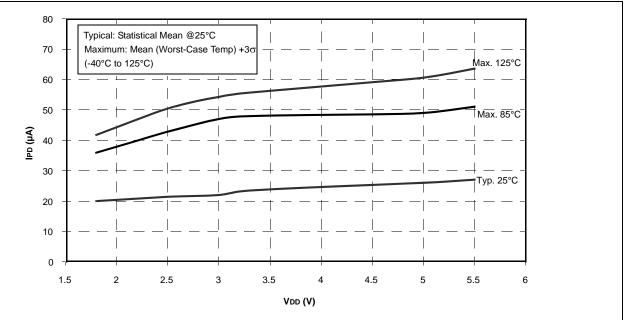

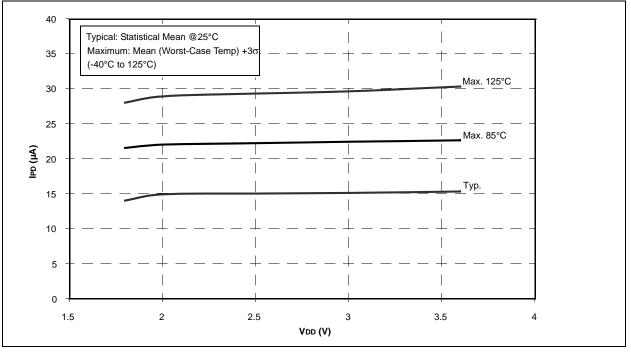

#### FIGURE 24-16: PIC16F720/721 WDT IPD vs. VDD

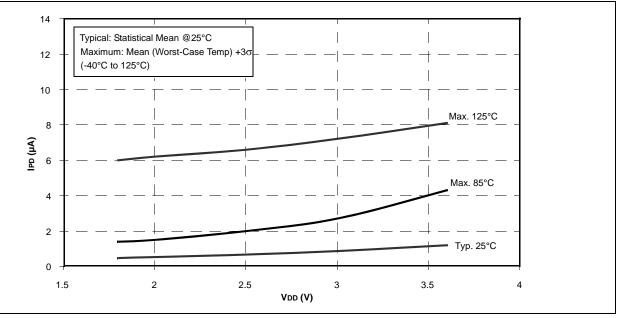

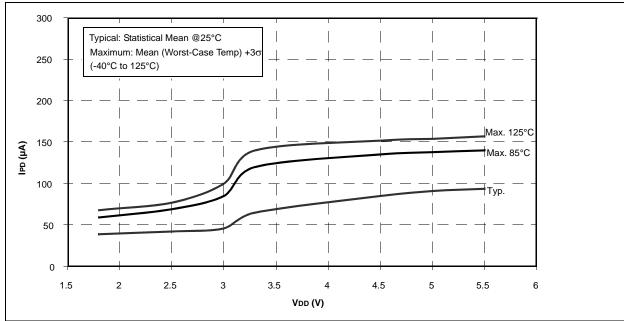

#### FIGURE 24-18: PIC16F720/721 FIXED VOLTAGE REFERENCE IPD vs. VDD

### 25.1 Package Marking Information

20-Lead SOIC (7.50 mm)

20-Lead SSOP (5.30 mm)

Example

| Leg | end: | XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-----|------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not | b    | e carried                                | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                            |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

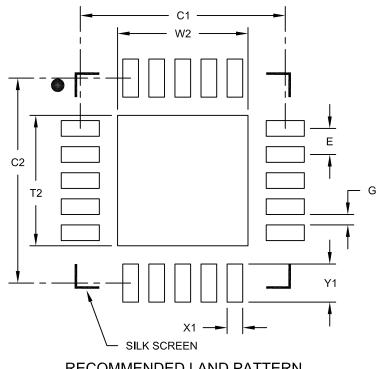

# 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

| RECOMMENDED | LAND | PAT | IERN |  |

|-------------|------|-----|------|--|

|             |      |     |      |  |

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimension                  | MIN         | NOM      | MAX  |      |  |

| Contact Pitch E            |             | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 2.50 |  |

| Optional Center Pad Length | T2          |          |      | 2.50 |  |

| Contact Pad Spacing        | C1          |          | 3.93 |      |  |

| Contact Pad Spacing        | C2          |          | 3.93 |      |  |

| Contact Pad Width          | X1          |          |      | 0.30 |  |

| Contact Pad Length         | Y1          |          |      | 0.73 |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2010-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0041-7

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.