Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf720-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| Device Overview                                                              | 7   |

|------------------------------------------------------------------------------|-----|

| Memory Organization                                                          |     |

| Resets                                                                       |     |

| Interrupts                                                                   |     |

| Low Dropout (LDO) Voltage Regulator                                          | 41  |

| I/O Ports                                                                    |     |

| Oscillator Module                                                            |     |

| Device Configuration                                                         |     |

| Analog-to-Digital Converter (ADC) Module                                     |     |

| Fixed Voltage Reference                                                      |     |

| Temperature Indicator Module                                                 |     |

| Timer0 Module                                                                |     |

| Timer1 Module with Gate Control                                              |     |

| Timer2 Module                                                                |     |

| Capture/Compare/PWM (CCP) Module                                             | 100 |

| Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 109 |

| SSP Module Overview                                                          | 129 |

| Flash Program Memory Self-Read/Self-Write Control                            | 151 |

| Power-Down Mode (Sleep)                                                      |     |

| In-Circuit Serial Programming <sup>TM</sup> (ICSP <sup>TM</sup> )            |     |

| Instruction Set Summary                                                      |     |

| Development Support                                                          | 170 |

| Electrical Specifications                                                    | 174 |

| DC and AC Characteristics Graphs and Charts                                  |     |

| Packaging Information                                                        |     |

| Appendix A: Data Sheet Revision History                                      |     |

| Appendix B: Migrating From Other PIC® Devices                                |     |

| The Microchip Website                                                        |     |

| Customer Change Notification Service                                         | 231 |

| Customer Support                                                             | 231 |

| Product Identification System                                                | 232 |

| POR | BOR | то | PD | Condition                                               |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset or LDO Reset                             |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

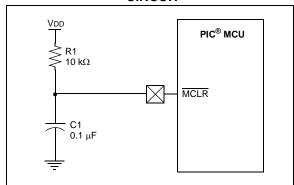

# 3.1 MCLR

The PIC16(L)F720/721 has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a Reset does not drive the  $\overline{\text{MCLR}}$  pin low.

Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 3-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the MCLRE bit in the Configuration Word register. When MCLRE = 0, the Reset signal to the chip is generated internally. When the MCLRE = 1, the RA3/MCLR pin becomes an external Reset input. In this mode, the RA3/MCLR pin has a weak pull-up to VDD. In-Circuit Serial Programming<sup>TM</sup> is not affected by selecting the internal MCLR option.

#### FIGURE 3-2: RECOMMENDED MCLR CIRCUIT

# 3.2 Power-on Reset (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. A maximum rise time for VDD is required. See **Section 23.0 "Electrical Specifications"** for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 3.5** "**Brown-out Reset (BOR)**").

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note *AN607, Power-up Trouble Shooting* (DS0000607).

# 3.3 **Power-up Timer (PWRT)**

The Power-up Timer provides a fixed 72 ms (nominal) time out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the WDT oscillator. For more information, see **Section 7.3** "Internal Clock Modes". The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip and vary due to:

- VDD variation

- Temperature variation

- · Process variation

See DC parameters for details (Section 23.0 "Electrical Specifications").

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word.

# 3.4 Watchdog Timer (WDT)

The WDT has the following features:

- Shares an 8-bit prescaler with Timer0

- Time-out period is from 17 ms to 2.2 seconds, nominal

- Enabled by a Configuration bit

WDT is cleared under certain conditions described in Table 3-3.

#### 3.4.1 WDT OSCILLATOR

The WDT derives its time base from 31 kHz internal oscillator.

#### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0                | R/W-0                 | R/W-0 | R/W-x |

|-------|-------|--------|-------|----------------------|-----------------------|-------|-------|

| GIE   | PEIE  | TMR0IE | INTE  | RABIE <sup>(1)</sup> | TMR0IF <sup>(2)</sup> | INTF  | RABIF |

| bit 7 |       |        |       |                      |                       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7  | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts                                                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6  | <ul> <li>0 = Disables all interrupts</li> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all unmasked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul> |

| bit 5  | <b>TMROIE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                           |

| bit 4  | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                           |

| bit 3  | <b>RABIE:</b> PORTA or PORTB Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PORTA or PORTB change interrupt<br>0 = Disables the PORTA or PORTB change interrupt                         |

| bit 2  | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                               |

| bit 1  | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred (must be cleared in software)<br>0 = The INT external interrupt did not occur                                         |

| bit 0  | <b>RABIF:</b> PORTA or PORTB Change Interrupt Flag bit<br>1 = When at least one of the PORTA or PORTB general purpose I/O pins changed state (must be<br>cleared in software)                          |

| Note 1 | 0 = None of the PORTA or PORTB general purpose I/O pins have changed state                                                                                                                             |

- Note 1: The appropriate bits in the IOCB register must also be set.

- 2: TMR0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing TMR0IF bit.

# 9.1 ADC Configuration

When configuring and using the ADC, the following functions must be considered:

- Port Configuration

- · Channel selection

- ADC conversion clock source

- Interrupt control

#### 9.1.1 PORT CONFIGURATION

When converting analog signals, the I/O pin selected as the input channel should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 6.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 9.1.2 CHANNEL SELECTION

There are 14 channel selections available:

- AN<11:0> pins

- Temperature Indicator

- FVR (Fixed Voltage Reference) Output

Refer to Section 11.0 "Temperature Indicator Module" and Section 10.0 "Fixed Voltage Reference" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2 "ADC Operation"** for more information.

#### 9.1.3 CONVERSION CLOCK

The source of the conversion clock is softwareselectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 10 TAD periods as shown in Figure 9-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in Section 23.0 "Electrical Specifications" for more information. Table 9-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock Period (TAD) |           | Device Frequency (Fosc)     |                             |                               |                               |

|------------------------|-----------|-----------------------------|-----------------------------|-------------------------------|-------------------------------|

| ADC<br>Clock Source    | ADCS<2:0> | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                         |

| Fosc/2                 | 000       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                        |

| Fosc/4                 | 100       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                        |

| Fosc/8                 | 001       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8 μs <b>(5)</b>               |

| Fosc/16                | 101       | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <b><sup>(5)</sup></b> |

| Fosc/32                | 010       | 2.0 μs                      | 4.0 μs                      | 8 μs <b>(5)</b>               | 32.0 μs <sup>(3)</sup>        |

| Fosc/64                | 110       | 4.0 μs                      | 8 μs <b>(5)</b>             | 16.0 μs <b><sup>(5)</sup></b> | 64.0 μs <sup>(3)</sup>        |

| FRC                    | x11       | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup>   |

Legend: Shaded cells are outside of the recommended range.

- Note 1: The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

- 5: Recommended values for VDD  $\leq$  2.0V and temperature -40°C to 85°C. The 16.0  $\mu$ s setting should be avoided for temperature > 85°C.

#### 13.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescaler counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 13.4 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 13.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 13.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 13.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 gate count enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 13.5.1 TIMER1 GATE COUNT ENABLE

The Timer1 gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 gate is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate  $(\overline{T1G})$  input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 13-3 for timing details.

| TABLE 13-3: | TIMER1 GATE ENABLE |

|-------------|--------------------|

|             | SELECTIONS         |

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 13.5.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 13-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                       |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)               |

| 10    | Timer2 match PR2<br>(TMR2 increments to match PR2)                    |

| 11    | Count Enabled by WDT Overflow<br>(Watchdog Time-out interval expired) |

# 13.10 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 13-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | U-0 | R/W-0  | U-0 | R/W-0  |

|---------|---------|---------|---------|-----|--------|-----|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | —   | T1SYNC | _   | TMR10N |

| bit 7   |         |         |         |     |        |     | bit 0  |

| Legend:                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-6 | TMR1CS<1:0>: Timer1 Clock Source Select bits<br>11 = Reserved                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>10 = Timer1 clock source is pin or oscillator. External clock from T1CKI pin (on the rising edge)</li> <li>01 = Timer1 clock source is system clock (Fosc)</li> <li>00 = Timer1 clock source is instruction clock (Fosc/4)</li> </ul> |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                                                                                                           |

|         | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value                                                                                                                                                                                             |

|         | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                                                                                             |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                     |

| bit 2   | <b>TISYNC</b> : Timer1 External Clock Input Synchronization Control bit                                                                                                                                                                        |

| Dit 2   | $\underline{\text{TMR1CS}(1:0)} = 1 \text{X}$                                                                                                                                                                                                  |

|         | 1 = Do not synchronize external clock input                                                                                                                                                                                                    |

|         | 0 = Synchronize external clock input with system clock (Fosc)                                                                                                                                                                                  |

|         | <u>TMR1CS&lt;1:0&gt; = <math>0x</math></u><br>This bit is ignored. Timer1 uses the internal clock when TMR1CS<1:0> = 1x.                                                                                                                       |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                                                                     |

| bit 0   | TMR10N: Timer1 On bit                                                                                                                                                                                                                          |

|         | 1 = Enables Timer1                                                                                                                                                                                                                             |

|         | 0 = Stops Timer1<br>Clears Timer1 gate flip-flop                                                                                                                                                                                               |

|         |                                                                                                                                                                                                                                                |

# 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- · Sleep operation

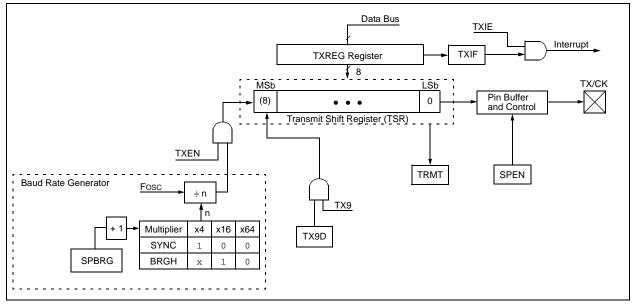

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

#### FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

#### 16.1 AUSART Asynchronous Mode

The AUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(baud rate). An on-chip dedicated 8-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. Refer to Table 16-5 for examples of baud rate Configurations.

The AUSART transmits and receives the LSb first. The AUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 16.1.1 AUSART ASYNCHRONOUS TRANSMITTER

The AUSART transmitter block diagram is shown in Figure 16-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 16.1.1.1 Enabling the Transmitter

The AUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the TX/CK I/O pin as an output.

- Note 1: When the SPEN bit is set the RX/DT I/O pin is automatically configured as an input, regardless of the state of the corresponding TRIS bit and whether or not the AUSART receiver is enabled. The RX/ DT pin data can be read via a normal PORT read but PORT latch data output is precluded.

- 2: The TXIF transmitter interrupt flag is set when the TXEN enable bit is set.

#### 16.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 16.1.1.3 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the AUSART transmitter is enabled and no character is being held for transmission in TXREG. In other words, the TXIF bit is only clear when TSR is busy with a character and a new character has been queued for transmission in TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever TXREG is empty, regardless of the state of the TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to TXREG.

# PIC16(L)F720/721

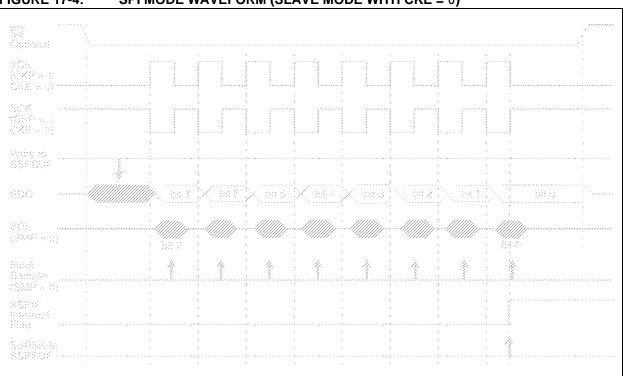

#### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

#### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

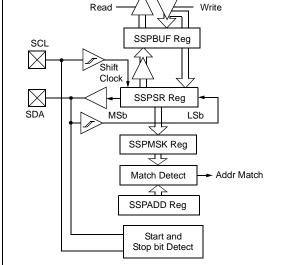

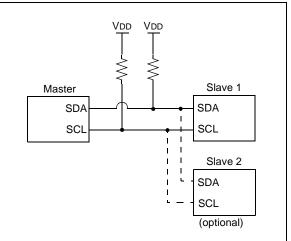

# 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

## 22.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 22.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 22.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 22.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 23.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | 40°C to +125°C            |

|----------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                            |                           |

| Voltage on VDD with respect to Vss, PIC16F720/721                                                              | 0.3V to +6.5V             |

| Voltage on VDD with respect to Vss, PIC16LF720/721                                                             | 0.3V to +4.0V             |

| Voltage on MCLR with respect to Vss                                                                            | 0.3V to +9.0V             |

| Voltage on all other pins with respect to Vss                                                                  | 0.3V to (VDD + 0.3V)      |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                    |

| Maximum current out of Vss pin                                                                                 |                           |

| Maximum current into VDD pin                                                                                   | 70 mA                     |

| Clamp current, Iк (VPIN < 0 or VPIN > VDD)                                                                     |                           |

| Maximum output current sunk by any I/O pin                                                                     | 25 mA                     |

| Maximum output current sourced by any I/O pin                                                                  | 25 mA                     |

| Maximum current sunk by all ports, -40°C $\leq$ Ta $\leq$ +85°C for industrial                                 | 200 mA                    |

| Maximum current sunk by all ports, -40°C $\leq$ Ta $\leq$ +125°C for extended                                  | 90 mA                     |

| Maximum current sourced by all ports, $40^{\circ}C \le T_A \le +85^{\circ}C$ for industrial                    | 140 mA                    |

| Maximum current sourced by all ports, -40°C $\leq$ TA $\leq$ +125°C for extended                               | 65 mA                     |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\sum$ IOH} + $\sum$ {(VDD IOL). | ) – Vон) x Iон} + ∑(Vol x |

| + NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause pe                            | ermanent damage to the    |

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

# 23.4 DC Characteristics: PIC16(L)F720/721-I/E (Continued)

| DC CHARACTERISTICS                |       |                           | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C $\le$ TA $\le$ +85°C for industrial} \\ \ -40°C $\le$ TA $\le$ +125°C for extended \end{array}$ |      |       |            |                                                                      |  |

|-----------------------------------|-------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|----------------------------------------------------------------------|--|

| Param.<br>No. Sym. Characteristic |       | Min.                      | Тур†                                                                                                                                                                                                                  | Max. | Units | Conditions |                                                                      |  |

| D133                              | TPEW  | Erase/Write cycle time    | -                                                                                                                                                                                                                     |      | 2.8   | ms         | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D134*                             | TRETD | Characteristic Retention  | _                                                                                                                                                                                                                     | 40   | —     | Year       | Provided no other specifications are violated                        |  |

| D135                              | EHEFC | High-Endurance Flash Cell | 100K                                                                                                                                                                                                                  | _    | _     | E/W        | 0°C to +60°C<br>Lower byte,<br>Last 128 Addresses in Flash<br>memory |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

# PIC16(L)F720/721

#### OSCILLATOR PARAMETERS<sup>(1)</sup> **TABLE 23-2:**

#### Standard Operating Conditions (unless otherwise stated)

4000 × T . ......

| Operatin      | Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                                                           |                    |      |      |      |       |                                                                                               |  |

|---------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Sym                                                           | Characteristic                                                                            | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                                    |  |

| OS08          | HFosc                                                         | Internal Calibrated HFINTOSC<br>Frequency <sup>(2, 3)</sup>                               | ± 2%               |      | 16.0 | —    | MHz   | $\begin{array}{l} 0^{\circ}C \leq TA \leq +60^{\circ}C, \\ V\text{DD} \geq 2.5 V \end{array}$ |  |

|               |                                                               |                                                                                           | $\pm$ 3%           | —    | 16.0 | —    | MHz   | +60°C $\leq$ TA $\leq$ +85°C,<br>VDD $\geq$ 2.5V                                              |  |

|               |                                                               |                                                                                           | $\pm5\%$           | _    | 16.0 | —    | MHz   | $-40^{\circ}C \le TA \le +125^{\circ}C$                                                       |  |

| OS08          | MFosc                                                         | Internal Calibrated MFINTOSC<br>Frequency <sup>(2, 3)</sup>                               | ± 2%               | _    | 500  | —    | kHz   | $\begin{array}{l} 0^{\circ}C \leq TA \leq +60^{\circ}C, \\ V\text{DD} \geq 2.5 V \end{array}$ |  |

|               |                                                               |                                                                                           | $\pm$ 3%           | —    | 500  | —    | kHz   | +60°C $\leq$ TA $\leq$ +85°C,<br>VDD $\geq$ 2.5V                                              |  |

|               |                                                               |                                                                                           | $\pm5\%$           | _    | 500  | —    | kHz   | $-40^{\circ}C \leq TA \leq +125^{\circ}C$                                                     |  |

| OS10*         | TIOSC ST                                                      | HFINTOSC 16 MHz and<br>MFINTOSC 500 kHz<br>Oscillator Wake-up from Sleep<br>Start-up Time |                    |      | 5    | 8    | μS    |                                                                                               |  |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

- 3: The frequency tolerance of the internal oscillator is ±2% from 0-60°C and ±3% from 60-85°C (see Figure 23-5).

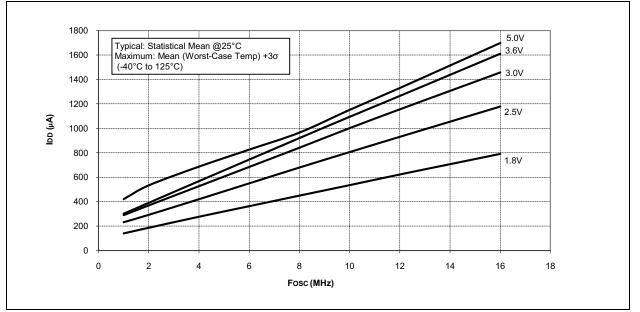

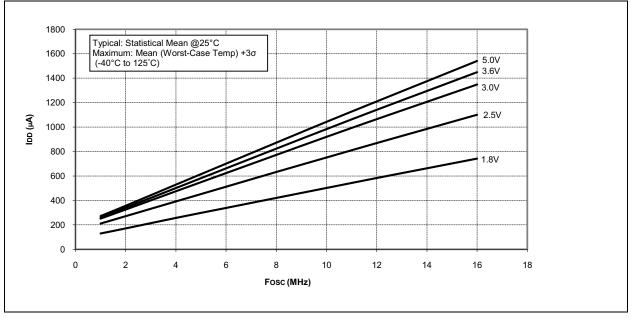

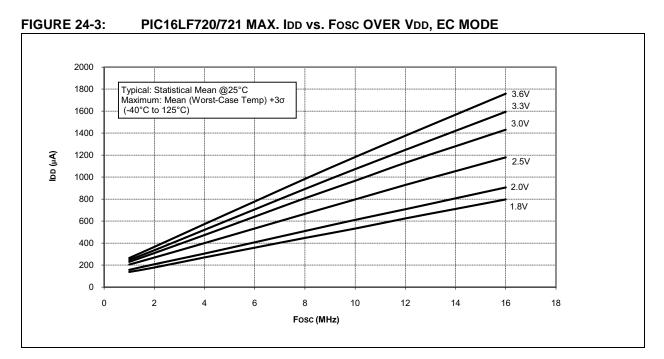

# 24.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

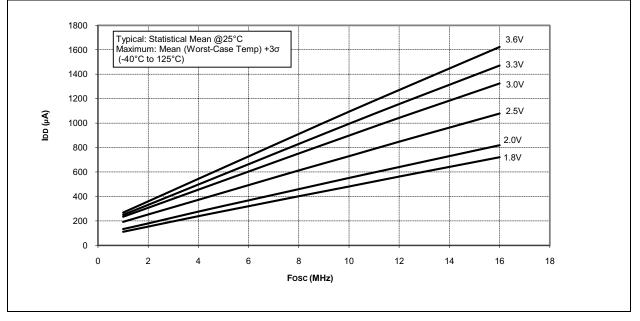

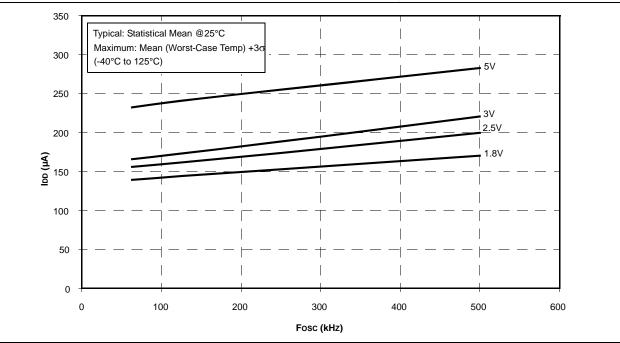

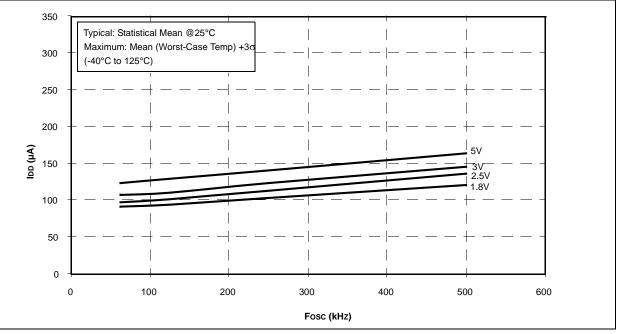

#### FIGURE 24-5: PIC16F720/721 MAX. IDD vs. Fosc OVER VDD, MFINTOSC

# 25.0 PACKAGING INFORMATION

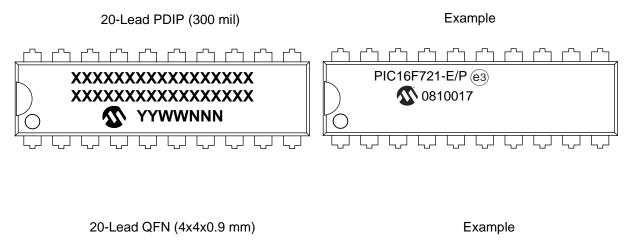

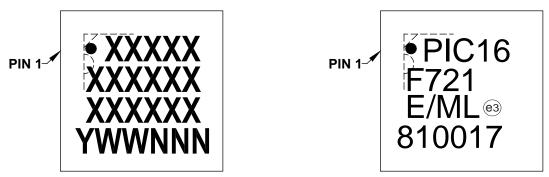

# 25.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator (e3)<br>can be found on the outer packaging for this package. |

|--------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                               |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

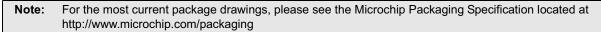

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimensio                 | MIN         | NOM  | MAX      |      |  |

| Contact Pitch            |             |      | 0.65 BSC |      |  |

| Contact Pad Spacing      |             |      | 7.20     |      |  |

| Contact Pad Width (X20)  | X1          |      |          | 0.45 |  |

| Contact Pad Length (X20) | Y1          |      |          | 1.75 |  |

| Distance Between Pads    |             | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A