Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

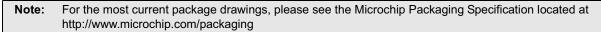

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf721-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 2-2:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address                         | Name           | Bit 7   | Bit 6            | Bit 5         | Bit 4           | Bit 3                   | Bit 2           | Bit 1         | Bit 0    | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------------------|----------------|---------|------------------|---------------|-----------------|-------------------------|-----------------|---------------|----------|----------------------|---------------------------------|

| Bank 1                          |                |         |                  |               |                 |                         |                 |               |          |                      |                                 |

| 80h <sup>(</sup> 2 <sup>)</sup> | INDF           | Addres  | sing this locati | on uses conte | nts of FSR to a | address data n          | nemory (not     | a physical re | egister) | XXXX XXXX            | XXXX XXXX                       |

| 81h                             | OPTION_<br>REG | RABPU   | INTEDG           | TOCS          | TOSE            | PSA                     | PS2             | PS1           | PS0      | 1111 1111            | 1111 1111                       |

| 82h <sup>(</sup> <b>2</b> )     | PCL            |         |                  | Program C     | Counter (PC) Le | east Significar         | nt Byte         |               |          | 0000 0000            | 0000 0000                       |

| 83h <sup>(</sup> <b>2</b> )     | STATUS         | IRP     | RP1              | RP0           | TO              | PD                      | Z               | DC            | С        | 0001 1xxx            | 000q quuu                       |

| 84h <sup>(</sup> <b>2</b> )     | FSR            |         |                  | Indirec       | t Data Memory   | Address Poin            | ter             |               |          | xxxx xxxx            | uuuu uuuu                       |

| 85h <sup>(5)</sup>              | TRISA          | _       | _                | TRISA5        | TRISA4          | (4)                     | TRISA2          | TRISA1        | TRISA0   | 11 -111              | 11 -111                         |

| 86h                             | TRISB          | TRISB7  | TRISB6           | TRISB5        | TRISB4          | _                       | _               | _             | _        | 1111                 | 1111                            |

| 87h                             | TRISC          | TRISC7  | TRISC6           | TRISC5        | TRISC4          | TRISC3                  | TRISC2          | TRISC1        | TRISC0   | 1111 1111            | 1111 1111                       |

| 88h                             | —              |         |                  |               | Unimplem        | ented                   |                 |               |          | —                    | —                               |

| 89h                             | —              |         |                  |               | Unimplem        | ented                   |                 |               |          | —                    | —                               |

| 8Ah <sup>(</sup> 1),( 2)        | PCLATH         | —       | —                | —             | Write Buff      | fer for the upp         | er 5 bits of th | ne Program    | Counter  | 0 0000               | 0 0000                          |

| 8Bh <sup>(</sup> 2)             | INTCON         | GIE     | PEIE             | TMR0IE        | INTE            | RABIE                   | TMR0IF          | INTF          | RABIF    | 0000 000x            | 0000 000x                       |

| 8Ch                             | PIE1           | TMR1GIE | ADIE             | RCIE          | TXIE            | SSPIE                   | CCP1IE          | TMR2IE        | TMR1IE   | 0000 0000            | 0000 0000                       |

| 8Dh                             | _              |         |                  |               | Unimplem        | ented                   | •               |               |          | _                    | _                               |

| 8Eh                             | PCON           | —       | —                | —             | —               | —                       | _               | POR           | BOR      | dd                   | uu                              |

| 8Fh                             | T1GCON         | TMR1GE  | T1GPOL           | T1GTM         | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL          | T1GSS1        | T1GSS0   | 0000 0x00            | uuuu uxuu                       |

| 90h                             | OSCCON         | —       | _                | IRCF1         | IRCF0           | ICSL                    | ICSS            | _             | _        | 10 qq                | 10 qq                           |

| 91h                             | OSCTUNE        | —       | _                | TUN5          | TUN4            | TUN3                    | TUN2            | TUN1          | TUN0     | 00 0000              | uu uuuu                         |

| 92h                             | PR2            |         |                  | Tim           | er2 module Pe   | riod Register           |                 |               |          | 1111 1111            | 1111 1111                       |

| 93h                             | SSPADD         |         |                  |               | ADD<7:          | 0>                      |                 |               |          | 0000 0000            | 0000 0000                       |

| 93h <sup>(</sup> <b>3</b> )     | SSPMSK         |         |                  |               | MSK<7           | 0>                      |                 |               |          | 1111 1111            | 1111 1111                       |

| 94h                             | SSPSTAT        | SMP     | CKE              | D/A           | Р               | S                       | R/W             | UA            | BF       | 0000 0000            | 0000 0000                       |

| 95h                             | WPUA           | _       | _                | WPUA5         | WPUA4           | WPUA3                   | WPUA2           | WPUA1         | WPUA0    | 11 1111              | 11 1111                         |

| 96h                             | IOCA           | _       | -                | IOCA5         | IOCA4           | IOCA3                   | IOCA2           | IOCA1         | IOCA0    | 00 0000              | 00 0000                         |

| 97h                             | —              |         |                  |               | Unimplem        | ented                   | •               | •             | •        | _                    | _                               |

| 98h                             | TXSTA          | CSRC    | TX9              | TXEN          | SYNC            | —                       | BRGH            | TRMT          | TX9D     | 0000 -010            | 0000 -010                       |

| 99h                             | SPBRG          | BRG7    | BRG6             | BRG5          | BRG4            | BRG3                    | BRG2            | BRG1          | BRG0     | 0000 0000            | 0000 0000                       |

| 9Ah                             | —              |         |                  |               | Unimplem        | ented                   |                 |               |          | —                    | —                               |

| 9Bh                             | _              |         |                  |               | Unimplem        | ented                   |                 |               |          | —                    | —                               |

| 9Ch                             | _              |         |                  |               | Unimplem        | ented                   |                 |               |          | —                    | _                               |

| 9Dh                             | FVRCON         | FVRRDY  | FVREN            | TSEN          | TSRNG           | _                       | _               | ADFVR1        | ADFVR0   | d00000               | d00000                          |

| 9Eh                             | —              |         |                  |               | Unimplem        | ented                   |                 |               | •        | —                    | —                               |

| 9Fh                             | ADCON1         | _       | ADCS2            | ADCS1         | ADCS0           | _                       | _               |               |          | -000                 | -000                            |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. Accessible only when SSPM<3:0> = 1001. 2:

3:

4: This bit is unimplemented and reads as '1'.

5: See Register 6-2.

#### **TABLE 2-2:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address                      | Name           | Bit 7  | Bit 6                                                        | Bit 5         | Bit 4           | Bit 3           | Bit 2       | Bit 1         | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------------|----------------|--------|--------------------------------------------------------------|---------------|-----------------|-----------------|-------------|---------------|---------|----------------------|---------------------------------|

| Bank 3                       |                |        |                                                              |               |                 |                 |             |               |         |                      |                                 |

| 180h <sup>(</sup> <b>2</b> ) | INDF           | Addres | sing this location                                           | on uses conte | nts of FSR to a | address data n  | nemory (not | a physical re | gister) | xxxx xxxx            | xxxx xxxx                       |

| 181h                         | OPTION_<br>REG | RABPU  | INTEDG                                                       | TOCS          | TOSE            | PSA             | PS2         | PS1           | PS0     | 1111 1111            | 1111 1111                       |

| 182h <sup>(</sup> <b>2</b> ) | PCL            |        |                                                              | Program C     | Counter (PC) Le | east Significar | nt Byte     |               |         | 0000 0000            | 0000 0000                       |

| 183h <sup>(</sup> <b>2</b> ) | STATUS         | IRP    | RP1                                                          | RP0           | TO              | PD              | Z           | DC            | С       | 0001 1xxx            | 000q quuu                       |

| 184h <sup>(</sup> <b>2</b> ) | FSR            |        |                                                              | Indirec       | t Data Memory   | Address Poin    | iter        |               |         | xxxx xxxx            | uuuu uuuu                       |

| 185h                         | ANSELA         | -      | _                                                            | _             | ANSA4           | _               | ANSA2       | ANSA1         | ANSA0   | 1 -111               | 1 -111                          |

| 186h                         | ANSELB         | _      | _                                                            | ANSB5         | ANSB4           |                 | _           | _             | _       | 11                   | 11                              |

| 187h                         | ANSELC         | ANSC7  | ANSC6                                                        | _             | —               | ANSC3           | ANSC2       | ANSC1         | ANSC0   | 11 1111              | 11 1111                         |

| 188h                         | _              |        |                                                              |               | Unimplem        | ented           | •           |               |         | _                    | _                               |

| 18Ah <b>( 1),( 2)</b>        | PCLATH         | -      | — — Write Buffer for the upper 5 bits of the Program Counter |               |                 |                 |             |               |         | 0 0000               | 0 0000                          |

| 18Bh <sup>(</sup> <b>2</b> ) | INTCON         | GIE    | PEIE                                                         | TMR0IE        | INTE            | RABIE           | TMR0IF      | INTF          | RABIF   | 0000 000x            | 0000 000x                       |

| 18Ch                         | PMCON1         | (4)    | CFGS                                                         | LWLO          | FREE            | —               | WREN        | WR            | RD      | 1000 -000            | 1000 -000                       |

| 18Dh                         | PMCON2         |        | Program Memory Control Register 2 (not a physical register)  |               |                 |                 |             |               |         |                      |                                 |

| 190h                         | _              |        | Unimplemented                                                |               |                 |                 |             |               |         | _                    | _                               |

| 191h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 192h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 193h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 194h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 195h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 196h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 197h                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 198h                         | _              |        | Unimplemented                                                |               |                 |                 |             |               |         | _                    | _                               |

| 199h                         | —              |        | Unimplemented                                                |               |                 |                 |             |               |         | _                    | —                               |

| 19Ah                         | —              |        | Unimplemented                                                |               |                 |                 |             |               |         | _                    | —                               |

| 19Bh                         | —              |        | Unimplemented                                                |               |                 |                 |             |               |         | _                    | —                               |

| 19Ch                         | —              |        |                                                              |               | Unimplem        | ented           |             |               |         | —                    | —                               |

| 19Dh                         | —              |        |                                                              |               | Unimplem        | ented           |             |               |         | —                    | —                               |

| 19Eh                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

| 19Fh                         | _              |        |                                                              |               | Unimplem        | ented           |             |               |         | _                    | _                               |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: Accessible only when SSPM<3:0> = 1001.

4: This bit is unimplemented and reads as '1'.

5: See Register 6-2

5: See Register 6-2.

### FIGURE 3-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD): CASE 3

#### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0                | R/W-0                 | R/W-0 | R/W-x |

|-------|-------|--------|-------|----------------------|-----------------------|-------|-------|

| GIE   | PEIE  | TMR0IE | INTE  | RABIE <sup>(1)</sup> | TMR0IF <sup>(2)</sup> | INTF  | RABIF |

| bit 7 |       |        |       |                      |                       |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 7  | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts                                                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6  | <ul> <li>0 = Disables all interrupts</li> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all unmasked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul> |

| bit 5  | <b>TMROIE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                           |

| bit 4  | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                           |

| bit 3  | <b>RABIE:</b> PORTA or PORTB Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PORTA or PORTB change interrupt<br>0 = Disables the PORTA or PORTB change interrupt                         |

| bit 2  | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                               |

| bit 1  | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred (must be cleared in software)<br>0 = The INT external interrupt did not occur                                         |

| bit 0  | <b>RABIF:</b> PORTA or PORTB Change Interrupt Flag bit<br>1 = When at least one of the PORTA or PORTB general purpose I/O pins changed state (must be<br>cleared in software)                          |

| Note 1 | 0 = None of the PORTA or PORTB general purpose I/O pins have changed state                                                                                                                             |

- Note 1: The appropriate bits in the IOCB register must also be set.

- 2: TMR0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing TMR0IF bit.

#### 4.5.3 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 4-3.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-3: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0   | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---------|-------|------|------|-------|--------|--------|--------|

| TMR1GIF | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7   |       |      |      |       |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| L:1.7 | TNDAOLE Time and Only Internated Elements                                |

|-------|--------------------------------------------------------------------------|

| bit 7 | TMR1GIF: Timer1 Gate Interrupt Flag bit                                  |

|       | 1 = Timer1 gate is inactive                                              |

|       | 0 = Timer1 gate is active                                                |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                   |

|       | 1 = A/D conversion complete (must be cleared in software)                |

|       | 0 = A/D conversion has not completed or has not been started             |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                                   |

|       | 1 = The USART receive buffer is full (cleared by reading RCREG)          |

|       | 0 = The USART receive buffer is not full                                 |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                                  |

|       | 1 = The USART transmit buffer is empty (cleared by writing to TXREG)     |

|       | 0 = The USART transmit buffer is full                                    |

| bit 3 | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit                  |

|       | 1 = The Transmission/Reception is complete (must be cleared in software) |

|       | 0 = Waiting to Transmit/Receive                                          |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                                          |

|       | Capture mode:                                                            |

|       | 1 = A TMR1 register capture occurred (must be cleared in software)       |

|       | 0 = No TMR1 register capture occurred                                    |

|       | Compare mode:                                                            |

|       | 1 = A TMR1 register compare match occurred (must be cleared in software) |

|       | 0 = No TMR1 register compare match occurred                              |

|       | PWM mode:                                                                |

|       | Unused in this mode                                                      |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                                 |

|       | 1 = A Timer2 to PR2 match occurred (must be cleared in software)         |

|       | 0 = No Timer2 to PR2 match occurred                                      |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                               |

|       | 1 = The TMR1 register overflowed (must be cleared in software)           |

|       | 0 = The TMR1 register did not overflow                                   |

|       |                                                                          |

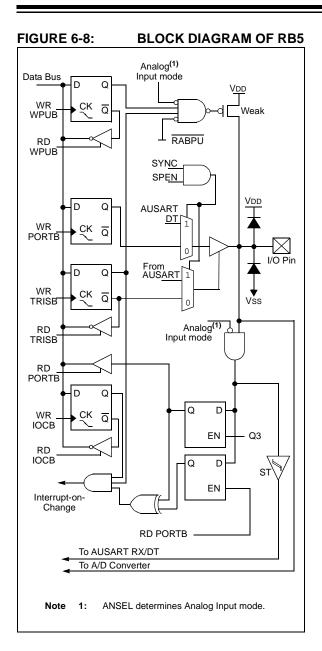

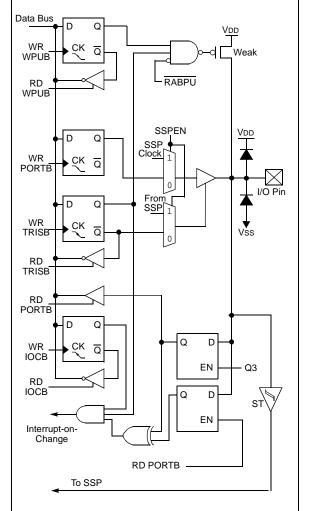

#### FIGURE 6-9:

#### **BLOCK DIAGRAM OF RB6**

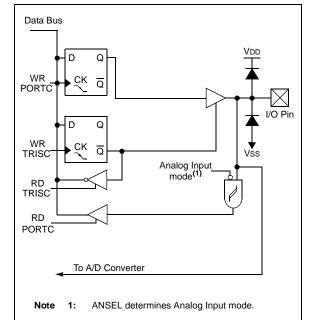

#### 6.3 **PORTC and TRISC Registers**

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 6-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-3 shows how to initialize PORTC.

Reading the PORTC register (Register 6-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register (Register 6-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-3: INITIALIZING PORTC

| BANKSEL PORTC     | ;                      |

|-------------------|------------------------|

| CLRF PORTC        | ;Init PORTC            |

| BANKSEL TRISC     | ;                      |

| MOVLW B'00001100' | ;Set RC<3:2> as inputs |

| MOVWF TRISC       | ;and set RC<7:4,1:0>   |

|                   | ;as outputs            |

|                   |                        |

#### 6.3.1 ANSELC REGISTER

The ANSELC register (Register 6-13) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### 6.3.2 RC0/AN4

Figure 6-11 shows the diagram for this pin. The RC0 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

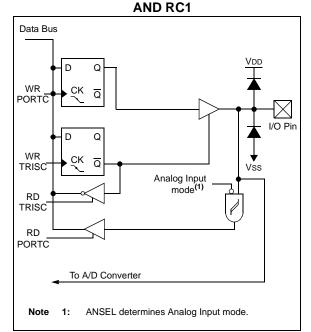

#### 6.3.3 RC1/AN5

Figure 6-11 shows the diagram for this pin. The RC1 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

#### 6.3.4 RC2/AN6

Figure 6-12 shows the diagram for this pin. The RC2 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

#### 6.3.5 RC3/AN7

Figure 6-12 shows the diagram for this pin. The RC3 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

#### 6.3.6 RC4

Figure 6-13 shows the diagram for this pin. The RC4 pin functions as one of the following:

• General purpose I/O

#### 6.3.7 RC5/CCP1

Figure 6-14 shows the diagram for this pin. The RC5 pin is configurable to function as one of the following:

- General purpose I/O

- Capture, Compare or PWM (one output)

#### 6.3.8 RC6/AN8/SS

Figure 6-15 shows the diagram for this pin. The RC6 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

- SS input to SSP

#### 6.3.9 RC7/AN9/SDO

Figure 6-16 shows the diagram for this pin. The RC7 pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the A/D

- SDO output of SSP

## FIGURE 6-11: BLOCK DIAGRAM OF RC0

### FIGURE 6-12:

#### BLOCK DIAGRAM OF RC2 AND RC3

#### 7.4 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 7-1) displays the status and allows frequency selection of the internal oscillator (INTOSC) system clock. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Status Locked bits (ICSL)

- Status Stable bits (ICSS)

#### REGISTER 7-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0   | U-0 | R/W-1 | R/W-0 | R-q  | R-q  | U-0 | U-0   |

|-------|-----|-------|-------|------|------|-----|-------|

| —     | —   | IRCF1 | IRCF0 | ICSL | ICSS | —   | —     |

| bit 7 |     |       |       |      |      |     | bit 0 |

| Legend:                        |                  |                                    |                    |  |  |  |

|--------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit               | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR              | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| q = Value depends on condition |                  |                                    |                    |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | IRCF<1:0>: Internal Oscillator Frequency Select bits                                                                                               |

|         | <u>When PLLEN = 1 (16 MHz HFINTOSC)</u>                                                                                                            |

|         | 11 = 16 MHz                                                                                                                                        |

|         | 10 = 8 MHz (default)                                                                                                                               |

|         | 01 = 4 MHz                                                                                                                                         |

|         | 00 = 2 MHz                                                                                                                                         |

|         | <u>When PLLEN = 0 (500 kHz MFINTOSC)</u>                                                                                                           |

|         | 11 = 500 kHz                                                                                                                                       |

|         | 10 = 250  kHz (default)                                                                                                                            |

|         | 01 = 125 kHz                                                                                                                                       |

|         | 00 = 62.5 kHz                                                                                                                                      |

| bit 3   | ICSL: Internal Clock Oscillator Status Locked bit                                                                                                  |

|         | <ul> <li>1 = 16 MHz/500 kHz internal oscillator is at least 2% accurate</li> <li>0 = 16 MHz/500 kHz internal oscillator not 2% accurate</li> </ul> |

| bit 2   | ICSS: Internal Clock Oscillator Status Stable bit                                                                                                  |

|         | 1 = 16  MHz/500  kHz internal oscillator is at least 0.5% accurate<br>0 = 16  MHz/500  kHz internal oscillator not 0.5% accurate                   |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                         |

|                             | 2. ADCO                                                                                                                    |                                                                  |                                   | ISTER I                                      |                  |                 |       |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------|----------------------------------------------|------------------|-----------------|-------|

| U-0                         | R/W-0                                                                                                                      | R/W-0                                                            | R/W-0                             | U-0                                          | U-0              | U-0             | U-0   |

| —                           | ADCS2                                                                                                                      | ADCS1                                                            | ADCS0                             | _                                            | —                | —               | —     |

| bit 7                       |                                                                                                                            |                                                                  |                                   |                                              |                  |                 | bit 0 |

|                             |                                                                                                                            |                                                                  |                                   |                                              |                  |                 |       |

| Legend:                     |                                                                                                                            |                                                                  |                                   |                                              |                  |                 |       |

| R = Readable I              | oit                                                                                                                        | W = Writable                                                     | bit                               | U = Unimpler                                 | nented bit, read | d as '0'        |       |

| -n = Value at P             | OR                                                                                                                         | '1' = Bit is set                                                 |                                   | '0' = Bit is cle                             | ared             | x = Bit is unkr | nown  |

| bit 7<br>bit 6-4<br>bit 3-0 | ADCS<2:0>:<br>000 = Fosc/2<br>001 = Fosc/2<br>010 = Fosc/2<br>011 = Frc (c<br>100 = Fosc/2<br>101 = Fosc/2<br>110 = Fosc/2 | 2<br>33<br>Ilock supplied f<br>4<br>16<br>64<br>Ilock supplied f | n Clock Select<br>from a dedicate | t bits<br>ed RC oscillato<br>ed RC oscillato |                  |                 |       |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  | •      |        |        | •      |        |        | bit 0  |

| Legend:           |                  |                                                 |                    |  |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | Vritable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |  |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

| R-q          | R/W-0                                  | R/W-0                                                                                                                                                                                              | R/W-0           | U-0               | U-0             | R/W-0           | R/W-0  |  |  |  |  |  |

|--------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|--------|--|--|--|--|--|

| FVRRDY       | FVREN                                  | TSEN                                                                                                                                                                                               | TSRNG           |                   | _               | ADFVR1          | ADFVR0 |  |  |  |  |  |

| bit 7        | ·                                      | •                                                                                                                                                                                                  |                 |                   |                 |                 | bit 0  |  |  |  |  |  |

|              |                                        |                                                                                                                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| Legend:      |                                        |                                                                                                                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| R = Readab   | le bit                                 | W = Writable                                                                                                                                                                                       | bit             | U = Unimplen      | nented bit, rea | id as '0'       |        |  |  |  |  |  |

| -n = Value a | t POR                                  | '1' = Bit is se                                                                                                                                                                                    | t               | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |  |  |  |  |  |

| q = Value de | epends on condit                       | ion                                                                                                                                                                                                |                 |                   |                 |                 |        |  |  |  |  |  |

|              |                                        | -                                                                                                                                                                                                  |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 7        |                                        | Fixed Voltage I                                                                                                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

|              |                                        | <ul> <li>0 = Fixed Voltage Reference output is not active or stable</li> <li>1 = Fixed Voltage Reference output is ready for use</li> </ul>                                                        |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 6        |                                        | <b>FVREN:</b> Fixed Voltage Reference Enable bit                                                                                                                                                   |                 |                   |                 |                 |        |  |  |  |  |  |

| JIL O        |                                        | 0 = Fixed Voltage Reference is disabled                                                                                                                                                            |                 |                   |                 |                 |        |  |  |  |  |  |

|              | 1 = Fixed Voltage Reference is enabled |                                                                                                                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 5        |                                        | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup>                                                                                                                                       |                 |                   |                 |                 |        |  |  |  |  |  |

|              |                                        | 0 = Temperature indicator is disabled                                                                                                                                                              |                 |                   |                 |                 |        |  |  |  |  |  |

| <b>b</b> :4  | •                                      | 1 = Temperature indicator is enabled                                                                                                                                                               |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 4        |                                        | <b>TSRNG:</b> Temperature Indicator Range Selection bit <sup>(3)</sup><br>1 = VOUT = VDD - 4VT (High Range)                                                                                        |                 |                   |                 |                 |        |  |  |  |  |  |

|              | 0 = VOUT = VDD - 2VT (Low Range)       |                                                                                                                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 3-2      | Unimplemer                             | nted: Read as                                                                                                                                                                                      | 0'              |                   |                 |                 |        |  |  |  |  |  |

| bit 1-0      | ADFVR<1:0:                             | >: A/D Convert                                                                                                                                                                                     | er Fixed Voltag | ge Reference S    | election bits   |                 |        |  |  |  |  |  |

|              |                                        | 00 = A/D Converter Fixed Voltage Reference Peripheral output is off                                                                                                                                |                 |                   |                 |                 |        |  |  |  |  |  |

|              |                                        | <ul> <li>01 = A/D Converter Fixed Voltage Reference Peripheral output is 1x (1.024V)</li> <li>10 = A/D Converter Fixed Voltage Reference Peripheral output is 2x (2.048V)<sup>(2)</sup></li> </ul> |                 |                   |                 |                 |        |  |  |  |  |  |

|              |                                        |                                                                                                                                                                                                    |                 | nce Peripheral    |                 |                 |        |  |  |  |  |  |

| Note 1: F    | VRRDY is alway                         |                                                                                                                                                                                                    |                 |                   | ·               |                 |        |  |  |  |  |  |

|              | ixed Voltage Ref                       |                                                                                                                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

|              | Section 11 0                           | -                                                                                                                                                                                                  |                 |                   | ional informat  | ion             |        |  |  |  |  |  |

#### REGISTER 10-1: FVRCON: FIXED VOLTAGE REFERENCE REGISTER

3: See Section 11.0 "Temperature Indicator Module" for additional information.

| TABLE 10-2: SUMMARY OF ASSOCIATED FIXED VOLTAGE REFERENCE REGISTER |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Nam  | e  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|------|----|--------|-------|-------|-------|-------|-------|--------|--------|---------------------|

| FVRC | ON | FVRRDY | FVREN | TSEN  | TSRNG |       |       | ADFVR1 | ADFVR0 | 81                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for Fixed Voltage Reference.

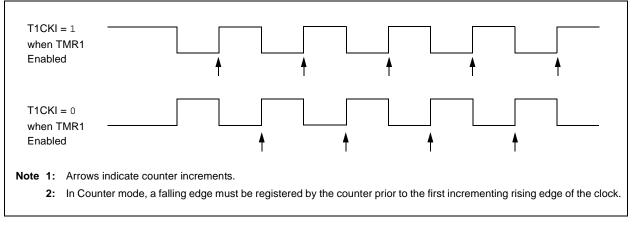

### 13.6 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, these bits must be set:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 13.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, the clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- TMR1GE bit of the T1GCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 13.8 CCP Capture/Compare Time Base

The CCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 15.0 "Capture/ Compare/PWM (CCP) Module".

### 13.9 CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc/4 to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 9.2.5 "Special Event Trigger".

#### FIGURE 13-2: TIMER1 INCREMENTING EDGE

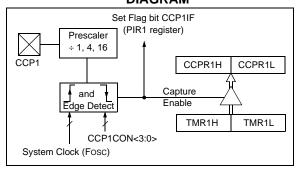

### 15.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register:

- Every falling edge

- · Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCP1IF of the PIR1 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPR1H, CCPR1L register pair is read, the old captured value is overwritten by the new captured value (refer to Figure 15-1).

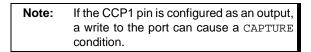

#### 15.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the associated TRIS control bit.

#### FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 15.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode or when Timer1 is clocked at Fosc, the capture operation may not work.

| Note: | Clocking Timer1 from the system clock (Fosc) should not be used in Capture |

|-------|----------------------------------------------------------------------------|

|       | (FOSC) should not be used in Capture                                       |

|       | mode. In order for Capture mode to                                         |

|       | recognize the trigger event on the CCP1                                    |

|       | pin, Timer1 must be clocked from the                                       |

|       | Instruction Clock (Fosc/4) or from an                                      |

|       | external clock source.                                                     |

#### 15.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit of the PIE1 register clear to avoid false interrupts. Additionally, the user should clear the CCP1IF interrupt flag bit of the PIR1 register following any change in Operating mode.

#### 15.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCP1M<3:0> bits of the CCP1CON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCP1CON register before changing the prescaler (refer to Example 15-1).

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ĺ | BANKSEL | CCP1CON     | ;Set Bank bits to point |

|---|---------|-------------|-------------------------|

|   |         |             | ;to CCP1CON             |

|   | CLRF    | CCP1CON     | ;Turn CCP module off    |

|   | MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|   |         |             | ; the new prescaler     |

|   |         |             | ; move value and CCP ON |

|   | MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|   |         |             | ; value                 |

### 15.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

If Timer1 is clocked by FOSC/4, then Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

If Timer1 is clocked by an external clock source, then Capture mode will operate as defined in **Section 15.1** "**Capture Mode**".

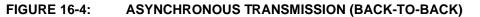

#### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7   | Bit 6                         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

|--------|---------|-------------------------------|--------|--------|--------|--------|--------|--------|---------------------|--|

| INTCON | GIE     | PEIE                          | TMR0IE | INTE   | RABIE  | TMR0IF | INTF   | RABIF  | 37                  |  |

| PIE1   | TMR1GIE | ADIE                          | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 38                  |  |

| PIR1   | TMR1GIF | ADIF                          | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |  |

| RCSTA  | SPEN    | RX9                           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 118                 |  |

| SPBRG  | BRG7    | BRG6                          | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 119                 |  |

| TRISC  | TRISC7  | TRISC6                        | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 58                  |  |

| TXREG  |         | AUSART Transmit Data Register |        |        |        |        |        |        |                     |  |

| TXSTA  | CSRC    | TX9                           | TXEN   | SYNC   |        | BRGH   | TRMT   | TX9D   | 117                 |  |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous transmission.

#### 16.1.2 AUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the AUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 16.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

Note: When the SPEN bit is set, the TX/CK I/O pin is automatically configured as an output, regardless of the state of the corresponding TRIS bit and whether or not the AUSART transmitter is enabled. The PORT latch is disconnected from the output driver so it is not possible to use the TX/CK pin as a general purpose output.

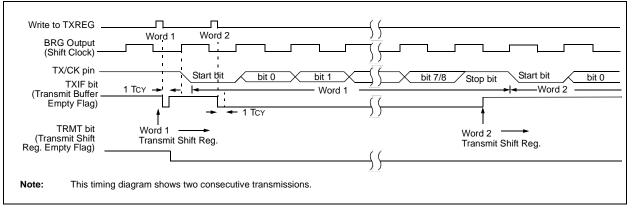

FIGURE 17-2: SPI MODE BLOCK DIAGRAM

#### 17.1.2.4 Slave Select Operation

The  $\overline{SS}$  pin allows Synchronous Slave mode operation. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100). The associated TRIS bit for the  $\overline{SS}$  pin must be set, making  $\overline{SS}$  an input.

In Slave Select mode, when:

- SS = 0, The device operates as specified in Section 17.1.2 "Slave Mode".

- $\overline{SS} = 1$ , The SPI module is held in Reset and the SDO pin will be tri-stated.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is driven high.

- 2: If the SPI is used in Slave mode with CKE set, the SS pin control must be enabled.

When the SPI module resets, the bit counter is cleared to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit. Figure 17-6 shows the timing waveform for such a synchronization event.

| Note: | SSPSR must be reinitialized by writing to |

|-------|-------------------------------------------|

|       | the SSPBUF register before the data can   |

|       | be clocked out of the slave again.        |

#### 17.1.2.5 Sleep in Slave Mode

While in Sleep mode, the slave can transmit/receive data. The SPI Transmit/Receive Shift register operates asynchronously to the device on the externally supplied clock source. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP Interrupt Flag bit will be set and, if enabled, will wake the device from Sleep.

|                          | -<br>-<br>-<br>-<br>- |                                                |                                                                                             |                                               |                                       |                                                                                             |                   |                                         |                                      |                            | (<br>\<br>\                                                                                      |

|--------------------------|-----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------|-------------------|-----------------------------------------|--------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------|

| SCK<br>(CKP = 0          |                       |                                                |                                                                                             |                                               |                                       |                                                                                             |                   |                                         | <b></b>                              |                            |                                                                                                  |

| SCK<br>(CKP = 1          |                       |                                                |                                                                                             |                                               |                                       | :<br> <br>                           |                   |                                         |                                      | ;<br>;<br>;<br>;<br>;<br>; | · · · · · · · · · · · · · · · · · · ·                                                            |

| 9982-09<br>3589889       |                       | 2<br>2<br>2<br>4<br>4<br>8<br>8<br>8<br>8<br>8 | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |                                               |                                       | SSR<br>the<br>be o                                                                          | SR must<br>SSPBUF | be reiniti<br>register b<br>t of the sk | sized by<br>efore the<br>type again. | writing to<br>data can     | (<br>)<br>)<br>)<br>)<br>)<br>)<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; |

| 30X?                     |                       | 4<br>5<br>7<br>838 7<br>8                      | X 88.8                                                                                      |                                               |                                       | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |                   | X                                       |                                      |                            | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5      |

| SDI                      |                       | -//////                                        | $\sim$                                                                                      | 2<br>2<br>2                                   | <pre></pre>                           | 2<br>2<br>2<br>2<br>2                                                                       |                   | $\leftarrow$                            | $\rightarrow$                        |                            |                                                                                                  |

| Input<br>Sample          |                       |                                                | 1                                                                                           |                                               |                                       |                                                                                             | <u> </u>          | 1                                       | <u> </u>                             |                            | <u></u>                                                                                          |

| SSPH<br>Interrupt<br>Pag |                       | -<br>2<br>                                     |                                                                                             | ·<br>·<br>· · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |                                                                                             | •<br>•<br>•       |                                         | S                                    | -<br>-<br>-                | (                                                                                                |

| SSPSR 10<br>SSPRIF       |                       |                                                |                                                                                             |                                               |                                       |                                                                                             |                   |                                         |                                      |                            | \$<br>                                                                                           |

### REGISTER 17-4: SSPSTAT: SYNCHRONOUS SERIAL PORT STATUS REGISTER (I<sup>2</sup>C MODE)

| R/W-0             | R/W-0                                                                                                                                                                                                                                                                      | R-0              | R-0 | R-0                                | R-0 | R-0                | R-0   |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------------------------|-----|--------------------|-------|--|--|

| SMP               | CKE                                                                                                                                                                                                                                                                        | D/A              | Р   | S                                  | R/W | UA                 | BF    |  |  |

| bit 7             |                                                                                                                                                                                                                                                                            |                  |     |                                    |     |                    | bit 0 |  |  |

|                   |                                                                                                                                                                                                                                                                            |                  |     |                                    |     |                    |       |  |  |

| Legend:           |                                                                                                                                                                                                                                                                            |                  |     |                                    |     |                    |       |  |  |

| R = Readable bit  |                                                                                                                                                                                                                                                                            | W = Writable bit |     | U = Unimplemented bit, read as '0' |     |                    |       |  |  |

| -n = Value at POR |                                                                                                                                                                                                                                                                            | '1' = Bit is set |     | '0' = Bit is cleared               |     | x = Bit is unknown |       |  |  |

| bit 7             | <b>SMP</b> : SPI Data Input Sample Phase bit $1 = $ Slew Rate Control (limiting) disabled. Operating in I <sup>2</sup> C Standard mode (100 kHz and 1 MHz). $0 = $ Slew Rate Control (limiting) enabled. Operating in I <sup>2</sup> C Fast mode (400 kHz).                |                  |     |                                    |     |                    |       |  |  |

| bit 6             | <b>CKE</b> : SPI Clock Edge Select bit<br>This bit must be maintained clear. Used in SPI mode only.                                                                                                                                                                        |                  |     |                                    |     |                    |       |  |  |

| bit 5             | <b>D/A</b> : DATA/ADDRESS bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data<br>0 = Indicates that the last byte received or transmitted was address                                                                    |                  |     |                                    |     |                    |       |  |  |

| bit 4             | <ul> <li>P: Stop bit</li> <li>This bit is cleared when the SSP module is disabled, or when the Start bit is detected last.</li> <li>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Stop bit was not detected last</li> </ul> |                  |     |                                    |     |                    |       |  |  |

| bit 3             | <ul> <li>Start bit</li> <li>This bit is cleared when the SSP module is disabled, or when the Stop bit is detected last.</li> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul>  |                  |     |                                    |     |                    |       |  |  |

| bit 2             | <b>R/W</b> : READ/WRITE bit Information<br>This bit holds the R/W bit information following the last address match. This bit is only valid from the<br>address match to the next Start bit, Stop bit or ACK bit.<br>1 = Read<br>0 = Write                                  |                  |     |                                    |     |                    |       |  |  |

| bit 1             | <b>UA</b> : Update Address bit (10-bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the SSPADD register<br>0 = Address does not need to be updated                                                                            |                  |     |                                    |     |                    |       |  |  |

| bit 0             | <b>BF</b> : Buffer Full Status bit<br><u>Receive:</u><br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty<br><u>Transmit:</u><br>1 = Transmit in progress, SSPBUF is full<br>0 = Transmit complete, SSPBUF is empty                       |                  |     |                                    |     |                    |       |  |  |

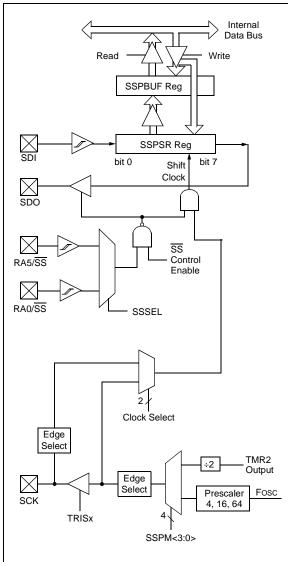

### 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

The device is placed into Program/Verify mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP from 0V to VPP. In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ISCPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F720/721 Flash Memory Programming Specification" (DS41409).

#### FIGURE 20-1: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

#### 22.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.