Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8051                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | SIO, UART/USART                                                        |

| Peripherals                | -                                                                      |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C                                                           |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                        |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c52-16ji |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

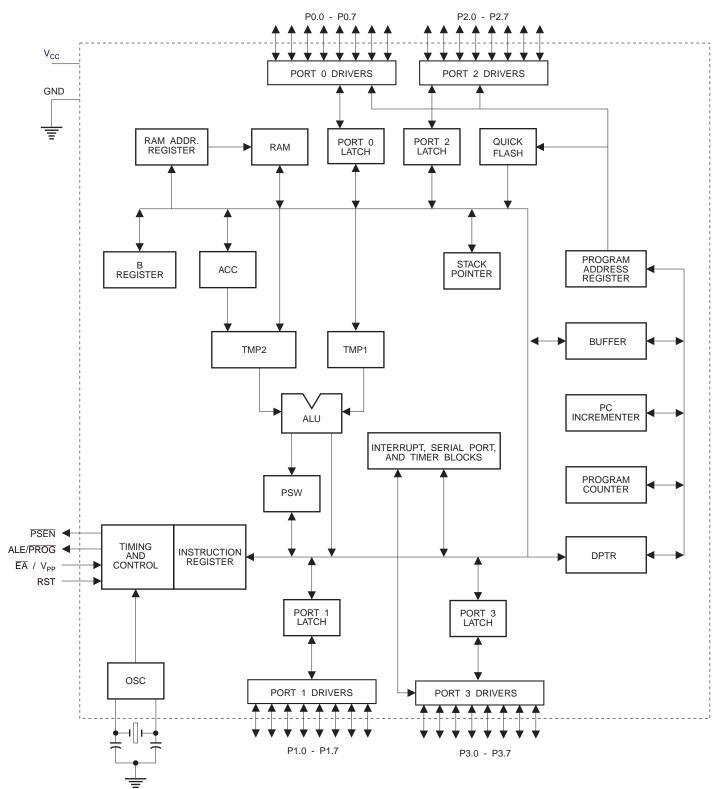

# **Block Diagram**

timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external data memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

## **PSEN**

Program Store Enable is the read strobe to external program memory.

When the AT89C52 is executing code from external program memory, **PSEN** is activated twice each machine cycle, except that two **PSEN** activations are skipped during each access to external data memory.

## EA/VPP

External Access Enable.  $\overline{EA}$  must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed,  $\overline{EA}$  will be internally latched on reset.

$\overline{\text{EA}}$  should be strapped to  $V_{\text{CC}}$  for internal program executions.

This pin also receives the 12-volt programming enable voltage ( $V_{PP}$ ) during Flash programming when 12-volt programming is selected.

## XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

## XTAL2

Output from the inverting oscillator amplifier.

| _    |                   |                   |                    |                    |                 |                 |                  | _    |

|------|-------------------|-------------------|--------------------|--------------------|-----------------|-----------------|------------------|------|

| 0F8H |                   |                   |                    |                    |                 |                 |                  | 0FFH |

| 0F0H | B<br>00000000     |                   |                    |                    |                 |                 |                  | 0F7H |

| 0E8H |                   |                   |                    |                    |                 |                 |                  | 0EFH |

| 0E0H | ACC<br>00000000   |                   |                    |                    |                 |                 |                  | 0E7H |

| 0D8H |                   |                   |                    |                    |                 |                 |                  | 0DFH |

| 0D0H | PSW<br>00000000   |                   |                    |                    |                 |                 |                  | 0D7H |

| 0C8H | T2CON<br>00000000 | T2MOD<br>XXXXXX00 | RCAP2L<br>00000000 | RCAP2H<br>00000000 | TL2<br>00000000 | TH2<br>00000000 |                  | 0CFH |

| 0C0H |                   |                   |                    |                    |                 |                 |                  | 0C7H |

| 0B8H | IP<br>XX000000    |                   |                    |                    |                 |                 |                  | 0BFH |

| 0B0H | P3<br>11111111    |                   |                    |                    |                 |                 |                  | 0B7H |

| 0A8H | IE<br>0X000000    |                   |                    |                    |                 |                 |                  | 0AFH |

| 0A0H | P2<br>11111111    |                   |                    |                    |                 |                 |                  | 0A7H |

| 98H  | SCON<br>00000000  | SBUF<br>XXXXXXXX  |                    |                    |                 |                 |                  | 9FH  |

| 90H  | P1<br>11111111    |                   |                    |                    |                 |                 |                  | 97H  |

| 88H  | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000 | TH1<br>00000000 |                  | 8FH  |

| 80H  | P0<br>11111111    | SP<br>00000111    | DPL<br>00000000    | DPH<br>00000000    |                 |                 | PCON<br>0XXX0000 | 87H  |

| L    |                   | AT89              | C52 🗖              |                    | 1               | 1               | 1 1              |      |

Table 1. AT89C52 SFR Map and Reset Values

# **Special Function Registers**

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future products to invoke

Table 2. T2CON – Timer/Counter 2 Control Registe

new features. In that case, the reset or inactive values of the new bits will always be 0.

**Timer 2 Registers** Control and status bits are contained in registers T2CON (shown in Table 2) and T2MOD (shown in Table 4) for Timer 2. The register pair (RCAP2H, RCAP2L) are the Capture/Reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.

**Interrupt Registers** The individual interrupt enable bits are in the IE register. Two priorities can be set for each of the six interrupt sources in the IP register.r

| T2CON   | Address = 0     | C8H  |      | Reset Value = 0000 0000B |       |     |      |        |  |  |  |

|---------|-----------------|------|------|--------------------------|-------|-----|------|--------|--|--|--|

| Bit Add | Bit Addressable |      |      |                          |       |     |      |        |  |  |  |

| Bit     | TF2             | EXF2 | RCLK | TCLK                     | EXEN2 | TR2 | C/T2 | CP/RL2 |  |  |  |

|         | 7               | 6    | 5    | 4                        | 3     | 2   | 1    | 0      |  |  |  |

Symbol

Function

# **Data Memory**

The AT89C52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. That means the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the address mode used in the instruction

specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions that use direct addressing access SFR space.

For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2).

MOV 0A0H, #data

Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

MOV @R0, #data

Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space.

## Timer 0 and 1

Timer 0 and Timer 1 in the AT89C52 operate the same way as Timer 0 and Timer 1 in the AT89C51.

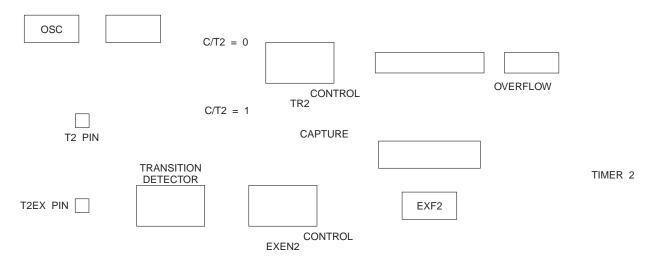

# Timer 2

Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit  $C/\overline{12}$  in the SFR T2CON (shown in Table 2). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 3.

Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.

## **Capture Mode**

In the capture mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter which upon overflow sets bit TF2 in T2CON. This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 performs the same operation, but a 1-to-0 transition at external input T2EX also causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt. The capture mode is illustrated in Figure 1.

## Auto-reload (Up or Down Counter)

Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by the DCEN (Down Counter Enable) bit located in the SFR T2MOD (see Table 4). Upon reset, the DCEN bit is set to 0 so that timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down, depending on the value of the T2EX pin.

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external

## Figure 1. Timer in Capture Mode

Figure 2 shows Timer 2 automatically counting up when DCEN = 0. In this mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 counts up to OFFFFH and then sets the TF2 bit upon overflow. The overflow also causes the timer registers to be reloaded with the 16-bit value in RCAP2H and RCAP2L. The values in Timer in Capture ModeRCAP2H and RCAP2L are preset by software. If EXEN2 = 1, a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at external input T2EX. This transition also sets the EXF2 bit. Both the TF2 and EXF2 bits can generate an interrupt if enabled.

Setting the DCEN bit enables Timer 2 to count up or down, as shown in Figure 3. In this mode, the T2EX pin controls

the direction of the count. A logic 1 at T2EX makes Timer 2 count up. The timer will overflow at 0FFFFH and set the TF2 bit. This overflow also causes the 16-bit value in RCAP2H and RCAP2L to be reloaded into the timer registers, TH2 and TL2, respectively.

A logic 0 at T2EX makes Timer 2 count down. The timer underflows when TH2 and TL2 equal the values stored in RCAP2H and RCAP2L. The underflow sets the TF2 bit and causes 0FFFFH to be reloaded into the timer registers.

The EXF2 bit toggles whenever Timer 2 overflows or underflows and can be used as a 17th bit of resolution. In this operating mode, EXF2 does not flag an interrupt.

# AME

Figure 2. Timer 2 Auto Reload Mode (DCEN = 0)

## Table 4. T2MOD – Timer 2 Mode Control Register

| T2MOD Address = 0C9H |            |                                                                           |   |   |   |   | Reset Value = XXXX XX00B |      |  |  |  |

|----------------------|------------|---------------------------------------------------------------------------|---|---|---|---|--------------------------|------|--|--|--|

| Not Bit A            | ddressable |                                                                           |   |   |   |   |                          |      |  |  |  |

|                      | _          | _                                                                         | - | _ | - | _ | T2OE                     | DCEN |  |  |  |

| Bit                  | 7          | 6                                                                         | 5 | 4 | 3 | 2 | 1                        | 0    |  |  |  |

| Symbol               | Functio    | Function                                                                  |   |   |   |   |                          |      |  |  |  |

| -                    | Not impl   | Not implemented, reserved for future                                      |   |   |   |   |                          |      |  |  |  |

| T2OE                 | Timer 2    | Timer 2 Output Enable bit.                                                |   |   |   |   |                          |      |  |  |  |

| DCEN                 | When se    | When set, this bit allows Timer 2 to be configured as an up/down counter. |   |   |   |   |                          |      |  |  |  |

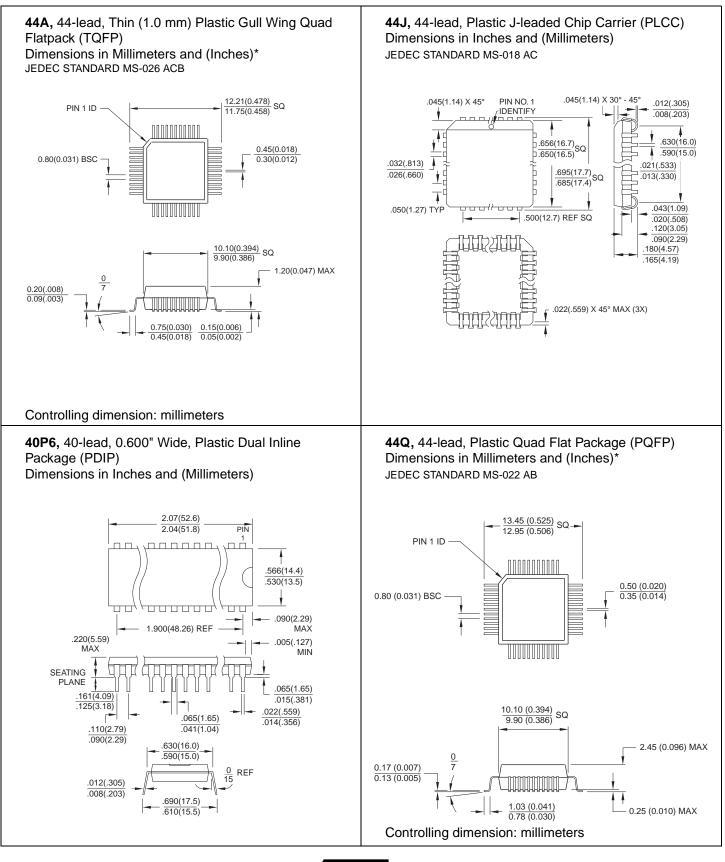

# **Packaging Information**

## **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

## Europe

Atmel U.K., Ltd. Coliseum Business Centre Riverside Way Camberley, Surrey GU15 3YL England TEL (44) 1276-686-677 FAX (44) 1276-686-697

## Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

## Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

## **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

Atmel Rousset Zone Industrielle 13106 Rousset Cedex France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

## *Fax-on-Demand* North America: 1-(800) 292-8635 International: 1-(408) 441-0732

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

BBS 1-(408) 436-4309

#### © Atmel Corporation 1999.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Marks bearing <sup>®</sup> and/or <sup>™</sup> are registered trademarks and trademarks of Atmel Corporation.

Terms and product names in this document may be trademarks of others.