Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324j2ta |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|     | 12.6 CLOCK AND TIMING CHARACTERISTICS                       | 124 |

|-----|-------------------------------------------------------------|-----|

|     | 12.6.1 General Timings                                      | 124 |

|     | 12.6.2 External Clock Source                                |     |

|     | 12.6.3 Crystal and Ceramic Resonator Oscillators            |     |

|     | 12.6.4 RC Oscillators                                       |     |

|     | 12.6.5 PLL Characteristics                                  |     |

|     | 12.7 MEMORY CHARACTERISTICS                                 |     |

|     | 12.7.1 RAM and Hardware Registers                           |     |

|     | 12.7.2 FLASH Memory                                         |     |

|     |                                                             |     |

|     | 12.8.1 Functional EMS (Electro Magnetic Susceptibility)     |     |

|     | 12.8.3 Absolute Maximum Ratings (Electrical Sensitivity)    |     |

|     | 12.9 I/O PORT PIN CHARACTERISTICS                           |     |

|     | 12.9.1 General Characteristics                              |     |

|     | 12.9.2 Output Driving Current                               |     |

|     | 12.10 CONTROL PIN CHARACTERISTICS                           |     |

|     | 12.10.1Asynchronous RESET Pin                               | 136 |

|     | 12.10.2ICĆSEL/VPP Pin                                       |     |

|     | 12.11 TIMER PERIPHERAL CHARACTERISTICS                      | 139 |

|     | 12.11.116-Bit Timer                                         |     |

|     | 12.12 COMMUNICATION INTERFACE CHARACTERISTICS               |     |

|     | 12.12.1SPI - Serial Peripheral Interface                    |     |

|     | 12.13 10-BIT ADC CHARACTERISTICS                            |     |

|     | 12.13.1Analog Power Supply and Reference Pins               |     |

|     | 12.13.2General PCB Design Guidelines                        |     |

| . ^ | 12.13.3ADC Accuracy                                         |     |

| ıs  | 13.1 PACKAGE MECHANICAL DATA                                |     |

|     |                                                             |     |

|     |                                                             |     |

|     | 13.3 SOLDERING INFORMATION                                  |     |

| 14  | ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION       |     |

|     | 14.1 FLASH OPTION BYTES                                     |     |

|     | 14.2 FLASH DEVICE ORDERING INFORMATION                      |     |

|     | 14.3 SILICON IDENTIFICATION                                 |     |

|     | 14.4 DEVELOPMENT TOOLS                                      |     |

|     | 14.4.1 Socket and Emulator Adapter Information              |     |

|     | 14.5 ST7 APPLICATION NOTES                                  | 157 |

| 15  | KNOWN LIMITATIONS                                           |     |

|     | 15.1 ALL DEVICES                                            | 159 |

|     | 15.1.1 External RC option                                   |     |

|     | 15.1.2 CSS Function                                         |     |

|     | 15.1.3 Safe Connection of OSC1/OSC2 Pins                    |     |

|     | 15.1.4 Unexpected Reset Fetch                               |     |

|     | 15.1.5 Clearing active interrupts outside interrupt routine |     |

|     | 13.1.0 Lateniai intenuptiviisseu                            | 109 |

#### **5 CENTRAL PROCESSING UNIT**

#### 5.1 INTRODUCTION

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

#### **5.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

#### **5.3 CPU REGISTERS**

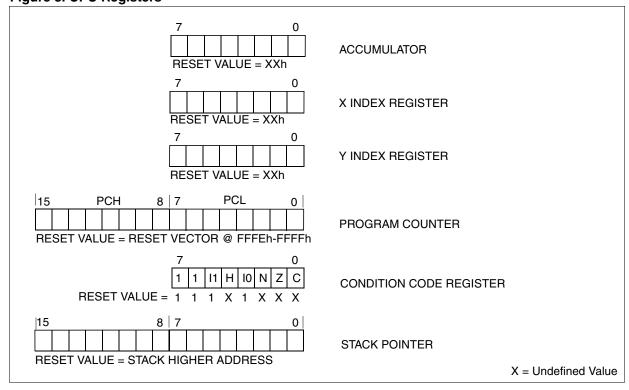

The 6 CPU registers shown in Figure 8 are not present in the memory mapping and are accessed by specific instructions.

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

#### **Program Counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

Figure 8. CPU Registers

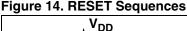

#### **RESET SEQUENCE MANAGER** (Cont'd)

The RESET pin is an asynchronous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in the electrical characteristics section.

#### 6.3.3 External Power-On RESET

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until V<sub>DD</sub> is over the minimum level specified for the selected f<sub>OSC</sub> frequency.

A proper reset signal for a slow rising V<sub>DD</sub> supply can generally be provided by an external RC network connected to the RESET pin.

#### 6.3.4 Internal Low Voltage Detector (LVD) RESET

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

The device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or V<sub>DD</sub><V<sub>IT</sub> (falling edge) as shown in Figure 14.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{q(VDD)}$  to avoid parasitic resets.

#### 6.3.5 Internal Watchdog RESET

The RESET sequence generated by a internal Watchdog counter overflow is shown in Figure 14.

Starting from the Watchdog counter underflow, the device RESET pin acts as an output that is pulled low during at least tw(RSTL)out.

#### **INTERRUPTS** (Cont'd)

#### **Servicing Pending Interrupts**

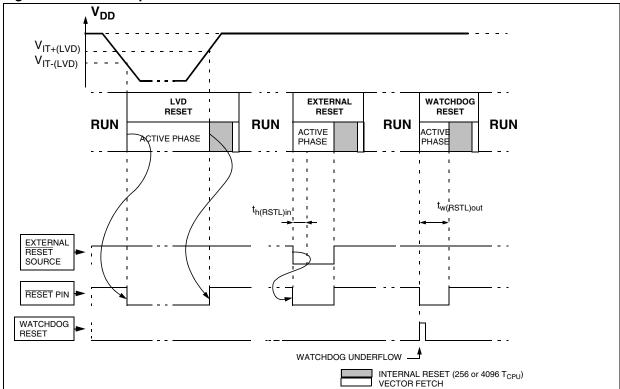

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 18 describes this decision process.

Figure 18. Priority Decision Process

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one.

**Note 1**: The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

**Note 2**: RESET and TRAP can be considered as having the highest software priority in the decision process.

#### **Different Interrupt Vector Sources**

Two interrupt source types are managed by the ST7 interrupt controller: the non-maskable type (RESET,TRAP) and the maskable type (external or from internal peripherals).

#### **Non-Maskable Sources**

These sources are processed regardless of the state of the I1 and I0 bits of the CC register (see Figure 17). After stacking the PC, X, A and CC registers (except for RESET), the corresponding

vector is loaded in the PC register and the I1 and I0 bits of the CC are set to disable interrupts (level 3). These sources allow the processor to exit HALT mode.

■ TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in Figure 17.

#### RESET

The RESET source has the highest priority in the ST7. This means that the first current routine has the highest software priority (level 3) and the highest hardware priority.

See the RESET chapter for more details.

#### **Maskable Sources**

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two conditions is false, the interrupt is latched and thus remains pending.

#### ■ External Interrupts

External interrupts allow the processor to exit from HALT low power mode. External interrupt sensitivity is software selectable through the External Interrupt Control register (EICR).

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically ORed.

#### Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to exit from HALT mode except those mentioned in the "Interrupt Mapping" table. A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register. The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being serviced) will therefore be lost if the clear sequence is executed.

# I/O PORTS (Cont'd)

Table 13. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2   | 1 | 0   |

|-------------------|--------------------------|-----|---|---|---|---|-----|---|-----|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0   | 0 | 0   |

| 0000h             | PADR                     |     |   |   |   |   |     |   |     |

| 0001h             | PADDR                    | MSB |   |   |   |   |     |   | LSB |

| 0002h             | PAOR                     |     |   |   |   |   |     |   |     |

| 0003h             | PBDR                     |     |   |   |   |   |     |   |     |

| 0004h             | PBDDR                    | MSB |   |   |   |   |     |   | LSB |

| 0005h             | PBOR                     |     |   |   |   |   |     |   |     |

| 0006h             | PCDR                     | MSB |   |   |   |   |     |   |     |

| 0007h             | PCDDR                    |     |   |   |   |   | LSB |   |     |

| 0008h             | PCOR                     |     |   |   |   |   |     |   |     |

| 0009h             | PDDR                     |     |   |   |   |   |     |   |     |

| 000Ah             | PDDDR                    | MSB |   |   |   |   |     |   | LSB |

| 000Bh             | PDOR                     |     |   |   |   |   |     |   |     |

| 000Ch             | PEDR                     |     |   |   |   |   |     |   |     |

| 000Dh             | PEDDR                    | MSB |   |   |   |   |     |   | LSB |

| 000Eh             | PEOR                     |     |   |   |   |   |     |   |     |

| 000Fh             | PFDR                     |     | _ |   | _ |   |     | _ |     |

| 0010h             | PFDDR                    | MSB |   |   |   |   |     |   | LSB |

| 0011h             | PFOR                     |     |   |   |   |   |     |   |     |

#### WATCHDOG TIMER (Cont'd)

## Figure 33. Exact Timeout Duration (t<sub>min</sub> and t<sub>max</sub>)

#### WHERE:

$t_{min0} = (LSB + 128) \times 64 \times t_{OSC2}$

$t_{max0} = 16384 \text{ x } t_{OSC2}$

$t_{OSC2} = 125$ ns if  $f_{OSC2} = 8$  MHz

CNT = Value of T[5:0] bits in the WDGCR register (6 bits)

MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 Bit<br>(MCCSR Reg.) | TB0 Bit<br>(MCCSR Reg.) | Selected MCCSR<br>Timebase | MSB | LSB |

|-------------------------|-------------------------|----------------------------|-----|-----|

| 0                       | 0                       | 2ms                        | 4   | 59  |

| 0                       | 1                       | 4ms                        | 8   | 53  |

| 1                       | 0                       | 10ms                       | 20  | 35  |

| 1                       | 1                       | 25ms                       | 49  | 54  |

# To calculate the minimum Watchdog Timeout (tmin):

$$\begin{aligned} \textbf{IF CNT} < & \left[ \frac{\text{MSB}}{4} \right] & \textbf{THEN} & t_{min} = t_{min0} + 16384 \times \text{CNT} \times t_{osc2} \\ & \textbf{ELSE} & t_{min} = t_{min0} + \left\lceil 16384 \times \left( \text{CNT} - \left\lceil \frac{4\text{CNT}}{\text{MSB}} \right\rceil \right) + (192 + \text{LSB}) \times 64 \times \left\lceil \frac{4\text{CNT}}{\text{MSB}} \right\rceil \right\rceil \times t_{osc2} \end{aligned}$$

# To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

$$\begin{aligned} \textbf{IF} \ \text{CNT} \leq & \left[ \frac{\text{MSB}}{4} \right] & \textbf{THEN} \quad t_{\text{max}} = t_{\text{max}0} + 16384 \times \text{CNT} \times t_{\text{osc2}} \\ & \textbf{ELSE} \quad t_{\text{max}} = t_{\text{max}0} + \left\lceil 16384 \times \left( \text{CNT} - \left\lceil \frac{4\text{CNT}}{\text{MSB}} \right\rceil \right) + (192 + \text{LSB}) \times 64 \times \left\lceil \frac{4\text{CNT}}{\text{MSB}} \right\rceil \right\rceil \times t_{\text{osc2}} \end{aligned}$$

Note: In the above formulae, division results must be rounded down to the next integer value.

#### **Example:**

With 2ms timeout selected in MCCSR register

| Value of T[5:0] Bits in WDGCR Register (Hex.) | Min. Watchdog<br>Timeout (ms)<br>t <sub>min</sub> | Max. Watchdog<br>Timeout (ms)<br>t <sub>max</sub> |  |

|-----------------------------------------------|---------------------------------------------------|---------------------------------------------------|--|

| 00                                            | 1.496                                             | 2.048                                             |  |

| 3F                                            | 128                                               | 128.552                                           |  |

#### MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

#### 10.2.5 Low Power Modes

| Mode            | Description                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.  MCC/RTC interrupt cause the device to exit from WAIT mode.                                                   |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is set), the registers are frozen.  MCC/RTC interrupt cause the device to exit from ACTIVE-HALT mode.    |

| HALT            | MCC/RTC counter and registers are frozen. MCC/RTC operation resumes when the MCU is woken up by an interrupt with "exit from HALT" capability. |

#### 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

#### Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

# 10.2.7 Register Description MCC CONTROL/STATUS REGISTER (MCCSR)

Read/Write

Reset Value: 0000 0000 (00h)

7 0 MCO CP1 CP0 SMS TB1 TB0 OIE OIF

Bit 7 = **MCO** Main clock out selection

This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.

- 0: MCO alternate function disabled (I/O pin free for general-purpose I/O)

- MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

**Note**: To reduce power consumption, the MCO function is not active in ACTIVE-HALT mode.

Bit 6:5 = **CP[1:0]** *CPU clock prescaler*

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC2</sub> / 2         | 0   | 0   |

| f <sub>OSC2</sub> / 4         | 0   | 1   |

| f <sub>OSC2</sub> / 8         | 1   | 0   |

| f <sub>OSC2</sub> / 16        | 1   | 1   |

Bit 4 = **SMS** Slow mode select

This bit is set and cleared by software.

0: Normal mode. f<sub>CPU</sub> = f<sub>OSC2</sub>

1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0

See Section 8.2 SLOW MODE and Section 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) for more details.

## Bit 3:2 = **TB[1:0]** Time base control

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                    | TB1                     | ТВ0 |     |  |

|-----------|-------------------------|-------------------------|-----|-----|--|

| Prescaler | f <sub>OSC2</sub> =4MHz | f <sub>OSC2</sub> =8MHz | 161 | 150 |  |

| 16000     | 4ms                     | 2ms                     | 0   | 0   |  |

| 32000     | 8ms                     | 4ms                     | 0   | 1   |  |

| 80000     | 20ms                    | 10ms                    | 1   | 0   |  |

| 200000    | 50ms                    | 25ms                    | 1   | 1   |  |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

Bit 1 = **OIE** Oscillator interrupt enable

This bit set and cleared by software.

- 0: Oscillator interrupt disabled

- 1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode.

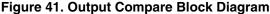

#### 10.3.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are 2 output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC/E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC/R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### Procedure:

To use the output compare function, select the following in the CR2 register:

- Set the OCiE bit if an output is needed then the OCMPi pin is dedicated to the output compare i signal.

- Select the timer clock (CC[1:0]) (see Table 16 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVLi bit to applied to the OCMPi pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCRi register and CR register:

OCFi bit is set.

- The OCMPi pin takes OLVLi bit value (OCMPi pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OCiR register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC} iR = \frac{\Delta t * f_{CPU}}{PRESC}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 de-

pending on CC[1:0] bits, see Table 16

Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}_{iR} = \Delta t * f_{EXT}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (i.e. clearing the OCF *i* bit) is done by:

- 1. Reading the SR register while the OCFi bit is

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OCiHR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCFi bit, which may be already set).

- Write to the OCiLR register (enables the output compare function and clears the OCFi bit).

#### Notes:

- After a processor write cycle to the OCiHR register, the output compare function is inhibited until the OCiLR register is also written.

- 2. If the OCiE bit is not set, the OCMPi pin is a general I/O port and the OLVLi bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- When the timer clock is f<sub>CPU</sub>/2, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 42 on page 67). This behaviour is the same in OPM or PWM mode.

- When the timer clock is f<sub>CPU</sub>/4, f<sub>CPU</sub>/8 or in external clock mode, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value plus 1 (see Figure 43 on page 67).

- 4. The output compare functions can be used both for generating external events on the OCMP*i* pins even if the input capture mode is also used.

- 5. The value in the 16-bit OCiR register and the OLVi bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

In Flash devices, the TAOC2HR, TAOC2LR registers are "write only" in Timer A. The corresponding event cannot be generated (OCF2 is forced by hardware to 0).

#### **Forced Compare Output capability**

When the FOLVi bit is set by software, the OLVi bit is copied to the OCMPi pin. The OLVi bit has to be toggled in order to toggle the OCMPi pin when it is enabled (OCiE bit=1). The OCFi bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

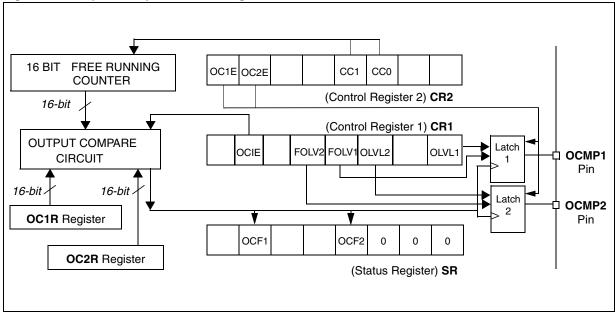

#### 10.3.3.5 One Pulse Mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The one pulse mode uses the Input Capture1 function and the Output Compare1 function.

#### **Procedure:**

To use one pulse mode:

- Load the OC1R register with the value corresponding to the length of the pulse (see the formula in the opposite column).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit.

- Select the timer clock CC[1:0] (see Table 16 Clock Control Bits).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the Input Capture interrupt request (i.e. clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the ICiLR register.

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OCiR Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

= Pulse period (in seconds)

$f_{CPU} = CPU$  clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits, see Table 16 Clock Control Bits)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{FXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin, (See Figure 44).

#### Notes:

- 1. The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3. If OLVL1=OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4. The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5. When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

- In Flash devices, Timer A OCF2 bit is forced by hardware to 0.

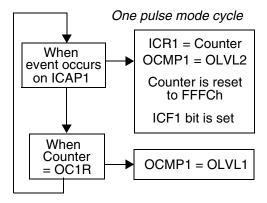

#### 10.3.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### **Procedure**

To use pulse width modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1=0 and OLVL2=1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 16 Clock Control Bits).

If OLVL1=1 and OLVL2=0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1=OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OCiR register value required for a specific timing application can be calculated using the following formula:

$$OCiR Value = \frac{t * f_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 16)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{FXT} - 5$$

Where:

= Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz) The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 45)

#### Notes:

- After a write instruction to the OC/HR register, the output compare function is inhibited until the OC/LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- In Flash devices, the TAOC2HR, TAOC2LR registers in Timer A are "write only". A read operation returns an undefined value.

- 7. In Flash devices, the ICAP2 registers (TAIC2HR, TAIC2LR) are not available in Timer A. The ICF2 bit is forced by hardware to 0.

#### 10.3.7 Register Description

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

## **CONTROL REGISTER 1 (CR1)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       |       |  |

|------|------|------|-------|-------|-------|-------|-------|--|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |  |

Bit 7 = ICIE Input Capture Interrupt Enable.

0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable*. 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.*

0: Interrupt is inhibited.

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

Bit 4 = **FOLV2** Forced Output Compare 2.

This bit is set and cleared by software.

0: No effect on the OCMP2 pin.

1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

This bit is set and cleared by software.

0: No effect on the OCMP1 pin.

1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

Bit 2 = **OLVL2** Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

Bit 1 = **IEDG1** Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

Bit 0 = **OLVL1** Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

#### **CONTROL/STATUS REGISTER (CSR)**

Read Only (except bit 2 R/W)

Reset Value: xxxx x0xx (xxh)

| 7    |      |     |      |      |      |   |   |  |

|------|------|-----|------|------|------|---|---|--|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | TIMD | 0 | 0 |  |

#### Bit 7 = ICF1 Input Capture Flag 1.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP1 pin or the counter has reached the OC2R value in PWM mode. To clear this bit, first read the SR register, then read or write the low byte of the IC1R (IC1LR) register.

#### Bit 6 = **OCF1** Output Compare Flag 1.

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the low byte of the OC1R (OC1LR) register.

#### Bit 5 = **TOF** Timer Overflow Flag.

0: No timer overflow (reset value).

1: The free running counter rolled over from FFFFh to 0000h. To clear this bit, first read the SR register, then read or write the low byte of the CR (CLR) register.

**Note:** Reading or writing the ACLR register does not clear TOF.

Bit 4 = ICF2 Input Capture Flag 2.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the low byte of the IC2R (IC2LR) register.

**Note:** In Flash devices, this bit is not available for Timer A and is forced by hardware to 0.

#### Bit 3 = **OCF2** Output Compare Flag 2.

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC2R register. To clear this bit, first read the SR register, then read or write the low byte of the OC2R (OC2LR) register.

**Note:** In Flash devices, this bit is not available for Timer A and is forced by hardware to 0.

#### Bit 2 = **TIMD** Timer disable.

This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.

0: Timer enabled

1: Timer prescaler, counter and outputs disabled

Bits 1:0 = Reserved, must be kept cleared.

#### 10.5 SERIAL COMMUNICATIONS INTERFACE (SCI)

#### 10.5.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 10.5.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

#### 10.5.3 General Description

The interface is externally connected to another device by two pins (see Figure 2.):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input.

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

47/

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) DATA REGISTER (SCIDR)

Read/Write

Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 1.).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 1.).

#### **BAUD RATE REGISTER (SCIBRR)**

Read/Write

Reset Value: 0000 0000 (00h)

7 0 | SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

Bits 7:6 = **SCP[1:0]** First SCI Prescaler These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| 1                    | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | 1    | 0    |

| 13                   | 1    | 1    |

Bits 5:3 = **SCT[2:0]** *SCI Transmitter rate divisor* These 3 bits, in conjunction with the SCP1 & SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.*These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR Dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

# **SERIAL COMMUNICATION INTERFACE** (Cont'd)

Table 22. SCI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0050h             | SCISR             | TDRE | TC   | RDRF | IDLE | OR   | NF   | FE   | PE   |

| 005011            | Reset Value       | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0051h             | SCIDR             | MSB  |      |      |      |      |      |      | LSB  |

| 005111            | Reset Value       | Х    | х    | х    | Х    | х    | Х    | Х    | х    |

| 0052h             | SCIBRR            | SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

| 003211            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0053h             | SCICR1            | R8   | T8   | SCID | М    | WAKE | PCE  | PS   | PIE  |

| 005311            | Reset Value       | Х    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0054h             | SCICR2            | TIE  | TCIE | RIE  | ILIE | TE   | RE   | RWU  | SBK  |

| 005411            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0055h             | SCIERPR           | MSB  |      |      |      |      |      |      | LSB  |

| 005511            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0057h             | SCIPETPR          | MSB  |      |      |      |      |      |      | LSB  |

| 005711            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### **INSTRUCTION SET OVERVIEW (Cont'd)**

#### 11.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

### **Indirect Indexed (Short)**

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

Table 25. Instructions Supporting Direct, Indexed, Indirect and Indirect Indexed Addressing Modes

| Long and Short<br>Instructions | Function                                      |

|--------------------------------|-----------------------------------------------|

| LD                             | Load                                          |

| СР                             | Compare                                       |

| AND, OR, XOR                   | Logical Operations                            |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Substractions operations |

| ВСР                            | Bit Compare                                   |

| Short Instructions<br>Only | Function                     |

|----------------------------|------------------------------|

| CLR                        | Clear                        |

| INC, DEC                   | Increment/Decrement          |

| TNZ                        | Test Negative or Zero        |

| CPL, NEG                   | 1 or 2 Complement            |

| BSET, BRES                 | Bit Operations               |

| BTJT, BTJF                 | Bit Test and Jump Operations |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations  |

| SWAP                       | Swap Nibbles                 |

| CALL, JP                   | Call or Jump subroutine      |

#### 11.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### Relative (Direct)

The offset is following the opcode.

### Relative (Indirect)

The offset is defined in memory, which address follows the opcode.

#### 12.8 EMC CHARACTERISTICS

Susceptibility tests are performed on a sample basis during product characterization.

# 12.8.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 12.8.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It

should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015)

| Symbo             | Parameter                                                                                                                        | Conditions                                                                                                               | Level/<br>Class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | 8 or 16K Flash device, V <sub>DD</sub> =5V,<br>T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz conforms to IEC<br>1000-4-2 | 4B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4                           | 4A              |

#### 12.12 COMMUNICATION INTERFACE CHARACTERISTICS

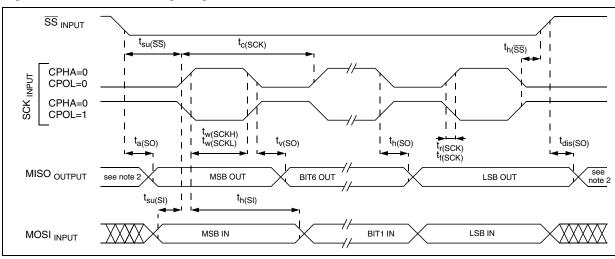

#### 12.12.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified. Data based on design simulation and/or characterisation results, not tested in production.

When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration. Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                    | Parameter                    | Conditions                    | Min                             | Max                      | Unit             |

|---------------------------|------------------------------|-------------------------------|---------------------------------|--------------------------|------------------|

| f <sub>SCK</sub>          | SPI clock frequency          | Master f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128<br>0.0625 | f <sub>CPU</sub> /4<br>2 | MHz              |

| 1/t <sub>c(SCK)</sub>     | SPI Clock frequency          | Slave f <sub>CPU</sub> =8MHz  | 0                               | f <sub>CPU</sub> /2<br>4 |                  |

| $t_{r(SCK)} \ t_{f(SCK)}$ | SPI clock rise and fall time |                               | see I/O p                       | oort pin de              | scription        |

| t <sub>su(SS)</sub>       | SS setup time                | Slave                         | 120                             |                          |                  |

| t <sub>h(SS)</sub>        | SS hold time                 | Slave                         | 120                             |                          | •                |

| t <sub>w(SCKH)</sub>      | SCK high and low time        | Master<br>Slave               | 100<br>90                       |                          |                  |

| t <sub>su(MI)</sub>       | Data input setup time        | Master<br>Slave               | 100<br>100                      |                          |                  |

| t <sub>h(MI)</sub>        | Data input hold time         | Master<br>Slave               | 100<br>100                      |                          | ns               |

| t <sub>a(SO)</sub>        | Data output access time      | Slave                         | 0                               | 120                      |                  |

| t <sub>dis(SO)</sub>      | Data output disable time     | Slave                         |                                 | 240                      | •                |

| t <sub>v(SO)</sub>        | Data output valid time       | Slave (after enable edge)     |                                 | 90                       | •                |

| t <sub>h(SO)</sub>        | Data output hold time        | Slave (alter eriable edge)    | 0                               |                          |                  |

| t <sub>v(MO)</sub>        | Data output valid time       | Master (before capture edge)  | 0.25                            |                          | +                |

| t <sub>h(MO)</sub>        | Data output hold time        | inaster (before capture edge) | 0.25                            |                          | t <sub>CPU</sub> |

Figure 80. SPI Slave Timing Diagram with CPHA=0 1)

#### Notes:

140/164

1. Measurement points are done at CMOS levels: 0.3xV<sub>DD</sub> and 0.7xV<sub>DD</sub>.

# **Table 30. ST7 Application Notes**

| IDENTIFICATION | DESCRIPTION                                                             |

|----------------|-------------------------------------------------------------------------|

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                      |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                       |

| AN 985         | EXECUTING CODE IN ST7 RAM                                               |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                             |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                  |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                   |

| AN 989         | GETTING STARTED WITH THE ST7 HIWARE C TOOLCHAIN                         |

| AN1039         | ST7 MATH UTILITY ROUTINES                                               |

| AN1064         | WRITING OPTIMIZED HIWARE C LANGUAGE FOR ST7                             |

| AN1106         | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                              |

| AN1446         | USING THE ST72521 EMULATOR TO DEBUG A ST72324 TARGET APPLICATION        |

| AN1478         | PORTING AN ST7 PANTA PROJECT TO CODEWARRIOR IDE                         |

| AN1575         | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS            |

| AN1576         | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS |

| AN1635         | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                               |

| AN1754         | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC               |

| AN1796         | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT     |

| SYSTEM OPTIMIZ | ATION                                                                   |

| AN1711         | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                     |