Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324j4t6-tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 10.4.7 Interrupts                                           |     |

|-------------------------------------------------------------|-----|

| 10.4.8 Register Description                                 |     |

| 10.5.1 Introduction                                         |     |

| 10.5.2 Main Features                                        |     |

| 10.5.3 General Description                                  |     |

| 10.5.4 Functional Description                               |     |

| 10.5.6 Interrupts                                           |     |

| 10.5.7 Register Description                                 |     |

| 10.6 10-BIT A/D CONVERTER (ADC)                             |     |

| 10.6.1 Introduction                                         |     |

| 10.6.3 Functional Description                               |     |

| 10.6.4 Low Power Modes                                      |     |

| 10.6.5 Interrupts                                           |     |

| 10.6.6 Register Description                                 |     |

| 11.1 CPU ADDRESSING MODES                                   |     |

| 11.1.1 Inherent                                             |     |

| 11.1.2 Immediate                                            |     |

| 11.1.3 Direct                                               |     |

| 11.1.4 Indexed (No Offset, Short, Long)                     |     |

| 11.1.5 Indirect (Short, Long)                               |     |

| 11.1.7 Relative mode (Direct, Indirect)                     |     |

| 11.2 INSTRUCTION GROUPS                                     |     |

| 12 ELECTRICAL CHARACTERISTICS                               |     |

| 12.1 PARAMETER CONDITIONS                                   |     |

| 12.1.1 Minimum and Maximum values                           |     |

| 12.1.3 Typical curves                                       |     |

| 12.1.4 Loading capacitor                                    |     |

| 12.1.5 Pin input voltage                                    |     |

| 12.2 ABSOLUTE MAXIMUM RATINGS                               |     |

| 12.2.1 Voltage Characteristics                              |     |

| 12.2.3 Thermal Characteristics                              |     |

| 12.3 OPERATING CONDITIONS                                   | 118 |

| 12.3.1 Operating Conditions                                 |     |

| 12.4 LVD/AVD CHARACTERISTICS                                |     |

| 12.4.1 Operating Conditions with Low Voltage Detector (LVD) |     |

| 12.5 SUPPLY CURRENT CHARACTERISTICS                         |     |

| 12.5.1 CURRENT CONSUMPTION                                  |     |

| 12.5.2 Supply and Clock Managers                            | 122 |

| 12.5.3 On-Chip Peripherals                                  | 123 |

57

# **1 INTRODUCTION**

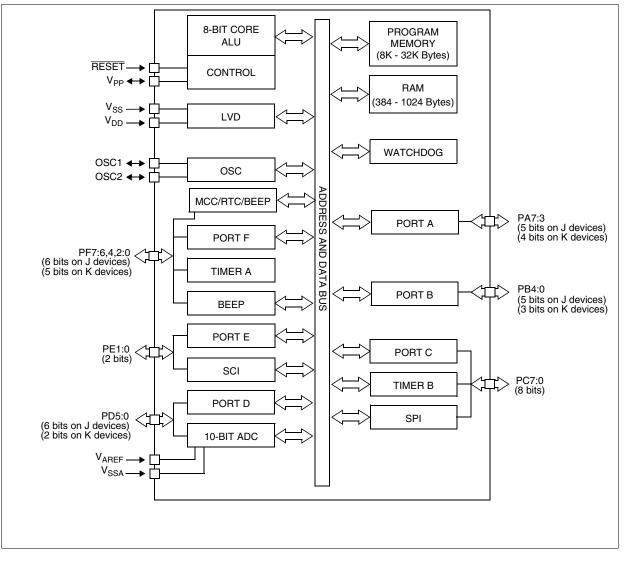

The ST72324 devices are members of the ST7 microcontroller family designed for the 5V operating range.

- The 32-pin devices are designed for mid-range applications

- The 42/44-pin devices target the same range of applications requiring more than 24 I/O ports.

For a description of the differences between ST72324 and ST72324B devices refer to Section 14.2 on page 152

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruc-

#### Figure 1. Device Block Diagram

57/

tion set and are available with FLASH program memory.

Under software control, all devices can be placed in WAIT, SLOW, ACTIVE-HALT or HALT mode, reducing power consumption when the application is in idle or stand-by state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

# **2 PIN DESCRIPTION**

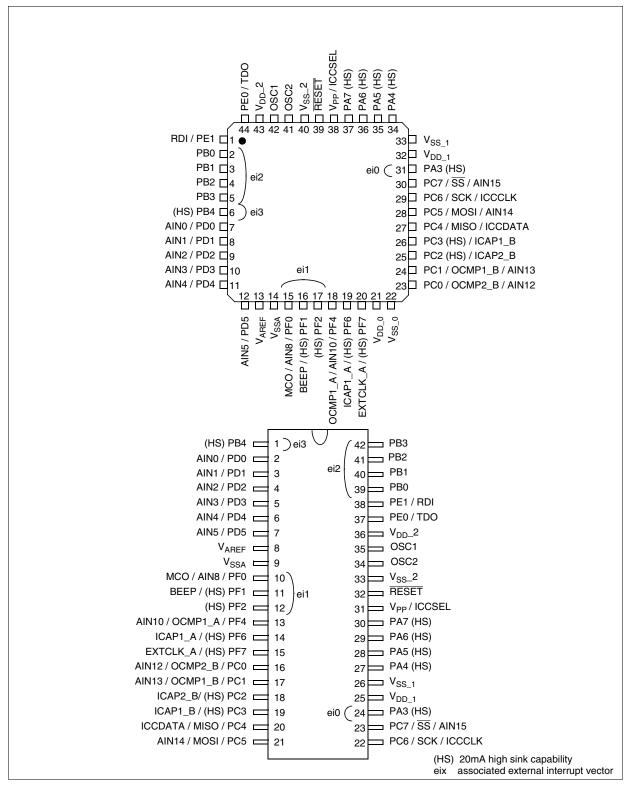

#### Figure 2. 42-Pin SDIP and 44-Pin TQFP Package Pinouts

Legend: x=undefined, R/W=read/write

#### Notes:

- 1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

- 2. The bits associated with unavailable pins must always keep their reset value.

- 3. The Timer A Input Capture 2 pin is not available (not bonded).

- In Flash devices: The TAIC2HR and TAIC2LR registers are not present. Bit 5 of the TACSR register (ICF2) is forced by hardware to 0. Consequently, the corresponding interrupt cannot be used.

- 4. The Timer A Output Compare 2 pin is not available (not bonded).

- The TAOC2HR and TAOC2LR Registers are write only, reading them will return undefined values. Bit 4 of the TACSR register (OCF2) is forced by hardware to 0. Consequently, the corresponding interrupt cannot be used.

**Caution:** The TAIC2HR and TAIC2LR registers and the ICF2 and OCF2 flags are not present in Flash devices but are present in the emulator. For compatibility with the emulator, it is recommended to perform a dummy access (read or write) to the TAIC2LR and TAOC2LR registers to clear the interrupt flags.

**47/**

# I/O PORTS (Cont'd)

# Table 13. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|--------------------------|-----|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h             | PADR                     |     |   |   |   |   |   |   |     |

| 0001h             | PADDR                    | MSB |   |   |   |   |   |   | LSB |

| 0002h             | PAOR                     |     |   |   |   |   |   |   |     |

| 0003h             | PBDR                     |     |   |   |   |   |   |   |     |

| 0004h             | PBDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0005h             | PBOR                     |     |   |   |   |   |   |   |     |

| 0006h             | PCDR                     |     |   |   |   |   |   |   |     |

| 0007h             | PCDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0008h             | PCOR                     |     |   |   |   |   |   |   |     |

| 0009h             | PDDR                     |     |   |   |   |   |   |   |     |

| 000Ah             | PDDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Bh             | PDOR                     |     |   |   |   |   |   |   |     |

| 000Ch             | PEDR                     |     |   |   |   |   |   |   |     |

| 000Dh             | PEDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Eh             | PEOR                     |     |   |   |   |   |   |   |     |

| 000Fh             | PFDR                     |     |   |   |   |   |   |   |     |

| 0010h             | PFDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0011h             | PFOR                     | Ī   |   |   |   |   |   |   |     |

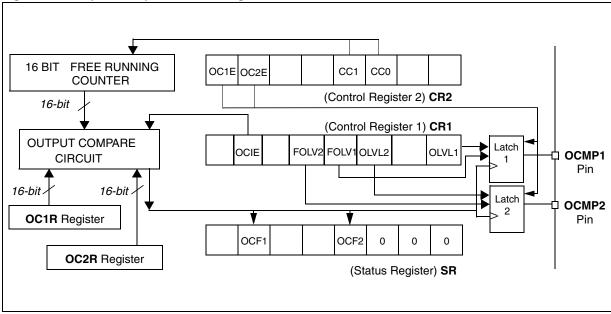

#### **10.3 16-BIT TIMER**

#### 10.3.1 Introduction

The timer consists of a 16-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU clock prescaler.

Some ST7 devices have two on-chip 16-bit timers. They are completely independent, and do not share any resources. They are synchronized after a MCU reset as long as the timer clock frequencies are not modified.

This description covers one or two 16-bit timers. In ST7 devices with two timers, register names are prefixed with TA (Timer A) or TB (Timer B).

#### 10.3.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4 or 8.

- Overflow status flag and maskable interrupt

- External clock input (must be at least 4 times slower than the CPU clock speed) with the choice of active edge

- 1 or 2 Output Compare functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- 1 or 2 Input Capture functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced Power Mode

- 5 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2, EXTCLK)\*

The Block Diagram is shown in Figure 35.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

#### **10.3.3 Functional Description**

#### 10.3.3.1 Counter

The main block of the Programmable Timer is a 16-bit free running upcounter and its associated 16-bit registers. The 16-bit registers are made up of two 8-bit registers called high & low.

Counter Register (CR):

- Counter High Register (CHR) is the most significant byte (MS Byte).

- Counter Low Register (CLR) is the least significant byte (LS Byte).

Alternate Counter Register (ACR)

- Alternate Counter High Register (ACHR) is the most significant byte (MS Byte).

- Alternate Counter Low Register (ACLR) is the least significant byte (LS Byte).

These two read-only 16-bit registers contain the same value but with the difference that reading the ACLR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR), (see note at the end of paragraph titled 16-bit read sequence).

Writing in the CLR register or ACLR register resets the free running counter to the FFFCh value.

Both counters have a reset value of FFFCh (this is the only value which is reloaded in the 16-bit timer). The reset value of both counters is also FFFCh in One Pulse mode and PWM mode.

The timer clock depends on the clock control bits of the CR2 register, as illustrated in Table 16 Clock Control Bits. The value in the counter register repeats every 131072, 262144 or 524288 CPU clock cycles depending on the CC[1:0] bits.

The timer frequency can be  $f_{CPU}/2$ ,  $f_{CPU}/4$ ,  $f_{CPU}/8$  or an external frequency.

**Caution:** In Flash devices, Timer A functionality has the following restrictions:

- TAOC2HR and TAOC2LR registers are write only

- Input Capture 2 is not implemented

- The corresponding interrupts cannot be used (ICF2, OCF2 forced by hardware to zero)

57

#### 10.3.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are 2 output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC/E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### **Procedure:**

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 16 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCRi register and CR register:

- OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \operatorname{OC}_{i} R = \frac{\Delta t * f_{CPU}}{\mathsf{PRESC}}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 16 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC} i \text{R} = \Delta t * f_{\text{EXT}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (i.e. clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

#### Notes:

- 1. After a processor write cycle to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. If the OC*i*E bit is not set, the OCMP*i* pin is a general I/O port and the OLVL*i* bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- When the timer clock is f<sub>CPU</sub>/2, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value (see Figure 42 on page 67). This behaviour is the same in OPM or PWM mode.

When the timer clock is f<sub>CPU</sub>/4, f<sub>CPU</sub>/8 or in

external clock mode, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value plus 1 (see Figure 43 on page 67).

- 4. The output compare functions can be used both for generating external events on the OCMP*i* pins even if the input capture mode is also used.

- 5. The value in the 16-bit OC*i*R register and the OLV*i* bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

6. In Flash devices, the TAOC2HR, TAOC2LR registers are "write only" in Timer A. The corresponding event cannot be generated (OCF2 is forced by hardware to 0).

#### Forced Compare Output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit=1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

#### Figure 41. Output Compare Block Diagram

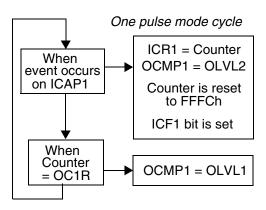

#### 10.3.3.5 One Pulse Mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The one pulse mode uses the Input Capture1 function and the Output Compare1 function.

#### Procedure:

To use one pulse mode:

- 1. Load the OC1R register with the value corresponding to the length of the pulse (see the formula in the opposite column).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit.

- Select the timer clock CC[1:0] (see Table 16 Clock Control Bits).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the Input Capture interrupt request (i.e. clearing the ICF*i* bit) is done in two steps:

1. Reading the SR register while the ICF*i* bit is set.

2. An access (read or write) to the ICiLR register.

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OCiR Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits, see Table 16 Clock Control Bits)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin, (See Figure 44).

#### Notes:

- 1. The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2. When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3. If OLVL1=OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4. The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5. When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

- 6. In Flash devices, Timer A OCF2 bit is forced by hardware to 0.

#### 10.3.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                      |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                           |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

#### 10.3.5 Interrupts

57

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    | ICF1          | ICIE                     | Yes                  | No                   |

| Input Capture 2 event                              | ICF2*         | ICIE                     | Yes                  | No                   |

| Output Compare 1 event (not available in PWM mode) | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) | OCF2*         | OUIE                     | Yes                  | No                   |

| Timer Overflow event                               | TOF           | TOIE                     | Yes                  | No                   |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

\* In Flash devices, the ICF2 and OCF2 bits are forced by hardware to 0 in Timer A, hence there is no interrupt event for these flags.

#### 10.3.6 Summary of Timer modes

| MODES                       | TIMER RESOURCES                 |                                    |                  |                         |  |  |  |  |

|-----------------------------|---------------------------------|------------------------------------|------------------|-------------------------|--|--|--|--|

| MODES                       | Input Capture 1 Input Capture 2 |                                    | Output Compare 1 | Output Compare 2        |  |  |  |  |

| Input Capture (1 and/or 2)  | Yes                             | Yes <sup>2)5)</sup>                | Yes              | Yes <sup>4)</sup>       |  |  |  |  |

| Output Compare (1 and/or 2) | Yes                             | Yes <sup>5)</sup>                  | Yes              | Yes <sup>4)</sup>       |  |  |  |  |

| One Pulse Mode              | No                              | Not<br>Recommended <sup>1)5)</sup> | No               | Partially <sup>2)</sup> |  |  |  |  |

| PWM Mode                    | No                              | Not<br>Recommended <sup>3)5)</sup> | No               | No                      |  |  |  |  |

1) See note 4 in Section 10.3.3.5 One Pulse Mode

- 2) See note 5 and 6 in Section 10.3.3.5 One Pulse Mode

- 3) See note 4 in Section 10.3.3.6 Pulse Width Modulation Mode

- 4) In Flash devices, the TAOC2HR, TAOC2LR registers are write only in Timer A. Output Compare 2 event cannot be generated, OCF2 is forced by hardware to 0.

- 5) In Flash devices, Input Capture 2 is not implemented in Timer A. ICF2 bit is forced by hardware to 0.

# **INPUT CAPTURE 1 HIGH REGISTER (IC1HR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |   |

|-----|--|--|--|-----|---|

| MSB |  |  |  | LSB | ĺ |

# **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

#### Read Only

**Reset Value: Undefined**

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

57/

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# SERIAL PERIPHERAL INTERFACE (Cont'd)

# 10.4.3.2 Slave Select Management

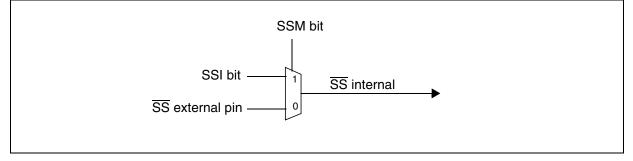

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see Figure 49)

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$ signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode:

5/

- SS internal must be held high continuously

#### In Slave Mode:

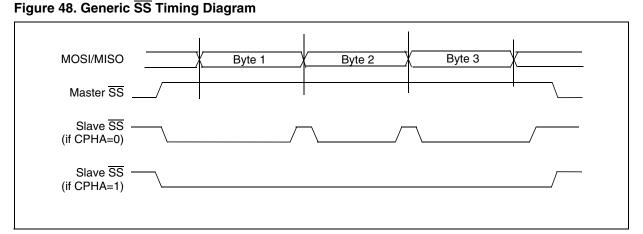

There are two cases depending on the data/clock timing relationship (see Figure 48):

- If CPHA=1 (data latched on 2nd clock edge):

- $-\overline{SS}$  internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or made free for standard I/O by managing the SS function by software (SSM= 1 and SSI=0 in the in the SPICSR register)

If CPHA=0 (data latched on 1st clock edge):

$-\overline{SS}$  internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see Section 10.4.5.3).

## Figure 49. Hardware/Software Slave Select Management

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.9 Clock Deviation Causes

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error (Local oscillator error of the transmitter or the transmitter is transmitting at a different baud rate).

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete SCI message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the SCI clock tolerance:

$\mathsf{D}_{\mathsf{TRA}} + \mathsf{D}_{\mathsf{QUANT}} + \mathsf{D}_{\mathsf{REC}} + \mathsf{D}_{\mathsf{TCL}} < 3.75\%$

#### 10.5.4.10 Noise Error Causes

See also description of Noise error in Section 0.1.4.3.

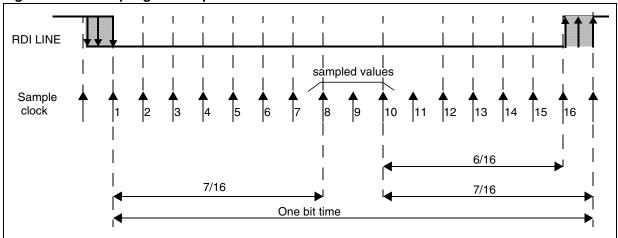

#### Start bit

The noise flag (NF) is set during start bit reception if one of the following conditions occurs:

- 1. A valid falling edge is not detected. A falling edge is considered to be valid if the 3 consecutive samples before the falling edge occurs are detected as '1' and, after the falling edge occurs, during the sampling of the 16 samples, if one of the samples numbered 3, 5 or 7 is detected as a "1".

- 2. During sampling of the 16 samples, if one of the samples numbered 8, 9 or 10 is detected as a "1".

Therefore, a valid Start Bit must satisfy both the above conditions to prevent the Noise Flag getting set.

#### **Data Bits**

The noise flag (NF) is set during normal data bit reception if the following condition occurs:

During the sampling of 16 samples, if all three samples numbered 8, 9 and 10 are not the same. The majority of the 8th, 9th and 10th samples is considered as the bit value.

Therefore, a valid Data Bit must have samples 8, 9 and 10 at the same value to prevent the Noise Flag getting set.

#### Figure 56. Bit Sampling in Reception Mode

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

#### Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

#### Bit 7 = **R8** Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = **T8** Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit  $4 = \mathbf{M}$  Word length. This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

#### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.

0: Parity error interrupt disabled

1: Parity error interrupt enabled.

57

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### **10.6.6 Register Description**

## **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   |       |      |   |     |     |     | 0   |

|-----|-------|------|---|-----|-----|-----|-----|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by hardware when software reads the ADCDRH register or writes to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = **SPEED** ADC clock selection This bit is set and cleared by software. 0:  $f_{ADC} = f_{CPU}/4$ 1:  $f_{ADC} = f_{CPU}/2$

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **Reserved.** Must be kept cleared.

#### Bit 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 1   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

\*The number of channels is device dependent. Refer to the device pinout description.

#### **DATA REGISTER (ADCDRH)**

Read Only Reset Value: 0000 0000 (00h)

7

|    | l. |    | l. | l. | r. | r. | r. |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

|    |    |    |    |    |    |    |    |

0

Bit 7:0 = D[9:2] MSB of Converted Analog Value

## DATA REGISTER (ADCDRL)

Read Only Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 = Reserved. Forced by hardware to 0.

Bit 1:0 = **D**[1:0] *LSB of Converted Analog Value*

# INSTRUCTION SET OVERVIEW (Cont'd)

57

| Mnemo | Description            | Function/Example    | Dst     | Src     | 11 | н | 10 | Ν | Ζ | С |

|-------|------------------------|---------------------|---------|---------|----|---|----|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |    |   |    |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |    |   |    | Ν | Ζ |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A |    | 0 |    |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |    |   |    | Ν | Z | С |

| NOP   | No Operation           |                     |         |         |    |   |    |   |   |   |

| OR    | OR operation           | A=A+M               | А       | М       |    |   |    | Ν | Z |   |

| POP   | Don from the Stool     | pop reg             | reg     | М       |    |   |    |   |   |   |

| POP   | Pop from the Stack     | pop CC              | CC      | М       | 11 | н | 10 | Ν | Ζ | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |    |   |    |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |    |   |    |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |    |   |    |   |   |   |

| RIM   | Enable Interrupts      | 11:0 = 10 (level 0) |         |         | 1  |   | 0  |   |   |   |

| RLC   | Rotate left true C     | C <= A <= C         | reg, M  |         |    |   |    | Ν | Ζ | С |

| RRC   | Rotate right true C    | C => A => C         | reg, M  |         |    |   |    | Ν | Ζ | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |    |   |    |   |   |   |

| SBC   | Substract with Carry   | A = A - M - C       | А       | М       |    |   |    | Ν | Ζ | С |

| SCF   | Set carry flag         | C = 1               |         |         |    |   |    |   |   | 1 |

| SIM   | Disable Interrupts     | l1:0 = 11 (level 3) |         |         | 1  |   | 1  |   |   |   |

| SLA   | Shift left Arithmetic  | C <= A <= 0         | reg, M  |         |    |   |    | Ν | Ζ | С |

| SLL   | Shift left Logic       | C <= A <= 0         | reg, M  |         |    |   |    | Ν | Ζ | С |

| SRL   | Shift right Logic      | 0 => A => C         | reg, M  |         |    |   |    | 0 | Z | С |

| SRA   | Shift right Arithmetic | A7 => A => C        | reg, M  |         |    |   |    | Ν | Ζ | С |

| SUB   | Substraction           | A = A - M           | А       | М       |    |   |    | Ν | Z | С |

| SWAP  | SWAP nibbles           | A7-A4 <=> A3-A0     | reg, M  |         |    |   |    | Ν | Ζ |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |    |   |    | Ν | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         | 1  |   | 1  |   |   |   |

| WFI   | Wait for Interrupt     |                     |         |         | 1  |   | 0  |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | А       | М       |    |   | l  | Ν | Ζ |   |

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

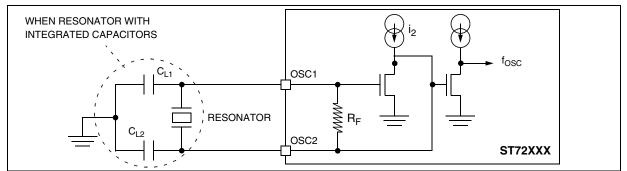

## 12.6.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol           | Parameter                                                                    | Con                  | Conditions      |    | Max | Unit       |

|------------------|------------------------------------------------------------------------------|----------------------|-----------------|----|-----|------------|

|                  |                                                                              | LP: Low power        | r oscillator    | 1  | 2   |            |

| f <sub>OSC</sub> | Oppillator Fragmanau 1)                                                      | MP: Medium p         | ower oscillator | >2 | 4   | N/I I      |

|                  | Oscillator Frequency <sup>1)</sup>                                           | MS: Medium s         | >4              | 8  | MHz |            |

|                  |                                                                              | HS: High spee        | >8              | 16 |     |            |

| R <sub>F</sub>   | Feedback resistor <sup>2)</sup>                                              |                      |                 | 20 | 40  | kΩ         |

|                  |                                                                              | R <sub>S</sub> =200Ω | LP oscillator   | 22 | 56  |            |

| C <sub>L1</sub>  | Recommended load capacitance ver-<br>sus equivalent serial resistance of the | R <sub>S</sub> =200Ω | MP oscillator   | 22 | 46  | ~ <b>F</b> |

| C <sub>L2</sub>  |                                                                              | R <sub>S</sub> =200Ω | MS oscillator   | 18 | 33  | pF         |

|                  | crystal or ceramic resonator (R <sub>S</sub> )                               | R <sub>S</sub> =100Ω | HS oscillator   | 15 | 33  |            |

| Symbol         | Parameter            | Conditions                       |               | Тур | Max | Unit |

|----------------|----------------------|----------------------------------|---------------|-----|-----|------|

|                |                      | V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator | 80  | 150 |      |

|                | OSC2 driving current |                                  | MP oscillator | 160 | 250 |      |

| 1 <sub>2</sub> |                      |                                  | MS oscillator | 310 | 460 | μΑ   |

|                |                      |                                  | HS oscillator | 610 | 910 |      |

# Figure 66. Typical Application with a Crystal or Ceramic Resonator

Notes:

5/

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# **12.7 MEMORY CHARACTERISTICS**

#### 12.7.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 12.7.2 FLASH Memory

| DUAL VOL                                | TAGE HDFLASH MEMORY                           |                             |                   |     |                   |        |

|-----------------------------------------|-----------------------------------------------|-----------------------------|-------------------|-----|-------------------|--------|

| Symbol                                  | Parameter                                     | Conditions                  | Min <sup>2)</sup> | Тур | Max <sup>2)</sup> | Unit   |

| f                                       | Operating frequency                           | Read mode                   | 0                 |     | 8                 | MHz    |

| f <sub>CPU</sub>                        | Operating frequency                           | Write / Erase mode          | 1                 |     | 8                 |        |

| V <sub>PP</sub>                         | Programming voltage <sup>3)</sup>             | $4.5V \le V_{DD} \le 5.5V$  | 11.4              |     | 12.6              | V      |

| I <sub>DD</sub>                         | Supply current <sup>4)</sup>                  | Write / Erase               |                   | 0   |                   | mA     |

| 1                                       | V <sub>PP</sub> current <sup>4)</sup>         | Read (V <sub>PP</sub> =12V) |                   |     | 200               | μA     |

| I <sub>PP</sub>                         |                                               | Write / Erase               |                   |     | 30                | mA     |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time   |                             |                   | 10  |                   | μs     |

| t <sub>RET</sub>                        | Data retention                                | T <sub>A</sub> =55°C        | 20                |     |                   | years  |

| N <sub>RW</sub>                         | Write erase cycles                            | T <sub>A</sub> =25°C        | 100               |     |                   | cycles |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing tempera-<br>ture range |                             | -40               | 25  | 85                | °C     |

#### Notes:

47/

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Not tested in production.

2. Data based on characterization results, not tested in production.

3. V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons.

4. Data based on simulation results, not tested in production.

# DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

#### **14.2 FLASH DEVICE ORDERING INFORMATION**

With the objective of continuous improvement, ST is developing new ST72F324B devices and is transferring the production to higher capacity fabs. Refer to the following tables for guidance on ordering.

#### **Standard and Industrial Versions**

- For new designs the ST72F324B devices from to the separate ST72324B datasheet.

- For for running production orders select the devices from Table 26

#### KNOWN LIMITATIONS (Cont'd)

To avoid this, a semaphore is set to '1' before checking the level change. The semaphore is changed to level '0' inside the interrupt routine. When a level change is detected, the semaphore status is checked and if it is '1' this means that the last interrupt has been missed. In this case, the interrupt routine is invoked with the call instruction.

There is another possible case, that is, if writing to PxOR or PxDDR is done with global interrupts disabled (interrupt mask bit set). In this case, the semaphore is changed to '1' when the level change is detected. Detecting a missed interrupt is done after the global interrupts are enabled (interrupt mask bit reset) and by checking the status of the semaphore. If it is '1' this means that the last interrupt was missed and the interrupt routine is invoked with the call instruction.

To implement the workaround, the following software sequence is to be followed for writing into the PxOR/PxDDR registers. The example is for Port PF1 with falling edge interrupt sensitivity. The software sequence is given for both cases (global interrupt disabled/enabled).

**Case 1:** Writing to PxOR or PxDDR with Global Interrupts Enabled:

LD A,#01

LD sema,A ; set the semaphore to '1'

LD A, PFDR

AND A,#02

LD X,A ; store the level before writing to PxOR/PxDDR

LD A,#\$90

LD PFDDR,A ; Write to PFDDR

LD A,#\$ff

LD PFOR,A ; Write to PFOR

LD A, PFDR

AND A,#02

LD Y,A ; store the level after writing to PxOR/PxDDR

LD A,X ; check for falling edge

cp A,#02

jrne OUT

TNZ Y

irne OUT

LD A, sema ; check the semaphore status if edge is detected

RIM

OUT:

RIM

47/

CP A,#01

irne OUT call call\_routine; call the interrupt routine OUT:LD A,#00 LD sema,A .call routine ; entry to call routine PUSH A PUSH X PUSH CC .ext1 rt ; entry to interrupt routine LD A,#00 LD sema,A IRET Case 2: Writing to PxOR or PxDDR with Global Interrupts Disabled: SIM ; set the interrupt mask LD A, PFDR AND A,#\$02 LD X,A ; store the level before writing to PxOR/PxDDR LD A,#\$90 LD PFDDR,A ; Write into PFDDR LD A,#\$ff LD PFOR,A ; Write to PFOR LD A.PFDR AND A,#\$02 ; store the level after writing to LD Y.A PxOR/PxDDR LD A,X ; check for falling edge cp A,#\$02 irne OUT TNZ Y irne OUT LD A,#\$01 LD sema.A ; set the semaphore to '1' if edge is detected RIM ; reset the interrupt mask LD A,sema ; check the semaphore status CP A,#\$01 irne OUT call call routine; call the interrupt routine