Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LQFP                                                                 |

| Supplier Device Package    | · ·                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324j4tc-tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 2 PIN D | ODUCTION                                                                               | 8   |

|---------|----------------------------------------------------------------------------------------|-----|

|         | ISTER & MEMORY MAP                                                                     |     |

| 4 FLAS  | SH PROGRAM MEMORY                                                                      |     |

| 4.1     |                                                                                        | 17  |

| 4.2     | MAIN FEATURES                                                                          | 17  |

| 4.3     | STRUCTURE                                                                              | 17  |

|         | 4.3.1 Read-out Protection                                                              | 17  |

| 4.4     | ICC INTERFACE                                                                          | -   |

| 4.5     | ICP (IN-CIRCUIT PROGRAMMING)                                                           | 19  |

| 4.6     | IAP (IN-APPLICATION PROGRAMMING)                                                       | 19  |

| 4.7     | RELATED DOCUMENTATION                                                                  | 19  |

|         | 4.7.1 Register Description                                                             | 19  |

| 5 CEN   |                                                                                        |     |

| 5.1     |                                                                                        | 20  |

| 5.2     | MAIN FEATURES                                                                          | 20  |

| 5.3     | CPU REGISTERS                                                                          | 20  |

| 6 SUPF  | PLY, RESET AND CLOCK MANAGEMENT                                                        |     |

| 6.1     | PHASE LOCKED LOOP                                                                      |     |

| 6.2     | MULTI-OSCILLATOR (MO)                                                                  | 24  |

| 6.3     | RESET SEQUENCE MANAGER (RSM)                                                           |     |

|         | 6.3.1 Introduction                                                                     |     |

|         | 6.3.2 Asynchronous External RESET pin                                                  |     |

|         | 6.3.3 External Power-On RESET                                                          | 26  |

|         | 6.3.4 Internal Low Voltage Detector (LVD) RESET                                        |     |

| ~ /     | 6.3.5 Internal Watchdog RESET                                                          |     |

| 6.4     | SYSTEM INTEGRITY MANAGEMENT (SI)                                                       |     |

|         | 6.4.1 Low Voltage Detector (LVD)                                                       |     |

|         | <ul><li>6.4.2 Auxiliary Voltage Detector (AVD)</li><li>6.4.3 Low Power Modes</li></ul> |     |

|         | 6.4.3 Low Power Modes   6.4.4 Register Description                                     |     |

| 7 INTE  | RRUPTS                                                                                 |     |

| 7.1     | INTRODUCTION                                                                           |     |

| 7.2     | MASKING AND PROCESSING FLOW                                                            |     |

| 7.3     | INTERRUPTS AND LOW POWER MODES                                                         |     |

| 7.4     | CONCURRENT & NESTED MANAGEMENT                                                         |     |

| 7.5     |                                                                                        |     |

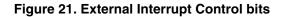

| 7.6     | EXTERNAL INTERRUPTS                                                                    |     |

| 0.1     |                                                                                        |     |

| 7.7     | 7.6.1 I/O Port Interrupt Sensitivity                                                   |     |

|         | ER SAVING MODES                                                                        |     |

| 8.1     | INTRODUCTION                                                                           |     |

| 8.2     | SLOW MODE                                                                              |     |

| • • •   |                                                                                        |     |

| 8.3     | WAIT MODE                                                                              | 4 I |

# **3 REGISTER & MEMORY MAP**

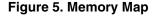

As shown in Figure 5, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register locations, up to 1024 bytes of RAM and up to 32 Kbytes of user program memory. The RAM space includes up to 256 bytes for the stack from 0100h to 01FFh.

The highest address bytes contain the user reset and interrupt vectors.

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

57/

## 6.2 MULTI-OSCILLATOR (MO)

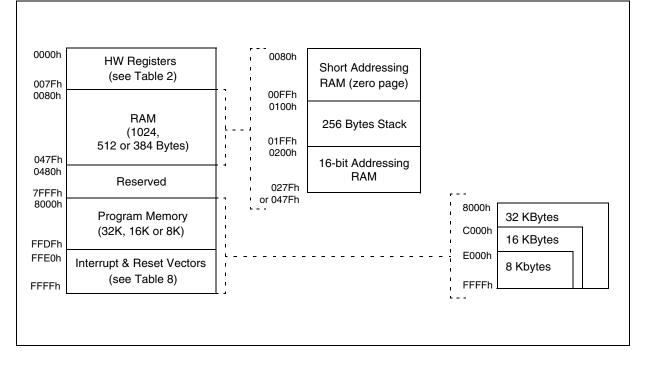

The main clock of the ST7 can be generated by three different source types coming from the multi-oscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 5. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

### **External Clock Source**

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

### **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to Section 14.1 on page 150 for more details on the frequency ranges). In this mode of the multioscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

In order not to exceed the max. operating frequency, the internal RC oscillator must not be used with the PLL.

47/

## 6.3 RESET SEQUENCE MANAGER (RSM)

## 6.3.1 Introduction

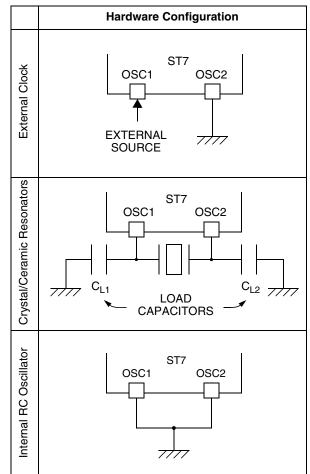

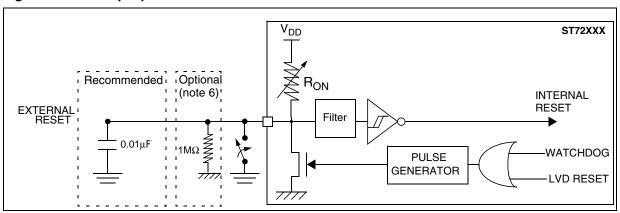

The reset sequence manager includes three RE-SET sources as shown in Figure 13:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

The basic RESET sequence consists of 3 phases as shown in Figure 12:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

5/

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application.

## Figure 13. Reset Block Diagram

The RESET vector fetch phase duration is 2 clock cycles.

## Figure 12. RESET Sequence Phases

|              | RESET                                      |                 |

|--------------|--------------------------------------------|-----------------|

| Active Phase | INTERNAL RESET<br>256 or 4096 CLOCK CYCLES | FETCH<br>VECTOR |

## 6.3.2 Asynchronous External RESET pin

The  $\overrightarrow{\text{RESET}}$  pin is both an input and an open-drain output with integrated  $\overrightarrow{\text{R}}_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See Electrical Characteristic section for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 14). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

## INTERRUPTS (Cont'd)

57

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 1  | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0=11 (level 3)       | 11:0=11?              |    |   |    |   |   |   |

| JRNM        | Jump if I1:0<>11                | 11:0<>11?             |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 1  | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   |   |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  |   |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  |   |   |   |

## Table 7. Dedicated Interrupt Instruction Set

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

## WATCHDOG TIMER (Cont'd)

## Figure 33. Exact Timeout Duration (t<sub>min</sub> and t<sub>max</sub>)

## WHERE:

**IF** CNT <  $\left[\frac{\text{MSB}}{4}\right]$

47/

$t_{min0} = (LSB + 128) \times 64 \times t_{OSC2}$   $t_{max0} = 16384 \times t_{OSC2}$  $t_{OSC2} = 125$ ns if  $f_{OSC2}$ =8 MHz

CNT = Value of T[5:0] bits in the WDGCR register (6 bits) MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 Bit<br>(MCCSR Reg.) | TB0 Bit<br>(MCCSR Reg.) | Selected MCCSR<br>Timebase | MSB | LSB |

|-------------------------|-------------------------|----------------------------|-----|-----|

| 0                       | 0                       | 2ms                        | 4   | 59  |

| 0                       | 1                       | 4ms                        | 8   | 53  |

| 1                       | 0                       | 10ms                       | 20  | 35  |

| 1                       | 1                       | 25ms                       | 49  | 54  |

To calculate the minimum Watchdog Timeout (t<sub>min</sub>):

**THEN**  $t_{min} = t_{min0} + 16384 \times CNT \times t_{osc2}$

**ELSE**

$$t_{min} = t_{min0} + \left[ 16384 \times \left( CNT - \left[ \frac{4CNT}{MSB} \right] \right) + (192 + LSB) \times 64 \times \left[ \frac{4CNT}{MSB} \right] \right] \times t_{osc2}$$

To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

$$\begin{aligned} \text{IF } \text{CNT} \leq \left[\frac{\text{MSB}}{4}\right] & \text{THEN} \quad t_{\text{max}} = t_{\text{max0}} + 16384 \times \text{CNT} \times t_{\text{osc2}} \\ & \text{ELSE} \quad t_{\text{max}} = t_{\text{max0}} + \left[16384 \times \left(\text{CNT} - \left[\frac{4\text{CNT}}{\text{MSB}}\right]\right) + (192 + \text{LSB}) \times 64 \times \left[\frac{4\text{CNT}}{\text{MSB}}\right]\right] \times t_{\text{osc2}} \end{aligned}$$

**Note:** In the above formulae, division results must be rounded down to the next integer value. **Example:**

With 2ms timeout selected in MCCSR register

| Value of T[5:0] Bits in<br>WDGCR Register (Hex.) | Min. Watchdog<br>Timeout (ms)<br>t <sub>min</sub> | Max. Watchdog<br>Timeout (ms)<br>t <sub>max</sub> |  |  |

|--------------------------------------------------|---------------------------------------------------|---------------------------------------------------|--|--|

| 00                                               | 1.496                                             | 2.048                                             |  |  |

| 3F                                               | 128                                               | 128.552                                           |  |  |

## 16-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |     |     |     |       | 0     |

|------|------|-----|-----|-----|-----|-------|-------|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | EXEDG |

## Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

**Note:** In Flash devices, this bit is not available for Timer A. It must be kept at its reset value.

### Bit 5 = **OPM** One Pulse Mode.

0: One Pulse Mode is not active.

1: One Pulse Mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

## Bit 4 = **PWM** Pulse Width Modulation.

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

### Bit 3, 2 = CC[1:0] Clock Control.

The timer clock mode depends on these bits:

### Table 16. Clock Control Bits

| Timer Clock                      | CC1 | CC0 |

|----------------------------------|-----|-----|

| f <sub>CPU</sub> / 4             | 0   | 0   |

| f <sub>CPU</sub> / 2             | 0   | 1   |

| f <sub>CPU</sub> / 8             | 1   | 0   |

| External Clock (where available) | 1   | 1   |

**Note**: If the external clock pin is not available, programming the external clock configuration stops the counter.

### Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

### Bit 0 = **EXEDG** External Clock Edge.

This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.

0: A falling edge triggers the counter register.

1: A rising edge triggers the counter register.

## 16-BIT TIMER (Cont'd)

Table 17. 16-Bit Timer Register Map and Reset Values

| Address<br>(Hex.)        | Register<br>Label | 7    | 6                 | 5    | 4                  | 3                 | 2     | 1                  | 0     |

|--------------------------|-------------------|------|-------------------|------|--------------------|-------------------|-------|--------------------|-------|

| Timer A: 32              | CR1               | ICIE | OCIE              | TOIE | FOLV2 <sup>1</sup> | FOLV1             | OLVL2 | IEDG1              | OLVL1 |

| Timer B: 42              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 31              | CR2               | OC1E | OC2E <sup>1</sup> | OPM  | PWM                | CC1               | CC0   | IEDG2 <sup>1</sup> | EXEDG |

| Timer B: 41              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 33              | CSR               | ICF1 | OCF1              | TOF  | ICF2 <sup>2</sup>  | OCF2 <sup>2</sup> | TIMD  | -                  | -     |

| Timer B: 43              | Reset Value       | х    | х                 | х    | х                  | х                 | 0     | х                  | x     |

| Timer A: 34              | IC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 44              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 35              | IC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 45              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 36              | OC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 46              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 37              | OC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 47              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3E <sup>3</sup> | OC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4E              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3F <sup>3</sup> | OC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4F              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 38              | CHR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 48              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 39              | CLR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 49              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3A              | ACHR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4A              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 3B              | ACLR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4B              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3C <sup>4</sup> | IC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4C              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

| Timer A: 3D <sup>4</sup> | IC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4D              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

<sup>1</sup> In Flash devices, these bits are not used in Timer A and must be kept cleared.

<sup>2</sup> In Flash devices, these bits are forced by hardware to 0 in Timer A

<sup>3</sup> In Flash devices, the TAOC2HR and TAOC2LR Registers are write only, reading them will return undefined values

<sup>4</sup> In Flash devices, the TAIC2HR and TAIC2LR registers are not present.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

### 10.4.5 Error Flags

## 10.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device has its SS pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

### 10.4.5.2 Overrun Condition (OVR)

An overrun condition occurs, when the master device has sent a data byte and the slave device has

not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

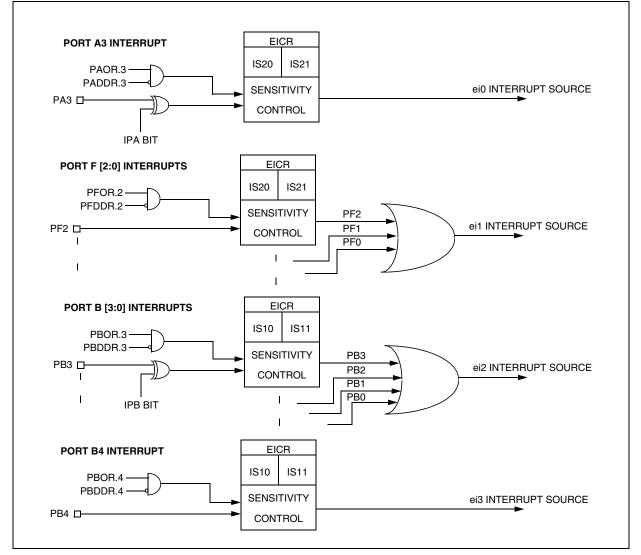

### 10.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 10.4.3.2 Slave Select Management.

**Note:** a "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

Clearing the WCOL bit is done through a software sequence (see Figure 51).

### Figure 51. Clearing the WCOL bit (Write Collision Flag) Software Sequence

## SERIAL PERIPHERAL INTERFACE (Cont'd)

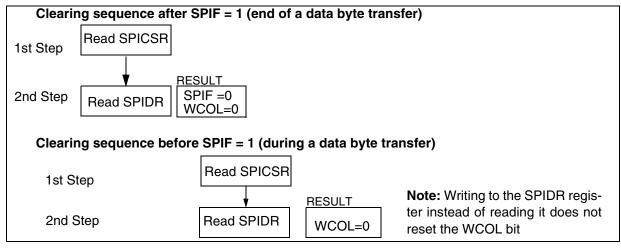

## 10.4.5.4 Single Master Systems

57/

A typical single master system may be configured, using an MCU as the master and four MCUs as slaves (see Figure 52).

The master device selects the individual slave devices by using four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

## 10.4.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up by<br>an interrupt with "exit from HALT mode" ca-<br>pability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 10.4.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware. **Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 10.4.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

### 10.4.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Transfer<br>Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode Fault<br>Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

### 10.5.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1.).

### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

5/

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 2.).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## **Framing Error**

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

- A break is received.

When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

## 10.5.4.4 Conventional Baud Rate Generation

The baud rate for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows:

$$Tx = \frac{f_{CPU}}{(16*PR)*TR} \qquad Rx = \frac{f_{CPU}}{(16*PR)*RR}$$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits) TR = 1, 2, 4, 8, 16, 32, 64,128 (see SCT[2:0] bits) RR = 1, 2, 4, 8, 16, 32, 64,128 (see SCR[2:0] bits)

All these bits are in the SCIBRR register.

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

**Note:** The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

## 10.5.4.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 3.

The output clock rate sent to the transmitter or to the receiver is the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCI-ERPR or the SCIETPR register. **Note:** the extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \cdot ETPR^{*}(PR^{*}TR)} Rx = \frac{f_{CPU}}{16 \cdot ERPR^{*}(PR^{*}RR)}$$

with:

ETPR = 1,..,255 (see SCIETPR register)

ERPR = 1,.. 255 (see SCIERPR register)

### 10.5.4.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non addressed receivers.

The non addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits can not be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

Receiver wakes-up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes-up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

**CAUTION**: In Mute mode, do not write to the SCICR2 register. If the SCI is in Mute mode during the read operation (RWU = 1) and a address mark wake up event occurs (RWU is reset) before the write operation, the RWU bit is set again by this write operation. Consequently the address byte is lost and the SCI is not woken up from Mute mode.

## **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

### 12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | Ratings                                             | Maximum value                   | Unit    |

|-------------------------------------------|-----------------------------------------------------|---------------------------------|---------|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                      | 6.5                             |         |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming Voltage                                 | 13                              | v       |

| V <sub>IN</sub> <sup>1) &amp; 2)</sup>    | Input Voltage on true open drain pin                | V <sub>SS</sub> -0.3 to 6.5     | v       |

| VIN /                                     | Input voltage on any other pin                      | $V_{SS}$ -0.3 to $V_{DD}$ +0.3  |         |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins     | 50                              | mV      |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins   | 50                              | IIIV    |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model) | son Section 12.8.3 on n         | 200 132 |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)    | - see Section 12.8.3 on page 13 |         |

### **12.2.2 Current Characteristics**

| Symbol                                       | Ratings                                           |                                | Maximum value | Unit |  |

|----------------------------------------------|---------------------------------------------------|--------------------------------|---------------|------|--|

| 1                                            | Total current into V <sub>DD</sub> power lines    | 32-pin devices                 | 75            | mA   |  |

| IVDD                                         | (source) <sup>3)</sup>                            | 44-pin devices                 | 150           | IIIA |  |

|                                              | Total current out of V <sub>SS</sub> ground lines | 32-pin devices                 | 75            | mA   |  |

| Ivss                                         | (sink) <sup>3)</sup>                              | 44-pin devices                 | 150           | IIIA |  |

|                                              | Output current sunk by any standard I/            | O and control pin              | 25            |      |  |

| I <sub>IO</sub>                              | Output current sunk by any high sink l            | 50                             |               |      |  |

|                                              | Output current source by any I/Os and             | - 25                           |               |      |  |

|                                              | Injected current on VPP pin                       |                                | ± 5           |      |  |

|                                              | Injected current on RESET pin                     | ± 5                            | mA            |      |  |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on OSC1 and OSC2 p               | ± 5                            |               |      |  |

|                                              | Injected current on Flash device pin Pl           | +5                             |               |      |  |

|                                              | Injected current on any other pin 5) & 6)         | ± 5                            |               |      |  |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup>         | Total injected current (sum of all I/O ar         | nd control pins) <sup>5)</sup> | ± 25          |      |  |

#### Notes:

1. Directly connecting the RESET and I/O pins to  $V_{DD}$  or  $V_{SS}$  could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7k $\Omega$  for RESET, 10k $\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to  $V_{DD}$  or  $V_{SS}$ .

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "ADC Accuracy" on page 145.

For best reliability, it is recommended to avoid negative injection of more than 1.6mA.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

## SUPPLY CURRENT CHARACTERISTICS (Cont'd)

## 12.5.2 Supply and Clock Managers

The previous current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode).

| Symbol                 | Parameter                                                     | Conditions           | Тур                                  | Max | Unit |

|------------------------|---------------------------------------------------------------|----------------------|--------------------------------------|-----|------|

| I <sub>DD(RCINT)</sub> | Supply current of internal RC oscillator                      |                      | 625                                  |     |      |

| I <sub>DD(RES)</sub>   | Supply current of resonator oscillator <sup>1) &amp; 2)</sup> |                      | see Section<br>12.6.3 on page<br>125 |     | μA   |

| I <sub>DD(PLL)</sub>   | PLL supply current                                            | V <sub>DD</sub> = 5V | 360                                  |     | μA   |

| I <sub>DD(LVD)</sub>   | LVD supply current                                            | V <sub>DD</sub> = 5V | 150                                  | 300 |      |

#### Notes:

1. Data based on characterization results done with the external components specified in Section 12.6.3, not tested in production.

2. As the oscillator is based on a current source, the consumption does not depend on the voltage.

## CONTROL PIN CHARACTERISTICS (Cont'd)

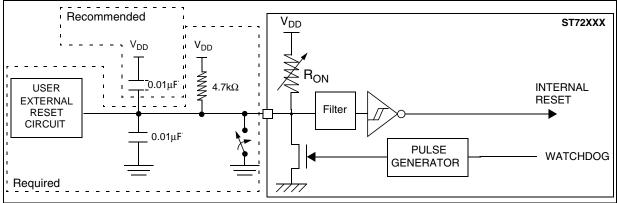

## Figure 77. RESET pin protection when LVD is enabled.<sup>1)2)3)4)5)6)7)</sup>

1. The reset network protects the device against parasitic resets.

2. The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

3. Whatever the reset source is (internal or external), the user must ensure that the level on the  $\overrightarrow{\text{RESET}}$  pin can go below the V<sub>IL</sub> max. level specified in Section 12.10.1. Otherwise the reset will not be taken into account internally.

4. Because the reset circuit is <u>design</u>ed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin (by an external pull-up for example) is less than the absolute maximum value specified for  $I_{INJ(RESET)}$  in Section 12.2.2 on page 117.

5. When the LVD is enabled, it is mandatory not to connect a pull-up resistor. A 10nF pull-down capacitor is recommended to filter noise on the reset line.

6. In case a capacitive power supply is used, it is recommended to connect a1M $\Omega$  pull-down resistor to the RESET pin to discharge any residual voltage induced by this capacitive power supply (this will add 5µA to the power consumption of the MCU).

7. Tips when using the LVD:

- 1. Check that all recommendations related to ICCCLK and reset circuit have been applied (see notes above)

- 2. Check that the power supply is properly decoupled (100nF + 10 $\mu$ F close to the MCU). Refer to AN1709. If this cannot be done, it is recommended to put a 100nF + 1M $\Omega$  pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoiding any start-up marginality. In most cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor."

## 10-BIT ADC CHARACTERISTICS (Cont'd)

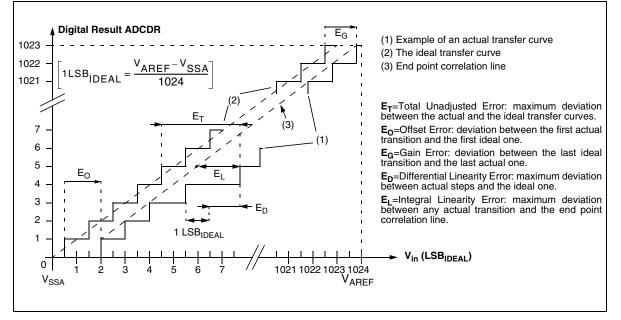

## 12.13.3 ADC Accuracy

Conditions:  $V_{DD}=5V^{(1)}$

| Symbol            | Parameter                            | Conditions                                | Flash [ | Unit              |     |

|-------------------|--------------------------------------|-------------------------------------------|---------|-------------------|-----|

| Symbol            | Faialletei                           | Conditions                                | Тур     | Max <sup>2)</sup> | Omt |

| IE <sub>T</sub> I | Total unadjusted error <sup>1)</sup> |                                           | 4       | 6                 |     |

| IE <sub>O</sub> I | Offset error 1)                      |                                           | 3       | 5                 |     |

| IE <sub>G</sub> I | Gain Error <sup>1)</sup>             |                                           | 0.5     | 4.5               | LSB |

| IE <sub>D</sub> I | Differential linearity error 1)      | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1.5     | 4.5               |     |

| IELI              | Integral linearity error 1)          | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1.5     | 4.5               |     |

### Notes:

1. ADC Accuracy vs. Negative Injection Current: Injecting negative current may reduce the accuracy of the conversion being performed on another analog input.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.9 does not affect the ADC accuracy.

2. Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to 125°C ( $\pm$  3 $\sigma$  distribution limits).

### Figure 87. ADC Accuracy Characteristics

## 14 ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION

## **14.1 FLASH OPTION BYTES**

|         | STATIC OPTION BYTE 0 |    |      |   |   |       | STATIC OPTION BYTE 1 |      |     |     |   |   |   |   |              |      |   |   |   |   |    |   |  |    |      |      |    |       |    |     |

|---------|----------------------|----|------|---|---|-------|----------------------|------|-----|-----|---|---|---|---|--------------|------|---|---|---|---|----|---|--|----|------|------|----|-------|----|-----|

|         | 7                    |    |      |   |   |       |                      | 0    | 7   |     |   |   |   |   |              | 0    |   |   |   |   |    |   |  |    |      |      |    |       |    |     |

|         | WI                   | DG | rved | v | D |       | ~                    | rved | -   | ~   | ~ |   |   |   | а <u>-</u> 5 |      | - | - | 5 | 5 | 51 | 5 |  | TC | OSC. | TYPE | OS | SCRAN | GE | DFF |

|         | НАLТ                 | SW | Rese | 1 | 0 | Resei | Reser                | FMP  | PKG | RS. | 1 | 0 | 2 | 1 | 0            | PLLQ |   |   |   |   |    |   |  |    |      |      |    |       |    |     |

| Default | 1                    | 1  | 1    | 0 | 0 | 1     | 1                    | 1    | 1   | 1   | 1 | 0 | 1 | 1 | 1            | 1    |   |   |   |   |    |   |  |    |      |      |    |       |    |     |

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with the internal RC clock source.

### **OPTION BYTE 0**

OPT7= **WDG HALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

OPT6= **WDG SW** Hardware or software watchdog This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

### OPT4:3= VD[1:0] Voltage detection

These option bits enable the voltage detection block (LVD, and AVD) with a selected threshold for the LVD and AVD.

| Selected Low Voltage Detector                    | VD1 | VD0 |

|--------------------------------------------------|-----|-----|

| LVD and AVD Off                                  | 1   | 1   |

| Lowest Voltage Threshold (V <sub>DD</sub> ~3V)   | 1   | 0   |

| Medium Voltage Threshold (V <sub>DD</sub> ~3.5V) | 0   | 1   |

| Highest Voltage Threshold (V <sub>DD</sub> ~4V)  | 0   | 0   |

**Caution:** If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed. For details on the AVD and LVD threshold levels refer to Section 12.4.1 on page 119

OPT2:1 = Reserved, must be kept at default value.

OPT0= **FMP\_R** Flash memory read-out protection Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory.

Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 7.3.1 on page 37 and the ST7 Flash Programming Reference Manual for more details.

0: Read-out protection enabled

1: Read-out protection disabled

# 14.4.1 Socket and Emulator Adapter Information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in Table 29.

**Note:** Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet (www.yamaichi.de for TQFP44 10 x 10 and www.ironwoodelectronics.com for TQFP32 7 x 7).

## Table 29. Suggested List of Socket Types

| Device        | Socket (supplied with<br>ST7MDT20J-EMU3) | Emulator Adapter (supplied with<br>ST7MDT20J-EMU3) |  |  |  |

|---------------|------------------------------------------|----------------------------------------------------|--|--|--|

| TQFP32 7 X 7  | IRONWOOD SF-QFE32SA-L-01                 | IRONWOOD SK-UGA06/32A-01                           |  |  |  |

| TQFP44 10 X10 | YAMAICHI IC149-044-*52-*5                | YAMAICHI ICP-044-5                                 |  |  |  |