#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -10°C ~ 85°C (TA)                                                    |

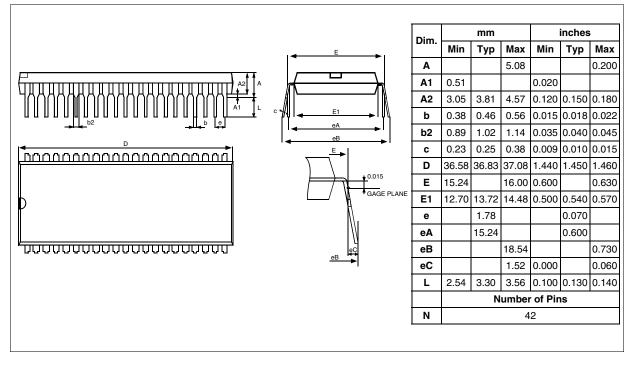

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 42-DIP (0.600", 15.24mm)                                             |

| Supplier Device Package    | •                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324j6b5 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 8.4     | ACT                                                                                                                                                      | IVE-HALT AND HALT MODES                                                                                                                                                                                                                                                                                                                     | 42                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|         | 8.4.1                                                                                                                                                    | ACTIVE-HALT MODE                                                                                                                                                                                                                                                                                                                            | 42                                                                                     |

|         | 8.4.2                                                                                                                                                    | HALT MODE                                                                                                                                                                                                                                                                                                                                   | 43                                                                                     |

| 9 I/O P |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

| 9.1     | INTF                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                             | 45                                                                                     |

| 9.2     | FUN                                                                                                                                                      | CTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                         | 45                                                                                     |

|         | 9.2.1                                                                                                                                                    | Input Modes                                                                                                                                                                                                                                                                                                                                 | 45                                                                                     |

|         | 9.2.2                                                                                                                                                    | Output Modes                                                                                                                                                                                                                                                                                                                                |                                                                                        |

|         |                                                                                                                                                          | Alternate Functions                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 9.3     |                                                                                                                                                          | PORT IMPLEMENTATION                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 9.4     | LOW                                                                                                                                                      | POWER MODES                                                                                                                                                                                                                                                                                                                                 | 48                                                                                     |

| 9.5     | INTE                                                                                                                                                     | RRUPTS                                                                                                                                                                                                                                                                                                                                      | 48                                                                                     |

|         |                                                                                                                                                          | I/O Port Implementation                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|         |                                                                                                                                                          | PERIPHERALS                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

| 10.1    | I WAT                                                                                                                                                    | CHDOG TIMER (WDG)                                                                                                                                                                                                                                                                                                                           | 51                                                                                     |

|         | 10.1.1                                                                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                | 51                                                                                     |

|         |                                                                                                                                                          | Main Features                                                                                                                                                                                                                                                                                                                               |                                                                                        |

|         |                                                                                                                                                          | Functional Description                                                                                                                                                                                                                                                                                                                      |                                                                                        |

|         |                                                                                                                                                          | How to Program the Watchdog Timeout                                                                                                                                                                                                                                                                                                         |                                                                                        |

|         |                                                                                                                                                          | Low Power Modes                                                                                                                                                                                                                                                                                                                             |                                                                                        |

|         |                                                                                                                                                          | Using Halt Mode with the WDG (WDGHALT option)                                                                                                                                                                                                                                                                                               |                                                                                        |

|         |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

|         |                                                                                                                                                          | Register Description                                                                                                                                                                                                                                                                                                                        |                                                                                        |

| 10.2    |                                                                                                                                                          | N CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) .                                                                                                                                                                                                                                                                              |                                                                                        |

|         | 10.2.1                                                                                                                                                   | Programmable CPU Clock Prescaler                                                                                                                                                                                                                                                                                                            | 56                                                                                     |

|         | 10.2.2                                                                                                                                                   | Clock-out Capability                                                                                                                                                                                                                                                                                                                        | 56                                                                                     |

|         |                                                                                                                                                          | Real Time Clock Timer (RTC)                                                                                                                                                                                                                                                                                                                 |                                                                                        |

|         |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

|         |                                                                                                                                                          | Beeper                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

|         |                                                                                                                                                          | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57                                                                                     |

|         | 10.2.6                                                                                                                                                   | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57                                                                               |

| 10 3    | 10.2.6<br>10.2.7                                                                                                                                         | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>57                                                                         |

| 10.3    | 10.2.6<br>10.2.7<br>3 16-B                                                                                                                               | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>57<br>59                                                                   |

| 10.3    | 10.2.6<br>10.2.7<br>3 16-B<br>10.3.1                                                                                                                     | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>57<br>59<br>59                                                             |

| 10.3    | 10.2.6<br>10.2.7<br>3 16-B<br>10.3.1<br>10.3.2                                                                                                           | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>57<br>59<br>59<br>59                                                       |

| 10.3    | 10.2.6<br>10.2.7<br>3 16-B<br>10.3.1<br>10.3.2<br>10.3.3                                                                                                 | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>59<br>59<br>59<br>59                                                       |

| 10.3    | 10.2.6<br>10.2.7<br>16-B<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4                                                                                         | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>59<br>59<br>59<br>59<br>59<br>71                                           |

| 10.3    | 10.2.6<br>10.2.7<br>3 16-B<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5                                                                             | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>59<br>59<br>59<br>59<br>59<br>71<br>71                                     |

|         | 10.2.6<br>10.2.7<br>16-B<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7                                                           | Low Power Modes                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>71                               |

|         | 10.2.6<br>10.2.7<br>16-B<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br>1 SER                                                  | Low Power Modes<br>Interrupts<br>Register Description<br>IT TIMER<br>Introduction<br>Main Features<br>Functional Description<br>Low Power Modes<br>Interrupts<br>Summary of Timer modes<br>Register Description<br>IAL PERIPHERAL INTERFACE (SPI)                                                                                           | 57<br>57<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>72<br>79                         |

|         | 10.2.6<br>10.2.7<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br>10.3.7<br>10.4.1                                               | Low Power Modes<br>Interrupts<br>Register Description<br>IT TIMER<br>Introduction<br>Main Features<br>Functional Description<br>Low Power Modes<br>Interrupts<br>Summary of Timer modes<br>Register Description<br>IAL PERIPHERAL INTERFACE (SPI)                                                                                           | 57<br>57<br>59<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>72<br>79<br>79             |

|         | 10.2.6<br>10.2.7<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br>1 SER<br>10.4.1<br>10.4.2                                      | Low Power Modes<br>Interrupts<br>Register Description<br>IT TIMER<br>Introduction<br>Main Features<br>Functional Description<br>Low Power Modes<br>Interrupts<br>Summary of Timer modes<br>Register Description<br>IAL PERIPHERAL INTERFACE (SPI)                                                                                           | 57<br>57<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>72<br>79<br>79                   |

|         | 10.2.6<br>10.2.7<br>16-B<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br>\$ SER<br>10.4.1<br>10.4.2<br>10.4.3                   | Low Power Modes<br>Interrupts<br>Register Description<br>IT TIMER<br>Introduction<br>Main Features<br>Functional Description<br>Low Power Modes<br>Interrupts<br>Summary of Timer modes<br>Register Description<br>IAL PERIPHERAL INTERFACE (SPI)<br>Introduction<br>Main Features<br>General Description                                   | 57<br>57<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>72<br>79<br>79<br>79             |

|         | 10.2.6<br>10.2.7<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br>10.4.1<br>10.4.2<br>10.4.3<br>10.4.4                           | Low Power Modes<br>Interrupts<br>Register Description<br>IT TIMER<br>Introduction<br>Main Features<br>Functional Description<br>Low Power Modes<br>Interrupts<br>Summary of Timer modes<br>Register Description<br>IAL PERIPHERAL INTERFACE (SPI)<br>Introduction<br>Main Features<br>General Description<br>Clock Phase and Clock Polarity | 57<br>57<br>59<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>72<br>79<br>79<br>79<br>83 |

|         | 10.2.6<br>10.2.7<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br><b>4</b> SER<br>10.4.1<br>10.4.2<br>10.4.3<br>10.4.4<br>10.4.5 | Low Power Modes<br>Interrupts<br>Register Description<br>IT TIMER<br>Introduction<br>Main Features<br>Functional Description<br>Low Power Modes<br>Interrupts<br>Summary of Timer modes<br>Register Description<br>IAL PERIPHERAL INTERFACE (SPI)<br>Introduction<br>Main Features<br>General Description                                   | 57<br>57<br>59<br>59<br>59<br>59<br>71<br>71<br>71<br>72<br>79<br>79<br>79<br>83<br>84 |

| Address                                                                                                                                      | Block   | Register<br>Label                                                                                                                                                        | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reset<br>Status                                                                                                     | Remarks                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Ch<br>003Ch<br>003Ch<br>003Ch | TIMER A | TACR2<br>TACR1<br>TACSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR<br>TAOC1LR<br>TACHR<br>TACHR<br>TACLR<br>TAACHR<br>TAACLR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAOC2HR<br>TAOC2LR | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Control/Status Register <sup>3)4)</sup><br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register<br>Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter High Register<br>Timer A Counter Low Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register <sup>3)</sup><br>Timer A Input Compare 2 High Register <sup>4)</sup><br>Timer A Output Compare 2 Low Register <sup>4)</sup> | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>R/W                    |

| 0040h                                                                                                                                        |         |                                                                                                                                                                          | Reserved Area (1 Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |                                                                                                                                                                                                                |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Ch          | TIMER B | TBCR2<br>TBCR1<br>TBCSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1LR<br>TBCHR<br>TBCHR<br>TBCLR<br>TBACLR<br>TBACLR<br>TBIC2HR<br>TBIC2LR<br>TBIC2LR                      | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Control/Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter Low Register<br>Timer B Input Capture 2 High Register<br>Timer B Input Capture 2 Low Register<br>Timer B Output Compare 2 High Register                                                                                                                                     | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h               | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                                         | SCI     | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                                       | SCI Status Register<br>SCI Data Register<br>SCI Baud Rate Register<br>SCI Control Register 1<br>SCI Control Register 2<br>SCI Extended Receive Prescaler Register<br>Reserved area<br>SCI Extended Transmit Prescaler Register                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C0h<br>xxh<br>00h<br>x000 0000h<br>00h<br>00h<br><br>00h                                                            | Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                                   |

| 0058h<br>to<br>006Fh                                                                                                                         |         |                                                                                                                                                                          | Reserved Area (24 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |                                                                                                                                                                                                                |

| 0070h<br>0071h<br>0072h                                                                                                                      | ADC     | ADCCSR<br>ADCDRH<br>ADCDRL                                                                                                                                               | Control/Status Register<br>Data High Register<br>Data Low Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00h<br>00h<br>00h                                                                                                   | R/W<br>Read Only<br>Read Only                                                                                                                                                                                  |

| 0073h<br>007Fh                                                                                                                               |         | 1                                                                                                                                                                        | Reserved Area (13 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I                                                                                                                   |                                                                                                                                                                                                                |

57

## CENTRAL PROCESSING UNIT (Cont'd)

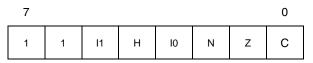

## Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

## Arithmetic Management Bits

#### Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{th}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

## Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

## Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

## **Interrupt Management Bits**

#### Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 1 | 10 |

|-------------------------------|---|----|

| Level 0 (main)                | 1 | 0  |

| Level 1                       | 0 | 1  |

| Level 2                       | 0 | 0  |

| Level 3 (= interrupt disable) | 1 | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

## POWER SAVING MODES (Cont'd)

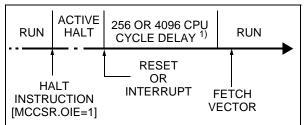

## 8.4 ACTIVE-HALT AND HALT MODES

ACTIVE-HALT and HALT modes are the two lowest power consumption modes of the MCU. They are both entered by executing the 'HALT' instruction. The decision to enter either in ACTIVE-HALT or HALT mode is given by the MCC/RTC interrupt enable flag (OIE bit in MCCSR register).

| MCCSR<br>OIE bit | Power Saving Mode entered when HALT<br>instruction is executed |

|------------------|----------------------------------------------------------------|

| 0                | HALT mode                                                      |

| 1                | ACTIVE-HALT mode                                               |

## 8.4.1 ACTIVE-HALT MODE

ACTIVE-HALT mode is the lowest power consumption mode of the MCU with a real time clock available. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is set (see Section 10.2 on page 56 for more details on the MCCSR register).

The MCU can exit ACTIVE-HALT mode on reception of either an MCC/RTC interrupt, a specific interrupt (see Table 8, "Interrupt Mapping," on page 36) or a RESET. When exiting ACTIVE-HALT mode by means of an interrupt, no 256 or 4096 CPU cycle delay occurs. The CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 26). When entering ACTIVE-HALT mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In ACTIVE-HALT mode, only the main oscillator and its associated counter (MCC/RTC) are running to keep a wake-up time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as external or auxiliary oscillator).

The safeguard against staying locked in ACTIVE-HALT mode is provided by the oscillator interrupt.

**Note:** As soon as the interrupt capability of one of the oscillators is selected (MCCSR.OIE bit set), entering ACTIVE-HALT mode while the Watchdog is active does not generate a RESET.

This means that the device cannot spend more than a defined delay in this power saving mode.

**CAUTION:** When exiting ACTIVE-HALT mode following an interrupt, OIE bit of MCCSR register must not be cleared before  $t_{DELAY}$  after the interrupt occurs ( $t_{DELAY}$  = 256 or 4096  $t_{CPU}$  delay de-

pending on option byte). Otherwise, the ST7 enters HALT mode for the remaining  $t_{\text{DELAY}}$  period.

#### Figure 25. ACTIVE-HALT Timing Overview

#### Figure 26. ACTIVE-HALT Mode Flow-chart

#### Notes:

1. This delay occurs only if the MCU exits ACTIVE-HALT mode by means of a RESET.

2. Peripheral clocked with an external clock source can still be active.

3. Only the MCC/RTC interrupt and some specific interrupts can exit the MCU from ACTIVE-HALT mode (such as external interrupt). Refer to Table 8, "Interrupt Mapping," on page 36 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

## POWER SAVING MODES (Cont'd)

#### 8.4.2.1 Halt Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

## I/O PORTS (Cont'd)

## Table 13. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |  |

|-------------------|--------------------------|-----|---|---|---|---|---|---|-----|--|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |  |

| 0000h             | PADR                     |     |   |   |   |   |   |   |     |  |

| 0001h             | PADDR                    | MSB |   |   |   |   |   |   | LSB |  |

| 0002h             | PAOR                     |     |   |   |   |   |   |   |     |  |

| 0003h             | PBDR                     |     |   |   |   |   |   |   |     |  |

| 0004h             | PBDDR                    | MSB |   |   |   |   |   |   | LSB |  |

| 0005h             | PBOR                     |     |   |   |   |   |   |   |     |  |

| 0006h             | PCDR                     |     |   |   |   |   |   |   |     |  |

| 0007h             | PCDDR                    | MSB |   |   |   |   |   |   | LSB |  |

| 0008h             | PCOR                     |     |   |   |   |   |   |   |     |  |

| 0009h             | PDDR                     |     |   |   |   |   |   |   |     |  |

| 000Ah             | PDDDR                    | MSB |   |   |   |   |   |   | LSB |  |

| 000Bh             | PDOR                     |     |   |   |   |   |   |   |     |  |

| 000Ch             | PEDR                     |     |   |   |   |   |   |   |     |  |

| 000Dh             | PEDDR                    | MSB |   |   |   |   |   |   | LSB |  |

| 000Eh             | PEOR                     | Ī   |   |   |   |   |   |   |     |  |

| 000Fh             | PFDR                     |     |   |   |   |   |   |   |     |  |

| 0010h             | PFDDR                    | MSB |   |   |   |   |   |   | LSB |  |

| 0011h             | PFOR                     | Ī   |   |   |   |   |   |   |     |  |

## WATCHDOG TIMER (Cont'd)

## 10.1.5 Low Power Modes

| Mode | Description  |             |                                                                                                                                                                                                                                                                                                                                |

|------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLOW | No effect on | Watchdog.   |                                                                                                                                                                                                                                                                                                                                |

| WAIT | No effect on | Watchdog.   |                                                                                                                                                                                                                                                                                                                                |

|      | OIE bit in   | WDGHALT bit |                                                                                                                                                                                                                                                                                                                                |

|      | MCCSR        | in Option   |                                                                                                                                                                                                                                                                                                                                |

|      | register     | Byte        |                                                                                                                                                                                                                                                                                                                                |

|      | 0            | 0           | No Watchdog reset is generated. The MCU enters Halt mode. The Watch-<br>dog counter is decremented once and then stops counting and is no longer<br>able to generate a watchdog reset until the MCU receives an external inter-<br>rupt or a reset.                                                                            |

| HALT | 0            | 0           | If an external interrupt is received, the Watchdog restarts counting after 256 or 4096 CPU clocks. If a reset is generated, the Watchdog is disabled (reset state) unless Hardware Watchdog is selected by option byte. For application recommendations see Section 10.1.7 below.                                              |

|      | 0            | 1           | A reset is generated.                                                                                                                                                                                                                                                                                                          |

|      | 1            | x           | No reset is generated. The MCU enters Active Halt mode. The Watchdog counter is not decremented. It stop counting. When the MCU receives an oscillator interrupt or external interrupt, the Watchdog restarts counting immediately. When the MCU receives a reset the Watchdog restarts counting after 256 or 4096 CPU clocks. |

#### 10.1.6 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the WDGCR is not used. Refer to the Option Byte description.

## 10.1.7 Using Halt Mode with the WDG (WDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled.

Before executing the HALT instruction, refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller.

## 10.1.8 Interrupts

None.

## 10.1.9 Register Description CONTROL REGISTER (WDGCR)

#### Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | ТЗ | T2 | T1 | то |

#### Bit 7 = **WDGA** Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bit 6:0 = **T[6:0]** 7-bit counter (MSB to LSB).

These bits contain the value of the watchdog counter. It is decremented every 16384  $f_{OSC2}$  cycles (approx.). A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

## Table 14. Watchdog Timer Register Map and Reset Values

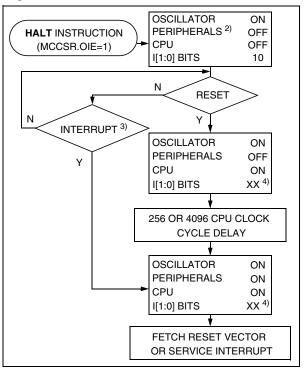

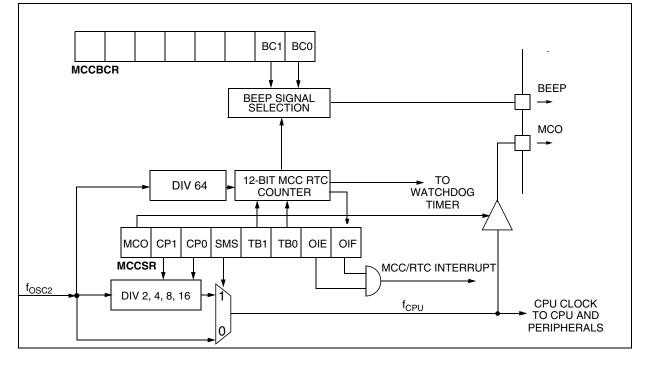

## 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC)

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real time clock timer with interrupt capability

Each function can be used independently and simultaneously.

#### 10.2.1 Programmable CPU Clock Prescaler

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages SLOW power saving mode (See Section 8.2 SLOW MODE for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

#### 10.2.2 Clock-out Capability

The clock-out capability is an alternate function of an I/O port pin that outputs the  $f_{CPU}$  clock to drive

external devices. It is controlled by the MCO bit in the MCCSR register.

**CAUTION**: When selected, the clock out pin suspends the clock during ACTIVE-HALT mode.

## 10.2.3 Real Time Clock Timer (RTC)

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCC-SR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE-HALT mode when the HALT instruction is executed. See Section 8.4 AC-TIVE-HALT AND HALT MODES for more details.

#### 10.2.4 Beeper

The beep function is controlled by the MCCBCR register. It can output three selectable frequencies on the BEEP pin (I/O port alternate function).

47/

#### Figure 34. Main Clock Controller (MCC/RTC) Block Diagram

## SERIAL PERIPHERAL INTERFACE (Cont'd)

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master MCU.

#### 10.4.3.1 Functional Description

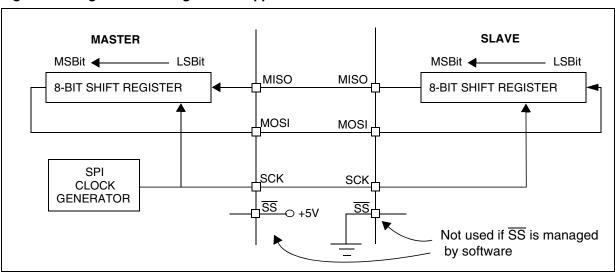

A basic example of interconnections between a single master and a single slave is illustrated in Figure 47.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 50) but master and slave must be programmed with the same timing mode.

#### Figure 47. Single Master/ Single Slave Application

## **10.5 SERIAL COMMUNICATIONS INTERFACE (SCI)**

#### 10.5.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 10.5.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

#### **10.5.3 General Description**

The interface is externally connected to another device by two pins (see Figure 2.):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

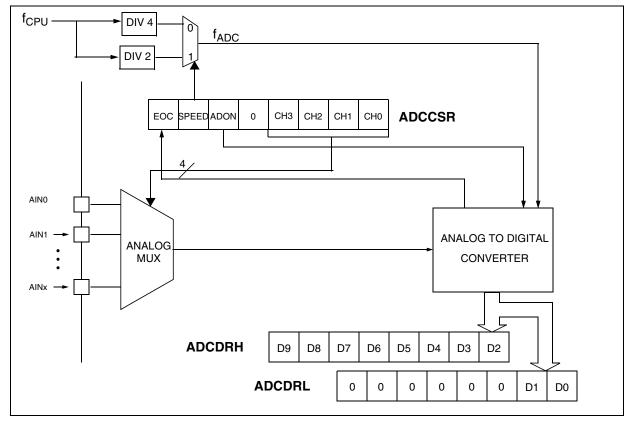

## 10.6 10-BIT A/D CONVERTER (ADC)

#### 10.6.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 10.6.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

**47**/

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 57.

## Figure 57. ADC Block Diagram

## **10-BIT A/D CONVERTER** (Cont'd)

57

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

## Table 23. ADC Register Map and Reset Values

## **OPERATING CONDITIONS** (Cont'd)

## **12.4 LVD/AVD CHARACTERISTICS**

## 12.4.1 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for  $\mathsf{T}_\mathsf{A}$

| Symbol                | Parameter                                            | Conditions                                   | Min                | Тур  | Max                | Unit |

|-----------------------|------------------------------------------------------|----------------------------------------------|--------------------|------|--------------------|------|

|                       | Baratasha ang diseraha dal                           | VD level = High in option byte               | 4.0 <sup>1)</sup>  | 4.2  | 4.5                |      |

| V <sub>IT+(LVD)</sub> | Reset release threshold<br>(V <sub>DD</sub> rise)    | VD level = Med. in option byte <sup>2)</sup> | 3.55 <sup>1)</sup> | 3.75 | 4.0 <sup>1)</sup>  |      |

| (272)                 |                                                      | VD level = Low in option byte <sup>2)</sup>  | 2.95 <sup>1)</sup> | 3.15 | 3.35 <sup>1)</sup> | v    |

|                       |                                                      | VD level = High in option byte               | 3.8                | 4.0  | 4.25 <sup>1)</sup> | v    |

| V <sub>IT-(LVD)</sub> | Reset generation threshold<br>(V <sub>DD</sub> fall) | VD level = Med. in option byte <sup>2)</sup> | 3.35 <sup>1)</sup> | 3.55 | 3.75 <sup>1)</sup> |      |

|                       |                                                      | VD level = Low in option byte <sup>2)</sup>  | 2.8 <sup>1)</sup>  | 3.0  | 3.15 <sup>1)</sup> |      |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis 1)                  | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub> | 150                | 200  | 250                | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>1)</sup>              |                                              | 6μs/V              |      | 100ms/V            |      |

| t <sub>g(VDD)</sub>   | Filtered glitch delay on $V_{DD}^{(1)}$              | Not detected by the LVD                      |                    |      | 40                 | ns   |

#### Notes:

1. Data based on characterization results, not tested in production.

2. If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range.

## 12.4.2 Auxiliary Voltage Detector (AVD) Thresholds

Subject to general operating conditions for  $\mathsf{T}_\mathsf{A}$

| Symbol                 | Parameter                                                                   | Conditions                                   | Min                | Тур               | Max                | Unit |

|------------------------|-----------------------------------------------------------------------------|----------------------------------------------|--------------------|-------------------|--------------------|------|

|                        | $1 \rightarrow 0$ AVDE flog toggle threshold                                | VD level = High in option byte               | 4.4 <sup>1)</sup>  | 4.6               | 4.9                |      |

| V <sub>IT+(AVD)</sub>  | $(AVD)$ 1 $\Rightarrow$ 0 AVDF flag toggle threshold (V <sub>DD</sub> rise) | VD level = Med. in option byte               | 3.95 <sup>1)</sup> | 4.15              | 4.4 <sup>1)</sup>  |      |

| (v <sub>DD</sub> lise) | VD level = Low in option byte                                               | 3.4 <sup>1)</sup>                            | 3.6                | 3.8 <sup>1)</sup> | v                  |      |

|                        | 0⇒1 AVDF flag toggle threshold                                              | VD level = High in option byte               | 4.2                | 4.4               | 4.65 <sup>1)</sup> | v    |

| V <sub>IT-(AVD)</sub>  |                                                                             | VD level = Med. in option byte               | 3.75 <sup>1)</sup> | 4.0               | 4.2 <sup>1)</sup>  |      |

| . ,                    | $V_{\text{IT-(AVD)}}$ ( $V_{\text{DD}}$ fall)                               | VD level = Low in option byte                | 3.2 <sup>1)</sup>  | 3.4               | 3.6 <sup>1)</sup>  |      |

| V <sub>hys(AVD)</sub>  | AVD voltage threshold hysteresis                                            | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> |                    | 200               |                    | mV   |

| $\Delta V_{IT-}$       | Voltage drop between AVD flag set<br>and LVD reset activated                | V <sub>IT-(AVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 450               |                    | mV   |

1. Data based on characterization results not tested in production.

## **12.5 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

#### 12.5.1 CURRENT CONSUMPTION

| Symbol          | Parameter                                        | Conditions                                                                                                                                                                                                    | Flash Devices             |                              | Unit |

|-----------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------|------|

|                 |                                                  | Conditions                                                                                                                                                                                                    | Тур                       | Max <sup>1)</sup>            | Unit |

|                 | Supply current in RUN mode <sup>2)</sup>         | $\begin{array}{l} f_{OSC}=2MHz, \ f_{CPU}=1MHz\\ f_{OSC}=4MHz, \ f_{CPU}=2MHz\\ f_{OSC}=8MHz, \ f_{CPU}=4MHz\\ f_{OSC}=16MHz, \ f_{CPU}=8MHz \end{array}$                                                     | 1.3<br>2.0<br>3.6<br>7.1  | 3.0<br>5.0<br>8.0<br>15.0    | mA   |

|                 | Supply current in SLOW mode <sup>2)</sup>        | $\begin{array}{l} f_{OSC}{=}2MHz, f_{CPU}{=}62.5 \text{kHz} \\ f_{OSC}{=}4MHz, f_{CPU}{=}125 \text{kHz} \\ f_{OSC}{=}8MHz, f_{CPU}{=}250 \text{kHz} \\ f_{OSC}{=}16MHz, f_{CPU}{=}500 \text{kHz} \end{array}$ | 600<br>700<br>800<br>1100 | 2700<br>3000<br>3600<br>4000 | μA   |

| I <sub>DD</sub> | Supply current in WAIT mode <sup>2)</sup>        | $\begin{array}{l} f_{OSC}{=}2MHz, f_{CPU}{=}1MHz\\ f_{OSC}{=}4MHz, f_{CPU}{=}2MHz\\ f_{OSC}{=}8MHz, f_{CPU}{=}4MHz\\ f_{OSC}{=}16MHz, f_{CPU}{=}8MHz \end{array}$                                             | 1.0<br>1.5<br>2.5<br>4.5  | 3.0<br>4.0<br>5.0<br>7.0     | mA   |

|                 | Supply current in SLOW WAIT mode <sup>2)</sup>   | $\begin{array}{l} f_{OSC}{=}2MHz, f_{CPU}{=}62.5 \text{kHz} \\ f_{OSC}{=}4MHz, f_{CPU}{=}125 \text{kHz} \\ f_{OSC}{=}8MHz, f_{CPU}{=}250 \text{kHz} \\ f_{OSC}{=}16MHz, f_{CPU}{=}500 \text{kHz} \end{array}$ | 580<br>650<br>770<br>1050 | 1200<br>1300<br>1800<br>2000 | μA   |

|                 | Supply current in HALT mode <sup>3)</sup>        | -40°C≤T <sub>A</sub> ≤+85°C                                                                                                                                                                                   | <1                        | 10                           |      |

|                 |                                                  | -40°C≤T <sub>A</sub> ≤+125°C                                                                                                                                                                                  | <1                        | 50                           |      |

| I <sub>DD</sub> | Supply current in ACTIVE-HALT mode <sup>4)</sup> | $\begin{array}{l} f_{OSC} = 2MHz \\ f_{OSC} = 4MHz \\ f_{OSC} = 8MHz \\ f_{OSC} = 16MHz \end{array}$                                                                                                          | 80<br>160<br>325<br>650   | No max.<br>guaran-<br>teed   | μA   |

#### Notes:

1. Data based on characterization results, tested in production at  $V_{DD}$  max. and  $f_{CPU}$  max.

2. Measurements are done in the following conditions:

- Program executed from RAM, CPU running with RAM access. The increase in consumption when executing from Flash is 50%.

- All I/O pins in input mode with a static value at  $V_{\text{DD}}$  or  $V_{\text{SS}}$  (no load)

- All peripherals in reset state.

- LVD disabled.

- Clock input (OSC1) driven by external square wave.

- In SLOW and SLOW WAIT mode,  $f_{\mbox{CPU}}$  is based on  $f_{\mbox{OSC}}$  divided by 32.

- To obtain the total current consumption of the device, add the clock source (Section 12.6.3) and the peripheral power consumption (Section 12.5.3).

- All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load), LVD disabled. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

- 4. Data based on characterisation results, not tested in production. All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load); clock input (OSC1) driven by external square wave, LVD disabled. To obtain the total current consumption of the device, add the clock source consumption (Section 12.6.3).

## **CLOCK CHARACTERISTICS** (Cont'd)

## **12.6.5 PLL Characteristics**

| Symbol                                 | Parameter                              | Conditions                                   | Min | Тур | Max | Unit |

|----------------------------------------|----------------------------------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>OSC</sub>                       | PLL input frequency range              |                                              | 2   |     | 4   | MHz  |

| $\Delta  {\rm f_{CPU}}/ {\rm f_{CPU}}$ | Instantaneous PLL jitter <sup>1)</sup> | Flash ST72F324,<br>f <sub>OSC</sub> = 4 MHz. |     | 1.0 | 2.5 | %    |

|                                        | -                                      | Flash ST72F324,<br>f <sub>OSC</sub> = 2 MHz. |     | 2.5 | 4.0 | 70   |

#### Note:

1. Data characterized but not tested.

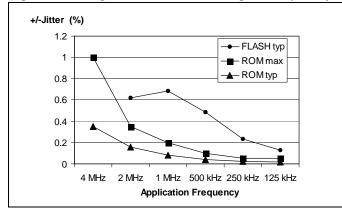

The user must take the PLL jitter into account in the application (for example in serial communication or sampling of high frequency signals). The PLL jitter is a periodic effect, which is integrated over several CPU cycles. Therefore the longer the period of the application signal, the less it will be impacted by the PLL jitter.

Figure 68 shows the PLL jitter integrated on application signals in the range 125kHz to 2MHz. At frequencies of less than 125KHz, the jitter is negligible.

#### Figure 68. Integrated PLL Jitter vs signal frequency<sup>1</sup>

Note 1: Measurement conditions: f<sub>CPU</sub> = 8MHz.

## EMC CHARACTERISTICS (Cont'd)

# 12.8.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### 12.8.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

#### Absolute Maximum Ratings

| Symbol                | Ratings                                                    | Conditions            | Maximum value 1) | Unit |

|-----------------------|------------------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)     | T <sub>A</sub> =+25°C | 2000             |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage<br>(Machine Model)        | T <sub>A</sub> =+25°C | 200              | V    |

| V <sub>ESD(CD)</sub>  | Electro-static discharge voltage<br>(Charged Device Model) | T <sub>A</sub> =+25°C | 250              |      |

#### Notes:

1. Data based on characterization results, not tested in production.

- 12.8.3.2 Static and Dynamic Latch-Up

- LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

- DLU: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

#### **Electrical Sensitivities**

| Symbol | Parameter              | Conditions                                                    | Class <sup>1)</sup> |

|--------|------------------------|---------------------------------------------------------------|---------------------|