Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LQFP                                                                 |

| Supplier Device Package    | · ·                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324j6t6-tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 15.1.7 16-bit Timer PWM Mode 16   15.1.8 SCI Wrong Break duration 16   15.2 FLASH DEVICES ONLY 16 | 1 |

|---------------------------------------------------------------------------------------------------|---|

| 15.2.1 Internal RC Operation 16                                                                   |   |

| 16 IMPORTANT NOTES ON ST72F324B FLASH DEVICES:                                                    | 2 |

| 16.1 RESET PIN LOGIC LEVELS 16                                                                    | 2 |

| 16.2 WAKE-UP FROM ACTIVE HALT MODE USING EXTERNAL INTERRUPTS 16                                   | 2 |

| 16.3 PLL JITTER                                                                                   | 2 |

| 16.4 ACTIVE HALT POWER CONSUMPTION 16                                                             | 2 |

| 16.5 TIMER A REGISTERS 16                                                                         | 2 |

| 17 REVISION HISTORY                                                                               | 3 |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet.

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 159.

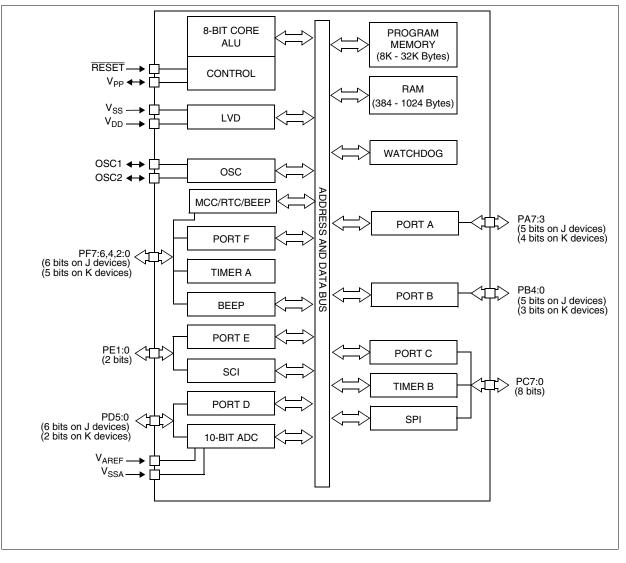

# **1 INTRODUCTION**

The ST72324 devices are members of the ST7 microcontroller family designed for the 5V operating range.

- The 32-pin devices are designed for mid-range applications

- The 42/44-pin devices target the same range of applications requiring more than 24 I/O ports.

For a description of the differences between ST72324 and ST72324B devices refer to Section 14.2 on page 152

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruc-

# Figure 1. Device Block Diagram

57/

tion set and are available with FLASH program memory.

Under software control, all devices can be placed in WAIT, SLOW, ACTIVE-HALT or HALT mode, reducing power consumption when the application is in idle or stand-by state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

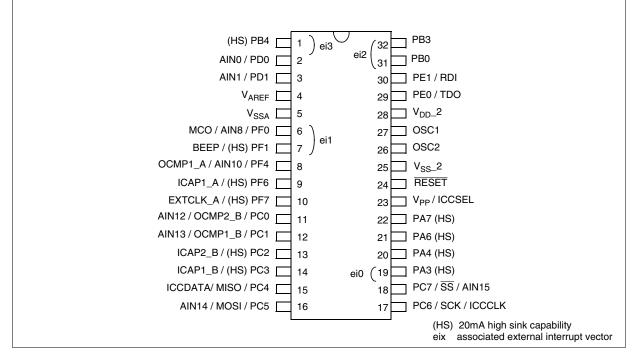

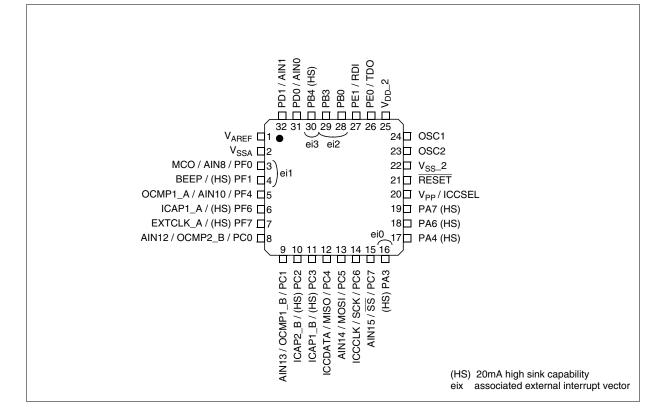

# PIN DESCRIPTION (Cont'd)

# Figure 3. 32-Pin SDIP Package Pinout

Figure 4. 32-Pin TQFP 7x7 Package Pinout

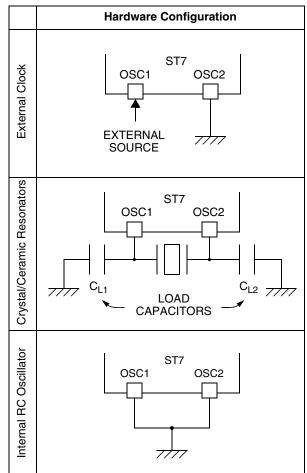

# 6.2 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by three different source types coming from the multi-oscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 5. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

# **External Clock Source**

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

# **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to Section 14.1 on page 150 for more details on the frequency ranges). In this mode of the multioscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

In order not to exceed the max. operating frequency, the internal RC oscillator must not be used with the PLL.

47/

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

# 6.4.3 Low Power Modes

| Mode | Description                                                              |

|------|--------------------------------------------------------------------------|

| WAIT | No effect on SI. AVD interrupt causes the device to exit from Wait mode. |

| HALT | The CRSR register is frozen.                                             |

# 6.4.3.1 Interrupts

57

The AVD interrupt event generates an interrupt if the AVDIE bit is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------|---------------|--------------------------|----------------------|----------------------|

| AVD event       | AVDF          | AVDIE                    | Yes                  | No                   |

# INTERRUPTS (Cont'd)

# 7.3 INTERRUPTS AND LOW POWER MODES

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in Figure 18.

**Note**: If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

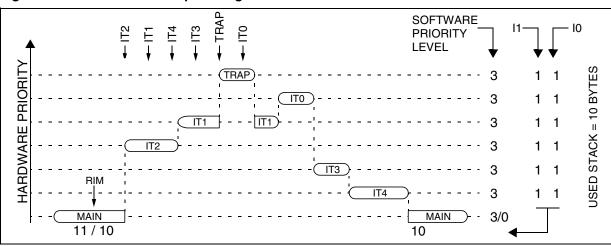

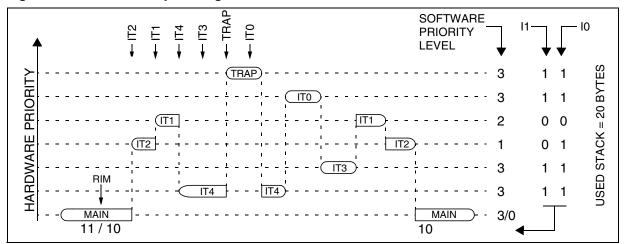

# 7.4 CONCURRENT & NESTED MANAGEMENT

The following Figure 19 and Figure 20 show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in Figure 20. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0. The software priority is given for each interrupt.

**Warning**: A stack overflow may occur without notifying the software of the failure.

#### Figure 19. Concurrent Interrupt Management

Figure 20. Nested Interrupt Management

57/

# I/O PORTS (Cont'd)

# Table 13. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|--------------------------|-----|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h             | PADR                     |     |   |   |   |   |   |   |     |

| 0001h             | PADDR                    | MSB |   |   |   |   |   |   | LSB |

| 0002h             | PAOR                     |     |   |   |   |   |   |   |     |

| 0003h             | PBDR                     |     |   |   |   |   |   |   |     |

| 0004h             | PBDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0005h             | PBOR                     |     |   |   |   |   |   |   |     |

| 0006h             | PCDR                     |     |   |   |   |   |   |   |     |

| 0007h             | PCDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0008h             | PCOR                     |     |   |   |   |   |   |   |     |

| 0009h             | PDDR                     |     |   |   |   |   |   |   |     |

| 000Ah             | PDDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Bh             | PDOR                     |     |   |   |   |   |   |   |     |

| 000Ch             | PEDR                     |     |   |   |   |   |   |   |     |

| 000Dh             | PEDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Eh             | PEOR                     |     |   |   |   |   |   |   |     |

| 000Fh             | PFDR                     |     |   |   |   |   |   |   |     |

| 0010h             | PFDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0011h             | PFOR                     | Ī   |   |   |   |   |   |   |     |

# 16-BIT TIMER (Cont'd)

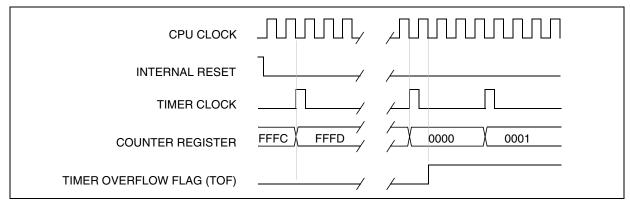

| Figure 36. Counter | <sup>•</sup> Timing Diagram, | , internal o | clock divided b | y 2 |

|--------------------|------------------------------|--------------|-----------------|-----|

|--------------------|------------------------------|--------------|-----------------|-----|

| CPU CLOCK                 |                                                 |

|---------------------------|-------------------------------------------------|

| INTERNAL RESET            |                                                 |

| TIMER CLOCK               |                                                 |

| –<br>COUNTER REGISTER –   | \ FFFD\ FFFE\ FFFF\ 0000 \ 0001 \ 0002 \ 0003 \ |

| TIMER OVERFLOW FLAG (TOF) |                                                 |

# Figure 37. Counter Timing Diagram, internal clock divided by 4

# Figure 38. Counter Timing Diagram, internal clock divided by 8

| CPU CLOCK                 |                |

|---------------------------|----------------|

| INTERNAL RESET            | 1              |

| TIMER CLOCK               | /              |

| COUNTER REGISTER          | FFFC FFFD 0000 |

| TIMER OVERFLOW FLAG (TOF) |                |

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

# 16-BIT TIMER (Cont'd) CONTROL/STATUS REGISTER (CSR)

Read Only (except bit 2 R/W)

Reset Value: xxxx x0xx (xxh)

| 7    |      |     |      |      |      |   | 0 |

|------|------|-----|------|------|------|---|---|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | TIMD | 0 | 0 |

Bit 7 = ICF1 Input Capture Flag 1.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP1 pin or the counter has reached the OC2R value in PWM mode. To clear this bit, first read the SR register, then read or write the low byte of the IC1R (IC1LR) register.

# Bit 6 = OCF1 Output Compare Flag 1.

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the low byte of the OC1R (OC1LR) register.

#### Bit 5 = **TOF** *Timer Overflow Flag.*

0: No timer overflow (reset value).

1: The free running counter rolled over from FFFFh to 0000h. To clear this bit, first read the SR register, then read or write the low byte of the CR (CLR) register.

**Note:** Reading or writing the ACLR register does not clear TOF.

#### Bit 4 = ICF2 Input Capture Flag 2.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the low byte of the IC2R (IC2LR) register.

**Note:** In Flash devices, this bit is not available for Timer A and is forced by hardware to 0.

#### Bit 3 = **OCF2** *Output Compare Flag 2.*

- 0: No match (reset value).

- 1: The content of the free running counter has matched the content of the OC2R register. To clear this bit, first read the SR register, then read or write the low byte of the OC2R (OC2LR) register.

**Note:** In Flash devices, this bit is not available for Timer A and is forced by hardware to 0.

#### Bit 2 = **TIMD** *Timer disable.*

This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.

0: Timer enabled

1: Timer prescaler, counter and outputs disabled

Bits 1:0 = Reserved, must be kept cleared.

# 16-BIT TIMER (Cont'd)

# **INPUT CAPTURE 1 HIGH REGISTER (IC1HR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |   |

|-----|--|--|--|-----|---|

| MSB |  |  |  | LSB | ĺ |

# **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

#### Read Only

**Reset Value: Undefined**

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

57/

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

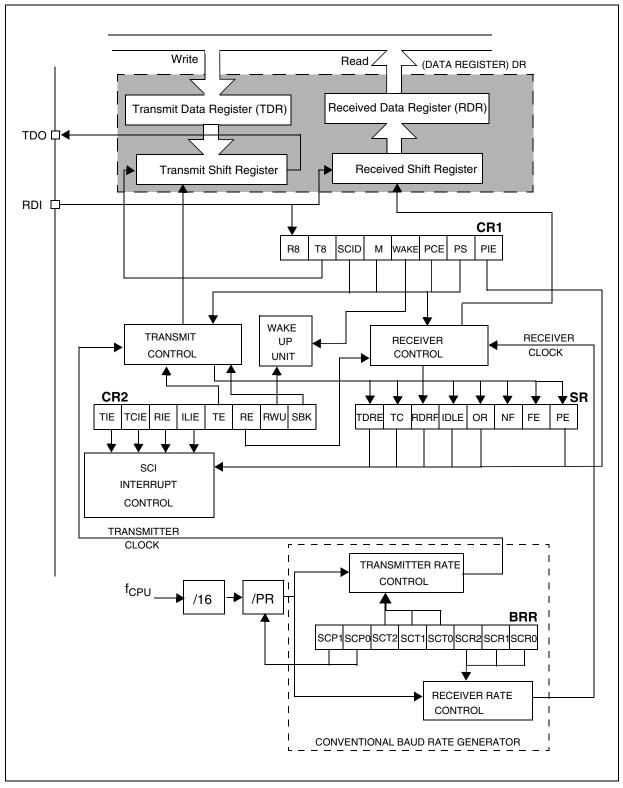

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# Figure 53. SCI Block Diagram

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

# Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE Transmission complete interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

# Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

# Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

# Bit 3 = **TE** *Transmitter enable.*

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

# Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

# Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

# Bit 1 = **RWU** *Receiver wake-up.*

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

# Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

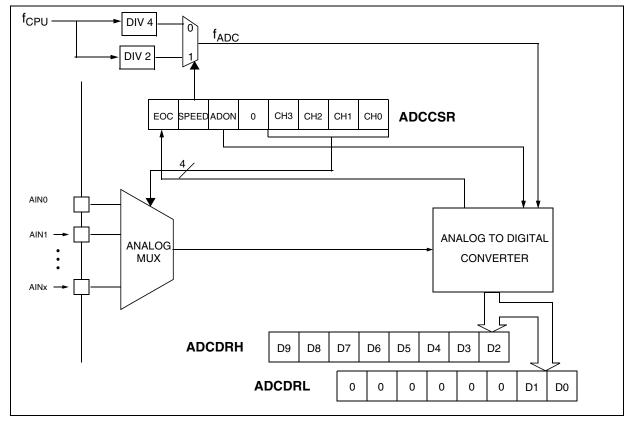

# 10.6 10-BIT A/D CONVERTER (ADC)

# **10.6.1 Introduction**

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 10.6.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

**47**/

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 57.

# Figure 57. ADC Block Diagram

# INSTRUCTION SET OVERVIEW (Cont'd)

| Mnemo | Description            | Function/Example    | Dst     | Src     | 11 | н | 10 | Ν | Ζ | С |

|-------|------------------------|---------------------|---------|---------|----|---|----|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |    |   |    |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |    |   |    | Ν | Ζ |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A |    | 0 |    |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |    |   |    | Ν | Z | С |

| NOP   | No Operation           |                     |         |         |    |   |    |   |   |   |

| OR    | OR operation           | A=A+M               | А       | М       |    |   |    | Ν | Z |   |

| POP   | Don from the Stool     | pop reg             | reg     | М       |    |   |    |   |   |   |

| POP   | Pop from the Stack     | pop CC              | CC      | М       | 11 | н | 10 | Ν | Ζ | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |    |   |    |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |    |   |    |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |    |   |    |   |   |   |

| RIM   | Enable Interrupts      | 11:0 = 10 (level 0) |         |         | 1  |   | 0  |   |   |   |

| RLC   | Rotate left true C     | C <= A <= C         | reg, M  |         |    |   |    | Ν | Ζ | С |

| RRC   | Rotate right true C    | C => A => C         | reg, M  |         |    |   |    | Ν | Ζ | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |    |   |    |   |   |   |

| SBC   | Substract with Carry   | A = A - M - C       | А       | М       |    |   |    | Ν | Ζ | С |

| SCF   | Set carry flag         | C = 1               |         |         |    |   |    |   |   | 1 |

| SIM   | Disable Interrupts     | l1:0 = 11 (level 3) |         |         | 1  |   | 1  |   |   |   |

| SLA   | Shift left Arithmetic  | C <= A <= 0         | reg, M  |         |    |   |    | Ν | Ζ | С |

| SLL   | Shift left Logic       | C <= A <= 0         | reg, M  |         |    |   |    | Ν | Ζ | С |

| SRL   | Shift right Logic      | 0 => A => C         | reg, M  |         |    |   |    | 0 | Z | С |

| SRA   | Shift right Arithmetic | A7 => A => C        | reg, M  |         |    |   |    | Ν | Ζ | С |

| SUB   | Substraction           | A = A - M           | А       | М       |    |   |    | Ν | Z | С |

| SWAP  | SWAP nibbles           | A7-A4 <=> A3-A0     | reg, M  |         |    |   |    | Ν | Ζ |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |    |   |    | Ν | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         | 1  |   | 1  |   |   |   |

| WFI   | Wait for Interrupt     |                     |         |         | 1  |   | 0  |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | А       | М       |    |   | l  | Ν | Ζ |   |

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

# 12.5.2 Supply and Clock Managers

The previous current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode).

| Symbol                 | Parameter                                                     | Conditions           | Тур                                  | Max | Unit |

|------------------------|---------------------------------------------------------------|----------------------|--------------------------------------|-----|------|

| I <sub>DD(RCINT)</sub> | Supply current of internal RC oscillator                      |                      | 625                                  |     |      |

| I <sub>DD(RES)</sub>   | Supply current of resonator oscillator <sup>1) &amp; 2)</sup> |                      | see Section<br>12.6.3 on page<br>125 |     | μA   |

| I <sub>DD(PLL)</sub>   | PLL supply current                                            | V <sub>DD</sub> = 5V | 360                                  |     | μA   |

| I <sub>DD(LVD)</sub>   | LVD supply current                                            | V <sub>DD</sub> = 5V | 150                                  | 300 |      |

#### Notes:

1. Data based on characterization results done with the external components specified in Section 12.6.3, not tested in production.

2. As the oscillator is based on a current source, the consumption does not depend on the voltage.

# EMC CHARACTERISTICS (Cont'd)

# 12.8.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Cymhol           | Parameter  | Conditions                                                              | Device/ Package        | Monitored       | Max vs. [ | fosc/fcpu] | Unit |  |

|------------------|------------|-------------------------------------------------------------------------|------------------------|-----------------|-----------|------------|------|--|

| Symbol Parameter |            | Conditions                                                              | Device/ Package        | Frequency Band  | 8/4MHz    | 16/8MHz    | Unit |  |

|                  |            |                                                                         | 8/16K Flash/<br>TQFP44 | 0.1MHz to 30MHz | 12        | 18         | dBµV |  |

|                  |            |                                                                         |                        | 30MHz to 130MHz | 19        | 25         |      |  |

|                  |            | $V_{DD}$ =5V,<br>T <sub>A</sub> =+25°C<br>conforming to<br>SAE J 1752/3 |                        | 130MHz to 1GHz  | 15        | 22         |      |  |

|                  |            |                                                                         |                        | SAE EMI Level   | 3         | 3.5        | -    |  |

|                  | Peak level |                                                                         | 32K Flash/TQFP44       | 0.1MHz to 30MHz | 20        | 21         | dBμV |  |

| · ·              |            |                                                                         |                        | 30MHz to 130MHz | 26        | 31         |      |  |

| S <sub>EMI</sub> | reak level |                                                                         |                        | 130MHz to 1GHz  | 22        | 28         |      |  |

|                  |            |                                                                         |                        | SAE EMI Level   | 3.5       | 4.0        | -    |  |

|                  |            |                                                                         | Flash/TQFP32           | 0.1MHz to 30MHz | 25        | 27         | dBµV |  |

|                  |            |                                                                         |                        | 30MHz to 130MHz | 30        | 36         |      |  |

|                  |            |                                                                         |                        | 130MHz to 1GHz  | 18        | 23         |      |  |

|                  |            |                                                                         |                        | SAE EMI Level   | 3.0       | 3.5        | -    |  |

Notes:

<u>(</u>ح)

1. Data based on characterization results, not tested in production.

2. Refer to Application Note AN1709 for data on other package types.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 12.9.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                        | Parameter                                                                                                              |     | Conditions                                                         | Min                  | Max        | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|----------------------|------------|------|

| V <sub>OL</sub> <sup>1)</sup> | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 71)                |     | I <sub>IO</sub> =+5mA                                              |                      | 1.2        |      |

|                               |                                                                                                                        |     | I <sub>IO</sub> =+2mA                                              |                      | 0.5        |      |

|                               | Output low level voltage for a high sink I/O pin<br>when 4 pins are sunk at same time<br>(see Figure 72 and Figure 74) | =5V | I <sub>IO</sub> =+20mA, T <sub>A</sub> ≤85°<br>T <sub>A</sub> >85° |                      | 1.3<br>1.5 | V    |

|                               |                                                                                                                        | VDD | I <sub>IO</sub> =+8mA                                              |                      | 0.6        |      |

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time                                          |     | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤85°<br>T <sub>A</sub> >85°  |                      |            |      |

|                               | (see Figure 73 and Figure 76)                                                                                          |     | I <sub>IO</sub> =-2mA                                              | V <sub>DD</sub> -0.7 |            | 1    |

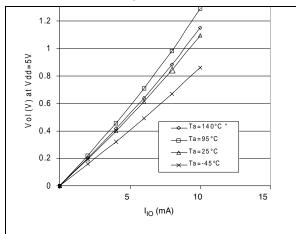

# Figure 71. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (std. ports)

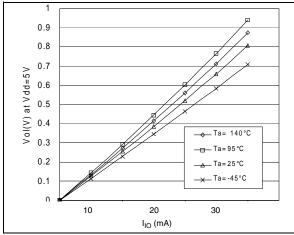

# Figure 72. Typ. V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink ports)

#### Notes:

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins do not have V<sub>OH</sub>.

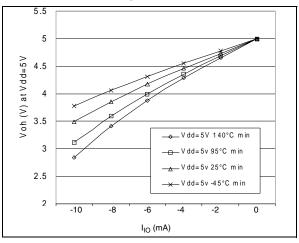

# Figure 73. Typical V<sub>OH</sub> at V<sub>DD</sub>=5V

# **13.2 THERMAL CHARACTERISTICS**

| Symbol            | Ratings                                          | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

|                   | Package thermal resistance (junction to ambient) |       |      |

|                   | TQFP44 10x10                                     | 52    |      |

| R <sub>thJA</sub> | TQFP32 7x7                                       | 70    | °C/W |

|                   | SDIP42 600mil                                    | 55    |      |

|                   | SDIP32 200mil                                    | 50    |      |

| PD                | Power dissipation <sup>1)</sup>                  | 500   | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

#### Notes:

1. The power dissipation is obtained from the formula  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD}xV_{DD}$ ) and  $P_{PORT}$  is the port power dissipation determined by the user.

2. The average chip-junction temperature can be obtained from the formula  $T_J = T_A + P_D x$  RthJA.

# 16 IMPORTANT NOTES ON ST72F324B FLASH DEVICES:

With the objective of continuous improvement, ST has developed new ST72F324B devices. These devices are fully compatible with all ROM features and provide an improved price/performance ratio compared to the ST72F324 flash devices.

A summary of the technical improvements is given below.

Refer to separate ST72324B datasheet for the ordering information and full specifications.

# 16.1 Reset Pin Logic levels

In ST72F324B Flash devices, the  $V_{\text{IH}}/V_{\text{IL}}$  levels for the reset pin are the same as specified for ROM devices

# 16.2 Wake-Up from Active Halt mode using external interrupts

In ST72F324B Flash devices, any external interrupt that capable of waking-up the MCU from Halt mode can also wake-up the MCU from Active Halt mode. Consequently note 1 below Table 8 on page 36 does not apply to 'B' devices.

# 16.3 PLL Jitter

In ST72F324B Flash devices, PLL clock accuracy is improved and the jitter is the same as specified for ROM devices

# **16.4 Active Halt Power Consumption**

In ST72F324B Flash devices, the power consumption in Active Halt mode is specified as 230µA max. See Table 12.5.1 on page 120 for test conditions.

#### 16.5 Timer A Registers

In ST72F324B Flash devices, all Timer A registers are present and their functionality is the same as described for ROM devices in the ST72324B datasheet.