Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324j6tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 2. Hardware Register Map

| Address              | Block                | Register<br>Label | Register Name                                | Reset<br>Status   | Remarks           |

|----------------------|----------------------|-------------------|----------------------------------------------|-------------------|-------------------|

| 0000h                | Port A <sup>2)</sup> | PADR              | Port A Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0001h                |                      | PADDR             | Port A Data Direction Register               | 00h               | R/W               |

| 0002h                |                      | PAOR              | Port A Option Register                       | 00h               | R/W               |

| 0003h                | Port B <sup>2)</sup> | PBDR              | Port B Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0004h                |                      | PBDDR             | Port B Data Direction Register               | 00h               | R/W               |

| 0005h                |                      | PBOR              | Port B Option Register                       | 00h               | R/W               |

| 0006h                | Port C               | PCDR              | Port C Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0007h                |                      | PCDDR             | Port C Data Direction Register               | 00h               | R/W               |

| 0008h                |                      | PCOR              | Port C Option Register                       | 00h               | R/W               |

| 0009h                | Port D <sup>2)</sup> | PDADR             | Port D Data Register                         | 00h <sup>1)</sup> | R/W               |

| 000Ah                |                      | PDDDR             | Port D Data Direction Register               | 00h               | R/W               |

| 000Bh                |                      | PDOR              | Port D Option Register                       | 00h               | R/W               |

| 000Ch                | Port E <sup>2)</sup> | PEDR              | Port E Data Register                         | 00h <sup>1)</sup> | R/W               |

| 000Dh                |                      | PEDDR             | Port E Data Direction Register               | 00h               | R/W <sup>2)</sup> |

| 000Eh                |                      | PEOR              | Port E Option Register                       | 00h               | R/W <sup>2)</sup> |

| 000Fh                | Port F <sup>2)</sup> | PFDR              | Port F Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0010h                |                      | PFDDR             | Port F Data Direction Register               | 00h               | R/W               |

| 0011h                |                      | PFOR              | Port F Option Register                       | 00h               | R/W               |

| 0012h<br>to<br>0020h |                      |                   | Reserved Area (15 Bytes)                     |                   | ·                 |

| 0021h                | SPI                  | SPIDR             | SPI Data I/O Register                        | xxh               | R/W               |

| 0022h                |                      | SPICR             | SPI Control Register                         | 0xh               | R/W               |

| 0023h                |                      | SPICSR            | SPI Control/Status Register                  | 00h               | R/W               |

| 0024h                | ITC                  | ISPR0             | Interrupt Software Priority Register 0       | FFh               | R/W               |

| 0025h                |                      | ISPR1             | Interrupt Software Priority Register 1       | FFh               | R/W               |

| 0026h                |                      | ISPR2             | Interrupt Software Priority Register 2       | FFh               | R/W               |

| 0027h                |                      | ISPR3             | Interrupt Software Priority Register 3       | FFh               | R/W               |

| 0028h                |                      | EICR              | External Interrupt Control Register          | 00h               | R/W               |

| 0029h                | FLASH                | FCSR              | Flash Control/Status Register                | 00h               | R/W               |

| 002Ah                | WATCHDOG             | WDGCR             | Watchdog Control Register                    | 7Fh               | R/W               |

| 002Bh                | SI                   | SICSR             | System Integrity Control Status Register     | xxh               | R/W               |

| 002Ch                | MCC                  | MCCSR             | Main Clock Control / Status Register         | 00h               | R/W               |

| 002Dh                |                      | MCCBCR            | Main Clock Controller: Beep Control Register | 00h               | R/W               |

| 002Eh<br>to<br>0030h |                      |                   | Reserved Area (3 Bytes)                      |                   |                   |

## FLASH PROGRAM MEMORY (Cont'd)

## 4.5 ICP (In-Circuit Programming)

To perform ICP the microcontroller must be switched to ICC (In-Circuit Communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see Figure 7). For more details on the pin locations, refer to the device pinout description.

## 4.6 IAP (In-Application Programming)

This mode uses a BootLoader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored, etc.). For example, it is possible to download code from the SPI, SCI, USB or CAN interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

#### 4.7 Related Documentation

For details on Flash programming and ICC protocol, refer to the ST7 Flash Programming Reference Manual and to the ST7 ICC Protocol Reference Manual.

#### 4.7.1 Register Description

FLASH CONTROL/STATUS REGISTER (FCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

This register is reserved for use by Programming Tool software. It controls the Flash programming and erasing operations.

#### Table 4. Flash Control/Status Register Address and Reset Value

| Address<br>(Hex.) | Register<br>Label   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---------------------|---|---|---|---|---|---|---|---|

| 0029h             | FCSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## CENTRAL PROCESSING UNIT (Cont'd)

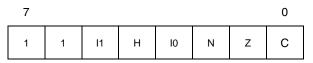

## Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

## Arithmetic Management Bits

## Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

## Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{th}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

## Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

## Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

## **Interrupt Management Bits**

## Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 1 | 10 |

|-------------------------------|---|----|

| Level 0 (main)                | 1 | 0  |

| Level 1                       | 0 | 1  |

| Level 2                       | 0 | 0  |

| Level 3 (= interrupt disable) | 1 | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

## INTERRUPTS (Cont'd)

## 7.3 INTERRUPTS AND LOW POWER MODES

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in Figure 18.

**Note:** If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

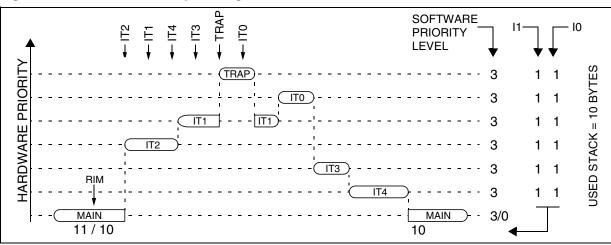

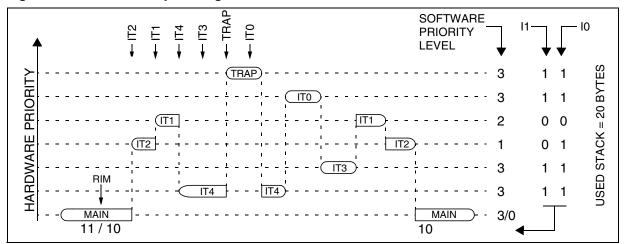

## 7.4 CONCURRENT & NESTED MANAGEMENT

The following Figure 19 and Figure 20 show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in Figure 20. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0. The software priority is given for each interrupt.

**Warning**: A stack overflow may occur without notifying the software of the failure.

#### Figure 19. Concurrent Interrupt Management

Figure 20. Nested Interrupt Management

57/

## INTERRUPTS (Cont'd)

## 7.7 EXTERNAL INTERRUPT CONTROL REGISTER (EICR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |      |      |     |   | 0 |

|------|------|-----|------|------|-----|---|---|

| IS11 | IS10 | IPB | IS21 | IS20 | IPA | 0 | 0 |

Bit 7:6 = **IS1[1:0]** *ei2* and *ei3* sensitivity The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the following external interrupts: - ei2 (port B3..0)

| IS11 | IS10 | External Interrupt Sensitivity |                             |  |  |  |  |

|------|------|--------------------------------|-----------------------------|--|--|--|--|

|      |      | IPB bit =0                     | IPB bit =1                  |  |  |  |  |

| 0    | 0    | Falling edge &<br>low level    | Rising edge<br>& high level |  |  |  |  |

| 0    | 1    | Rising edge only               | Falling edge only           |  |  |  |  |

| 1    | 0    | Falling edge only              | Rising edge only            |  |  |  |  |

| 1    | 1    | Rising and falling edge        |                             |  |  |  |  |

- ei3 (port B4)

| IS11 | IS10 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when 11 and 10 of the CC register are both set to 1 (level 3).

## Bit 5 = **IPB** Interrupt polarity for port B

This bit is used to invert the sensitivity of the port B [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3).

0: No sensitivity inversion

1: Sensitivity inversion

#### Bit 4:3 = **IS2[1:0]** *ei0* and *ei1* sensitivity The interrupt sensitivity, defined using the IS2[1:0] bits, is applied to the following external interrupts:

- ei0 (port A3..0)

| IS21 IS2 | 1820 | External Interrupt Sensitivity |                             |  |  |  |  |

|----------|------|--------------------------------|-----------------------------|--|--|--|--|

|          | 1320 | IPA bit =0                     | IPA bit =1                  |  |  |  |  |

| 0        | 0    | Falling edge &<br>low level    | Rising edge<br>& high level |  |  |  |  |

| 0        | 1    | Rising edge only               | Falling edge only           |  |  |  |  |

| 1        | 0    | Falling edge only              | Rising edge only            |  |  |  |  |

| 1        | 1    | Rising and falling edge        |                             |  |  |  |  |

- ei1 (port F2..0)

| IS21 | IS20 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

## Bit 2 = IPA Interrupt polarity for port A

This bit is used to invert the sensitivity of the port A [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3). 0: No sensitivity inversion

1: Sensitivity inversion

Bits 1:0 = Reserved, must always be kept cleared.

## **8 POWER SAVING MODES**

## **8.1 INTRODUCTION**

To give a large measure of flexibility to the application in terms of power consumption, four main power saving modes are implemented in the ST7 (see Figure 22): SLOW, WAIT (SLOW WAIT), AC-TIVE HALT and HALT.

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

# High RUN SLOW WAIT SLOW WAIT ACTIVE HALT HALT Low POWER CONSUMPTION

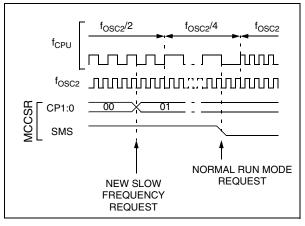

#### 8.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

SLOW mode is controlled by three bits in the MCCSR register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency (f<sub>CPU</sub>).

In this mode, the master clock frequency ( $f_{OSC2}$ ) can be divided by 2, 4, 8 or 16. The CPU and peripherals are clocked at this lower frequency ( $f_{CPU}$ ).

**Note**: SLOW-WAIT mode is activated when entering the WAIT mode while the device is already in SLOW mode.

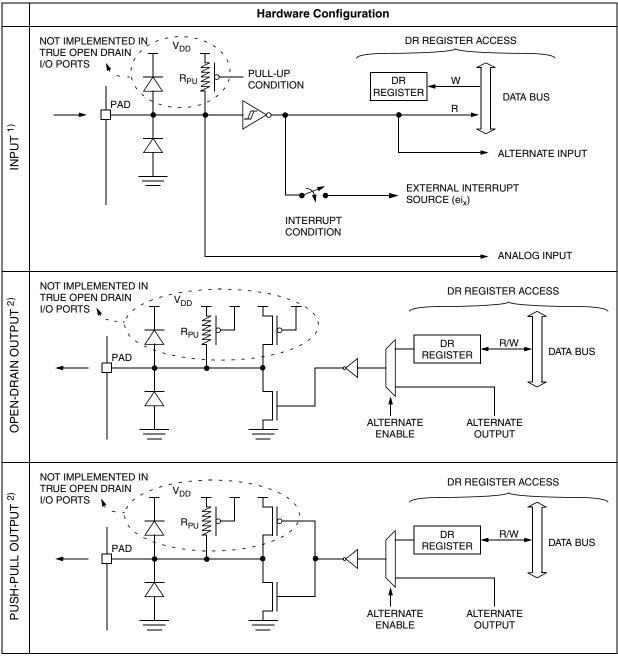

## I/O PORTS (Cont'd)

## Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- 2. When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

## Table 14. Watchdog Timer Register Map and Reset Values

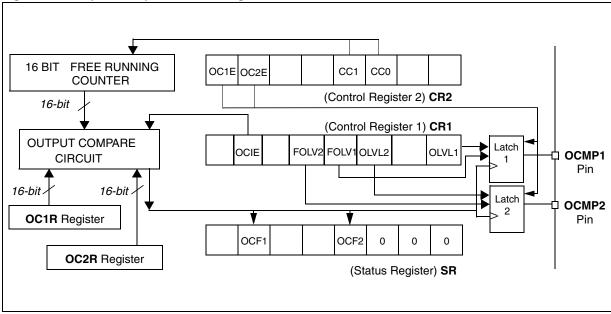

## **10.3 16-BIT TIMER**

## 10.3.1 Introduction

The timer consists of a 16-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU clock prescaler.

Some ST7 devices have two on-chip 16-bit timers. They are completely independent, and do not share any resources. They are synchronized after a MCU reset as long as the timer clock frequencies are not modified.

This description covers one or two 16-bit timers. In ST7 devices with two timers, register names are prefixed with TA (Timer A) or TB (Timer B).

#### 10.3.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4 or 8.

- Overflow status flag and maskable interrupt

- External clock input (must be at least 4 times slower than the CPU clock speed) with the choice of active edge

- 1 or 2 Output Compare functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- 1 or 2 Input Capture functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced Power Mode

- 5 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2, EXTCLK)\*

The Block Diagram is shown in Figure 35.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

#### **10.3.3 Functional Description**

#### 10.3.3.1 Counter

The main block of the Programmable Timer is a 16-bit free running upcounter and its associated 16-bit registers. The 16-bit registers are made up of two 8-bit registers called high & low.

Counter Register (CR):

- Counter High Register (CHR) is the most significant byte (MS Byte).

- Counter Low Register (CLR) is the least significant byte (LS Byte).

Alternate Counter Register (ACR)

- Alternate Counter High Register (ACHR) is the most significant byte (MS Byte).

- Alternate Counter Low Register (ACLR) is the least significant byte (LS Byte).

These two read-only 16-bit registers contain the same value but with the difference that reading the ACLR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR), (see note at the end of paragraph titled 16-bit read sequence).

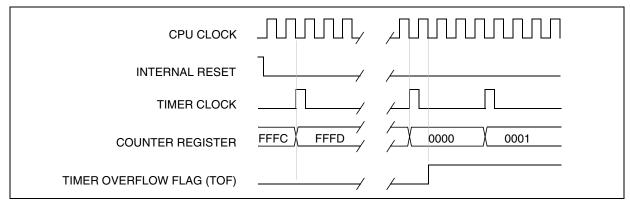

Writing in the CLR register or ACLR register resets the free running counter to the FFFCh value.

Both counters have a reset value of FFFCh (this is the only value which is reloaded in the 16-bit timer). The reset value of both counters is also FFFCh in One Pulse mode and PWM mode.

The timer clock depends on the clock control bits of the CR2 register, as illustrated in Table 16 Clock Control Bits. The value in the counter register repeats every 131072, 262144 or 524288 CPU clock cycles depending on the CC[1:0] bits.

The timer frequency can be  $f_{CPU}/2$ ,  $f_{CPU}/4$ ,  $f_{CPU}/8$  or an external frequency.

**Caution:** In Flash devices, Timer A functionality has the following restrictions:

- TAOC2HR and TAOC2LR registers are write only

- Input Capture 2 is not implemented

- The corresponding interrupts cannot be used (ICF2, OCF2 forced by hardware to zero)

57

## 16-BIT TIMER (Cont'd)

| Figure 36. Counter | <sup>•</sup> Timing Diagram, | , internal o | clock divided b | y 2 |

|--------------------|------------------------------|--------------|-----------------|-----|

|--------------------|------------------------------|--------------|-----------------|-----|

| CPU CLOCK                 |                                                 |

|---------------------------|-------------------------------------------------|

| INTERNAL RESET            |                                                 |

| TIMER CLOCK               |                                                 |

| –<br>COUNTER REGISTER –   | \ FFFD\ FFFE\ FFFF\ 0000 \ 0001 \ 0002 \ 0003 \ |

| TIMER OVERFLOW FLAG (TOF) |                                                 |

## Figure 37. Counter Timing Diagram, internal clock divided by 4

## Figure 38. Counter Timing Diagram, internal clock divided by 8

| CPU CLOCK                 |                |

|---------------------------|----------------|

| INTERNAL RESET            | 1              |

| TIMER CLOCK               | /              |

| COUNTER REGISTER          | FFFC FFFD 0000 |

| TIMER OVERFLOW FLAG (TOF) |                |

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

## 16-BIT TIMER (Cont'd)

## Notes:

- 1. After a processor write cycle to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. If the OC*i*E bit is not set, the OCMP*i* pin is a general I/O port and the OLVL*i* bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- When the timer clock is f<sub>CPU</sub>/2, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value (see Figure 42 on page 67). This behaviour is the same in OPM or PWM mode.

When the timer clock is f<sub>CPU</sub>/4, f<sub>CPU</sub>/8 or in

external clock mode, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value plus 1 (see Figure 43 on page 67).

- 4. The output compare functions can be used both for generating external events on the OCMP*i* pins even if the input capture mode is also used.

- 5. The value in the 16-bit OC*i*R register and the OLV*i* bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

6. In Flash devices, the TAOC2HR, TAOC2LR registers are "write only" in Timer A. The corresponding event cannot be generated (OCF2 is forced by hardware to 0).

## Forced Compare Output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit=1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

## Figure 41. Output Compare Block Diagram

## 16-BIT TIMER (Cont'd)

Table 17. 16-Bit Timer Register Map and Reset Values

| Address<br>(Hex.)        | Register<br>Label | 7    | 6                 | 5    | 4                  | 3                 | 2     | 1                  | 0     |

|--------------------------|-------------------|------|-------------------|------|--------------------|-------------------|-------|--------------------|-------|

| Timer A: 32              | CR1               | ICIE | OCIE              | TOIE | FOLV2 <sup>1</sup> | FOLV1             | OLVL2 | IEDG1              | OLVL1 |

| Timer B: 42              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 31              | CR2               | OC1E | OC2E <sup>1</sup> | OPM  | PWM                | CC1               | CC0   | IEDG2 <sup>1</sup> | EXEDG |

| Timer B: 41              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 33              | CSR               | ICF1 | OCF1              | TOF  | ICF2 <sup>2</sup>  | OCF2 <sup>2</sup> | TIMD  | -                  | -     |

| Timer B: 43              | Reset Value       | х    | х                 | х    | х                  | х                 | 0     | х                  | x     |

| Timer A: 34              | IC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 44              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 35              | IC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 45              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 36              | OC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 46              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 37              | OC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 47              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3E <sup>3</sup> | OC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4E              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3F <sup>3</sup> | OC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4F              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 38              | CHR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 48              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 39              | CLR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 49              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3A              | ACHR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4A              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 3B              | ACLR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4B              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3C <sup>4</sup> | IC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4C              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

| Timer A: 3D <sup>4</sup> | IC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4D              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

<sup>1</sup> In Flash devices, these bits are not used in Timer A and must be kept cleared.

<sup>2</sup> In Flash devices, these bits are forced by hardware to 0 in Timer A

<sup>3</sup> In Flash devices, the TAOC2HR and TAOC2LR Registers are write only, reading them will return undefined values

<sup>4</sup> In Flash devices, the TAIC2HR and TAIC2LR registers are not present.

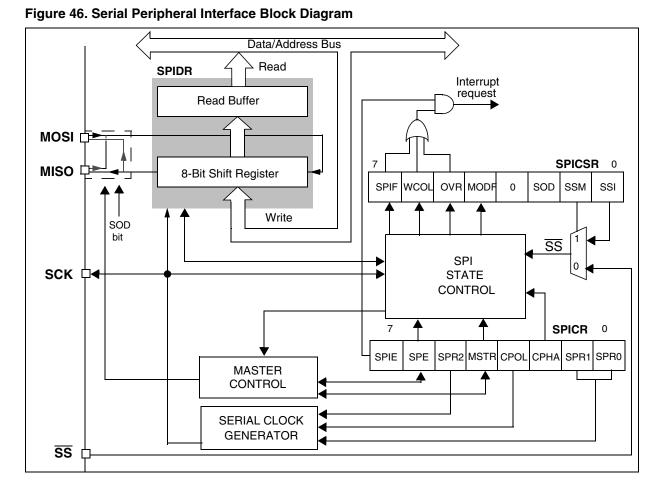

## **10.4 SERIAL PERIPHERAL INTERFACE (SPI)**

## 10.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves however the SPI interface can not be a master in a multi-master system.

## 10.4.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

57/

Write collision, Master Mode Fault and Overrun flags **Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

## 10.4.3 General Description

Figure 46 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 4 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## **10.5.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 1. It contains six dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 0.1.7 for the definitions of each bit.

Figure 54. Word Length Programming

## 10.5.4.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 1.).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

| 9-bit Word length (M bit is set) |

|----------------------------------|

| Data Frame                       |

| Data Frame                                                       |      |      |         |      |      |       |          | Possible<br>Parity<br>Bit |       |              | Next Data Frame |              |

|------------------------------------------------------------------|------|------|---------|------|------|-------|----------|---------------------------|-------|--------------|-----------------|--------------|

| <br>Start<br>Bit                                                 | Bit0 | Bit1 | Bit2    | Bit3 | Bit4 | Bit5  | Bit6     | Bit7                      | Bit8  | Stop<br>Bit  | Start<br>Bit    |              |

| <br>Idle Frame                                                   |      |      |         |      |      |       |          |                           |       | Start<br>Bit |                 |              |

|                                                                  |      | В    | eak Fra | ame  |      |       |          |                           |       |              | Extra           | Start<br>Bit |

| 8-bit Word length (M bit is reset)<br>Data Frame Possible<br>Bit |      |      |         |      |      |       | N        | Next Data Frame<br>Next   |       |              |                 |              |

| <br>Start<br>Bit                                                 | Bit0 | Bit1 | Bit2    | Bit3 | Bit  | 4 Bit | 5 Bit    | t6 Bi                     | t7 Si | top St       | art<br>it       |              |

| <br>Idle Frame                                                   |      |      |         |      |      |       | Sta<br>B |                           |       |              |                 |              |

| <br>Break Frame                                                  |      |      |         |      |      |       | Ex:      |                           |       |              |                 |              |

|                                                                  |      |      |         |      |      |       |          |                           |       |              |                 |              |

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## **Framing Error**

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

- A break is received.

When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

## 10.5.4.4 Conventional Baud Rate Generation

The baud rate for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows:

$$Tx = \frac{f_{CPU}}{(16*PR)*TR} \qquad Rx = \frac{f_{CPU}}{(16*PR)*RR}$$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits) TR = 1, 2, 4, 8, 16, 32, 64,128 (see SCT[2:0] bits) RR = 1, 2, 4, 8, 16, 32, 64,128 (see SCR[2:0] bits)

All these bits are in the SCIBRR register.

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

**Note:** The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

## 10.5.4.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 3.

The output clock rate sent to the transmitter or to the receiver is the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCI-ERPR or the SCIETPR register. **Note:** the extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \cdot ETPR^{*}(PR^{*}TR)} Rx = \frac{f_{CPU}}{16 \cdot ERPR^{*}(PR^{*}RR)}$$

with:

ETPR = 1,..,255 (see SCIETPR register)

ERPR = 1,.. 255 (see SCIERPR register)

## 10.5.4.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non addressed receivers.

The non addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits can not be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

Receiver wakes-up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes-up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

**CAUTION**: In Mute mode, do not write to the SCICR2 register. If the SCI is in Mute mode during the read operation (RWU = 1) and a address mark wake up event occurs (RWU is reset) before the write operation, the RWU bit is set again by this write operation. Consequently the address byte is lost and the SCI is not woken up from Mute mode.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.9 Clock Deviation Causes

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error (Local oscillator error of the transmitter or the transmitter is transmitting at a different baud rate).

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete SCI message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the SCI clock tolerance:

$\mathsf{D}_{\mathsf{TRA}} + \mathsf{D}_{\mathsf{QUANT}} + \mathsf{D}_{\mathsf{REC}} + \mathsf{D}_{\mathsf{TCL}} < 3.75\%$

## 10.5.4.10 Noise Error Causes

See also description of Noise error in Section 0.1.4.3.

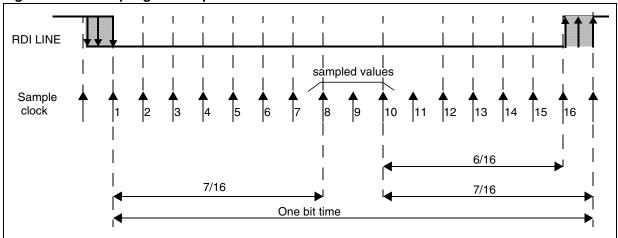

#### Start bit

The noise flag (NF) is set during start bit reception if one of the following conditions occurs:

- 1. A valid falling edge is not detected. A falling edge is considered to be valid if the 3 consecutive samples before the falling edge occurs are detected as '1' and, after the falling edge occurs, during the sampling of the 16 samples, if one of the samples numbered 3, 5 or 7 is detected as a "1".

- 2. During sampling of the 16 samples, if one of the samples numbered 8, 9 or 10 is detected as a "1".

Therefore, a valid Start Bit must satisfy both the above conditions to prevent the Noise Flag getting set.

#### **Data Bits**

The noise flag (NF) is set during normal data bit reception if the following condition occurs:

During the sampling of 16 samples, if all three samples numbered 8, 9 and 10 are not the same. The majority of the 8th, 9th and 10th samples is considered as the bit value.

Therefore, a valid Data Bit must have samples 8, 9 and 10 at the same value to prevent the Noise Flag getting set.

## Figure 56. Bit Sampling in Reception Mode

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

## Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE Transmission complete interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

## Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

## Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

## Bit 3 = **TE** *Transmitter enable.*

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

## Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

## Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

## Bit 1 = **RWU** *Receiver wake-up.*

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

## Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

## I/O PORT PIN CHARACTERISTICS (Cont'd)

57

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

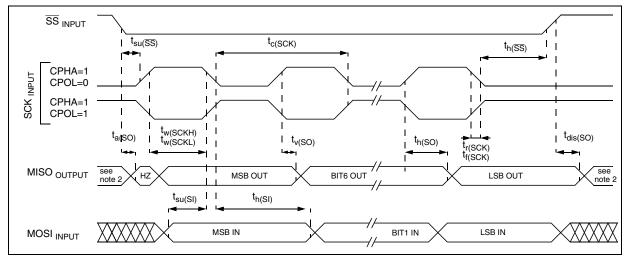

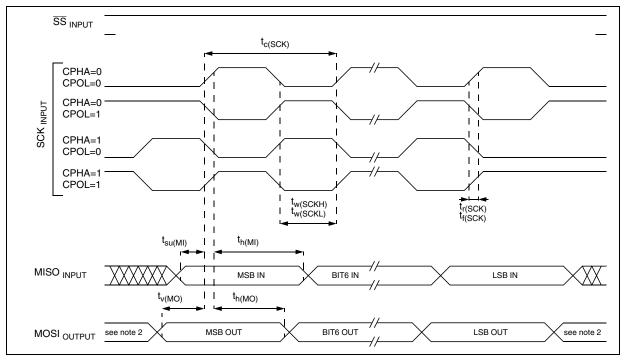

## Figure 81. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

## Figure 82. SPI Master Timing Diagram 1)

#### Notes:

**\$7**

1. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

## ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## **OPTION BYTE 1**

OPT7= **PKG1** *Pin package selection bit* This option bit selects the package.

| Version | Selected Package | PKG1 |

|---------|------------------|------|

| J       | TQFP44 / SDIP42  | 1    |

| К       | TQFP32 / SDIP32  | 0    |

**Note:** On the chip, each I/O port has 8 pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

#### OPT6 = RSTC RESET clock cycle selection

This option bit selects the number of CPU cycles applied during the RESET phase and when exiting HALT mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.

0: Reset phase with 4096 CPU cycles

1: Reset phase with 256 CPU cycles

#### OPT5:4 = OSCTYPE[1:0] Oscillator Type

These option bits select the ST7 main clock source type.

| Clock Source           | OSCTYPE |   |  |  |

|------------------------|---------|---|--|--|

| Clock Source           | 1       | 0 |  |  |

| Resonator Oscillator   | 0       | 0 |  |  |

| Reserved               | 0       | 1 |  |  |

| Internal RC Oscillator | 1       | 0 |  |  |

| External Source        | 1       | 1 |  |  |

#### OPT3:1 = **OSCRANGE[2:0]** Oscillator range

When the resonator oscillator type is selected,

these option bits select the resonator oscillator current source corresponding to the frequency range of the used resonator. Otherwise, these bits are used to select the normal operating frequency range.

| Tur              |         | OSCRANGE |   |   |  |  |  |

|------------------|---------|----------|---|---|--|--|--|

| Typ. Freq. Range |         | 2        | 1 | 0 |  |  |  |

| LP               | 1~2MHz  | 0        | 0 | 0 |  |  |  |

| MP               | 2~4MHz  | 0        | 0 | 1 |  |  |  |

| MS               | 4~8MHz  | 0        | 1 | 0 |  |  |  |

| HS               | 8~16MHz | 0        | 1 | 1 |  |  |  |

#### OPT0 = PLL OFF PLL activation

This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL must not be used with the internal RC oscillator. The PLL is guaranteed only with an input frequency between 2 and 4MHz.

0: PLL x2 enabled 1: PLL x2 disabled

**CAUTION**: the PLL can be enabled only if the "OSC RANGE" (OPT3:1) bits are configured to "MP - 2~4MHz". Otherwise, the device functionality is not guaranteed.