#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                            |

| Supplier Device Package    | •                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k2b6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 15.1.7       16-bit Timer PWM Mode       16         15.1.8       SCI Wrong Break duration       16         15.2       FLASH DEVICES ONLY       16 | 1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 15.2.1 Internal RC Operation 16                                                                                                                   |   |

| 16 IMPORTANT NOTES ON ST72F324B FLASH DEVICES:                                                                                                    | 2 |

| 16.1 RESET PIN LOGIC LEVELS 16                                                                                                                    | 2 |

| 16.2 WAKE-UP FROM ACTIVE HALT MODE USING EXTERNAL INTERRUPTS 16                                                                                   | 2 |

| 16.3 PLL JITTER                                                                                                                                   | 2 |

| 16.4 ACTIVE HALT POWER CONSUMPTION 16                                                                                                             | 2 |

| 16.5 TIMER A REGISTERS 16                                                                                                                         | 2 |

| 17 REVISION HISTORY                                                                                                                               | 3 |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet.

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 159.

57

column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. In the open drain output column, "T" defines a true open drain I/O (P-Buffer and protection diode to  $V_{DD}$  are not implemented). See See "I/O PORTS" on page 45. and Section 12.9 I/O PORT PIN CHARACTER-ISTICS for more details.

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 1 INTRODUCTION and Section 12.6 CLOCK AND TIMING CHARACTERISTICS for more details.

4. On the chip, each I/O port has 8 pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

47/

5. For details refer to Section 12.9.1 on page 133

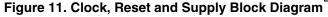

## **6 SUPPLY, RESET AND CLOCK MANAGEMENT**

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components. An overview is shown in Figure 11.

For more details, refer to dedicated parametric section.

## Main features

57/

- Optional PLL for multiplying the frequency by 2 (not to be used with internal RC oscillator in order to respect the max. operating frequency)

- Reset Sequence Manager (RSM)

- Multi-Oscillator Clock Management (MO)

- 5 Crystal/Ceramic resonator oscillators

- 1 Internal RC oscillator

- System Integrity Management (SI)

- Main supply Low voltage detection (LVD)

- Auxiliary Voltage detector (AVD) with interrupt capability for monitoring the main supply

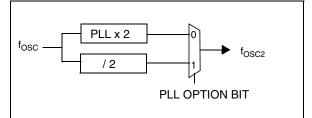

## 6.1 PHASE LOCKED LOOP

If the clock frequency input to the PLL is in the range 2 to 4 MHz, the PLL can be used to multiply the frequency by two to obtain an  $f_{OSC2}$  of 4 to 8 MHz. The PLL is enabled by option byte. If the PLL is disabled, then  $f_{OSC2} = f_{OSC}/2$ .

**Caution:** The PLL is not recommended for applications where timing accuracy is required.

**Caution**: The PLL must not be used with the internal RC oscillator.

#### Figure 10. PLL Block Diagram

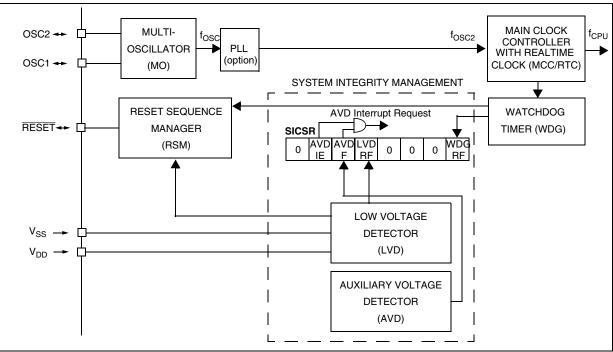

## 6.3 RESET SEQUENCE MANAGER (RSM)

## 6.3.1 Introduction

The reset sequence manager includes three RE-SET sources as shown in Figure 13:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

The basic RESET sequence consists of 3 phases as shown in Figure 12:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

5/

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application.

## Figure 13. Reset Block Diagram

The RESET vector fetch phase duration is 2 clock cycles.

## Figure 12. RESET Sequence Phases

| RESET        |                                            |                 |  |  |  |  |

|--------------|--------------------------------------------|-----------------|--|--|--|--|

| Active Phase | INTERNAL RESET<br>256 or 4096 CLOCK CYCLES | FETCH<br>VECTOR |  |  |  |  |

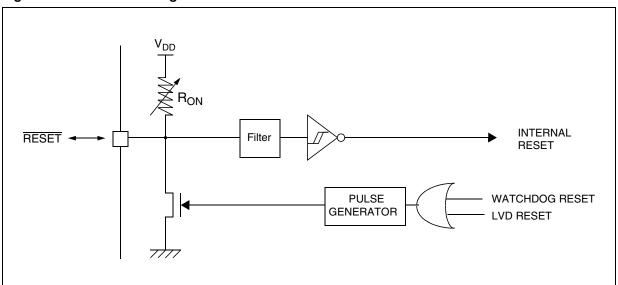

## 6.3.2 Asynchronous External RESET pin

The  $\overline{\text{RESET}}$  pin is both an input and an open-drain output with integrated  $R_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See Electrical Characteristic section for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 14). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

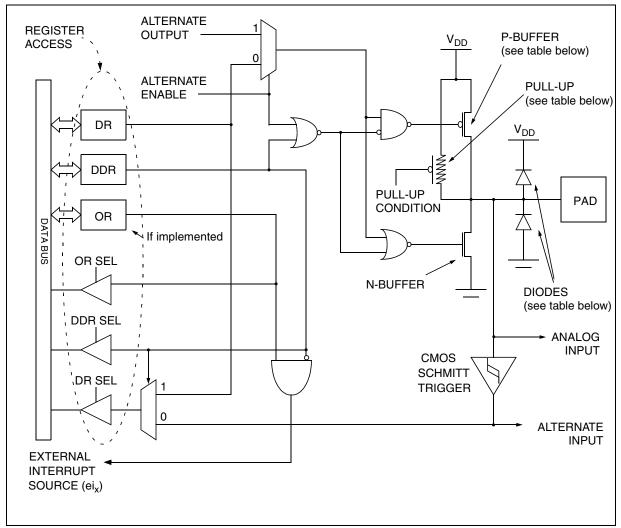

## I/O PORTS (Cont'd)

Table 10. I/O Port Mode Options

| Configuration Mode |                                 | Pull-Up | P-Buffer | Diodes             |                    |  |

|--------------------|---------------------------------|---------|----------|--------------------|--------------------|--|

|                    |                                 | Pull-Op | F-Duilei | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input              | Floating with/without Interrupt | Off Off |          |                    |                    |  |

| Input              | Pull-up with/without Interrupt  | On      |          | On                 |                    |  |

|                    | Push-pull                       | Off     | On       | - On               | On                 |  |

| Output             | Open Drain (logic level)        |         | Off      |                    |                    |  |

|                    | True Open Drain                 | NI      | NI       | NI (see note)      |                    |  |

Legend: NI - not implemented

Off - implemented not activated

On - implemented and activated

**Note**: The diode to  $V_{DD}$  is not implemented in the true open drain pads. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

## I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

## Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

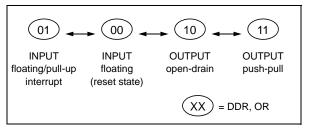

## 9.3 I/O PORT IMPLEMENTATION

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 30 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

## Figure 30. Interrupt I/O Port State Transitions

#### 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

#### 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  | Yes                  |

## MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

## 10.2.5 Low Power Modes

| Mode            | Description                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.<br>MCC/RTC interrupt cause the device to exit<br>from WAIT mode.                                                       |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is<br>set), the registers are frozen.<br>MCC/RTC interrupt cause the device to exit<br>from ACTIVE-HALT mode.     |

| HALT            | MCC/RTC counter and registers are frozen.<br>MCC/RTC operation resumes when the<br>MCU is woken up by an interrupt with "exit<br>from HALT" capability. |

## 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

## Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

## 10.2.7 Register Description MCC CONTROL/STATUS REGISTER (MCCSR) Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| мсо | CP1 | CP0 | SMS | TB1 | TB0 | OIE | OIF |  |

Bit 7 = **MCO** *Main clock out selection*

This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.

- 0: MCO alternate function disabled (I/O pin free for general-purpose I/O)

- 1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

**Note**: To reduce power consumption, the MCO function is not active in ACTIVE-HALT mode.

Bit 6:5 = **CP[1:0]** CPU clock prescaler

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC2</sub> / 2         | 0   | 0   |

| f <sub>OSC2</sub> / 4         | 0   | 1   |

| f <sub>OSC2</sub> / 8         | 1   | 0   |

| f <sub>OSC2</sub> / 16        | 1   | 1   |

## Bit 4 = **SMS** *Slow mode select*

This bit is set and cleared by software. 0: Normal mode.  $f_{CPU} = f_{OSC2}$ 1: Slow mode.  $f_{CPU}$  is given by CP1, CP0 See Section 8.2 SLOW MODE and Section 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) for more details.

## Bit 3:2 = **TB[1:0]** *Time base control*

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                    | TB1                     | тво |     |

|-----------|-------------------------|-------------------------|-----|-----|

| Prescaler | f <sub>OSC2</sub> =4MHz | f <sub>OSC2</sub> =8MHz | 101 | 100 |

| 16000     | 4ms                     | 2ms                     | 0   | 0   |

| 32000     | 8ms                     | 4ms                     | 0   | 1   |

| 80000     | 20ms                    | 10ms                    | 1   | 0   |

| 200000    | 50ms                    | 25ms                    | 1   | 1   |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

Bit 1 = **OIE** Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disabled

1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode.

57

## **16-BIT TIMER** (Cont'd)

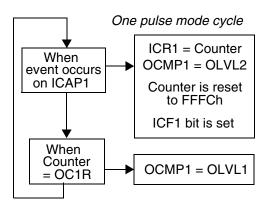

## 10.3.3.5 One Pulse Mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The one pulse mode uses the Input Capture1 function and the Output Compare1 function.

## Procedure:

To use one pulse mode:

- 1. Load the OC1R register with the value corresponding to the length of the pulse (see the formula in the opposite column).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit.

- Select the timer clock CC[1:0] (see Table 16 Clock Control Bits).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the Input Capture interrupt request (i.e. clearing the ICF*i* bit) is done in two steps:

1. Reading the SR register while the ICF*i* bit is set.

2. An access (read or write) to the ICiLR register.

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OCiR Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits, see Table 16 Clock Control Bits)

If the timer clock is an external clock the formula is:

$$OC_{iR} = t * f_{EXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin, (See Figure 44).

#### Notes:

- 1. The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2. When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3. If OLVL1=OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4. The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5. When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

- 6. In Flash devices, Timer A OCF2 bit is forced by hardware to 0.

## **16-BIT TIMER** (Cont'd)

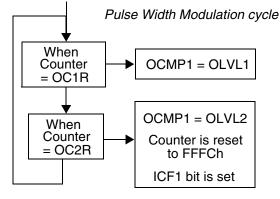

## 10.3.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### Procedure

To use pulse width modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1=0 and OLVL2=1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 16 Clock Control Bits).

If OLVL1=1 and OLVL2=0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1=OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OC/R Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

$f_{CPU} = CPU \operatorname{clock} \operatorname{frequency} (\operatorname{in} \operatorname{hertz})$

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 16)

If the timer clock is an external clock the formula is:

$$OC_{i}R = t * f_{FXT} - 5$$

Where:

t

= Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 45)

#### Notes:

- 1. After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5. When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 6. In Flash devices, the TAOC2HR, TAOC2LR registers in Timer A are "write only". A read operation returns an undefined value.

7. In Flash devices, the ICAP2 registers (TAIC2HR, TAIC2LR) are not available in Timer A. The ICF2 bit is forced by hardware to 0.

## 16-BIT TIMER (Cont'd) CONTROL/STATUS REGISTER (CSR)

Read Only (except bit 2 R/W)

Reset Value: xxxx x0xx (xxh)

| 7    |      |     |      |      |      |   | 0 |

|------|------|-----|------|------|------|---|---|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | TIMD | 0 | 0 |

Bit 7 = ICF1 Input Capture Flag 1.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP1 pin or the counter has reached the OC2R value in PWM mode. To clear this bit, first read the SR register, then read or write the low byte of the IC1R (IC1LR) register.

## Bit 6 = OCF1 Output Compare Flag 1.

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the low byte of the OC1R (OC1LR) register.

#### Bit 5 = **TOF** Timer Overflow Flag.

0: No timer overflow (reset value).

1: The free running counter rolled over from FFFFh to 0000h. To clear this bit, first read the SR register, then read or write the low byte of the CR (CLR) register.

**Note:** Reading or writing the ACLR register does not clear TOF.

#### Bit 4 = ICF2 Input Capture Flag 2.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the low byte of the IC2R (IC2LR) register.

**Note:** In Flash devices, this bit is not available for Timer A and is forced by hardware to 0.

#### Bit 3 = **OCF2** *Output Compare Flag 2.*

- 0: No match (reset value).

- 1: The content of the free running counter has matched the content of the OC2R register. To clear this bit, first read the SR register, then read or write the low byte of the OC2R (OC2LR) register.

**Note:** In Flash devices, this bit is not available for Timer A and is forced by hardware to 0.

#### Bit 2 = TIMD Timer disable.

This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.

0: Timer enabled

1: Timer prescaler, counter and outputs disabled

Bits 1:0 = Reserved, must be kept cleared.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

## 10.4.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

To operate the SPI in master mode, perform the following steps in order (if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account):

1. Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 50 shows the four possible configurations.

Note: The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

<u>Note</u>: MSTR and SPE bits remain set only if SS is high).

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.4.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.4.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 50).

Note: The slave must have the same CPOL and CPHA settings as the master.

- Manage the SS pin as described in Section 10.4.3.2 and Figure 48. If CPHA=1 SS must be held low continuously. If CPHA=0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.4.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

1. An access to the SPICSR register while the SPIF bit is set.

2. A write or a read to the SPIDR register.

**Notes:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.4.5.2).

47/

## SERIAL PERIPHERAL INTERFACE (Cont'd)

## 10.4.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up by<br>an interrupt with "exit from HALT mode" ca-<br>pability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 10.4.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware. **Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 10.4.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

## 10.4.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Transfer<br>Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode Fault<br>Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in

## **10.5 SERIAL COMMUNICATIONS INTERFACE (SCI)**

## 10.5.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 10.5.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

### **10.5.3 General Description**

The interface is externally connected to another device by two pins (see Figure 2.):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## **10.5.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 1. It contains six dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 0.1.7 for the definitions of each bit.

## 10.5.4.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 1.).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

| 9<br> | 9-bit V      | Vord I | <b>ength</b><br>D   | <b>(M bit</b><br>Pata Fra   |       | t)     |      |      | Possible<br>Parity<br>Bit |              |             | Next Data Frame<br>Next |

|-------|--------------|--------|---------------------|-----------------------------|-------|--------|------|------|---------------------------|--------------|-------------|-------------------------|

|       | Start<br>Bit | Bit0   | Bit1                | Bit2                        | Bit3  | Bit4   | Bit5 | Bit6 | Bit7                      | Bit8         | Stop<br>Bit | Start<br>Bit            |

|       |              |        | lo                  | lle Fra                     | me    |        |      |      |                           |              |             | Start<br>Bit            |

|       |              |        | В                   | reak F                      | rame  |        |      |      |                           |              |             | Extra Start<br>'1' Bit  |

|       | 8-bit        |        | <b>i lengi</b><br>D | i <b>h (M k</b><br>Pata Fra |       | eset)  |      |      | Possi<br>Par<br>Bi        | ity<br>t     | Ne          | Next Data Frame         |

|       | Bit          | Bit    | 0 Bit               | 1 Bit2                      | 2 Bit | 3 Bit4 | Bit5 | Bit  | 6 Bit                     | t7 Sto<br>Bi |             | t                       |

|       | Idle Frame   |        |                     |                             |       |        |      |      |                           | Sta<br>Bi    |             |                         |

|       |              |        | В                   | reak F                      | rame  |        |      |      |                           |              | Ext<br>'1   | ra Start<br>Bit         |

|       |              |        |                     |                             |       |        |      |      |                           |              | I           | <u> </u>                |

## Figure 54. Word Length Programming

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

## **10.6.6 Register Description**

## **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   |       |      |   |     |     |     | 0   |

|-----|-------|------|---|-----|-----|-----|-----|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by hardware when software reads the ADCDRH register or writes to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = **SPEED** ADC clock selection This bit is set and cleared by software. 0:  $f_{ADC} = f_{CPU}/4$ 1:  $f_{ADC} = f_{CPU}/2$

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **Reserved.** Must be kept cleared.

## Bit 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 1   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

\*The number of channels is device dependent. Refer to the device pinout description.

## **DATA REGISTER (ADCDRH)**

Read Only Reset Value: 0000 0000 (00h)

7

|    |    | l. | l. | l. | r. | r. | r. |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

|    |    |    |    |    |    |    |    |

0

Bit 7:0 = D[9:2] MSB of Converted Analog Value

## DATA REGISTER (ADCDRL)

Read Only Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 = Reserved. Forced by hardware to 0.

Bit 1:0 = **D**[1:0] *LSB of Converted Analog Value*

## INSTRUCTION SET OVERVIEW (Cont'd)

## 11.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

## Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

## Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table25. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressing ModesIndirectIndexedIndirect

| Long and Short<br>Instructions | Function                                           |

|--------------------------------|----------------------------------------------------|

| LD                             | Load                                               |

| CP                             | Compare                                            |

| AND, OR, XOR                   | Logical Operations                                 |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Sub-<br>stractions operations |

| BCP                            | Bit Compare                                        |

| Short Instructions<br>Only | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Opera-<br>tions  |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

## 11.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset is following the opcode.

#### Relative (Indirect)

The offset is defined in memory, which address follows the opcode.

## INSTRUCTION SET OVERVIEW (Cont'd)

## **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | СР   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a pre-byte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC opcode

57

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

## **12.10 CONTROL PIN CHARACTERISTICS**

## 12.10.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                              | Cor                 | ditions               | Min                              | Тур | Max                              | Unit |

|-------------------------|----------------------------------------|---------------------|-----------------------|----------------------------------|-----|----------------------------------|------|

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 2)  |                     |                       |                                  | 2.5 |                                  | V    |

| V <sub>IL</sub>         | Input low level voltage 1)             |                     |                       |                                  |     | $0.16 \mathrm{xV}_{\mathrm{DD}}$ | V    |

| V <sub>IH</sub>         | Input high level voltage 1)            |                     |                       | $0.85 \mathrm{xV}_{\mathrm{DD}}$ |     |                                  | v    |

| V <sub>OL</sub>         | Output low level voltage 3)            | V <sub>DD</sub> =5V | I <sub>IO</sub> =+2mA |                                  | 0.2 | 0.5                              | V    |

| I <sub>IO</sub>         | Driving current on RESET pin           |                     |                       |                                  | 2   |                                  | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor       | V <sub>DD</sub> =5V |                       | 20                               | 30  | 120                              | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration         | Internal re         | eset sources          | 20                               | 30  | 42 <sup>6)</sup>                 | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)      |                     |                       | 2.5                              |     |                                  | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup> |                     |                       |                                  | 200 |                                  | ns   |

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overline{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

6. Data guaranteed by design, not tested in production.

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

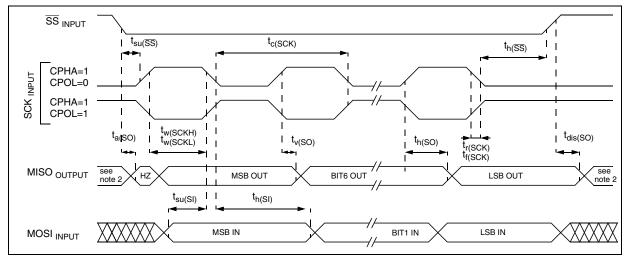

## Figure 81. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

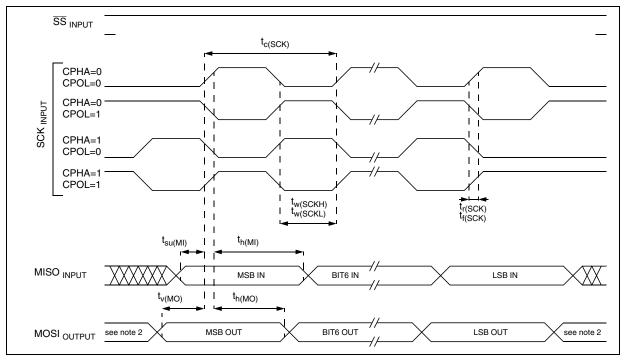

## Figure 82. SPI Master Timing Diagram 1)

#### Notes:

**\$7**

1. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

## **12.13 10-BIT ADC CHARACTERISTICS**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                                        | Conditions                                              | Min              | Тур     | Max                            | Unit               |

|-------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|---------|--------------------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                              |                                                         | 0.4              |         | 2                              | MHz                |

| V <sub>AREF</sub> | Analog reference voltage                                                                         | 0.7*V <sub>DD</sub> ≤V <sub>AREF</sub> ≤V <sub>DD</sub> | 3.8              |         | V <sub>DD</sub>                | V                  |

| V <sub>AIN</sub>  | Conversion voltage range 1)                                                                      |                                                         | V <sub>SSA</sub> |         | V <sub>AREF</sub>              | v                  |

| l <sub>lkg</sub>  | Positive input leakage current for analog input <sup>2)</sup>                                    | -40°C≤T <sub>A</sub> ≤+85°C                             |                  |         | ±250                           | nA                 |

|                   |                                                                                                  | +85°C≤T <sub>A</sub> ≤+125°C                            |                  |         | ±1                             | μA                 |

| R <sub>AIN</sub>  | External input impedance                                                                         |                                                         |                  |         | see                            | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                               |                                                         |                  |         | Figure 83<br>and               | pF                 |

| f <sub>AIN</sub>  | Variation freq. of analog input signal                                                           |                                                         |                  |         | Figure<br>84 <sup>2)3)4)</sup> | Hz                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                               |                                                         |                  | 12      |                                | pF                 |

| t <sub>ADC</sub>  | Conversion time (Sample+Hold)<br>f <sub>CPU</sub> =8MHz, SPEED=0 f <sub>ADC</sub> =2MHz          |                                                         |                  | 7.5     |                                | μs                 |

| t <sub>ADC</sub>  | <ul> <li>No of sample capacitor loading cycles</li> <li>No. of Hold conversion cycles</li> </ul> |                                                         |                  | 4<br>11 |                                | 1/f <sub>ADC</sub> |

#### Notes:

1. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

2.For Flash devices: injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input. Analog pins of ST72F324 devices can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.9 does not affect the ADC accuracy.