Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k2ta |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 2 PIN C | ODUCTION                                                                               | 8  |

|---------|----------------------------------------------------------------------------------------|----|

|         | ISTER & MEMORY MAP                                                                     |    |

| 4 FLAS  | SH PROGRAM MEMORY                                                                      |    |

| 4.1     |                                                                                        | 17 |

| 4.2     | MAIN FEATURES                                                                          | 17 |

| 4.3     | STRUCTURE                                                                              | 17 |

|         | 4.3.1 Read-out Protection                                                              | 17 |

| 4.4     | ICC INTERFACE                                                                          | -  |

| 4.5     | ICP (IN-CIRCUIT PROGRAMMING)                                                           | 19 |

| 4.6     | IAP (IN-APPLICATION PROGRAMMING)                                                       | 19 |

| 4.7     | RELATED DOCUMENTATION                                                                  | 19 |

|         | 4.7.1 Register Description                                                             | 19 |

| 5 CEN   |                                                                                        |    |

| 5.1     |                                                                                        | 20 |

| 5.2     | MAIN FEATURES                                                                          | 20 |

| 5.3     | CPU REGISTERS                                                                          | 20 |

| 6 SUPF  | PLY, RESET AND CLOCK MANAGEMENT                                                        |    |

| 6.1     | PHASE LOCKED LOOP                                                                      |    |

| 6.2     | MULTI-OSCILLATOR (MO)                                                                  | 24 |

| 6.3     | RESET SEQUENCE MANAGER (RSM)                                                           |    |

|         | 6.3.1 Introduction                                                                     |    |

|         | 6.3.2 Asynchronous External RESET pin                                                  |    |

|         | 6.3.3 External Power-On RESET                                                          | 26 |

|         | 6.3.4 Internal Low Voltage Detector (LVD) RESET                                        |    |

| ~ /     | 6.3.5 Internal Watchdog RESET                                                          |    |

| 6.4     | SYSTEM INTEGRITY MANAGEMENT (SI)                                                       |    |

|         | 6.4.1 Low Voltage Detector (LVD)                                                       |    |

|         | <ul><li>6.4.2 Auxiliary Voltage Detector (AVD)</li><li>6.4.3 Low Power Modes</li></ul> |    |

|         | 6.4.3       Low Power Modes         6.4.4       Register Description                   |    |

| 7 INTE  | RRUPTS                                                                                 |    |

| 7.1     | INTRODUCTION                                                                           |    |

| 7.2     | MASKING AND PROCESSING FLOW                                                            |    |

| 7.3     | INTERRUPTS AND LOW POWER MODES                                                         |    |

| 7.4     | CONCURRENT & NESTED MANAGEMENT                                                         |    |

| 7.5     |                                                                                        |    |

| 7.6     | EXTERNAL INTERRUPTS                                                                    |    |

| 0.1     |                                                                                        |    |

| 7.7     | 7.6.1 I/O Port Interrupt Sensitivity                                                   |    |

|         | ER SAVING MODES                                                                        |    |

| 8.1     | INTRODUCTION                                                                           |    |

| 8.2     | SLOW MODE                                                                              |    |

| • • •   |                                                                                        |    |

| 8.3     | WAIT MODE                                                                              | 41 |

# **Table of Contents**

| 15.1.7       16-bit Timer PWM Mode       16         15.1.8       SCI Wrong Break duration       16         15.2       FLASH DEVICES ONLY       16 | 1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 15.2.1 Internal RC Operation 16                                                                                                                   |   |

| 16 IMPORTANT NOTES ON ST72F324B FLASH DEVICES:                                                                                                    | 2 |

| 16.1 RESET PIN LOGIC LEVELS 16                                                                                                                    | 2 |

| 16.2 WAKE-UP FROM ACTIVE HALT MODE USING EXTERNAL INTERRUPTS 16                                                                                   | 2 |

| 16.3 PLL JITTER                                                                                                                                   | 2 |

| 16.4 ACTIVE HALT POWER CONSUMPTION 16                                                                                                             | 2 |

| 16.5 TIMER A REGISTERS 16                                                                                                                         | 2 |

| 17 REVISION HISTORY                                                                                                                               | 3 |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet.

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 159.

57

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 6.4.4 Register Description

## SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 000x 000x (00h)

| 7 |           |          |           |   |   |   | 0         |

|---|-----------|----------|-----------|---|---|---|-----------|

| 0 | AVD<br>IE | AVD<br>F | LVD<br>RF | 0 | 0 | 0 | WDG<br>RF |

Bit 7 = Reserved, must be kept cleared.

Bit 6 = **AVDIE** Voltage Detector interrupt enable This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 16 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  over  $V_{IT+(AVD)}$  threshold

1: V<sub>DD</sub> under V<sub>IT-(AVD)</sub> threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined. Bits 3:1 = Reserved, must be kept cleared.

#### Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

#### Application notes

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

# MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

#### Bit 0 = **OIF** Oscillator interrupt flag

This bit is set by hardware and cleared by software reading the MCCSR register. It indicates when set that the main oscillator has reached the selected elapsed time (TB1:0).

0: Timeout not reached

1: Timeout reached

**CAUTION**: The BRES and BSET instructions must not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.

# MCC BEEP CONTROL REGISTER (MCCBCR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | BC1 | BC0 |

Bit 7:2 = Reserved, must be kept cleared.

#### Bit 1:0 = **BC[1:0]** Beep control

These 2 bits select the PF1 pin beep capability.

| BC1 | BC0 | Beep mode with f <sub>OSC2</sub> =8MHz |                 |  |  |  |  |  |

|-----|-----|----------------------------------------|-----------------|--|--|--|--|--|

| 0   | 0   | Off                                    |                 |  |  |  |  |  |

| 0   | 1   | ~2-KHz                                 | Output          |  |  |  |  |  |

| 1   | 0   | ~1-KHz                                 | Beep signal     |  |  |  |  |  |

| 1   | 1   | ~500-Hz                                | ~50% duty cycle |  |  |  |  |  |

The beep output signal is available in ACTIVE-HALT mode but has to be disabled to reduce the consumption.

47/

#### Table 15. Main Clock Controller Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7   | 6     | 5    | 4     | 3   | 2   | 1   | 0     |

|-------------------|-------------------|-----|-------|------|-------|-----|-----|-----|-------|

| 002Bh             | SICSR             |     | AVDIE | AVDF | LVDRF |     |     |     | WDGRF |

| 002Bn             | Reset Value       | 0   | 0     | 0    | х     | 0   | 0   | 0   | х     |

| 002Ch             | MCCSR             | MCO | CP1   | CP0  | SMS   | TB1 | TB0 | OIE | OIF   |

| 002Ch             | Reset Value       | 0   | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

| 002Dh             | MCCBCR            |     |       |      |       |     |     | BC1 | BC0   |

|                   | Reset Value       | 0   | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

# SERIAL PERIPHERAL INTERFACE (Cont'd)

### 10.4.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

To operate the SPI in master mode, perform the following steps in order (if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account):

1. Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 50 shows the four possible configurations.

Note: The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

<u>Note</u>: MSTR and SPE bits remain set only if SS is high).

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.4.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.4.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 50).

Note: The slave must have the same CPOL and CPHA settings as the master.

- Manage the SS pin as described in Section 10.4.3.2 and Figure 48. If CPHA=1 SS must be held low continuously. If CPHA=0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.4.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

1. An access to the SPICSR register while the SPIF bit is set.

2. A write or a read to the SPIDR register.

**Notes:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.4.5.2).

# SERIAL PERIPHERAL INTERFACE (Cont'd)

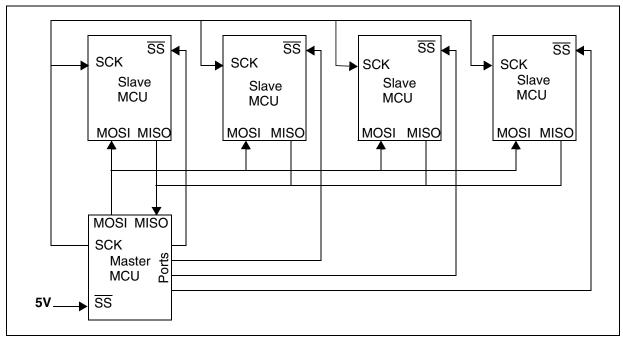

## 10.4.5.4 Single Master Systems

57/

A typical single master system may be configured, using an MCU as the master and four MCUs as slaves (see Figure 52).

The master device selects the individual slave devices by using four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## **10.5.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 1. It contains six dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 0.1.7 for the definitions of each bit.

## 10.5.4.1 Serial Data Format

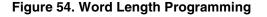

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 1.).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

| 9-bit V                                                                   | 9-bit Word length (M bit is set)<br>Data Frame |       |         |      |      |       |       |      |               | 9           | Next Data Frame        |  |  |

|---------------------------------------------------------------------------|------------------------------------------------|-------|---------|------|------|-------|-------|------|---------------|-------------|------------------------|--|--|

| <br>Start                                                                 |                                                |       |         |      |      |       |       |      | Bit           | Ctor        | Next<br>Start          |  |  |

| Bit                                                                       | Bit0                                           | Bit1  | Bit2    | Bit3 | Bit4 | Bit5  | Bit6  | Bit7 | Bit8          | Stop<br>Bit | Bit                    |  |  |

|                                                                           | Idle Frame                                     |       |         |      |      |       |       |      |               |             | Start<br>Bit           |  |  |

| <br>1                                                                     |                                                | В     | reak Fi | rame |      |       |       |      |               |             | Extra Start<br>'1' Bit |  |  |

| <br><b>8-bit Word length (M bit is reset)</b><br>Data Frame Parity<br>Bit |                                                |       |         |      |      |       |       |      | Ne            |             |                        |  |  |

| Sta<br>Bit                                                                | Bit                                            | 0 Bit | Bit2    | Bit3 | Bit  | 4 Bit | 5 Bit | 6 Bi | t7 Sto<br>Bit |             | art<br>t               |  |  |

|                                                                           | Idle Frame                                     |       |         |      |      |       |       |      |               | Sta<br>Bi   |                        |  |  |

|                                                                           | Break Frame                                    |       |         |      |      |       |       |      |               | Ext         | ra Start<br>Bit        |  |  |

|                                                                           |                                                |       |         |      |      |       |       |      |               |             | <u> </u>               |  |  |

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# 10.5.5 Low Power Modes

47/

| Mode | Description                                                                        |

|------|------------------------------------------------------------------------------------|

|      | No effect on SCI.                                                                  |

| WAIT | SCI interrupts cause the device to exit from Wait mode.                            |

|      | SCI registers are frozen.                                                          |

| HALT | In Halt mode, the SCI stops transmitting/re-<br>ceiving until Halt mode is exited. |

#### 10.5.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event                 | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|---------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty | TDRE          | TIE                      | Yes                  | No                   |

| Transmission Com-<br>plete      | тс            | TCIE                     | Yes                  | No                   |

| Received Data Ready to be Read  | RDRF          | RIE                      | Yes                  | No                   |

| Overrun Error Detect-<br>ed     | OR            | TUL                      | Yes                  | No                   |

| Idle Line Detected              | IDLE          | ILIE                     | Yes                  | No                   |

| Parity Error                    | PE            | PIE                      | Yes                  | No                   |

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

## Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

## Bit 7 = **R8** Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

## Bit 6 = **T8** Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit  $4 = \mathbf{M}$  Word length. This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

## Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

## Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.

0: Parity error interrupt disabled

1: Parity error interrupt enabled.

57

# **10-BIT A/D CONVERTER** (Cont'd)

57

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

# Table 23. ADC Register Map and Reset Values

# INSTRUCTION SET OVERVIEW (Cont'd)

## **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | СР   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a pre-byte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC opcode

57

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

# INSTRUCTION SET OVERVIEW (Cont'd)

| Mnemo | Description               | Function/Example    | Dst    | Src | 11 | н | 10 | Ν | z | С |

|-------|---------------------------|---------------------|--------|-----|----|---|----|---|---|---|

| ADC   | Add with Carry            | A=A+M+C             | А      | М   |    | Н |    | Ν | Z | С |

| ADD   | Addition                  | A = A + M           | А      | М   |    | н |    | Ν | Z | С |

| AND   | Logical And               | A = A . M           | А      | М   |    |   |    | Ν | Z |   |

| BCP   | Bit compare A, Memory     | tst (A . M)         | А      | М   |    |   |    | Ν | Ζ |   |

| BRES  | Bit Reset                 | bres Byte, #3       | М      |     |    |   |    |   |   |   |

| BSET  | Bit Set                   | bset Byte, #3       | М      |     |    |   |    |   |   |   |

| BTJF  | Jump if bit is false (0)  | btjf Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| BTJT  | Jump if bit is true (1)   | btjt Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| CALL  | Call subroutine           |                     |        |     |    |   |    |   |   |   |

| CALLR | Call subroutine relative  |                     |        |     |    |   |    |   |   |   |

| CLR   | Clear                     |                     | reg, M |     |    |   |    | 0 | 1 |   |

| СР    | Arithmetic Compare        | tst(Reg - M)        | reg    | М   |    |   |    | Ν | Ζ | С |

| CPL   | One Complement            | A = FFH-A           | reg, M |     |    |   |    | Ν | Ζ | 1 |

| DEC   | Decrement                 | dec Y               | reg, M |     |    |   |    | Ν | Ζ |   |

| HALT  | Halt                      |                     |        |     | 1  |   | 0  |   |   |   |

| IRET  | Interrupt routine return  | Pop CC, A, X, PC    |        |     | 11 | Н | 10 | Ν | Ζ | С |

| INC   | Increment                 | inc X               | reg, M |     |    |   |    | Ν | Z |   |

| JP    | Absolute Jump             | jp [TBL.w]          |        |     |    |   |    |   |   |   |

| JRA   | Jump relative always      |                     |        |     |    |   |    |   |   |   |

| JRT   | Jump relative             |                     |        |     |    |   |    |   |   |   |

| JRF   | Never jump                | jrf *               |        |     |    |   |    |   |   |   |

| JRIH  | Jump if ext. INT pin = 1  | (ext. INT pin high) |        |     |    |   |    |   |   |   |

| JRIL  | Jump if ext. INT pin = 0  | (ext. INT pin low)  |        |     |    |   |    |   |   |   |

| JRH   | Jump if H = 1             | H = 1?              |        |     |    |   |    |   |   |   |

| JRNH  | Jump if H = 0             | H = 0?              |        |     |    |   |    |   |   |   |

| JRM   | Jump if I1:0 = 11         | l1:0 = 11?          |        |     |    |   |    |   |   |   |

| JRNM  | Jump if I1:0 <> 11        | l1:0 <> 11?         |        |     |    |   |    |   |   |   |

| JRMI  | Jump if N = 1 (minus)     | N = 1?              |        |     |    |   |    |   |   |   |

| JRPL  | Jump if N = 0 (plus)      | N = 0?              |        |     |    |   |    |   |   |   |

| JREQ  | Jump if Z = 1 (equal)     | Z = 1?              |        |     |    |   |    |   |   |   |

| JRNE  | Jump if Z = 0 (not equal) | Z = 0?              |        |     |    |   |    |   |   |   |

| JRC   | Jump if C = 1             | C = 1?              |        |     |    |   |    |   |   |   |

| JRNC  | Jump if $C = 0$           | C = 0?              |        |     |    |   |    |   |   |   |

| JRULT | Jump if C = 1             | Unsigned <          |        |     |    |   |    |   |   |   |

| JRUGE | Jump if $C = 0$           | Jmp if unsigned >=  |        |     |    |   |    |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$     | Unsigned >          |        |     |    |   |    |   |   |   |

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

# 12.5.3 On-Chip Peripherals

$T_A = 25^{\circ}C f_{CPU} = 4MHz.$

| Symbol               | Parameter                                        | Conditions            | Тур | Unit |

|----------------------|--------------------------------------------------|-----------------------|-----|------|

| I <sub>DD(TIM)</sub> | 16-bit Timer supply current <sup>1)</sup>        | V <sub>DD</sub> =5.0V | 50  |      |

| I <sub>DD(SPI)</sub> | SPI supply current <sup>2)</sup>                 | V <sub>DD</sub> =5.0V | 400 |      |

| I <sub>DD(SCI)</sub> | SCI supply current <sup>3)</sup>                 | V <sub>DD</sub> =5.0V | 400 | μA   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>4)</sup> | V <sub>DD</sub> =5.0V | 400 |      |

Notes:

<u>(</u>ح)

Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer counter running at f<sub>CPU</sub>/4) and timer counter stopped (only TIMD bit set). Data valid for one timer.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

3. Data based on a differential I<sub>DD</sub> measurement between SCI low power state (SCID=1) and a permanent SCI data transmit sequence.

4. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

# EMC CHARACTERISTICS (Cont'd)

## 12.8.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Cymhol           | Parameter  | Conditions            | Device/ Package  | Monitored        | Max vs. [        | fosc/fcpu] | Unit            |                  |                 |    |

|------------------|------------|-----------------------|------------------|------------------|------------------|------------|-----------------|------------------|-----------------|----|

| Symbol           | Parameter  | Conditions            | Device/ Package  | Frequency Band   | 8/4MHz           | 16/8MHz    | Unit            |                  |                 |    |

|                  |            |                       |                  | 0.1MHz to 30MHz  | 12               | 18         |                 |                  |                 |    |

|                  |            |                       | 8/16K Flash/     | 30MHz to 130MHz  | 19               | 25         | dBμV            |                  |                 |    |

|                  |            |                       | TQFP44           | 130MHz to 1GHz   | 15               | 22         |                 |                  |                 |    |

|                  |            |                       |                  | SAE EMI Level    | 3                | 3.5        | -               |                  |                 |    |

|                  |            | V <sub>DD</sub> =5V,  |                  | 20K Elech/TOED44 | 20K Elech/TOED44 |            | 0.1MHz to 30MHz | 20               | 21              |    |

| · ·              | Peak level | T <sub>A</sub> =+25°C |                  |                  |                  |            |                 | 32K Flash/TQFP44 | 30MHz to 130MHz | 26 |

| S <sub>EMI</sub> | reak level | conforming to         | JZK FIASH/TQFF44 | 130MHz to 1GHz   | 22               | 28         |                 |                  |                 |    |

|                  |            | SAE J 1752/3          |                  |                  |                  | 1          | SAE EMI Level   | 3.5              | 4.0             | -  |

|                  |            |                       |                  | 0.1MHz to 30MHz  | 25               | 27         |                 |                  |                 |    |

|                  |            |                       | Flash/TQFP32     | 30MHz to 130MHz  | 30               | 36         | dBμV            |                  |                 |    |

|                  |            |                       | FIASH/TQFF32     | 130MHz to 1GHz   | 18               | 23         |                 |                  |                 |    |

|                  |            |                       |                  | SAE EMI Level    | 3.0              | 3.5        | -               |                  |                 |    |

Notes:

<u>(</u>ح)

1. Data based on characterization results, not tested in production.

2. Refer to Application Note AN1709 for data on other package types.

# **12.13 10-BIT ADC CHARACTERISTICS**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                                        | Conditions                             | Min              | Тур     | Мах                            | Unit               |

|-------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|------------------|---------|--------------------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                              |                                        | 0.4              |         | 2                              | MHz                |

| V <sub>AREF</sub> | Analog reference voltage                                                                         | $0.7*V_{DD} \leq V_{AREF} \leq V_{DD}$ | 3.8              |         | V <sub>DD</sub>                | V                  |

| V <sub>AIN</sub>  | Conversion voltage range 1)                                                                      |                                        | V <sub>SSA</sub> |         | V <sub>AREF</sub>              | v                  |

| 1                 | Positive input leakage current for analog                                                        | -40°C≤T <sub>A</sub> ≤+85°C            |                  |         | ±250                           | nA                 |

| l <sub>lkg</sub>  | input <sup>2)</sup>                                                                              | +85°C≤T <sub>A</sub> ≤+125°C           |                  |         | ±1                             | μA                 |

| R <sub>AIN</sub>  | External input impedance                                                                         |                                        |                  |         | see                            | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                               |                                        |                  |         | Figure 83<br>and               | pF                 |

| f <sub>AIN</sub>  | Variation freq. of analog input signal                                                           |                                        |                  |         | Figure<br>84 <sup>2)3)4)</sup> | Hz                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                               |                                        |                  | 12      |                                | pF                 |

| t <sub>ADC</sub>  | Conversion time (Sample+Hold)<br>f <sub>CPU</sub> =8MHz, SPEED=0 f <sub>ADC</sub> =2MHz          |                                        |                  | 7.5     |                                | μs                 |

| t <sub>ADC</sub>  | <ul> <li>No of sample capacitor loading cycles</li> <li>No. of Hold conversion cycles</li> </ul> |                                        |                  | 4<br>11 |                                | 1/f <sub>ADC</sub> |

#### Notes:

1. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

2.For Flash devices: injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input. Analog pins of ST72F324 devices can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.9 does not affect the ADC accuracy.

# PACKAGE MECHANICAL DATA (Cont'd)

57/

# Figure 90. 42-Pin Plastic Dual In-Line Package, Shrink 600-mil Width

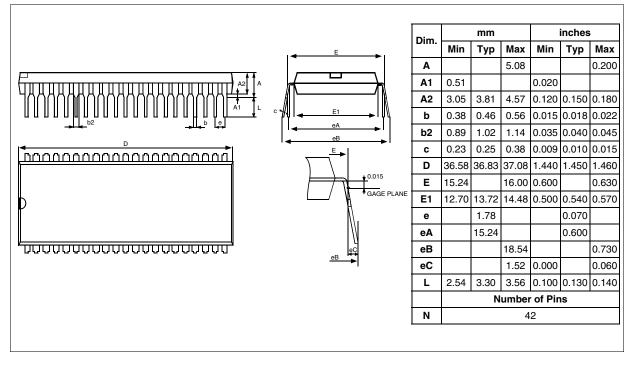

## Figure 91. 32-Pin Plastic Dual In-Line Package, Shrink 400-mil Width

# 14 ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION

# **14.1 FLASH OPTION BYTES**

|         |      |    | STATI | С ОРТ | ION B | YTE 0 |       |     |     | STAT | IC OP | TION B | YTE 1 |       |    |      |

|---------|------|----|-------|-------|-------|-------|-------|-----|-----|------|-------|--------|-------|-------|----|------|

|         | 7    |    |       |       |       |       |       | 0   | 7   |      |       |        |       |       |    | 0    |

|         | WI   | DG | rved  | v     | D     | rved  | rved  | ш   | 5   | TC   | OSC.  | TYPE   | OS    | SCRAN | GE | DFF  |

|         | НАLТ | SW | Rese  | 1     | 0     | Resei | Reser | FMP | PKG | RS.  | 1     | 0      | 2     | 1     | 0  | PLLQ |

| Default | 1    | 1  | 1     | 0     | 0     | 1     | 1     | 1   | 1   | 1    | 1     | 0      | 1     | 1     | 1  | 1    |

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with the internal RC clock source.

## **OPTION BYTE 0**

OPT7= **WDG HALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

OPT6= **WDG SW** Hardware or software watchdog This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

## OPT4:3= VD[1:0] Voltage detection

These option bits enable the voltage detection block (LVD, and AVD) with a selected threshold for the LVD and AVD.

| Selected Low Voltage Detector                    | VD1 | VD0 |

|--------------------------------------------------|-----|-----|

| LVD and AVD Off                                  | 1   | 1   |

| Lowest Voltage Threshold (V <sub>DD</sub> ~3V)   | 1   | 0   |

| Medium Voltage Threshold (V <sub>DD</sub> ~3.5V) | 0   | 1   |

| Highest Voltage Threshold (V <sub>DD</sub> ~4V)  | 0   | 0   |

**Caution:** If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed. For details on the AVD and LVD threshold levels refer to Section 12.4.1 on page 119

OPT2:1 = Reserved, must be kept at default value.

OPT0= **FMP\_R** Flash memory read-out protection Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory.

Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 7.3.1 on page 37 and the ST7 Flash Programming Reference Manual for more details.

0: Read-out protection enabled

1: Read-out protection disabled

# DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## **14.2 FLASH DEVICE ORDERING INFORMATION**

With the objective of continuous improvement, ST is developing new ST72F324B devices and is transferring the production to higher capacity fabs. Refer to the following tables for guidance on ordering.

## **Standard and Industrial Versions**

- For new designs the ST72F324B devices from to the separate ST72324B datasheet.

- For for running production orders select the devices from Table 26

# Table 30. ST7 Application Notes

| IDENTIFICATION | DESCRIPTION                                                             |

|----------------|-------------------------------------------------------------------------|

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                      |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                       |

| AN 985         | EXECUTING CODE IN ST7 RAM                                               |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                             |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                  |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                   |

| AN 989         | GETTING STARTED WITH THE ST7 HIWARE C TOOLCHAIN                         |

| AN1039         | ST7 MATH UTILITY ROUTINES                                               |

| AN1064         | WRITING OPTIMIZED HIWARE C LANGUAGE FOR ST7                             |

| AN1106         | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                              |

| AN1446         | USING THE ST72521 EMULATOR TO DEBUG A ST72324 TARGET APPLICATION        |

| AN1478         | PORTING AN ST7 PANTA PROJECT TO CODEWARRIOR IDE                         |

| AN1575         | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS            |

| AN1576         | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS |

| AN1635         | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                               |

| AN1754         | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC               |

| AN1796         | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT     |

| SYSTEM OPTIMIZ | ATION                                                                   |

| AN1711         | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                     |

# **17 REVISION HISTORY**

# Table 31. Revision History

57

| Date          | Revision | Description of Changes                                                               |

|---------------|----------|--------------------------------------------------------------------------------------|

|               |          | Merged ST72F324 Flash with ST72324B ROM datasheet.                                   |

|               |          | Vt POR max modified in Section 12.4 on page 119                                      |

|               |          | Added Figure 78 on page 137                                                          |

| 05-May-2004   | 2.0      | Modified V <sub>AREF</sub> min in "10-BIT ADC CHARACTERISTICS" on page 142           |

|               |          | Modified I INJ for PB0 in Section 12.9                                               |

|               |          | Added "Clearing active interrupts outside interrupt routine" on page 159             |

|               |          | Modified "32K ROM DEVICES ONLY" on page 164                                          |

|               |          | Removed Clock Security System (CSS) throughout document                              |

|               |          | Added notes on ST72F324B 8K/16K Flash devices in Table 1 and Table 27                |

|               |          | Corrected MCO description in Table 1 and Section 10.2                                |

|               |          | Modified VtPOR in Section 12.4 on page 119                                           |

|               |          | Static current consumption modified in Section 12.9 on page 133                      |

|               |          | Updated footnote and Figure 77 and Figure 78 on page 137                             |

| 30-Mar-2005   | 3        | Modified Soldering information in Section 13.3                                       |

| 00 11121 2000 | Ū        | Updated Section 14 on page 150                                                       |

|               |          | Added Table 27                                                                       |

|               |          | Modified Figure 7 and note 4 in "FLASH PROGRAM MEMORY" on page 17                    |

|               |          | Added limitation on ICC entry mode with 39 pulses to "KNOWN LIMITATIONS" on page 159 |

|               |          | Added Section 16 on page 162 for ST72F324B 8K/16K Flash devices                      |

|               |          | Modified "Internal Sales Types on box label" in Table 29                             |

| 08-Nov-2005   | 4        | Removed information on ST72F324B and ROM devices (now in separate datasheet)         |

|               |          | Changed status to "Not for new design"                                               |

| 04-Apr-2008   | 5        | Added "External interrupt missed" in "KNOWN LIMITATIONS" on page 159                 |

|               |          | Removed information on automotive versions (now in separate datasheet)               |