Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 384 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k2tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 2 PIN D | ODUCTION                                                                               | 8  |

|---------|----------------------------------------------------------------------------------------|----|

|         | ISTER & MEMORY MAP                                                                     |    |

| 4 FLAS  | SH PROGRAM MEMORY                                                                      |    |

| 4.1     |                                                                                        | 17 |

| 4.2     | MAIN FEATURES                                                                          | 17 |

| 4.3     | STRUCTURE                                                                              | 17 |

|         | 4.3.1 Read-out Protection                                                              | 17 |

| 4.4     | ICC INTERFACE                                                                          | -  |

| 4.5     | ICP (IN-CIRCUIT PROGRAMMING)                                                           | 19 |

| 4.6     | IAP (IN-APPLICATION PROGRAMMING)                                                       | 19 |

| 4.7     | RELATED DOCUMENTATION                                                                  | 19 |

|         | 4.7.1 Register Description                                                             | 19 |

| 5 CEN   |                                                                                        |    |

| 5.1     |                                                                                        | 20 |

| 5.2     | MAIN FEATURES                                                                          | 20 |

| 5.3     | CPU REGISTERS                                                                          | 20 |

| 6 SUPF  | PLY, RESET AND CLOCK MANAGEMENT                                                        |    |

| 6.1     | PHASE LOCKED LOOP                                                                      |    |

| 6.2     | MULTI-OSCILLATOR (MO)                                                                  | 24 |

| 6.3     | RESET SEQUENCE MANAGER (RSM)                                                           |    |

|         | 6.3.1 Introduction                                                                     |    |

|         | 6.3.2 Asynchronous External RESET pin                                                  |    |

|         | 6.3.3 External Power-On RESET                                                          | 26 |

|         | 6.3.4 Internal Low Voltage Detector (LVD) RESET                                        |    |

| ~ /     | 6.3.5 Internal Watchdog RESET                                                          |    |

| 6.4     | SYSTEM INTEGRITY MANAGEMENT (SI)                                                       |    |

|         | 6.4.1 Low Voltage Detector (LVD)                                                       |    |

|         | <ul><li>6.4.2 Auxiliary Voltage Detector (AVD)</li><li>6.4.3 Low Power Modes</li></ul> |    |

|         | 6.4.3       Low Power Modes         6.4.4       Register Description                   |    |

| 7 INTE  | RRUPTS                                                                                 |    |

| 7.1     | INTRODUCTION                                                                           |    |

| 7.2     | MASKING AND PROCESSING FLOW                                                            |    |

| 7.3     | INTERRUPTS AND LOW POWER MODES                                                         |    |

| 7.4     | CONCURRENT & NESTED MANAGEMENT                                                         |    |

| 7.5     |                                                                                        |    |

| 7.6     | EXTERNAL INTERRUPTS                                                                    |    |

| 0.1     |                                                                                        |    |

| 7.7     | 7.6.1 I/O Port Interrupt Sensitivity                                                   |    |

|         | ER SAVING MODES                                                                        |    |

| 8.1     | INTRODUCTION                                                                           |    |

| 8.2     | SLOW MODE                                                                              |    |

| • • •   |                                                                                        |    |

| 8.3     | WAIT MODE                                                                              | 41 |

## CENTRAL PROCESSING UNIT (Cont'd)

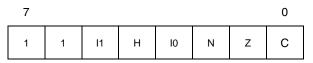

## Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Arithmetic Management Bits

#### Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{th}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

## Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### **Interrupt Management Bits**

#### Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 1 | 10 |

|-------------------------------|---|----|

| Level 0 (main)                | 1 | 0  |

| Level 1                       | 0 | 1  |

| Level 2                       | 0 | 0  |

| Level 3 (= interrupt disable) | 1 | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

## INTERRUPTS (Cont'd)

57

| Table 9. Nested Interrupts | Register | Map and | <b>Reset Values</b> |

|----------------------------|----------|---------|---------------------|

|----------------------------|----------|---------|---------------------|

| Address<br>(Hex.) | Register<br>Label    | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-------------------|----------------------|------------|------------|------------|------------|------------|------------|------------|------------|

|                   |                      | е          | i1         | e          | i0         | MCC        | ; + SI     |            |            |

| 0024h             | ISPR0<br>Reset Value | l1_3<br>1  | 10_3<br>1  | l1_2<br>1  | 10_2<br>1  | l1_1<br>1  | I0_1<br>1  | 1          | 1          |

|                   |                      | S          | PI         |            |            | е          | i3         | е          | 2          |

| 0025h             | ISPR1<br>Reset Value | l1_7<br>1  | 10_7<br>1  | l1_6<br>1  | 10_6<br>1  | l1_5<br>1  | 10_5<br>1  | 11_4<br>1  | 10_4<br>1  |

|                   |                      | AVD SO     |            | CI         | TIM        | ER B       | TIMER A    |            |            |

| 0026h             | ISPR2<br>Reset Value | l1_11<br>1 | l0_11<br>1 | l1_10<br>1 | l0_10<br>1 | l1_9<br>1  | 10_9<br>1  | l1_8<br>1  | l0_8<br>1  |

|                   |                      |            |            |            |            |            |            |            |            |

| 0027h             | ISPR3<br>Reset Value | 1          | 1          | 1          | 1          | l1_13<br>1 | l0_13<br>1 | l1_12<br>1 | l0_12<br>1 |

| 0028h             | EICR<br>Reset Value  | IS11<br>0  | IS10<br>0  | IPB<br>0   | IS21<br>0  | IS20<br>0  | IPA<br>0   | 0          | 0          |

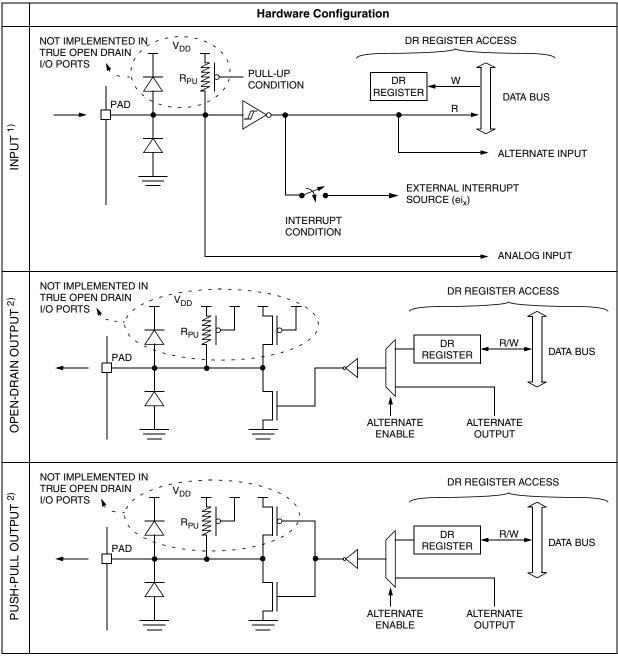

## I/O PORTS (Cont'd)

#### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- 2. When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

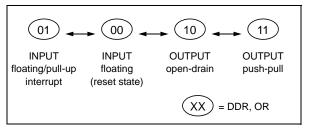

#### 9.3 I/O PORT IMPLEMENTATION

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 30 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 30. Interrupt I/O Port State Transitions

#### 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

#### 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  | Yes                  |

## WATCHDOG TIMER (Cont'd)

#### 10.1.5 Low Power Modes

| Mode | Description  |                        |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SLOW | No effect on | No effect on Watchdog. |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| WAIT | No effect on | Watchdog.              |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|      | OIE bit in   | WDGHALT bit            |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|      | MCCSR        | in Option              |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|      | register     | Byte                   |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|      | 0            | 0                      | No Watchdog reset is generated. The MCU enters Halt mode. The Watch-<br>dog counter is decremented once and then stops counting and is no longer<br>able to generate a watchdog reset until the MCU receives an external inter-<br>rupt or a reset.                                                                            |  |  |  |  |

| HALT |              |                        | If an external interrupt is received, the Watchdog restarts counting after 256 or 4096 CPU clocks. If a reset is generated, the Watchdog is disabled (reset state) unless Hardware Watchdog is selected by option byte. For application recommendations see Section 10.1.7 below.                                              |  |  |  |  |

|      | 0            | 1                      | A reset is generated.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|      | 1            | x                      | No reset is generated. The MCU enters Active Halt mode. The Watchdog counter is not decremented. It stop counting. When the MCU receives an oscillator interrupt or external interrupt, the Watchdog restarts counting immediately. When the MCU receives a reset the Watchdog restarts counting after 256 or 4096 CPU clocks. |  |  |  |  |

#### 10.1.6 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the WDGCR is not used. Refer to the Option Byte description.

## 10.1.7 Using Halt Mode with the WDG (WDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled.

Before executing the HALT instruction, refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller.

## 10.1.8 Interrupts

None.

## 10.1.9 Register Description CONTROL REGISTER (WDGCR)

#### Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | ТЗ | T2 | T1 | то |

#### Bit 7 = **WDGA** Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bit 6:0 = **T[6:0]** 7-bit counter (MSB to LSB).

These bits contain the value of the watchdog counter. It is decremented every 16384  $f_{OSC2}$  cycles (approx.). A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

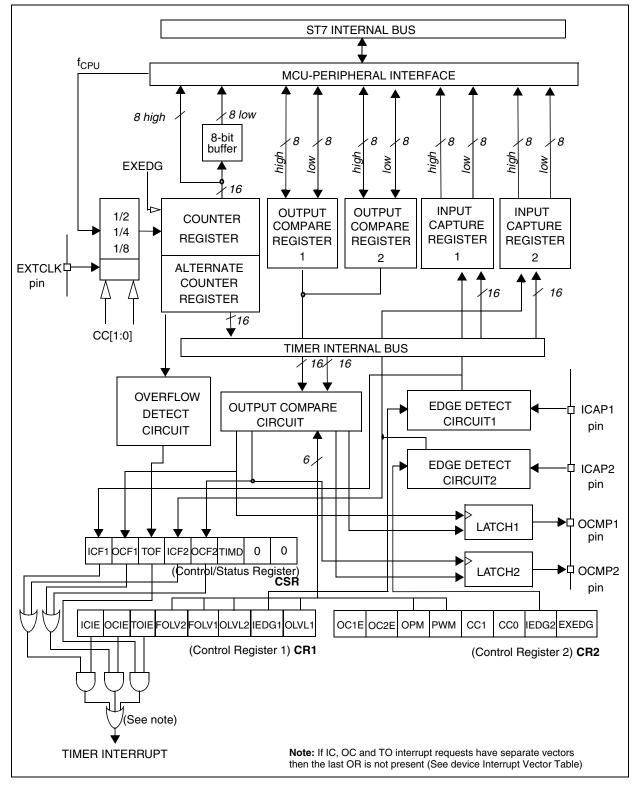

## Figure 35. Timer Block Diagram

47/

57

## Figure 42. Output Compare Timing Diagram, f<sub>TIMER</sub> =f<sub>CPU</sub>/2

| INTERNAL CPU CLOCK                   |                               |

|--------------------------------------|-------------------------------|

| TIMER CLOCK                          |                               |

| COUNTER REGISTER                     | 2ECFX2ED0X2ED1X2ED2X2ED3X2ED4 |

| OUTPUT COMPARE REGISTER i (OCRi)     | 2ED3                          |

| OUTPUT COMPARE FLAG i (OCFi)         |                               |

| OCMP <i>i</i> PIN (OLVL <i>i</i> =1) |                               |

|                                      |                               |

## Figure 43. Output Compare Timing Diagram, f<sub>TIMER</sub> =f<sub>CPU</sub>/4

## **INPUT CAPTURE 1 HIGH REGISTER (IC1HR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |   |

|-----|--|--|--|-----|---|

| MSB |  |  |  | LSB | ĺ |

## **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

#### Read Only

**Reset Value: Undefined**

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

57/

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, the Timer A OC2HR register is write-only.

# OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, the Timer A OC2LR register is write-only.

## **COUNTER HIGH REGISTER (CHR)**

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## **COUNTER LOW REGISTER (CLR)**

Read Only Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.3 Receiver

The SCI can receive data words of either 8 or 9 bits. When the M bit is set, word length is 9 bits and the MSB is stored in the R8 bit in the SCICR1 register.

#### Character reception

During a SCI reception, data shifts in least significant bit first through the RDI pin. In this mode, the SCIDR register consists or a buffer (RDR) between the internal bus and the received shift register (see Figure 1.).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIERPR registers.

- Set the RE bit, this enables the receiver which begins searching for a start bit.

When a character is received:

- The RDRF bit is set. It indicates that the content of the shift register is transferred to the RDR.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

- The error flags can be set if a frame error, noise or an overrun error has been detected during reception.

Clearing the RDRF bit is performed by the following software sequence done by:

- 1. An access to the SCISR register

- 2. A read to the SCIDR register.

The RDRF bit must be cleared before the end of the reception of the next character to avoid an overrun error.

#### **Break Character**

When a break character is received, the SCI handles it as a framing error.

#### **Idle Character**

When a idle frame is detected, there is the same procedure as a data received character plus an interrupt if the ILIE bit is set and the I bit is cleared in the CCR register.

#### **Overrun Error**

An overrun error occurs when a character is received when RDRF has not been reset. Data can not be transferred from the shift register to the RDR register as long as the RDRF bit is not cleared.

When an overrun error occurs:

- The OR bit is set.

- The RDR content is not lost.

- The shift register is overwritten.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

The OR bit is reset by an access to the SCISR register followed by a SCIDR register read operation.

#### Noise Error

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise. Normal data bits are considered valid if three consecutive samples (8th, 9th, 10th) have the same bit value, otherwise the NF flag is set. In the case of start bit detection, the NF flag is set on the basis of an algorithm combining both valid edge detection and three samples (8th, 9th, 10th). Therefore, to prevent the NF flag getting set during start bit reception, there should be a valid edge detection as well as three valid samples.

When noise is detected in a frame:

- The NF flag is set at the rising edge of the RDRF bit.

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The NF flag is reset by a SCISR register read operation followed by a SCIDR register read operation.

During reception, if a false start bit is detected (e.g. 8th, 9th, 10th samples are 011,101,110), the frame is discarded and the receiving sequence is not started for this frame. There is no RDRF bit set for this frame and the NF flag is set internally (not accessible to the user). This NF flag is accessible along with the RDRF bit when a next valid frame is received.

**Note:** If the application Start Bit is not long enough to match the above requirements, then the NF Flag may get set due to the short Start Bit. In this case, the NF flag may be ignored by the application software when the first valid byte is received.

See also Section 0.1.4.10.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## 10.5.4.7 Parity Control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 1.

| Table 20. | <b>Frame Formats</b> |

|-----------|----------------------|

|-----------|----------------------|

| M bit | PCE bit | SCI frame                  |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 1     | 0       | SB   9-bit data   STB      |

| 1     | 1       | SB   8-bit data PB   STB   |

**Legend:** SB = Start Bit, STB = Stop Bit,

PB = Parity Bit

5/

**Note**: In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** the parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 0 if even parity is selected (PS bit = 0).

**Odd parity:** the parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an

even number of "1s" if even parity is selected (PS = 0) or an odd number of "1s" if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

#### 10.5.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: If the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value is "1", but the Noise Flag bit is set because the three samples values are not the same.

Consequently, the bit length must be long enough so that the 8th, 9th and 10th samples have the desired bit value. This means the clock frequency should not vary more than 6/16 (37.5%) within one bit. The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation must not exceed 3.75%.

**Note:** The internal sampling clock of the microcontroller samples the pin value on every falling edge. Therefore, the internal sampling clock and the time the application expects the sampling to take place may be out of sync. For example: If the baud rate is 15.625 Kbaud (bit length is 64µs), then the 8th, 9th and 10th samples are at 28µs, 32µs and 36µs respectively (the first sample starting ideally at 0µs). But if the falling edge of the internal clock occurs just before the pin value changes, the samples would then be out of sync by ~4us. This means the entire bit length must be at least 40µs (36µs for the 10th sample + 4µs for synchronization with the internal sampling clock).

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

#### Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

#### Bit 7 = **R8** Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = **T8** Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit  $4 = \mathbf{M}$  Word length. This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

#### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.

0: Parity error interrupt disabled

1: Parity error interrupt enabled.

57

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE Transmission complete interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

#### Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

#### Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

#### Bit 3 = **TE** *Transmitter enable.*

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

#### Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

#### Bit 1 = **RWU** *Receiver wake-up.*

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

#### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

## INSTRUCTION SET OVERVIEW (Cont'd)

## 11.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

#### Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table25. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressing ModesIndirectIndexedIndirect

| Long and Short<br>Instructions | Function                                           |

|--------------------------------|----------------------------------------------------|

| LD                             | Load                                               |

| CP                             | Compare                                            |

| AND, OR, XOR                   | Logical Operations                                 |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Sub-<br>stractions operations |

| BCP                            | Bit Compare                                        |

| Short Instructions<br>Only | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Opera-<br>tions  |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

#### 11.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset is following the opcode.

#### Relative (Indirect)

The offset is defined in memory, which address follows the opcode.

## CLOCK AND TIMING CHARACTERISTICS (Cont'd)

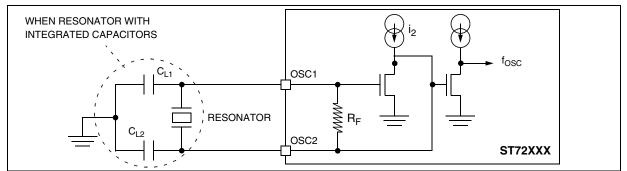

## 12.6.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                                              | Parameter                                                                    | Conditions                |                 | Min | Max | Unit       |

|-----------------------------------------------------|------------------------------------------------------------------------------|---------------------------|-----------------|-----|-----|------------|

|                                                     |                                                                              | LP: Low power             | r oscillator    | 1   | 2   |            |

| £                                                   | Oppillator Fragmanau 1)                                                      | MP: Medium p              | ower oscillator | >2  | 4   |            |

| f <sub>OSC</sub> Oscillator Frequency <sup>1)</sup> | MS: Medium speed oscillator                                                  |                           | >4              | 8   | MHz |            |

|                                                     |                                                                              | HS: High speed oscillator |                 | >8  | 16  |            |

| R <sub>F</sub>                                      | Feedback resistor <sup>2)</sup>                                              |                           |                 | 20  | 40  | kΩ         |

|                                                     |                                                                              | R <sub>S</sub> =200Ω      | LP oscillator   | 22  | 56  |            |

| C <sub>L1</sub>                                     | Recommended load capacitance ver-<br>sus equivalent serial resistance of the | R <sub>S</sub> =200Ω      | MP oscillator   | 22  | 46  | ~ <b>F</b> |

| C <sub>L2</sub>                                     |                                                                              | R <sub>S</sub> =200Ω      | MS oscillator   | 18  | 33  | pF         |

| °L2                                                 | crystal or ceramic resonator (R <sub>S</sub> )                               | R <sub>S</sub> =100Ω      | HS oscillator   | 15  | 33  |            |

| Symbol                              | Parameter | Conditions                       |               | Тур | Max | Unit |

|-------------------------------------|-----------|----------------------------------|---------------|-----|-----|------|

|                                     |           | V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator | 80  | 150 |      |

| i <sub>2</sub> OSC2 driving current |           |                                  | MP oscillator | 160 | 250 |      |

|                                     |           | MS oscillator                    | 310           | 460 | μΑ  |      |

|                                     |           |                                  | HS oscillator | 610 | 910 |      |

## Figure 66. Typical Application with a Crystal or Ceramic Resonator

Notes:

5/

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

## **12.7 MEMORY CHARACTERISTICS**

#### 12.7.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 12.7.2 FLASH Memory

| DUAL VOLTAGE HDFLASH MEMORY             |                                               |                             |                   |     |                   |        |

|-----------------------------------------|-----------------------------------------------|-----------------------------|-------------------|-----|-------------------|--------|

| Symbol                                  | Parameter                                     | Conditions                  | Min <sup>2)</sup> | Тур | Max <sup>2)</sup> | Unit   |

| 4                                       | Operating frequency                           | Read mode                   | 0                 |     | 8                 | MHz    |

| f <sub>CPU</sub>                        |                                               | Write / Erase mode          | 1                 |     | 8                 |        |

| V <sub>PP</sub>                         | Programming voltage <sup>3)</sup>             | $4.5V \le V_{DD} \le 5.5V$  | 11.4              |     | 12.6              | V      |

| I <sub>DD</sub>                         | Supply current <sup>4)</sup>                  | Write / Erase               |                   | 0   |                   | mA     |

| I <sub>PP</sub>                         | V <sub>PP</sub> current <sup>4)</sup>         | Read (V <sub>PP</sub> =12V) |                   |     | 200               | μA     |

|                                         |                                               | Write / Erase               |                   |     | 30                | mA     |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time   |                             |                   | 10  |                   | μs     |

| t <sub>RET</sub>                        | Data retention                                | T <sub>A</sub> =55°C        | 20                |     |                   | years  |

| N <sub>RW</sub>                         | Write erase cycles                            | T <sub>A</sub> =25°C        | 100               |     |                   | cycles |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing tempera-<br>ture range |                             | -40               | 25  | 85                | °C     |

#### Notes:

47/

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Not tested in production.

2. Data based on characterization results, not tested in production.

3. V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons.

4. Data based on simulation results, not tested in production.

## **12.13 10-BIT ADC CHARACTERISTICS**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                                        | Conditions                             | Min              | Тур     | Мах                            | Unit               |

|-------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|------------------|---------|--------------------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                              |                                        | 0.4              |         | 2                              | MHz                |

| V <sub>AREF</sub> | Analog reference voltage                                                                         | $0.7*V_{DD} \leq V_{AREF} \leq V_{DD}$ | 3.8              |         | V <sub>DD</sub>                | V                  |

| V <sub>AIN</sub>  | Conversion voltage range 1)                                                                      |                                        | V <sub>SSA</sub> |         | V <sub>AREF</sub>              | V                  |

| 1                 | Positive input leakage current for analog                                                        | -40°C≤T <sub>A</sub> ≤+85°C            |                  |         | ±250                           | nA                 |

| l <sub>lkg</sub>  | input <sup>2)</sup>                                                                              | +85°C≤T <sub>A</sub> ≤+125°C           |                  |         | ±1                             | μA                 |

| R <sub>AIN</sub>  | External input impedance                                                                         |                                        |                  |         | see                            | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                               |                                        |                  |         | Figure 83<br>and               | pF                 |

| f <sub>AIN</sub>  | Variation freq. of analog input signal                                                           |                                        |                  |         | Figure<br>84 <sup>2)3)4)</sup> | Hz                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                               |                                        |                  | 12      |                                | pF                 |

| t <sub>ADC</sub>  | Conversion time (Sample+Hold)<br>f <sub>CPU</sub> =8MHz, SPEED=0 f <sub>ADC</sub> =2MHz          |                                        |                  | 7.5     |                                | μs                 |

| t <sub>ADC</sub>  | <ul> <li>No of sample capacitor loading cycles</li> <li>No. of Hold conversion cycles</li> </ul> |                                        |                  | 4<br>11 |                                | 1/f <sub>ADC</sub> |

#### Notes:

1. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

2.For Flash devices: injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input. Analog pins of ST72F324 devices can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.9 does not affect the ADC accuracy.

#### **13.2 THERMAL CHARACTERISTICS**

| Symbol            | Ratings                                          | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

|                   | Package thermal resistance (junction to ambient) |       |      |

|                   | TQFP44 10x10                                     | 52    |      |

| R <sub>thJA</sub> | TQFP32 7x7                                       | 70    | °C/W |

|                   | SDIP42 600mil                                    | 55    |      |

|                   | SDIP32 200mil                                    | 50    |      |

| PD                | Power dissipation <sup>1)</sup>                  | 500   | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

#### Notes:

1. The power dissipation is obtained from the formula  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD}xV_{DD}$ ) and  $P_{PORT}$  is the port power dissipation determined by the user.

2. The average chip-junction temperature can be obtained from the formula  $T_J = T_A + P_D x$  RthJA.

#### **13.3 SOLDERING INFORMATION**

47/

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK® specifications are available at www.st.com.