Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k2tc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|     | 12.6 CLOCK AND TIMING CHARACTERISTICS                       | 124 |

|-----|-------------------------------------------------------------|-----|

|     | 12.6.1 General Timings                                      | 124 |

|     | 12.6.2 External Clock Source                                |     |

|     | 12.6.3 Crystal and Ceramic Resonator Oscillators            |     |

|     | 12.6.4 RC Oscillators                                       |     |

|     | 12.6.5 PLL Characteristics                                  |     |

|     | 12.7 MEMORY CHARACTERISTICS                                 |     |

|     | 12.7.1 RAM and Hardware Registers                           |     |

|     | 12.7.2 FLASH Memory                                         |     |

|     |                                                             |     |

|     | 12.8.1 Functional EMS (Electro Magnetic Susceptibility)     |     |

|     | 12.8.3 Absolute Maximum Ratings (Electrical Sensitivity)    |     |

|     | 12.9 I/O PORT PIN CHARACTERISTICS                           |     |

|     | 12.9.1 General Characteristics                              |     |

|     | 12.9.2 Output Driving Current                               |     |

|     | 12.10 CONTROL PIN CHARACTERISTICS                           |     |

|     | 12.10.1Asynchronous RESET Pin                               | 136 |

|     | 12.10.2ICĆSEL/VPP Pin                                       |     |

|     | 12.11 TIMER PERIPHERAL CHARACTERISTICS                      | 139 |

|     | 12.11.116-Bit Timer                                         |     |

|     | 12.12 COMMUNICATION INTERFACE CHARACTERISTICS               |     |

|     | 12.12.1SPI - Serial Peripheral Interface                    |     |

|     | 12.13 10-BIT ADC CHARACTERISTICS                            |     |

|     | 12.13.1Analog Power Supply and Reference Pins               |     |

|     | 12.13.2General PCB Design Guidelines                        |     |

| . ^ | 12.13.3ADC Accuracy                                         |     |

| ıs  | 13.1 PACKAGE MECHANICAL DATA                                |     |

|     |                                                             |     |

|     |                                                             |     |

|     | 13.3 SOLDERING INFORMATION                                  |     |

| 14  | ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION       |     |

|     | 14.1 FLASH OPTION BYTES                                     |     |

|     | 14.2 FLASH DEVICE ORDERING INFORMATION                      |     |

|     | 14.3 SILICON IDENTIFICATION                                 |     |

|     | 14.4 DEVELOPMENT TOOLS                                      |     |

|     | 14.4.1 Socket and Emulator Adapter Information              |     |

|     | 14.5 ST7 APPLICATION NOTES                                  | 157 |

| 15  | KNOWN LIMITATIONS                                           |     |

|     | 15.1 ALL DEVICES                                            | 159 |

|     | 15.1.1 External RC option                                   |     |

|     | 15.1.2 CSS Function                                         |     |

|     | 15.1.3 Safe Connection of OSC1/OSC2 Pins                    |     |

|     | 15.1.4 Unexpected Reset Fetch                               |     |

|     | 15.1.5 Clearing active interrupts outside interrupt routine |     |

|     | 13.1.0 Lateniai intenuptiviisseu                            | 109 |

## **2 PIN DESCRIPTION**

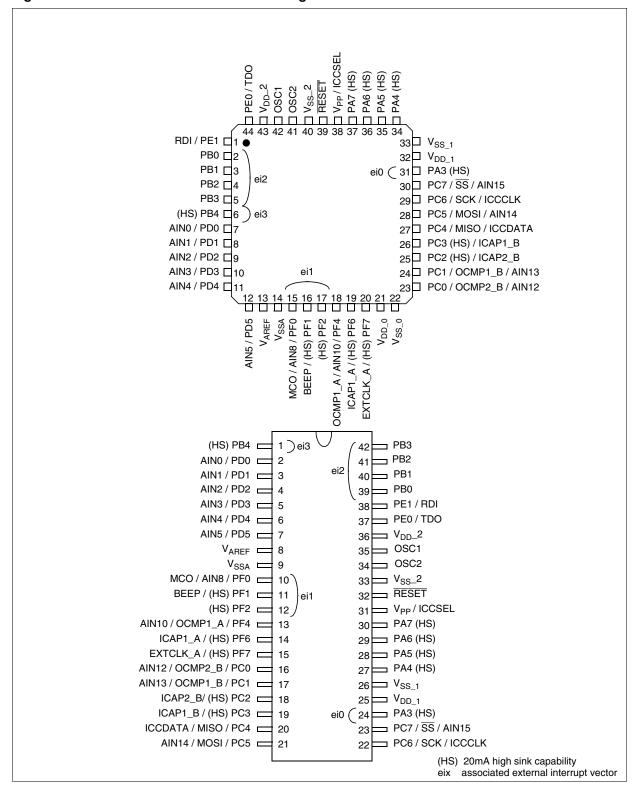

Figure 2. 42-Pin SDIP and 44-Pin TQFP Package Pinouts

# PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to See "ELECTRICAL CHARACTERISTICS" on page 116.

## Legend / Abbreviations for Table 1:

I = input, O = output, S = supplyType: A = Dedicated analog input Input level: In/Output level:  $C = CMOS \ 0.3V_{DD}/0.7V_{DD}$   $C_{T} = CMOS \ 0.3V_{DD}/0.7V_{DD}$  with input trigger

HS = 20mA high sink (on N-buffer only) Output level:

Port and control configuration:

float = floating, wpu = weak pull-up, int = interrupt 1), ana = analog ports – Input:

OD = open drain 2), PP = push-pull – Output:

Refer to "I/O PORTS" on page 45 for more details on the software configuration of the I/O ports.

The RESET configuration of each pin is shown in bold. This configuration is valid as long as the device is in reset state.

**Table 1. Device Pin Description**

|        | Pin n° |        |        |                       |      | Le             | evel   |       |     | Ρ   | ort |        |    | Main       |                                       |                        |                    |  |

|--------|--------|--------|--------|-----------------------|------|----------------|--------|-------|-----|-----|-----|--------|----|------------|---------------------------------------|------------------------|--------------------|--|

| P44    | 42     | P32    | 32     | Pin Name              | Туре | ut             | out    |       | Inp | out |     | Output |    | Output     |                                       | function<br>(after     | Alternate Function |  |

| TQFP44 | SDIP42 | TQFP32 | SDIP32 |                       |      | Input          | Output | float | ndw | int | ana | ОО     | РР | reset)     |                                       |                        |                    |  |

| 6      | 1      | 30     | 1      | PB4 (HS)              | I/O  | $C_T$          | HS     | X     | е   | i3  |     | Χ      | Χ  | Port B4    |                                       |                        |                    |  |

| 7      | 2      | 31     | 2      | PD0/AIN0              | I/O  | $C_{T}$        |        | Х     | Χ   |     | Χ   | Χ      | Х  | Port D0    | ADC Analog                            | Input 0                |                    |  |

| 8      | 3      | 32     | З      | PD1/AIN1              | I/O  | $C_{T}$        |        | Х     | Χ   |     | Χ   | Χ      | Х  | Port D1    | ADC Analog                            | Input 1                |                    |  |

| 9      | 4      |        |        | PD2/AIN2              | I/O  | $C_{T}$        |        | Х     | Χ   |     | Χ   | Χ      | Χ  | Port D2    | ADC Analog                            | Input 2                |                    |  |

| 10     | 5      |        |        | PD3/AIN3              | I/O  | $C_{T}$        |        | Х     | Χ   |     | Χ   | Χ      | Χ  | Port D3    | ADC Analog                            | Input 3                |                    |  |

| 11     | 6      |        |        | PD4/AIN4              | I/O  | $C_{T}$        |        | Х     | Χ   |     | Χ   | Χ      | Χ  | Port D4    | ADC Analog                            | Input 4                |                    |  |

| 12     | 7      |        |        | PD5/AIN5              | I/O  | $C_T$          |        | X     | Χ   |     | Χ   | Χ      | Χ  | Port D5    | ADC Analog Input 5                    |                        |                    |  |

| 13     | 8      | 1      | 4      | V <sub>AREF</sub>     | S    |                |        |       |     |     |     |        |    | Analog R   | Reference Voltage for ADC             |                        |                    |  |

| 14     | 9      | 2      | 5      | V <sub>SSA</sub>      | S    |                |        |       |     |     |     |        |    | Analog G   | g Ground Voltage                      |                        |                    |  |

| 15     | 10     | 3      | 6      | PF0/MCO/AIN8          | I/O  | C <sub>T</sub> |        | х     | е   | i1  | Χ   | Х      | Х  | Port F0    | Main clock<br>out (f <sub>CPU</sub> ) | ADC Analog<br>Input 8  |                    |  |

| 16     | 11     | 4      | 7      | PF1 (HS)/BEEP         | I/O  | $C_T$          | HS     | X     | е   | i1  |     | Χ      | Χ  | Port F1    | Beep signal output                    |                        |                    |  |

| 17     | 12     |        |        | PF2 (HS)              | I/O  | $C_T$          | HS     | X     |     | ei1 |     | Χ      | Χ  | Port F2    | I.                                    |                        |                    |  |

| 18     | 13     | 5      | 8      | PF4/OCMP1_A/<br>AIN10 | I/O  | C <sub>T</sub> |        | x     | X   |     | х   | Х      | х  | Port F4    | Timer A Out-<br>put Com-<br>pare 1    | ADC Analog<br>Input 10 |                    |  |

| 19     | 14     | 6      | 9      | PF6 (HS)/ICAP1_A      | I/O  | $C_{T}$        | HS     | X     | Χ   |     |     | Χ      | Х  | Port F6    | Timer A Input                         | Capture 1              |                    |  |

| 20     | 15     | 7      | 10     | PF7 (HS)/<br>EXTCLK_A | I/O  | C <sub>T</sub> | HS     | Х     | Χ   |     |     | Х      | х  | Port F7    | Timer A External Clock<br>Source      |                        |                    |  |

| 21     |        |        |        | $V_{DD_0}$            | S    |                |        |       |     |     |     |        |    | Digital Ma | Main Supply Voltage                   |                        |                    |  |

| 22     |        |        |        | V <sub>SS_0</sub>     | S    |                |        |       |     |     |     |        |    | Digital G  | Ground Voltage                        |                        |                    |  |

| 23     | 16     | 8      | 11     | PC0/OCMP2_B/<br>AIN12 | I/O  | Ст             |        | Х     | Х   |     | Х   | х      | х  | Port C0    | Timer B Out-<br>put Com-<br>pare 2    | ADC Analog<br>Input 12 |                    |  |

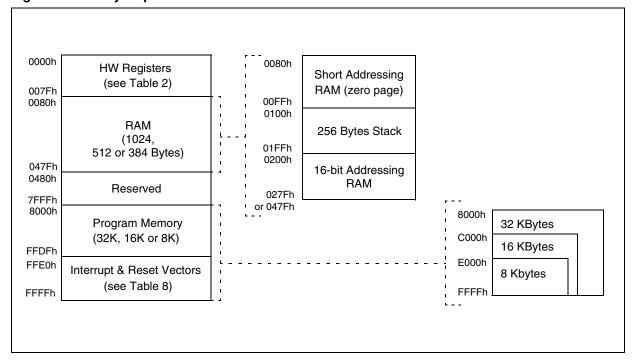

# **3 REGISTER & MEMORY MAP**

As shown in Figure 5, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register locations, up to 1024 bytes of RAM and up to 32 Kbytes of user program memory. The RAM space includes up to 256 bytes for the stack from 0100h to 01FFh.

The highest address bytes contain the user reset and interrupt vectors.

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

Figure 5. Memory Map

**Table 2. Hardware Register Map**

| Address                          | Block                | Register<br>Label                | Register Name                                                                                                                                               | Reset<br>Status                 | Remarks                                       |

|----------------------------------|----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------|

| 0000h<br>0001h<br>0002h          | Port A <sup>2)</sup> | PADR<br>PADDR<br>PAOR            | Port A Data Register Port A Data Direction Register Port A Option Register                                                                                  | 00h <sup>1)</sup><br>00h<br>00h | R/W<br>R/W<br>R/W                             |

| 0003h<br>0004h<br>0005h          | Port B <sup>2)</sup> | PBDR<br>PBDDR<br>PBOR            | Port B Data Register Port B Data Direction Register Port B Option Register                                                                                  | 00h <sup>1)</sup><br>00h<br>00h | R/W<br>R/W<br>R/W                             |

| 0006h<br>0007h<br>0008h          | Port C               | PCDR<br>PCDDR<br>PCOR            | Port C Data Register Port C Data Direction Register Port C Option Register                                                                                  | 00h <sup>1)</sup><br>00h<br>00h | R/W<br>R/W<br>R/W                             |

| 0009h<br>000Ah<br>000Bh          | Port D <sup>2)</sup> | PDADR<br>PDDDR<br>PDOR           | Port D Data Register Port D Data Direction Register Port D Option Register                                                                                  | 00h <sup>1)</sup><br>00h<br>00h | R/W<br>R/W<br>R/W                             |

| 000Ch<br>000Dh<br>000Eh          | Port E <sup>2)</sup> | PEDR<br>PEDDR<br>PEOR            | Port E Data Register Port E Data Direction Register Port E Option Register                                                                                  | 00h <sup>1)</sup><br>00h<br>00h | R/W<br>R/W <sup>2)</sup><br>R/W <sup>2)</sup> |

| 000Fh<br>0010h<br>0011h          | Port F <sup>2)</sup> | PFDR<br>PFDDR<br>PFOR            | Port F Data Register Port F Data Direction Register Port F Option Register                                                                                  | 00h <sup>1)</sup><br>00h<br>00h | R/W<br>R/W<br>R/W                             |

| 0012h<br>to<br>0020h             |                      |                                  | Reserved Area (15 Bytes)                                                                                                                                    |                                 |                                               |

| 0021h<br>0022h<br>0023h          | SPI                  | SPIDR<br>SPICR<br>SPICSR         | SPI Data I/O Register<br>SPI Control Register<br>SPI Control/Status Register                                                                                | xxh<br>0xh<br>00h               | R/W<br>R/W<br>R/W                             |

| 0024h<br>0025h<br>0026h<br>0027h | ITC                  | ISPR0<br>ISPR1<br>ISPR2<br>ISPR3 | Interrupt Software Priority Register 0 Interrupt Software Priority Register 1 Interrupt Software Priority Register 2 Interrupt Software Priority Register 3 | FFh<br>FFh<br>FFh<br>FFh        | R/W<br>R/W<br>R/W<br>R/W                      |

| 0028h                            |                      | EICR                             | External Interrupt Control Register                                                                                                                         | 00h                             | R/W                                           |

| 0029h                            | FLASH                | FCSR                             | Flash Control/Status Register                                                                                                                               | 00h                             | R/W                                           |

| 002Ah                            | WATCHDOG             | WDGCR                            | Watchdog Control Register                                                                                                                                   | 7Fh                             | R/W                                           |

| 002Bh                            | SI                   | SICSR                            | System Integrity Control Status Register                                                                                                                    | xxh                             | R/W                                           |

| 002Ch<br>002Dh                   | MCC                  | MCCSR<br>MCCBCR                  | Main Clock Control / Status Register<br>Main Clock Controller: Beep Control Register                                                                        | 00h<br>00h                      | R/W<br>R/W                                    |

| 002Eh<br>to<br>0030h             |                      |                                  | Reserved Area (3 Bytes)                                                                                                                                     |                                 |                                               |

## POWER SAVING MODES (Cont'd)

### 8.4.2.1 Halt Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

57

# I/O PORTS (Cont'd)

# 9.5.1 I/O Port Implementation

The I/O port register configurations are summarised as follows.

## **Standard Ports**

PA5:4, PC7:0, PD5:0, PE1:0, PF7:6, 4

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

# **Interrupt Ports**

# **PB4**, **PB2:0**, **PF1:0** (with pull-up)

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

PA3, PB3, PF2 (without pull-up)

| MODE                     | DDR | OR |

|--------------------------|-----|----|

| floating input           | 0   | 0  |

| floating interrupt input | 0   | 1  |

| open drain output        | 1   | 0  |

| push-pull output         | 1   | 1  |

# True Open Drain Ports PA7:6

| MODE                         | DDR |

|------------------------------|-----|

| floating input               | 0   |

| open drain (high sink ports) | 1   |

**Table 12. Port Configuration**

| Port   | Pin name   | <u> </u> | nput               | Ou         | tput      |

|--------|------------|----------|--------------------|------------|-----------|

| Port   | Pin name   | OR = 0   | OR = 1             | OR = 0     | OR = 1    |

|        | PA7:6      | flo      | pating             | true op    | en-drain  |

| Port A | PA5:4      | floating | pull-up            | open drain | push-pull |

|        | PA3        | floating | floating interrupt | open drain | push-pull |

| Port B | PB3        | floating | floating interrupt | open drain | push-pull |

| FULL   | PB4, PB2:0 | floating | pull-up interrupt  | open drain | push-pull |

| Port C | PC7:0      | floating | pull-up            | open drain | push-pull |

| Port D | PD5:0      | floating | pull-up            | open drain | push-pull |

| Port E | PE1:0      | floating | pull-up            | open drain | push-pull |

|        | PF7:6, 4   | floating | pull-up            | open drain | push-pull |

| Port F | PF2        | floating | floating interrupt | open drain | push-pull |

|        | PF1:0      | floating | pull-up interrupt  | open drain | push-pull |

Table 14. Watchdog Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### 10.3 16-BIT TIMER

#### 10.3.1 Introduction

The timer consists of a 16-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU clock prescaler.

Some ST7 devices have two on-chip 16-bit timers. They are completely independent, and do not share any resources. They are synchronized after a MCU reset as long as the timer clock frequencies are not modified.

This description covers one or two 16-bit timers. In ST7 devices with two timers, register names are prefixed with TA (Timer A) or TB (Timer B).

#### 10.3.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4 or 8.

- Overflow status flag and maskable interrupt

- External clock input (must be at least 4 times slower than the CPU clock speed) with the choice of active edge

- 1 or 2 Output Compare functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- 1 or 2 Input Capture functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced Power Mode

- 5 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2, EXTCLK)\*

The Block Diagram is shown in Figure 35.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

## 10.3.3 Functional Description

#### 10.3.3.1 Counter

The main block of the Programmable Timer is a 16-bit free running upcounter and its associated 16-bit registers. The 16-bit registers are made up of two 8-bit registers called high & low.

Counter Register (CR):

- Counter High Register (CHR) is the most significant byte (MS Byte).

- Counter Low Register (CLR) is the least significant byte (LS Byte).

Alternate Counter Register (ACR)

- Alternate Counter High Register (ACHR) is the most significant byte (MS Byte).

- Alternate Counter Low Register (ACLR) is the least significant byte (LS Byte).

These two read-only 16-bit registers contain the same value but with the difference that reading the ACLR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR), (see note at the end of paragraph titled 16-bit read sequence).

Writing in the CLR register or ACLR register resets the free running counter to the FFFCh value. Both counters have a reset value of FFFCh (this is the only value which is reloaded in the 16-bit timer). The reset value of both counters is also FFFCh in One Pulse mode and PWM mode.

The timer clock depends on the clock control bits of the CR2 register, as illustrated in Table 16 Clock Control Bits. The value in the counter register repeats every 131072, 262144 or 524288 CPU clock cycles depending on the CC[1:0] bits.

The timer frequency can be f<sub>CPU</sub>/2, f<sub>CPU</sub>/4, f<sub>CPU</sub>/8 or an external frequency.

**Caution:** In Flash devices, Timer A functionality has the following restrictions:

- TAOC2HR and TAOC2LR registers are write only

- Input Capture 2 is not implemented

- The corresponding interrupts cannot be used (ICF2, OCF2 forced by hardware to zero)

# ALTERNATE COUNTER HIGH REGISTER (ACHR)

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **INPUT CAPTURE 2 HIGH REGISTER (IC2HR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, this register is not implemented for Timer A.

## **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, this register is not implemented for Timer A.

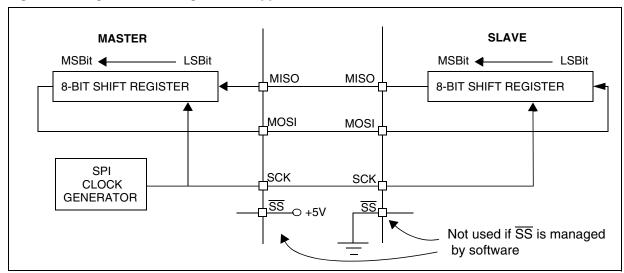

## SERIAL PERIPHERAL INTERFACE (Cont'd)

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master MCU.

## 10.4.3.1 Functional Description

A basic example of interconnections between a single master and a single slave is illustrated in Figure 47.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 50) but master and slave must be programmed with the same timing mode.

Figure 47. Single Master/ Single Slave Application

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

### 10.5.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1.).

#### **Procedure**

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set.

When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

- An access to the SCISR register

- 2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 2.).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### Idle Characters

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

## 12.2.3 Thermal Characteristics

| Symbol           | Ratings                                                                 | Value       | Unit |  |  |  |

|------------------|-------------------------------------------------------------------------|-------------|------|--|--|--|

| T <sub>STG</sub> | Storage temperature range                                               | -65 to +150 | °C   |  |  |  |

| T <sub>J</sub>   | Maximum junction temperature (see Section 13.2 THERMAL CHARACTERISTICS) |             |      |  |  |  |

## 12.3 OPERATING CONDITIONS

## 12.3.1 Operating Conditions

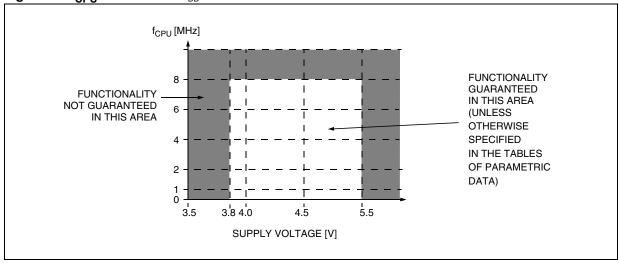

| Symbol           | Parameter                                        | Conditions                      | Min | Max | Unit |  |

|------------------|--------------------------------------------------|---------------------------------|-----|-----|------|--|

| f <sub>CPU</sub> | Internal clock frequency                         |                                 | 0   | 8   | MHz  |  |

| V <sub>DD</sub>  | Operating voltage (except Flash Write/<br>Erase) |                                 | 3.8 | 5.5 | V    |  |

|                  | Operating Voltage for Flash Write/Erase          | V <sub>PP</sub> = 11.4 to 12.6V | 4.5 | 5.5 |      |  |

|                  |                                                  | 1 Suffix Version                | 0   | 70  |      |  |

|                  | Ambient temperature range                        | 5 Suffix Version                | -10 | 85  | °C   |  |

| $T_A$            |                                                  | 6 Suffix Versions               | -40 | 85  |      |  |

|                  |                                                  | 7 Suffix Versions               | -40 | 105 |      |  |

|                  |                                                  | 3 Suffix Version                | -40 | 125 |      |  |

Figure 60.  $f_{CPU}$  Max Versus  $V_{DD}$

**Note:** Some temperature ranges are only available with a specific package and memory size. Refer to Ordering Information.

Warning: Do not connect 12V to V<sub>PP</sub> before V<sub>DD</sub> is powered on, as this may damage the device.

57

# **CLOCK AND TIMING CHARACTERISTICS** (Cont'd)

| 00   | cil. |                                                            | Typical Ceramic Resonators (information for guidance only) |       |                                                                                                          |                    |    | t <sub>SU(osc)</sub> |

|------|------|------------------------------------------------------------|------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------|--------------------|----|----------------------|

| Us   | CII. | Reference <sup>3)</sup> Freq. Characteristic <sup>1)</sup> |                                                            | [pF]  | [pF]                                                                                                     | [ms] <sup>2)</sup> |    |                      |

| 0    | LP   | ٨                                                          | CSA2.00MG                                                  | 2MHz  | $\Delta f_{OSC} = [\pm 0.5\%_{tolerance}, \pm 0.3\%_{\Delta Ta}, \pm 0.3\%_{aging}, \pm x.x\%_{correl}]$ | 22                 | 22 | 4                    |

| mi   | MP   | AT,                                                        | CSA4.00MG                                                  | 4MHz  | $\Delta f_{OSC} = [\pm 0.5\%_{tolerance}, \pm 0.3\%_{\Delta Ta}, \pm 0.3\%_{aging}, \pm x.x\%_{correl}]$ | 22                 | 22 | 2                    |

| Sera | MS   | IUR                                                        | CSA8.00MTZ                                                 | 8MHz  | $\Delta f_{OSC} = [\pm 0.5\%_{tolerance}, \pm 0.5\%_{\Delta Ta}, \pm 0.3\%_{aging}, \pm x.x\%_{correl}]$ | 33                 | 33 | 1                    |

|      | HS   | 2                                                          | CSA16.00MXZ040 <sup>4)</sup>                               | 16MHz | $\Delta f_{OSC} = [\pm 0.5\%_{tolerance}, \pm 0.3\%_{\Delta Ta}, \pm 0.3\%_{aging}, \pm x.x\%_{correl}]$ | 33                 | 33 | 0.7                  |

- 1. Resonator characteristics given by the ceramic resonator manufacturer.

- 2.  $t_{SU(OSC)}$  is the typical oscillator start-up time measured between  $V_{DD}$ =2.8V and the fetch of the first instruction (with a quick  $V_{DD}$  ramp-up from 0 to 5V (<50 $\mu$ s).

- 3. Resonators all have different characteristics. Contact the manufacturer to obtain the appropriate values of external components and to verify oscillator performance.

- 4. 3rd overtone resonators require specific validation by the resonator manufacturer.

## **EMC CHARACTERISTICS** (Cont'd)

# 12.8.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Cumbal           | Parameter  | Conditions                                                     | Daviss/ Daskans  | Monitored       | Max vs. [f <sub>OSC</sub> /f <sub>CPU</sub> ] |         | Unit      |  |

|------------------|------------|----------------------------------------------------------------|------------------|-----------------|-----------------------------------------------|---------|-----------|--|

| Symbol           | Parameter  | Conditions                                                     | Device/ Package  | Frequency Band  | 8/4MHz                                        | 16/8MHz | Oiiit     |  |

|                  |            |                                                                |                  | 0.1MHz to 30MHz | 12                                            | 18      |           |  |

|                  |            |                                                                | 8/16K Flash/     | 30MHz to 130MHz | 19                                            | 25      | $dB\mu V$ |  |

|                  | Peak level | $V_{DD}$ =5V,<br>$T_A$ =+25°C<br>conforming to<br>SAE J 1752/3 | TQFP44           | 130MHz to 1GHz  | 15                                            | 22      |           |  |

|                  |            |                                                                |                  | SAE EMI Level   | 3                                             | 3.5     | -         |  |

|                  |            |                                                                | 32K Flash/TQFP44 | 0.1MHz to 30MHz | 20                                            | 21      | dBμV      |  |

|                  |            |                                                                |                  | 30MHz to 130MHz | 26                                            | 31      |           |  |

| S <sub>EMI</sub> |            |                                                                |                  | 130MHz to 1GHz  | 22                                            | 28      |           |  |

|                  |            |                                                                |                  | SAE EMI Level   | 3.5                                           | 4.0     | -         |  |

|                  |            |                                                                |                  | 0.1MHz to 30MHz | 25                                            | 27      |           |  |

|                  |            |                                                                | Flash/TQFP32     | 30MHz to 130MHz | 30                                            | 36      | $dB\mu V$ |  |

|                  |            |                                                                | FIASII/TQFF32    | 130MHz to 1GHz  | 18                                            | 23      |           |  |

|                  |            |                                                                |                  | SAE EMI Level   | 3.0                                           | 3.5     | -         |  |

- 1. Data based on characterization results, not tested in production.

- 2. Refer to Application Note AN1709 for data on other package types.

#### 12.10 CONTROL PIN CHARACTERISTICS

# 12.10.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Symbol Parameter                                 |                        | Conditions            |                                | Тур | Max                  | Unit |

|-------------------------|--------------------------------------------------|------------------------|-----------------------|--------------------------------|-----|----------------------|------|

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis <sup>2)</sup> |                        |                       |                                | 2.5 |                      | V    |

| V <sub>IL</sub>         | Input low level voltage 1)                       |                        |                       |                                |     | 0.16xV <sub>DD</sub> | V    |

| V <sub>IH</sub>         | Input high level voltage 1)                      |                        |                       | $0.85 \mathrm{xV}_\mathrm{DD}$ |     |                      | v    |

| V <sub>OL</sub>         | Output low level voltage 3)                      | V <sub>DD</sub> =5V    | I <sub>IO</sub> =+2mA |                                | 0.2 | 0.5                  | V    |

| I <sub>IO</sub>         | Driving current on RESET pin                     |                        |                       |                                | 2   |                      | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor                 | V <sub>DD</sub> =5V    |                       | 20                             | 30  | 120                  | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration                   | Internal reset sources |                       | 20                             | 30  | 42 <sup>6)</sup>     | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)                |                        |                       | 2.5                            |     |                      | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup>           |                        |                       |                                | 200 |                      | ns   |

- 1. Data based on characterization results, not tested in production.

- 2. Hysteresis voltage between Schmitt trigger switching levels.

- 3. The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overline{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(RSTL)in}$  can be ignored.

- 5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

- 6. Data guaranteed by design, not tested in production.

# **CONTROL PIN CHARACTERISTICS** (Cont'd)

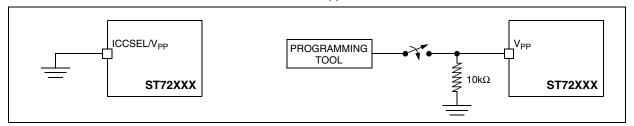

# 12.10.2 ICCSEL/V<sub>PP</sub> Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol          | Parameter                   | Conditions                       | Min                  | Max  | Unit |

|-----------------|-----------------------------|----------------------------------|----------------------|------|------|

| $V_{IL}$        | Input low level voltage 1)  |                                  | $V_{SS}$             | 0.2  | V    |

| V <sub>IH</sub> | Input high level voltage 1) |                                  | V <sub>DD</sub> -0.1 | 12.6 | V    |

| ΙL              | Input leakage current       | V <sub>IN</sub> =V <sub>SS</sub> |                      | ±1   | μΑ   |

Figure 79. Two typical Applications with ICCSEL/V<sub>PP</sub> Pin <sup>2)</sup>

- 1. Data based on design simulation and/or technology characteristics, not tested in production.

- 2. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to V<sub>SS</sub>.

## **COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)**

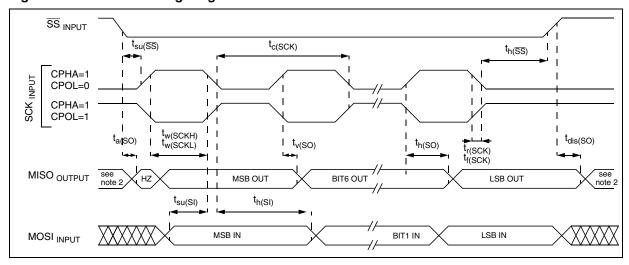

Figure 81. SPI Slave Timing Diagram with CPHA=11)

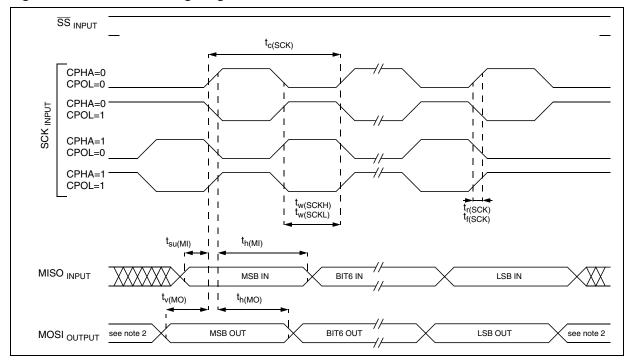

Figure 82. SPI Master Timing Diagram 1)

- 1. Measurement points are done at CMOS levels:  $0.3 \mathrm{xV}_{\mathrm{DD}}$  and  $0.7 \mathrm{xV}_{\mathrm{DD}}$ .

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

## 12.13 10-BIT ADC CHARACTERISTICS

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                               | Conditions                                              | Min              | Тур     | Max                         | Unit               |

|-------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|---------|-----------------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                     |                                                         | 0.4              |         | 2                           | MHz                |

| V <sub>AREF</sub> | Analog reference voltage                                                                | 0.7*V <sub>DD</sub> ≤V <sub>AREF</sub> ≤V <sub>DD</sub> | 3.8              |         | $V_{DD}$                    | V                  |

| V <sub>AIN</sub>  | Conversion voltage range 1)                                                             |                                                         | V <sub>SSA</sub> |         | V <sub>AREF</sub>           | V                  |

| 1                 | Positive input leakage current for analog                                               | -40°C≤T <sub>A</sub> ≤+85°C                             |                  |         | ±250                        | nA                 |

| I <sub>lkg</sub>  | input <sup>2)</sup>                                                                     | +85°C≤T <sub>A</sub> ≤+125°C                            |                  |         | ±1                          | μΑ                 |

| R <sub>AIN</sub>  | External input impedance                                                                |                                                         |                  |         | see                         | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                      |                                                         |                  |         | Figure 83                   | pF                 |

| f <sub>AIN</sub>  | Variation freq. of analog input signal                                                  |                                                         |                  |         | Figure 84 <sup>2)3)4)</sup> | Hz                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                      |                                                         |                  | 12      |                             | pF                 |

| t <sub>ADC</sub>  | Conversion time (Sample+Hold)<br>f <sub>CPU</sub> =8MHz, SPEED=0 f <sub>ADC</sub> =2MHz |                                                         |                  | 7.5     |                             | μs                 |

| t <sub>ADC</sub>  | - No of sample capacitor loading cycles - No. of Hold conversion cycles                 |                                                         |                  | 4<br>11 |                             | 1/f <sub>ADC</sub> |

<sup>1.</sup> Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

<sup>2.</sup>For Flash devices: injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input. Analog pins of ST72F324 devices can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and  $\Sigma$ I<sub>INJ(PIN)</sub> in Section 12.9 does not affect the ADC accuracy.

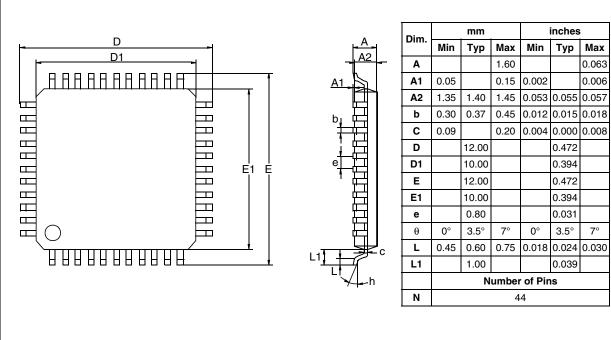

# 13 PACKAGE CHARACTERISTICS

#### 13.1 PACKAGE MECHANICAL DATA

Figure 88. 44-Pin Thin Quad Flat Package

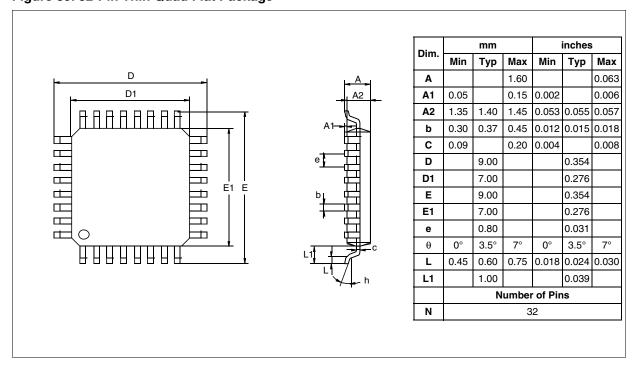

Figure 89. 32-Pin Thin Quad Flat Package