Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k4tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 2 PIN D | ODUCTION                                                                               | 8   |

|---------|----------------------------------------------------------------------------------------|-----|

|         | ISTER & MEMORY MAP                                                                     |     |

| 4 FLAS  | SH PROGRAM MEMORY                                                                      |     |

| 4.1     |                                                                                        | 17  |

| 4.2     | MAIN FEATURES                                                                          | 17  |

| 4.3     | STRUCTURE                                                                              | 17  |

|         | 4.3.1 Read-out Protection                                                              | 17  |

| 4.4     | ICC INTERFACE                                                                          | -   |

| 4.5     | ICP (IN-CIRCUIT PROGRAMMING)                                                           | 19  |

| 4.6     | IAP (IN-APPLICATION PROGRAMMING)                                                       | 19  |

| 4.7     | RELATED DOCUMENTATION                                                                  | 19  |

|         | 4.7.1 Register Description                                                             | 19  |

| 5 CEN   |                                                                                        |     |

| 5.1     |                                                                                        | 20  |

| 5.2     | MAIN FEATURES                                                                          | 20  |

| 5.3     | CPU REGISTERS                                                                          | 20  |

| 6 SUPF  | PLY, RESET AND CLOCK MANAGEMENT                                                        |     |

| 6.1     | PHASE LOCKED LOOP                                                                      |     |

| 6.2     | MULTI-OSCILLATOR (MO)                                                                  | 24  |

| 6.3     | RESET SEQUENCE MANAGER (RSM)                                                           |     |

|         | 6.3.1 Introduction                                                                     |     |

|         | 6.3.2 Asynchronous External RESET pin                                                  |     |

|         | 6.3.3 External Power-On RESET                                                          | 26  |

|         | 6.3.4 Internal Low Voltage Detector (LVD) RESET                                        |     |

| ~ /     | 6.3.5 Internal Watchdog RESET                                                          |     |

| 6.4     | SYSTEM INTEGRITY MANAGEMENT (SI)                                                       |     |

|         | 6.4.1 Low Voltage Detector (LVD)                                                       |     |

|         | <ul><li>6.4.2 Auxiliary Voltage Detector (AVD)</li><li>6.4.3 Low Power Modes</li></ul> |     |

|         | 6.4.3       Low Power Modes         6.4.4       Register Description                   |     |

| 7 INTE  | RRUPTS                                                                                 |     |

| 7.1     | INTRODUCTION                                                                           |     |

| 7.2     | MASKING AND PROCESSING FLOW                                                            |     |

| 7.3     | INTERRUPTS AND LOW POWER MODES                                                         |     |

| 7.4     | CONCURRENT & NESTED MANAGEMENT                                                         |     |

| 7.5     |                                                                                        |     |

| 7.6     | EXTERNAL INTERRUPTS                                                                    |     |

| 0.1     |                                                                                        |     |

| 7.7     | 7.6.1 I/O Port Interrupt Sensitivity                                                   |     |

|         | ER SAVING MODES                                                                        |     |

| 8.1     | INTRODUCTION                                                                           |     |

| 8.2     | SLOW MODE                                                                              |     |

| • • •   |                                                                                        |     |

| 8.3     | WAIT MODE                                                                              | 4 I |

# CENTRAL PROCESSING UNIT (Cont'd)

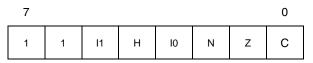

## Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Arithmetic Management Bits

#### Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{th}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### **Interrupt Management Bits**

#### Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 1 | 10 |

|-------------------------------|---|----|

| Level 0 (main)                | 1 | 0  |

| Level 1                       | 0 | 1  |

| Level 2                       | 0 | 0  |

| Level 3 (= interrupt disable) | 1 | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

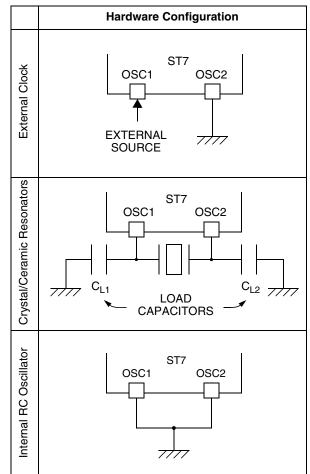

# 6.2 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by three different source types coming from the multi-oscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 5. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

#### **External Clock Source**

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

#### **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to Section 14.1 on page 150 for more details on the frequency ranges). In this mode of the multioscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

In order not to exceed the max. operating frequency, the internal RC oscillator must not be used with the PLL.

47/

# INTERRUPTS (Cont'd)

57

| Table 9. Nested Interrupts | Register | Map and | <b>Reset Values</b> |

|----------------------------|----------|---------|---------------------|

|----------------------------|----------|---------|---------------------|

| Address<br>(Hex.) | Register<br>Label    | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-------------------|----------------------|------------|------------|------------|------------|------------|------------|------------|------------|--|

|                   |                      | е          | i1         | e          | i0         | MCC        | ; + SI     |            |            |  |

| 0024h             | ISPR0<br>Reset Value | l1_3<br>1  | 10_3<br>1  | l1_2<br>1  | 10_2<br>1  | l1_1<br>1  | I0_1<br>1  | 1          | 1          |  |

|                   |                      | S          | PI         |            |            | е          | i3         | е          | 2          |  |

| 0025h             | ISPR1<br>Reset Value | l1_7<br>1  | 10_7<br>1  | l1_6<br>1  | 10_6<br>1  | l1_5<br>1  | 10_5<br>1  | 11_4<br>1  | 10_4<br>1  |  |

|                   |                      | A۱         | /D         | SCI        |            | TIM        | TIMER B    |            | TIMÉR A    |  |

| 0026h             | ISPR2<br>Reset Value | l1_11<br>1 | l0_11<br>1 | l1_10<br>1 | l0_10<br>1 | l1_9<br>1  | 10_9<br>1  | l1_8<br>1  | l0_8<br>1  |  |

|                   |                      |            |            |            |            |            |            |            |            |  |

| 0027h             | ISPR3<br>Reset Value | 1          | 1          | 1          | 1          | l1_13<br>1 | l0_13<br>1 | l1_12<br>1 | l0_12<br>1 |  |

| 0028h             | EICR<br>Reset Value  | IS11<br>0  | IS10<br>0  | IPB<br>0   | IS21<br>0  | IS20<br>0  | IPA<br>0   | 0          | 0          |  |

# POWER SAVING MODES (Cont'd)

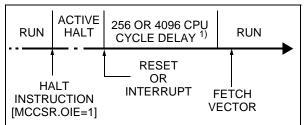

## 8.4 ACTIVE-HALT AND HALT MODES

ACTIVE-HALT and HALT modes are the two lowest power consumption modes of the MCU. They are both entered by executing the 'HALT' instruction. The decision to enter either in ACTIVE-HALT or HALT mode is given by the MCC/RTC interrupt enable flag (OIE bit in MCCSR register).

| MCCSR<br>OIE bit | Power Saving Mode entered when HALT<br>instruction is executed |

|------------------|----------------------------------------------------------------|

| 0                | HALT mode                                                      |

| 1                | ACTIVE-HALT mode                                               |

## 8.4.1 ACTIVE-HALT MODE

ACTIVE-HALT mode is the lowest power consumption mode of the MCU with a real time clock available. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is set (see Section 10.2 on page 56 for more details on the MCCSR register).

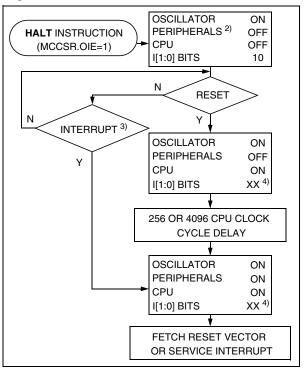

The MCU can exit ACTIVE-HALT mode on reception of either an MCC/RTC interrupt, a specific interrupt (see Table 8, "Interrupt Mapping," on page 36) or a RESET. When exiting ACTIVE-HALT mode by means of an interrupt, no 256 or 4096 CPU cycle delay occurs. The CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 26). When entering ACTIVE-HALT mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In ACTIVE-HALT mode, only the main oscillator and its associated counter (MCC/RTC) are running to keep a wake-up time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as external or auxiliary oscillator).

The safeguard against staying locked in ACTIVE-HALT mode is provided by the oscillator interrupt.

**Note:** As soon as the interrupt capability of one of the oscillators is selected (MCCSR.OIE bit set), entering ACTIVE-HALT mode while the Watchdog is active does not generate a RESET.

This means that the device cannot spend more than a defined delay in this power saving mode.

**CAUTION:** When exiting ACTIVE-HALT mode following an interrupt, OIE bit of MCCSR register must not be cleared before  $t_{DELAY}$  after the interrupt occurs ( $t_{DELAY}$  = 256 or 4096  $t_{CPU}$  delay de-

pending on option byte). Otherwise, the ST7 enters HALT mode for the remaining  $t_{\text{DELAY}}$  period.

#### Figure 25. ACTIVE-HALT Timing Overview

#### Figure 26. ACTIVE-HALT Mode Flow-chart

#### Notes:

1. This delay occurs only if the MCU exits ACTIVE-HALT mode by means of a RESET.

2. Peripheral clocked with an external clock source can still be active.

3. Only the MCC/RTC interrupt and some specific interrupts can exit the MCU from ACTIVE-HALT mode (such as external interrupt). Refer to Table 8, "Interrupt Mapping," on page 36 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

#### POWER SAVING MODES (Cont'd)

#### 8.4.2.1 Halt Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

# **10 ON-CHIP PERIPHERALS**

# **10.1 WATCHDOG TIMER (WDG)**

#### 10.1.1 Introduction

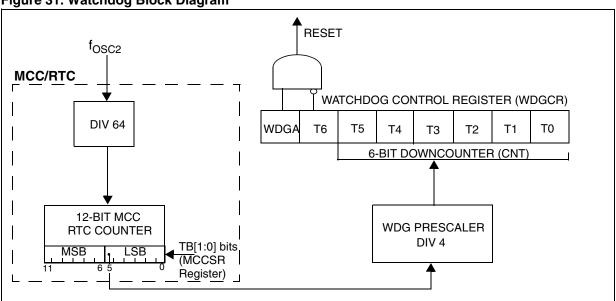

The Watchdog timer is used to detect the occurrence of a software fault, usually generated by external interference or by unforeseen logical conditions, which causes the application program to abandon its normal sequence. The Watchdog circuit generates an MCU reset on expiry of a programmed time period, unless the program refreshes the counter's contents before the T6 bit becomes cleared.

#### 10.1.2 Main Features

- Programmable free-running downcounter

- Programmable reset

- Reset (if watchdog activated) when the T6 bit reaches zero

- HALT Optional reset on instruction (configurable by option byte)

- Hardware Watchdog selectable by option byte

## 10.1.3 Functional Description

The counter value stored in the Watchdog Control register (WDGCR bits T[6:0]), is decremented every 16384 f<sub>OSC2</sub> cycles (approx.), and the length of the timeout period can be programmed by the user in 64 increments.

If the watchdog is activated (the WDGA bit is set) and when the 7-bit timer (bits T[6:0]) rolls over from 40h to 3Fh (T6 becomes cleared), it initiates a reset cycle pulling low the reset pin for typically 500ns.

The application program must write in the WDGCR register at regular intervals during normal operation to prevent an MCU reset. This downcounter is free-running: it counts down even if the watchdog is disabled. The value to be stored in the WDGCR register must be between FFh and C0h:

- The WDGA bit is set (watchdog enabled)

- The T6 bit is set to prevent generating an immediate reset

- The T[5:0] bits contain the number of increments which represents the time delay before the watchdog produces a reset (see Figure 32. Approximate Timeout Duration). The timing varies between a minimum and a maximum value due to the unknown status of the prescaler when writing to the WDGCR register (see Figure 33).

Following a reset, the watchdog is disabled. Once activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction will generate a Reset.

# Figure 31. Watchdog Block Diagram

5/

# SERIAL PERIPHERAL INTERFACE (Cont'd)

## 10.4.3.2 Slave Select Management

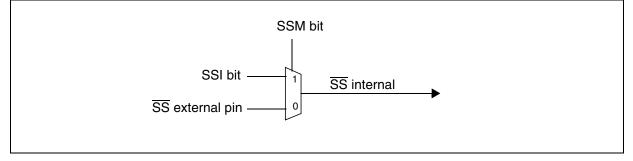

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see Figure 49)

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$ signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode:

5/

- SS internal must be held high continuously

#### In Slave Mode:

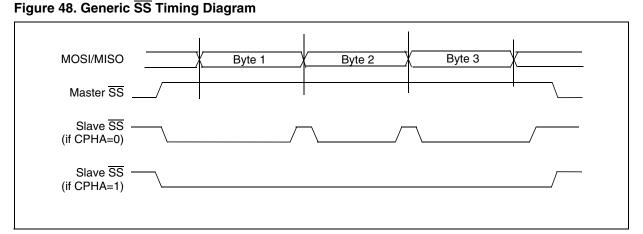

There are two cases depending on the data/clock timing relationship (see Figure 48):

- If CPHA=1 (data latched on 2nd clock edge):

- $\overline{SS}$  internal must be held low during the entire transmission. This implies that in single slave applications the  $\overline{SS}$  pin either can be tied to  $V_{SS}$ , or made free for standard I/O by managing the  $\overline{SS}$  function by software (SSM= 1 and SSI=0 in the in the SPICSR register)

If CPHA=0 (data latched on 1st clock edge):

$-\overline{SS}$  internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see Section 10.4.5.3).

## Figure 49. Hardware/Software Slave Select Management

# SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 10.4.5 Error Flags

#### 10.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device has its SS pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

#### 10.4.5.2 Overrun Condition (OVR)

An overrun condition occurs, when the master device has sent a data byte and the slave device has

not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### 10.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 10.4.3.2 Slave Select Management.

**Note:** a "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

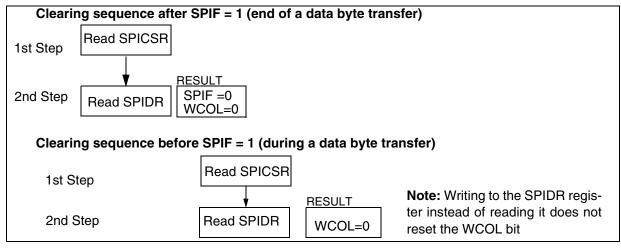

Clearing the WCOL bit is done through a software sequence (see Figure 51).

#### Figure 51. Clearing the WCOL bit (Write Collision Flag) Software Sequence

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

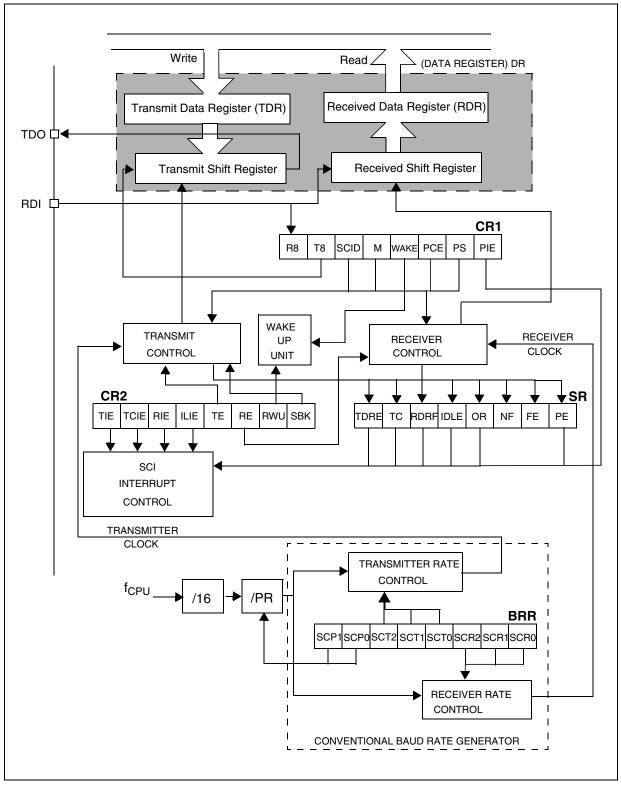

# Figure 53. SCI Block Diagram

5

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### **10.5.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 1. It contains six dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 0.1.7 for the definitions of each bit.

#### 10.5.4.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 1.).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

| 9-bit Word length (M bit is set) Possible Parity Data Frame Parity        |                                   |       |         |      |      |       |       |      | 9               | Next Data Frame |                        |

|---------------------------------------------------------------------------|-----------------------------------|-------|---------|------|------|-------|-------|------|-----------------|-----------------|------------------------|

| <br>Start                                                                 | Bi<br>Start I I I I I I I I I I I |       |         |      |      |       |       |      |                 | Ctor            | Next<br>Start          |

| Bit                                                                       | Bit0                              | Bit1  | Bit2    | Bit3 | Bit4 | Bit5  | Bit6  | Bit7 | Bit8            | Stop<br>Bit     | Bit                    |

| <br>Idle Frame                                                            |                                   |       |         |      |      |       |       |      |                 |                 | Start<br>Bit           |

| <br>1                                                                     |                                   | В     | reak Fi | rame |      |       |       |      |                 |                 | Extra Start<br>'1' Bit |

| <br><b>8-bit Word length (M bit is reset)</b><br>Data Frame Parity<br>Bit |                                   |       |         |      |      |       |       | Ne   |                 |                 |                        |

| Sta<br>Bit                                                                | Bit                               | 0 Bit | Bit2    | Bit3 | Bit  | 4 Bit | 5 Bit | 6 Bi | t7 Sto<br>Bit   |                 | art<br>t               |

|                                                                           |                                   | lc    | le Frar | ne   |      |       |       |      |                 | Sta<br>Bi       |                        |

| <br>Break Frame                                                           |                                   |       |         |      |      |       |       | Ext  | ra Start<br>Bit |                 |                        |

|                                                                           |                                   |       |         |      |      |       |       |      |                 |                 | <u> </u>               |

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### **10.6.3 Functional Description**

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{AREF}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the alloted time.

#### 10.6.3.1 A/D Converter Configuration

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the «I/O ports» chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

- Select the CS[3:0] bits to assign the analog channel to convert.

#### 10.6.3.2 Starting the Conversion

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRL register

- 3. Read the ADCDRH register. This clears EOC automatically.

**Note:** The data is not latched, so both the low and the high data register must be read before the next conversion is complete, so it is recommended to disable interrupts while reading the conversion result.

To read only 8 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRH register. This clears EOC automatically.

#### 10.6.3.3 Changing the conversion channel

The application can change channels during conversion. When software modifies the CH[3:0] bits in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

#### 10.6.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed.

| Mode | Description                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on A/D Converter                                                                                                                                                                |

|      | A/D Converter disabled.                                                                                                                                                                   |

| HALT | After wakeup from Halt mode, the A/D<br>Converter requires a stabilization time<br>t <sub>STAB</sub> (see Electrical Characteristics)<br>before accurate conversions can be<br>performed. |

#### 10.6.5 Interrupts

None.

# INSTRUCTION SET OVERVIEW (Cont'd)

#### 11.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                                 |

|----------------------------|------------------------------------------|

| NOP                        | No operation                             |

| TRAP                       | S/W Interrupt                            |

| WFI                        | Wait For Interrupt (Low Pow-<br>er Mode) |

| HALT                       | Halt Oscillator (Lowest Power<br>Mode)   |

| RET                        | Sub-routine Return                       |

| IRET                       | Interrupt Sub-routine Return             |

| SIM                        | Set Interrupt Mask (level 3)             |

| RIM                        | Reset Interrupt Mask (level 0)           |

| SCF                        | Set Carry Flag                           |

| RCF                        | Reset Carry Flag                         |

| RSP                        | Reset Stack Pointer                      |

| LD                         | Load                                     |

| CLR                        | Clear                                    |

| PUSH/POP                   | Push/Pop to/from the stack               |

| INC/DEC                    | Increment/Decrement                      |

| TNZ                        | Test Negative or Zero                    |

| CPL, NEG                   | 1 or 2 Complement                        |

| MUL                        | Byte Multiplication                      |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations              |

| SWAP                       | Swap Nibbles                             |

## 11.1.2 Immediate

Immediate instructions have two bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| CP                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

#### 11.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

#### Direct (short)

The address is a byte, thus requires only one byte after the opcode, but only allows 00 - FF addressing space.

#### Direct (long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

#### 11.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three sub-modes:

#### Indexed (No Offset)

There is no offset, (no extra byte after the opcode), and allows 00 - FF addressing space.

#### Indexed (Short)

The offset is a byte, thus requires only one byte after the opcode and allows 00 - 1FE addressing space.

#### Indexed (long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

#### 11.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer).

The pointer address follows the opcode. The indirect addressing mode consists of two sub-modes:

#### Indirect (short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

#### Indirect (long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

57

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

#### 12.5.2 Supply and Clock Managers

The previous current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode).

| Symbol                 | Parameter                                                     | Conditions           | Тур                     | Max     | Unit |

|------------------------|---------------------------------------------------------------|----------------------|-------------------------|---------|------|

| I <sub>DD(RCINT)</sub> | Supply current of internal RC oscillator 625                  |                      |                         |         |      |

| I <sub>DD(RES)</sub>   | Supply current of resonator oscillator <sup>1) &amp; 2)</sup> |                      | see S<br>12.6.3 c<br>12 | on page | μA   |

| I <sub>DD(PLL)</sub>   | PLL supply current                                            | V <sub>DD</sub> = 5V | 360                     |         | μA   |

| I <sub>DD(LVD)</sub>   | LVD supply current                                            | V <sub>DD</sub> = 5V | 150                     | 300     |      |

#### Notes:

1. Data based on characterization results done with the external components specified in Section 12.6.3, not tested in production.

2. As the oscillator is based on a current source, the consumption does not depend on the voltage.

# CLOCK CHARACTERISTICS (Cont'd)

# 12.6.4 RC Oscillators

57

| Symbol       | Parameter                                         | Conditions                                | Min | Тур | Max | Unit |

|--------------|---------------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| fosc (RCINT) | Internal RC oscillator frequency<br>See Figure 67 | T <sub>A</sub> =25°C, V <sub>DD</sub> =5V | 2   | 3.5 | 5.6 | MHz  |

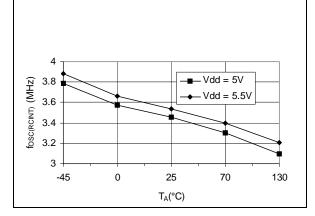

# Figure 67. Typical f<sub>OSC(RCINT)</sub> vs T<sub>A</sub>

Note: To reduce disturbance to the RC oscillator, it is recommended to place decoupling capacitors between  $V_{DD}$  and  $V_{SS}$  as shown in Figure 86

## ADC CHARACTERISTICS (Cont'd)

# 12.13.1 Analog Power Supply and Reference Pins

Depending on the MCU pin count, the package may feature separate  $V_{AREF}$  and  $V_{SSA}$  analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion. In some packages,  $V_{AREF}$  and  $V_{SSA}$  pins are not available (refer to Section 2 on page 8). In this case the analog supply and reference pads are internally bonded to the  $V_{DD}$  and  $V_{SS}$  pins.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see Section 12.13.2 General PCB Design Guidelines).

#### 12.13.2 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

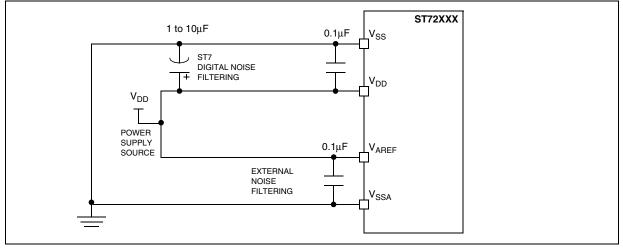

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing  $0.1\mu$ F and optionally, if needed 10pF capacitors as close as possible to the ST7 power supply pins and a 1 to  $10\mu$ F capacitor close to the power source (see Figure 86).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>AREF</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

47/

#### Figure 86. Power Supply Filtering

#### **13.3 SOLDERING INFORMATION**

47/

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK® specifications are available at www.st.com.

# 14 ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION

### **14.1 FLASH OPTION BYTES**

|         | STATIC OPTION BYTE 0 |    |            |   |    |       |       | STATIC OPTION BYTE 1 |     |          |   |   |     |   |   |      |

|---------|----------------------|----|------------|---|----|-------|-------|----------------------|-----|----------|---|---|-----|---|---|------|

|         | 7                    |    |            | 0 |    |       |       | 7                    |     |          |   |   |     |   | 0 |      |

|         | WDG                  |    | VD per var |   | ۲. | 5     | LC    | OSCTYPE              |     | OSCRANGE |   |   | DFF |   |   |      |

|         | HALT                 | SW | Rese       | 1 | 0  | Resei | Reser | FMP                  | PKG | RS.      | 1 | 0 | 2   | 1 | 0 | PLLQ |

| Default | 1                    | 1  | 1          | 0 | 0  | 1     | 1     | 1                    | 1   | 1        | 1 | 0 | 1   | 1 | 1 | 1    |

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with the internal RC clock source.

#### **OPTION BYTE 0**

OPT7= **WDG HALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

OPT6= **WDG SW** Hardware or software watchdog This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

#### OPT4:3= VD[1:0] Voltage detection

These option bits enable the voltage detection block (LVD, and AVD) with a selected threshold for the LVD and AVD.

| Selected Low Voltage Detector                    | VD1 | VD0 |

|--------------------------------------------------|-----|-----|

| LVD and AVD Off                                  | 1   | 1   |

| Lowest Voltage Threshold (V <sub>DD</sub> ~3V)   | 1   | 0   |

| Medium Voltage Threshold (V <sub>DD</sub> ~3.5V) | 0   | 1   |

| Highest Voltage Threshold (V <sub>DD</sub> ~4V)  | 0   | 0   |

**Caution:** If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed. For details on the AVD and LVD threshold levels refer to Section 12.4.1 on page 119

OPT2:1 = Reserved, must be kept at default value.

OPT0= **FMP\_R** Flash memory read-out protection Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory.

Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 7.3.1 on page 37 and the ST7 Flash Programming Reference Manual for more details.

0: Read-out protection enabled

1: Read-out protection disabled

### ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## **OPTION BYTE 1**

OPT7= **PKG1** *Pin package selection bit* This option bit selects the package.

| Version | Selected Package | PKG1 |

|---------|------------------|------|

| J       | TQFP44 / SDIP42  | 1    |

| К       | TQFP32 / SDIP32  | 0    |

**Note:** On the chip, each I/O port has 8 pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

#### OPT6 = RSTC RESET clock cycle selection

This option bit selects the number of CPU cycles applied during the RESET phase and when exiting HALT mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.

0: Reset phase with 4096 CPU cycles

1: Reset phase with 256 CPU cycles

#### OPT5:4 = OSCTYPE[1:0] Oscillator Type

These option bits select the ST7 main clock source type.

| Clock Source           | OSCTYPE |   |  |  |

|------------------------|---------|---|--|--|

| Clock Source           | 1       | 0 |  |  |

| Resonator Oscillator   | 0       | 0 |  |  |

| Reserved               | 0       | 1 |  |  |

| Internal RC Oscillator | 1       | 0 |  |  |

| External Source        | 1       | 1 |  |  |

#### OPT3:1 = **OSCRANGE[2:0]** Oscillator range

When the resonator oscillator type is selected,

these option bits select the resonator oscillator current source corresponding to the frequency range of the used resonator. Otherwise, these bits are used to select the normal operating frequency range.

| Tur |               | OSCRANGE |   |   |  |  |

|-----|---------------|----------|---|---|--|--|

| тур | . Freq. Range | 2        | 1 | 0 |  |  |

| LP  | 1~2MHz        | 0        | 0 | 0 |  |  |

| MP  | 2~4MHz        | 0        | 0 | 1 |  |  |

| MS  | 4~8MHz        | 0        | 1 | 0 |  |  |

| HS  | 8~16MHz       | 0        | 1 | 1 |  |  |

#### OPT0 = PLL OFF PLL activation

This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL must not be used with the internal RC oscillator. The PLL is guaranteed only with an input frequency between 2 and 4MHz.

0: PLL x2 enabled 1: PLL x2 disabled

**CAUTION**: the PLL can be enabled only if the "OSC RANGE" (OPT3:1) bits are configured to "MP - 2~4MHz". Otherwise, the device functionality is not guaranteed.

# DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

#### **14.2 FLASH DEVICE ORDERING INFORMATION**

With the objective of continuous improvement, ST is developing new ST72F324B devices and is transferring the production to higher capacity fabs. Refer to the following tables for guidance on ordering.

#### **Standard and Industrial Versions**

- For new designs the ST72F324B devices from to the separate ST72324B datasheet.

- For for running production orders select the devices from Table 26