Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 24                                                                      |

| Program Memory Size        | 16KB (16K × 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k4tc-tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 15.1.7 16-bit Timer PWM Mode 16   15.1.8 SCI Wrong Break duration 16   15.2 FLASH DEVICES ONLY 16 | 1 |

|---------------------------------------------------------------------------------------------------|---|

| 15.2.1 Internal RC Operation 16                                                                   |   |

| 16 IMPORTANT NOTES ON ST72F324B FLASH DEVICES:                                                    | 2 |

| 16.1 RESET PIN LOGIC LEVELS 16                                                                    | 2 |

| 16.2 WAKE-UP FROM ACTIVE HALT MODE USING EXTERNAL INTERRUPTS 16                                   | 2 |

| 16.3 PLL JITTER                                                                                   | 2 |

| 16.4 ACTIVE HALT POWER CONSUMPTION 16                                                             | 2 |

| 16.5 TIMER A REGISTERS 16                                                                         | 2 |

| 17 REVISION HISTORY                                                                               | 3 |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet.

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 159.

57

# INTERRUPTS (Cont'd)

57

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 1  | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0=11 (level 3)       | 11:0=11?              |    |   |    |   |   |   |

| JRNM        | Jump if I1:0<>11                | 11:0<>11?             |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 1  | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   |   |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  |   |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  |   |   |   |

# Table 7. Dedicated Interrupt Instruction Set

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

# Table 14. Watchdog Timer Register Map and Reset Values

# 16-BIT TIMER (Cont'd)

# 10.3.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are 2 output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC/E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

# **Procedure:**

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 16 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCRi register and CR register:

- OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \operatorname{OC}_{i} R = \frac{\Delta t * f_{CPU}}{PRESC}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 16 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}$$

i R =  $\Delta t \star f_{\text{EXT}}$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (i.e. clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

#### ALTERNATE COUNTER HIGH REGISTER (ACHR) Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

#### ALTERNATE COUNTER LOW REGISTER (ACLR) Read Only

Reset Value: 1111 1100 (FCh)

57/

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### INPUT CAPTURE 2 HIGH REGISTER (IC2HR) Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

**Note:** In Flash devices, this register is not implemented for Timer A.

#### INPUT CAPTURE 2 LOW REGISTER (IC2LR) Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, this register is not implemented for Timer A.

# 16-BIT TIMER (Cont'd)

Table 17. 16-Bit Timer Register Map and Reset Values

| Address<br>(Hex.)        | Register<br>Label | 7    | 6                 | 5    | 4                  | 3                 | 2     | 1                  | 0     |

|--------------------------|-------------------|------|-------------------|------|--------------------|-------------------|-------|--------------------|-------|

| Timer A: 32              | CR1               | ICIE | OCIE              | TOIE | FOLV2 <sup>1</sup> | FOLV1             | OLVL2 | IEDG1              | OLVL1 |

| Timer B: 42              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 31              | CR2               | OC1E | OC2E <sup>1</sup> | OPM  | PWM                | CC1               | CC0   | IEDG2 <sup>1</sup> | EXEDG |

| Timer B: 41              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 33              | CSR               | ICF1 | OCF1              | TOF  | ICF2 <sup>2</sup>  | OCF2 <sup>2</sup> | TIMD  | -                  | -     |

| Timer B: 43              | Reset Value       | х    | х                 | х    | х                  | х                 | 0     | х                  | x     |

| Timer A: 34              | IC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 44              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 35              | IC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 45              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 36              | OC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 46              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 37              | OC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 47              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3E <sup>3</sup> | OC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4E              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3F <sup>3</sup> | OC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4F              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 38              | CHR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 48              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 39              | CLR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 49              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3A              | ACHR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4A              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 3B              | ACLR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4B              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3C <sup>4</sup> | IC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4C              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

| Timer A: 3D <sup>4</sup> | IC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4D              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

<sup>1</sup> In Flash devices, these bits are not used in Timer A and must be kept cleared.

<sup>2</sup> In Flash devices, these bits are forced by hardware to 0 in Timer A

<sup>3</sup> In Flash devices, the TAOC2HR and TAOC2LR Registers are write only, reading them will return undefined values

<sup>4</sup> In Flash devices, the TAIC2HR and TAIC2LR registers are not present.

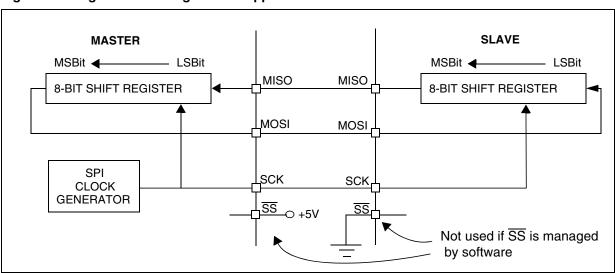

# SERIAL PERIPHERAL INTERFACE (Cont'd)

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master MCU.

#### 10.4.3.1 Functional Description

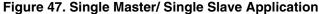

A basic example of interconnections between a single master and a single slave is illustrated in Figure 47.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 50) but master and slave must be programmed with the same timing mode.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

# 10.4.5.4 Single Master Systems

57/

A typical single master system may be configured, using an MCU as the master and four MCUs as slaves (see Figure 52).

The master device selects the individual slave devices by using four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

# SERIAL PERIPHERAL INTERFACE (Cont'd) 10.4.8 Register Description CONTROL REGISTER (SPICR)

#### Read/Write

Reset Value: 0000 xxxx (0xh)

| 7    |     |      |      |      |      |      |      |  |  |

|------|-----|------|------|------|------|------|------|--|--|

| SPIE | SPE | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |  |  |

# Bit 7 = **SPIE** Serial Peripheral Interrupt Enable. This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SPI interrupt is generated whenever SPIF=1, MODF=1 or OVR=1 in the SPICSR register

# Bit 6 = **SPE** Serial Peripheral Output Enable.

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS}=0$  (see Section 10.4.5.1 Master Mode Fault (MODF)). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.

0: I/O pins free for general purpose I/O 1: SPI I/O pin alternate functions enabled

#### Bit 5 = SPR2 Divider Enable.

This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to Table 18 SPI Master mode SCK Frequency.

0: Divider by 2 enabled

1: Divider by 2 disabled

Note: This bit has no effect in slave mode.

# Bit 4 = MSTR Master Mode.

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS}=0$  (see Section 10.4.5.1 Master Mode Fault (MODF)).

- 0: Slave mode

- 1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.

#### Bit 3 = CPOL Clock Polarity.

This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.

0: SCK pin has a low level idle state 1: SCK pin has a high level idle state

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Bit 2 = CPHA Clock Phase.

This bit is set and cleared by software.

- 0: The first clock transition is the first data capture edge.

- 1: The second clock transition is the first capture edge.

**Note:** The slave must have the same CPOL and CPHA settings as the master.

#### Bits 1:0 = **SPR[1:0]** Serial Clock Frequency.

These bits are set and cleared by software. Used with the SPR2 bit, they select the baud rate of the SPI serial clock SCK output by the SPI in master mode.

Note: These 2 bits have no effect in slave mode.

#### Table 18. SPI Master mode SCK Frequency

| Serial Clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    | 0    | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    | 0    | 1    |

| f <sub>CPU</sub> /32  | 1    | 1    | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |

| f <sub>CPU</sub> /128 | 0    | 1    | 1    |

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) EXTENDED RECEIVE PRESCALER DIVISION REGISTER (SCIERPR)

# Read/Write

Reset Value: 0000 0000 (00h)

Allows setting of the Extended Prescaler rate division factor for the receive circuit.

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ERPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

# Bits 7:0 = **ERPR[7:0]** 8-bit Extended Receive Prescaler Register.

The extended Baud Rate Generator is activated when a value different from 00h is stored in this register. Therefore the clock frequency issued from the 16 divider (see Figure 3.) is divided by the binary factor set in the SCIERPR register (in the range 1 to 255).

The extended baud rate generator is not used after a reset.

# Table 21. Baudrate Selection

# EXTENDED TRANSMIT PRESCALER DIVISION REGISTER (SCIETPR)

# Read/Write

Reset Value:0000 0000 (00h)

Allows setting of the External Prescaler rate division factor for the transmit circuit.

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ETPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

# Bits 7:0 = **ETPR[7:0]** 8-bit Extended Transmit Prescaler Register.

The extended Baud Rate Generator is activated when a value different from 00h is stored in this register. Therefore the clock frequency issued from the 16 divider (see Figure 3.) is divided by the binary factor set in the SCIETPR register (in the range 1 to 255).

The extended baud rate generator is not used after a reset.

47/

|                                    |                         |                  | Cor                     | nditions                                                                                                                                                                                                              |          | Baud                             |      |

|------------------------------------|-------------------------|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------|------|

| Symbol                             | Parameter               | f <sub>CPU</sub> | Accuracy vs<br>Standard | Prescaler                                                                                                                                                                                                             | Standard | Rate                             | Unit |

| f <sub>Tx</sub><br>f <sub>Rx</sub> | Communication frequency | 8 MHz            | ~0.16%                  | Conventional Mode<br>TR (or RR)=128, PR=13<br>TR (or RR)= 32, PR=13<br>TR (or RR)= 16, PR=13<br>TR (or RR)= 8, PR=13<br>TR (or RR)= 4, PR=13<br>TR (or RR)= 16, PR= 3<br>TR (or RR)= 2, PR=13<br>TR (or RR)= 1, PR=13 | 19200    | ~1201.92<br>~2403.84<br>~4807.69 | Hz   |

|                                    |                         |                  | ~0.79%                  | Extended Mode<br>ETPR (or ERPR) = 35,<br>TR (or RR)= 1, PR=1                                                                                                                                                          | 14400    | ~14285.71                        |      |

# SERIAL COMMUNICATION INTERFACE (Cont'd)

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0050h             | SCISR             | TDRE | TC   | RDRF | IDLE | OR   | NF   | FE   | PE   |

| 005011            | Reset Value       | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0051h             | SCIDR             | MSB  |      |      |      |      |      |      | LSB  |

| 005111            | Reset Value       | х    | х    | х    | х    | х    | х    | х    | х    |

| 0052h             | SCIBRR            | SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

| 005211            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0053h             | SCICR1            | R8   | T8   | SCID | М    | WAKE | PCE  | PS   | PIE  |

| 005511            | Reset Value       | х    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0054h             | SCICR2            | TIE  | TCIE | RIE  | ILIE | TE   | RE   | RWU  | SBK  |

| 005411            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0055h             | SCIERPR           | MSB  |      |      |      |      |      |      | LSB  |

| 005511            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0057h             | SCIPETPR          | MSB  |      |      |      |      |      |      | LSB  |

| 005711            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

# Table 22. SCI Register Map and Reset Values

57

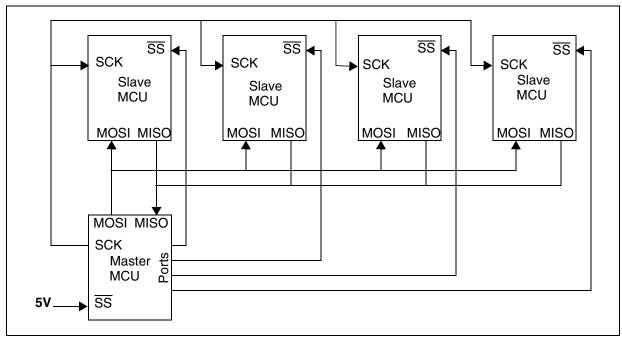

# 10.6 10-BIT A/D CONVERTER (ADC)

# **10.6.1 Introduction**

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

# 10.6.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

**47**/

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 57.

# Figure 57. ADC Block Diagram

# **10-BIT A/D CONVERTER** (Cont'd)

57

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

# Table 23. ADC Register Map and Reset Values

# INSTRUCTION SET OVERVIEW (Cont'd)

# 11.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

## Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

# Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table25. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressing ModesIndirectIndexedIndirect

| Long and Short<br>Instructions | Function                                           |

|--------------------------------|----------------------------------------------------|

| LD                             | Load                                               |

| CP                             | Compare                                            |

| AND, OR, XOR                   | Logical Operations                                 |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Sub-<br>stractions operations |

| BCP                            | Bit Compare                                        |

| Short Instructions<br>Only | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Opera-<br>tions  |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

# 11.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset is following the opcode.

#### Relative (Indirect)

The offset is defined in memory, which address follows the opcode.

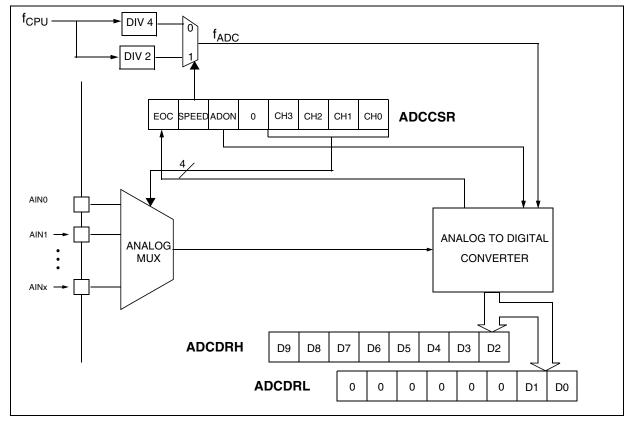

# **CLOCK CHARACTERISTICS** (Cont'd)

# **12.6.5 PLL Characteristics**

| Symbol                                         | Parameter                              | Conditions                                   | Min | Тур | Max | Unit |

|------------------------------------------------|----------------------------------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>OSC</sub>                               | PLL input frequency range              |                                              | 2   |     | 4   | MHz  |

| $\Delta  \mathrm{f_{CPU}} /  \mathrm{f_{CPU}}$ | Instantaneous PLL jitter <sup>1)</sup> | Flash ST72F324,<br>f <sub>OSC</sub> = 4 MHz. |     | 1.0 | 2.5 | 0/   |

|                                                | -                                      | Flash ST72F324,<br>f <sub>OSC</sub> = 2 MHz. |     | 2.5 | 4.0 | %    |

#### Note:

1. Data characterized but not tested.

The user must take the PLL jitter into account in the application (for example in serial communication or sampling of high frequency signals). The PLL jitter is a periodic effect, which is integrated over several CPU cycles. Therefore the longer the period of the application signal, the less it will be impacted by the PLL jitter.

Figure 68 shows the PLL jitter integrated on application signals in the range 125kHz to 2MHz. At frequencies of less than 125KHz, the jitter is negligible.

#### Figure 68. Integrated PLL Jitter vs signal frequency<sup>1</sup>

Note 1: Measurement conditions: f<sub>CPU</sub> = 8MHz.

# **12.7 MEMORY CHARACTERISTICS**

# 12.7.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

# 12.7.2 FLASH Memory

| DUAL VOL                                | DUAL VOLTAGE HDFLASH MEMORY                   |                             |                   |     |                   |        |  |  |  |  |  |

|-----------------------------------------|-----------------------------------------------|-----------------------------|-------------------|-----|-------------------|--------|--|--|--|--|--|

| Symbol                                  | Parameter                                     | Conditions                  | Min <sup>2)</sup> | Тур | Max <sup>2)</sup> | Unit   |  |  |  |  |  |

| f                                       | Operating frequency                           | Read mode                   | 0                 | 0   |                   | MHz    |  |  |  |  |  |

| f <sub>CPU</sub>                        | Operating frequency                           | Write / Erase mode          | 1                 |     | 8                 |        |  |  |  |  |  |

| V <sub>PP</sub>                         | Programming voltage <sup>3)</sup>             | $4.5V \le V_{DD} \le 5.5V$  | 11.4              |     | 12.6              | V      |  |  |  |  |  |

| I <sub>DD</sub>                         | Supply current <sup>4)</sup>                  | Write / Erase               |                   | 0   |                   | mA     |  |  |  |  |  |

| 1                                       | V ourropt <sup>4)</sup>                       | Read (V <sub>PP</sub> =12V) |                   |     | 200               | μA     |  |  |  |  |  |

| I <sub>PP</sub>                         | V <sub>PP</sub> current <sup>4)</sup>         | Write / Erase               |                   |     | 30                | mA     |  |  |  |  |  |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time   |                             |                   | 10  |                   | μs     |  |  |  |  |  |

| t <sub>RET</sub>                        | Data retention                                | T <sub>A</sub> =55°C        | 20                |     |                   | years  |  |  |  |  |  |

| N <sub>RW</sub>                         | Write erase cycles                            | T <sub>A</sub> =25°C        | 100               |     |                   | cycles |  |  |  |  |  |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing tempera-<br>ture range |                             | -40               | 25  | 85                | °C     |  |  |  |  |  |

# Notes:

47/

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Not tested in production.

2. Data based on characterization results, not tested in production.

3. V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons.

4. Data based on simulation results, not tested in production.

# 10-BIT ADC CHARACTERISTICS (Cont'd)

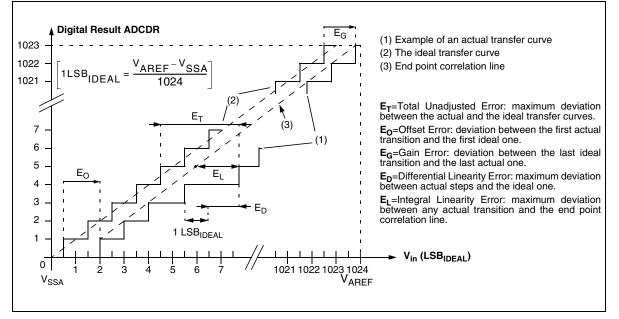

# 12.13.3 ADC Accuracy

Conditions:  $V_{DD}=5V^{(1)}$

| Symbol            | Parameter                            | Conditions                                | Flash I | Unit |     |

|-------------------|--------------------------------------|-------------------------------------------|---------|------|-----|

| Symbol Parameter  |                                      | Conditions                                | Тур     | Omt  |     |

| IE <sub>T</sub> I | Total unadjusted error <sup>1)</sup> |                                           | 4       | 6    |     |

| IE <sub>O</sub> I | Offset error 1)                      |                                           | 3       | 5    |     |

| IE <sub>G</sub> I | Gain Error <sup>1)</sup>             |                                           | 0.5     | 4.5  | LSB |

| IE <sub>D</sub> I | Differential linearity error 1)      | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1.5     | 4.5  |     |

| IELI              | Integral linearity error 1)          | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1.5     | 4.5  |     |

#### Notes:

1. ADC Accuracy vs. Negative Injection Current: Injecting negative current may reduce the accuracy of the conversion being performed on another analog input.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.9 does not affect the ADC accuracy.

2. Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to 125°C ( $\pm$  3 $\sigma$  distribution limits).

# Figure 87. ADC Accuracy Characteristics

# 14 ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION

# **14.1 FLASH OPTION BYTES**

|         | STATIC OPTION BYTE 0 |    |       |   |   |       |       |     |     | STATIC OPTION BYTE 1 |         |   |   |   |    |      |

|---------|----------------------|----|-------|---|---|-------|-------|-----|-----|----------------------|---------|---|---|---|----|------|

|         | 7                    |    |       |   |   |       |       | 0   | 7   |                      |         |   |   |   |    | 0    |

|         | WI                   | DG | rved  | v | D | rved  | rved  | ш   | 5   | TC                   | OSCTYPE |   |   |   | GE | DFF  |

|         | НАLТ                 | SW | Resei | 1 | 0 | Resei | Reser | FMP | PKG | RS.                  | 1       | 0 | 2 | 1 | 0  | PLLQ |

| Default | 1                    | 1  | 1     | 0 | 0 | 1     | 1     | 1   | 1   | 1                    | 1       | 0 | 1 | 1 | 1  | 1    |

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with the internal RC clock source.

# **OPTION BYTE 0**

OPT7= **WDG HALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

OPT6= **WDG SW** Hardware or software watchdog This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

# OPT4:3= VD[1:0] Voltage detection

These option bits enable the voltage detection block (LVD, and AVD) with a selected threshold for the LVD and AVD.

| Selected Low Voltage Detector                    | VD1 | VD0 |

|--------------------------------------------------|-----|-----|

| LVD and AVD Off                                  | 1   | 1   |

| Lowest Voltage Threshold (V <sub>DD</sub> ~3V)   | 1   | 0   |

| Medium Voltage Threshold (V <sub>DD</sub> ~3.5V) | 0   | 1   |

| Highest Voltage Threshold (V <sub>DD</sub> ~4V)  | 0   | 0   |

**Caution:** If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed. For details on the AVD and LVD threshold levels refer to Section 12.4.1 on page 119

OPT2:1 = Reserved, must be kept at default value.

OPT0= **FMP\_R** Flash memory read-out protection Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory.

Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 7.3.1 on page 37 and the ST7 Flash Programming Reference Manual for more details.

0: Read-out protection enabled

1: Read-out protection disabled

# **14.5 ST7 APPLICATION NOTES**

# Table 30. ST7 Application Notes

| IDENTIFICATION        | DESCRIPTION                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------|

| APPLICATION EXAMPLES  |                                                                                               |

| AN1658                | SERIAL NUMBERING IMPLEMENTATION                                                               |

| AN1720                | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                                    |

| AN1755                | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                                   |

| EXAMPLE DRIVERS       |                                                                                               |

| AN 969                | SCI COMMUNICATION BETWEEN ST7 AND PC                                                          |

| AN 970                | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                                      |

| AN 972                | ST7 SOFTWARE SPI MASTER COMMUNICATION                                                         |

| AN 973                | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                               |

| AN 974                | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                                 |

| AN 976                | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                               |

| AN 979                | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                                   |

| AN 980                | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                             |

| AN1041                | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                                     |

| AN1044                | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                                            |

| AN1046                | UART EMULATION SOFTWARE                                                                       |

| AN1047                | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                                        |

| AN1048                | ST7 SOFTWARE LCD DRIVER                                                                       |

| AN1078                | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                                  |

| AN1445                | EMULATED 16 BIT SLAVE SPI                                                                     |

| AN1504                | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER                       |

| GENERAL PURPOSE       |                                                                                               |

| AN1476                | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                                     |

| AN1709                | EMC DESIGN FOR ST MICROCONTROLLERS                                                            |

| AN1752                | ST72324 QUICK REFERENCE NOTE                                                                  |

| PRODUCT EVALUATION    |                                                                                               |

| AN 910                | PERFORMANCE BENCHMARKING                                                                      |

| AN 990                | ST7 BENEFITS VERSUS INDUSTRY STANDARD                                                         |

| AN1150                | BENCHMARK ST72 VS PC16                                                                        |

| AN1151                | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                                             |

| AN1278                | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                                    |

| PRODUCT MIGRA         |                                                                                               |

| AN1131                | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324                            |

| AN2197                | GUIDELINES FOR MIGRATING ST72F324 & ST72F321 APPLICATIONS TO ST72F324B, ST72F321B OR ST72F325 |

| PRODUCT OPTIMIZATION  |                                                                                               |

| AN 982                | USING ST7 WITH CERAMIC RESONATOR                                                              |

| AN1014                | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                                     |

| AN1015                | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                             |

| AN1070                | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                                         |

| AN1181                | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                                                 |

| AN1502                | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                                  |

| AN1530                | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLA-<br>TOR              |

| AN1636                | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                                            |

| PROGRAMMING AND TOOLS |                                                                                               |

# **15 KNOWN LIMITATIONS**

# **15.1 ALL DEVICES**

# 15.1.1 External RC option

The External RC clock source option described in previous datasheet revisions is no longer supported and has been removed from this specification.

# 15.1.2 CSS Function

The Clock Security System function has been removed from the datasheet.

#### 15.1.3 Safe Connection of OSC1/OSC2 Pins

The OSC1 and/or OSC2 pins must not be left unconnected otherwise the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. Refer to Section 6.2 on page 24.

#### 15.1.4 Unexpected Reset Fetch

If an interrupt request occurs while a "POP CC" instruction is executed, the interrupt controller does not recognise the source of the interrupt and, by default, passes the RESET vector address to the CPU.

#### Workaround

To solve this issue, a "POP CC" instruction must always be preceded by a "SIM" instruction.

# 15.1.5 Clearing active interrupts outside interrupt routine

When an active interrupt request occurs at the same time as the related flag is being cleared, an unwanted reset may occur.

**Note:** clearing the related interrupt mask will not generate an unwanted reset

#### Concurrent interrupt context

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request.

Example:

SIM

reset interrupt flag

RIM

# Nested interrupt context:

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

PUSH CC SIM reset interrupt flag

POP CC

# 15.1.6 External Interrupt Missed

To avoid any risk of generating a parasitic interrupt, the edge detector is automatically disabled for one clock cycle during an access to either DDR and OR. Any input signal edge during this period will not be detected and will not generate an interrupt.

This case can typically occur if the application refreshes the port configuration registers at intervals during runtime.

#### Workaround

The workaround is based on software checking the level on the interrupt pin before and after writing to the PxOR or PxDDR registers. If there is a level change (depending on the sensitivity programmed for this pin) the interrupt routine is invoked using the call instruction with three extra PUSH instructions before executing the interrupt routine (this is to make the call compatible with the IRET instruction at the end of the interrupt service routine).

But detection of the level change does ensure that edge occurs during the critical 1 cycle duration and the interrupt has been missed. This may lead to occurrence of same interrupt twice (one hardware and another with software call).

57