Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k6t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 15.1.7 16-bit Timer PWM Mode 16   15.1.8 SCI Wrong Break duration 16   15.2 FLASH DEVICES ONLY 16 | 1 |

|---------------------------------------------------------------------------------------------------|---|

| 15.2.1 Internal RC Operation 16                                                                   |   |

| 16 IMPORTANT NOTES ON ST72F324B FLASH DEVICES:                                                    | 2 |

| 16.1 RESET PIN LOGIC LEVELS 16                                                                    | 2 |

| 16.2 WAKE-UP FROM ACTIVE HALT MODE USING EXTERNAL INTERRUPTS 16                                   | 2 |

| 16.3 PLL JITTER                                                                                   | 2 |

| 16.4 ACTIVE HALT POWER CONSUMPTION 16                                                             | 2 |

| 16.5 TIMER A REGISTERS 16                                                                         | 2 |

| 17 REVISION HISTORY                                                                               | 3 |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet.

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 159.

57

## Table 2. Hardware Register Map

| Address              | Block                | Register<br>Label | Register Name                                | Reset<br>Status   | Remarks           |

|----------------------|----------------------|-------------------|----------------------------------------------|-------------------|-------------------|

| 0000h                | Port A <sup>2)</sup> | PADR              | Port A Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0001h                |                      | PADDR             | Port A Data Direction Register               | 00h               | R/W               |

| 0002h                |                      | PAOR              | Port A Option Register                       | 00h               | R/W               |

| 0003h                | Port B <sup>2)</sup> | PBDR              | Port B Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0004h                |                      | PBDDR             | Port B Data Direction Register               | 00h               | R/W               |

| 0005h                |                      | PBOR              | Port B Option Register                       | 00h               | R/W               |

| 0006h                | Port C               | PCDR              | Port C Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0007h                |                      | PCDDR             | Port C Data Direction Register               | 00h               | R/W               |

| 0008h                |                      | PCOR              | Port C Option Register                       | 00h               | R/W               |

| 0009h                | Port D <sup>2)</sup> | PDADR             | Port D Data Register                         | 00h <sup>1)</sup> | R/W               |

| 000Ah                |                      | PDDDR             | Port D Data Direction Register               | 00h               | R/W               |

| 000Bh                |                      | PDOR              | Port D Option Register                       | 00h               | R/W               |

| 000Ch                | Port E <sup>2)</sup> | PEDR              | Port E Data Register                         | 00h <sup>1)</sup> | R/W               |

| 000Dh                |                      | PEDDR             | Port E Data Direction Register               | 00h               | R/W <sup>2)</sup> |

| 000Eh                |                      | PEOR              | Port E Option Register                       | 00h               | R/W <sup>2)</sup> |

| 000Fh                | Port F <sup>2)</sup> | PFDR              | Port F Data Register                         | 00h <sup>1)</sup> | R/W               |

| 0010h                |                      | PFDDR             | Port F Data Direction Register               | 00h               | R/W               |

| 0011h                |                      | PFOR              | Port F Option Register                       | 00h               | R/W               |

| 0012h<br>to<br>0020h |                      |                   | Reserved Area (15 Bytes)                     |                   | ·                 |

| 0021h                | SPI                  | SPIDR             | SPI Data I/O Register                        | xxh               | R/W               |

| 0022h                |                      | SPICR             | SPI Control Register                         | 0xh               | R/W               |

| 0023h                |                      | SPICSR            | SPI Control/Status Register                  | 00h               | R/W               |

| 0024h                | ITC                  | ISPR0             | Interrupt Software Priority Register 0       | FFh               | R/W               |

| 0025h                |                      | ISPR1             | Interrupt Software Priority Register 1       | FFh               | R/W               |

| 0026h                |                      | ISPR2             | Interrupt Software Priority Register 2       | FFh               | R/W               |

| 0027h                |                      | ISPR3             | Interrupt Software Priority Register 3       | FFh               | R/W               |

| 0028h                |                      | EICR              | External Interrupt Control Register          | 00h               | R/W               |

| 0029h                | FLASH                | FCSR              | Flash Control/Status Register                | 00h               | R/W               |

| 002Ah                | WATCHDOG             | WDGCR             | Watchdog Control Register                    | 7Fh               | R/W               |

| 002Bh                | SI                   | SICSR             | System Integrity Control Status Register     | xxh               | R/W               |

| 002Ch                | MCC                  | MCCSR             | Main Clock Control / Status Register         | 00h               | R/W               |

| 002Dh                |                      | MCCBCR            | Main Clock Controller: Beep Control Register | 00h               | R/W               |

| 002Eh<br>to<br>0030h |                      |                   | Reserved Area (3 Bytes)                      |                   |                   |

# **4 FLASH PROGRAM MEMORY**

## 4.1 Introduction

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external  $V_{PP}$  supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

## 4.2 Main Features

- Three Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

## 4.3 Structure

5/

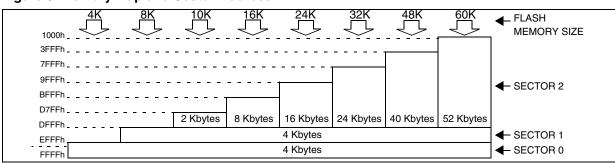

The Flash memory is organised in sectors and can be used for both code and data storage.

Figure 6. Memory Map and Sector Address

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see Table 3). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see Figure 6). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

#### Table 3. Sectors available in Flash devices

| Flash Size (bytes) | Available Sectors |

|--------------------|-------------------|

| 4K                 | Sector 0          |

| 8K                 | Sectors 0,1       |

| > 8K               | Sectors 0,1, 2    |

#### 4.3.1 Read-out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

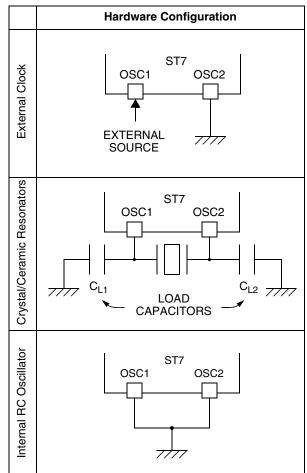

# 6.2 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by three different source types coming from the multi-oscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 5. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

#### **External Clock Source**

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

#### **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to Section 14.1 on page 150 for more details on the frequency ranges). In this mode of the multioscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

In order not to exceed the max. operating frequency, the internal RC oscillator must not be used with the PLL.

47/

# INTERRUPTS (Cont'd)

## Table 8. Interrupt Mapping

| N° | Source<br>Block | Description                               | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT/<br>ACTIVE<br>HALT <sup>1)</sup> | Address<br>Vector |

|----|-----------------|-------------------------------------------|-------------------|-------------------|-------------------------------------------------------|-------------------|

|    | RESET           | Reset N/A                                 |                   |                   | yes                                                   | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                        | N/A               |                   | no                                                    | FFFCh-FFFDh       |

| 0  |                 | Not used                                  |                   |                   | FFFAh-FFFBh                                           |                   |

| 1  | MCC/RTC         | Main clock controller time base interrupt | MCCSR High        |                   | yes                                                   | FFF8h-FFF9h       |

| 2  | ei0             | External interrupt port A30               |                   | Priority          | yes                                                   | FFF6h-FFF7h       |

| 3  | ei1             | External interrupt port F20               | N/A               |                   | yes                                                   | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt port B30               |                   |                   | yes                                                   | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt port B74               |                   |                   | yes                                                   | FFF0h-FFF1h       |

| 6  |                 | Not used                                  |                   |                   |                                                       | FFEEh-FFEFh       |

| 7  | SPI             | SPI peripheral interrupts                 | SPICSR            | ▼                 | yes                                                   | FFECh-FFEDh       |

| 8  | TIMER A         | TIMER A peripheral interrupts             | TASR              | Ī                 | no                                                    | FFEAh-FFEBh       |

| 9  | TIMER B         | TIMER B peripheral interrupts             | TBSR              | Ī                 | no                                                    | FFE8h-FFE9h       |

| 10 | SCI             | SCI Peripheral interrupts SCISR           |                   | Lower             | no                                                    | FFE6h-FFE7h       |

| 11 | AVD             | Auxiliary Voltage detector interrupt      | SICSR             | Priority          | no                                                    | FFE4h-FFE5h       |

#### Notes:

1. In Flash devices only a RESET or MCC/RTC interrupt can be used to wake-up from Active Halt mode.

## 7.6 EXTERNAL INTERRUPTS

## 7.6.1 I/O Port Interrupt Sensitivity

The external interrupt sensitivity is controlled by the IPA, IPB and ISxx bits of the EICR register (Figure 21). This control allows to have up to 4 fully independent external interrupt source sensitivities.

Each external interrupt source can be generated on four (or five) different events on the pin:

- Falling edge

- Rising edge

- Falling and rising edge

- Falling edge and low level

- Rising edge and high level (only for ei0 and ei2)

To guarantee correct functionality, the sensitivity bits in the EICR register can be modified only when the I1 and I0 bits of the CC register are both set to 1 (level 3). This means that interrupts must be disabled before changing sensitivity.

The pending interrupts are cleared by writing a different value in the ISx[1:0], IPA or IPB bits of the EICR.

## POWER SAVING MODES (Cont'd)

#### 8.4.2.1 Halt Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

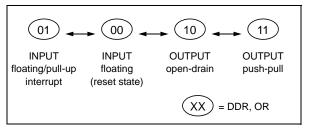

#### 9.3 I/O PORT IMPLEMENTATION

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 30 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 30. Interrupt I/O Port State Transitions

#### 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

#### 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |  |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|--|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  | Yes                  |  |

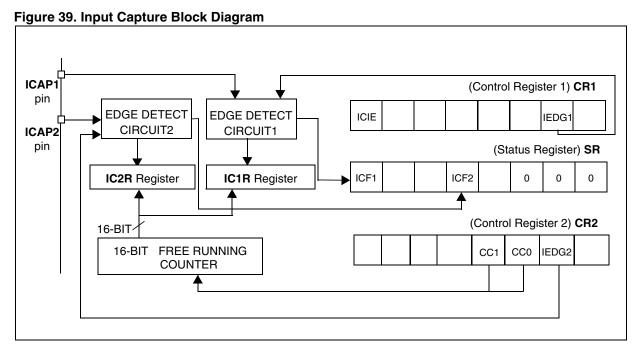

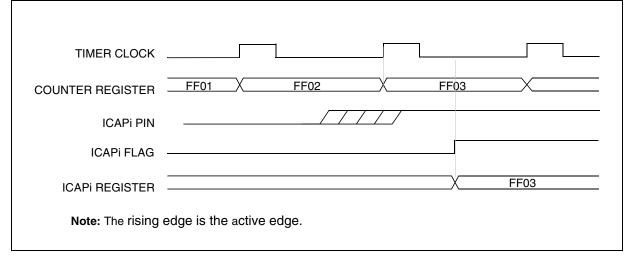

## 16-BIT TIMER (Cont'd)

## Figure 40. Input Capture Timing Diagram

## 16-BIT TIMER (Cont'd)

57

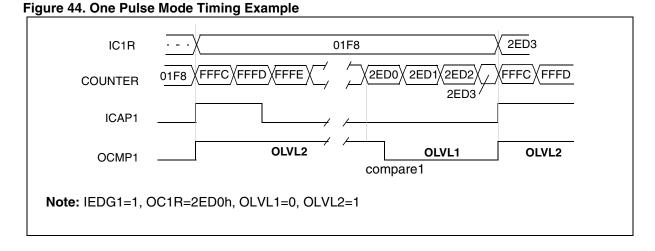

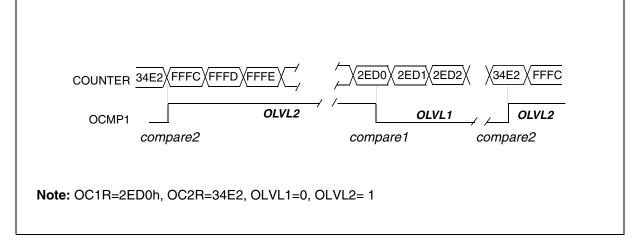

Figure 45. Pulse Width Modulation Mode Timing Example with 2 Output Compare Functions

# 16-BIT TIMER (Cont'd)

Table 17. 16-Bit Timer Register Map and Reset Values

| Address<br>(Hex.)        | Register<br>Label | 7    | 6                 | 5    | 4                  | 3                 | 2     | 1                  | 0     |

|--------------------------|-------------------|------|-------------------|------|--------------------|-------------------|-------|--------------------|-------|

| Timer A: 32              | CR1               | ICIE | OCIE              | TOIE | FOLV2 <sup>1</sup> | FOLV1             | OLVL2 | IEDG1              | OLVL1 |

| Timer B: 42              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 31              | CR2               | OC1E | OC2E <sup>1</sup> | OPM  | PWM                | CC1               | CC0   | IEDG2 <sup>1</sup> | EXEDG |

| Timer B: 41              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 33              | CSR               | ICF1 | OCF1              | TOF  | ICF2 <sup>2</sup>  | OCF2 <sup>2</sup> | TIMD  | -                  | -     |

| Timer B: 43              | Reset Value       | х    | х                 | х    | х                  | х                 | 0     | х                  | x     |

| Timer A: 34              | IC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 44              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 35              | IC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 45              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | x     |

| Timer A: 36              | OC1HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 46              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 37              | OC1LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 47              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3E <sup>3</sup> | OC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4E              | Reset Value       | 1    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 3F <sup>3</sup> | OC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4F              | Reset Value       | 0    | 0                 | 0    | 0                  | 0                 | 0     | 0                  | 0     |

| Timer A: 38              | CHR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 48              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 39              | CLR               | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 49              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3A              | ACHR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4A              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 1                  | 1     |

| Timer A: 3B              | ACLR              | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4B              | Reset Value       | 1    | 1                 | 1    | 1                  | 1                 | 1     | 0                  | 0     |

| Timer A: 3C <sup>4</sup> | IC2HR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4C              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

| Timer A: 3D <sup>4</sup> | IC2LR             | MSB  |                   |      |                    |                   |       |                    | LSB   |

| Timer B: 4D              | Reset Value       | х    | х                 | х    | х                  | х                 | х     | х                  | х     |

<sup>1</sup> In Flash devices, these bits are not used in Timer A and must be kept cleared.

<sup>2</sup> In Flash devices, these bits are forced by hardware to 0 in Timer A

<sup>3</sup> In Flash devices, the TAOC2HR and TAOC2LR Registers are write only, reading them will return undefined values

<sup>4</sup> In Flash devices, the TAIC2HR and TAIC2LR registers are not present.

# **10.4 SERIAL PERIPHERAL INTERFACE (SPI)**

## 10.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves however the SPI interface can not be a master in a multi-master system.

#### 10.4.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

57/

Write collision, Master Mode Fault and Overrun flags **Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

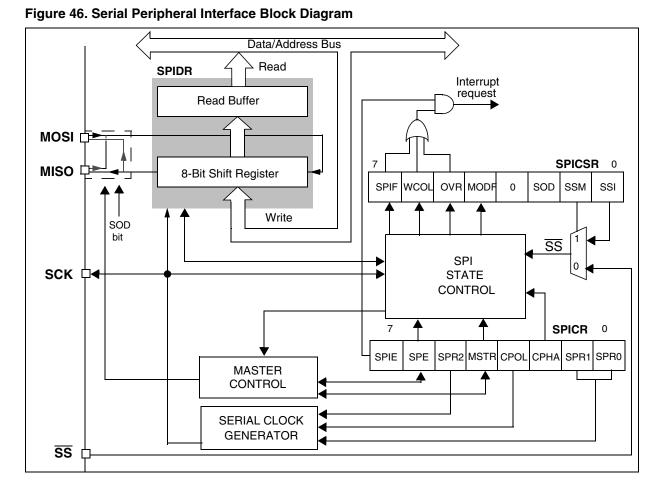

#### 10.4.3 General Description

Figure 46 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 4 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

## **10.5 SERIAL COMMUNICATIONS INTERFACE (SCI)**

## 10.5.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 10.5.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

#### **10.5.3 General Description**

The interface is externally connected to another device by two pins (see Figure 2.):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

## **10.6.6 Register Description**

## **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   | 7     |      |   |     |     |     |     |  |

|-----|-------|------|---|-----|-----|-----|-----|--|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |  |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by hardware when software reads the ADCDRH register or writes to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = **SPEED** ADC clock selection This bit is set and cleared by software. 0:  $f_{ADC} = f_{CPU}/4$ 1:  $f_{ADC} = f_{CPU}/2$

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **Reserved.** Must be kept cleared.

#### Bit 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 1   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

\*The number of channels is device dependent. Refer to the device pinout description.

#### **DATA REGISTER (ADCDRH)**

Read Only Reset Value: 0000 0000 (00h)

7

|    |    | l. | l. | l. | r. | r. | r. |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

|    |    |    |    |    |    |    |    |

0

Bit 7:0 = D[9:2] MSB of Converted Analog Value

## DATA REGISTER (ADCDRL)

Read Only Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 = Reserved. Forced by hardware to 0.

Bit 1:0 = **D**[1:0] *LSB of Converted Analog Value*

# I/O PORT PIN CHARACTERISTICS (Cont'd)

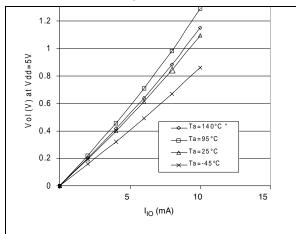

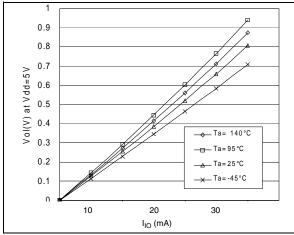

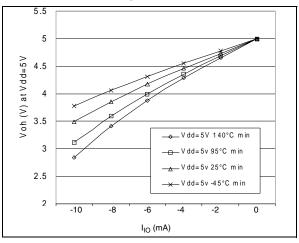

# 12.9.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                        | Parameter                                                                                                                                                                                                                         | Conditions |                                                                    | Min                  | Max        | Unit |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------|----------------------|------------|------|

|                               | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 71)<br>Output low level voltage for a high sink I/O pin<br>when 4 pins are sunk at same time<br>(see Figure 72 and Figure 74) |            | I <sub>IO</sub> =+5mA                                              |                      | 1.2        |      |

| V <sub>OL</sub> <sup>1)</sup> |                                                                                                                                                                                                                                   | )=5V       | I <sub>IO</sub> =+2mA                                              |                      | 0.5        |      |

|                               |                                                                                                                                                                                                                                   |            | I <sub>IO</sub> =+20mA, T <sub>A</sub> ≤85°<br>T <sub>A</sub> >85° |                      | 1.3<br>1.5 | V    |

|                               |                                                                                                                                                                                                                                   | VDD        | I <sub>IO</sub> =+8mA                                              |                      | 0.6        |      |

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time                                                                                                                                                     |            | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤85°<br>T <sub>A</sub> >85°  |                      |            |      |

|                               | (see Figure 73 and Figure 76)                                                                                                                                                                                                     |            | I <sub>IO</sub> =-2mA                                              | V <sub>DD</sub> -0.7 |            | 1    |

# Figure 71. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (std. ports)

## Figure 72. Typ. V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink ports)

#### Notes:

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins do not have V<sub>OH</sub>.

# Figure 73. Typical V<sub>OH</sub> at V<sub>DD</sub>=5V

# **12.10 CONTROL PIN CHARACTERISTICS**

## 12.10.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                              | Cor                    | nditions              | Min                              | Тур | Max                              | Unit |

|-------------------------|----------------------------------------|------------------------|-----------------------|----------------------------------|-----|----------------------------------|------|

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 2)  |                        |                       |                                  | 2.5 |                                  | V    |

| V <sub>IL</sub>         | Input low level voltage 1)             |                        |                       |                                  |     | $0.16 \mathrm{xV}_{\mathrm{DD}}$ | V    |

| V <sub>IH</sub>         | Input high level voltage 1)            |                        |                       | $0.85 \mathrm{xV}_{\mathrm{DD}}$ |     |                                  | v    |

| V <sub>OL</sub>         | Output low level voltage 3)            | V <sub>DD</sub> =5V    | I <sub>IO</sub> =+2mA |                                  | 0.2 | 0.5                              | V    |

| I <sub>IO</sub>         | Driving current on RESET pin           |                        |                       |                                  | 2   |                                  | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor       | V <sub>DD</sub> =5V    |                       | 20                               | 30  | 120                              | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration         | Internal reset sources |                       | 20                               | 30  | 42 <sup>6)</sup>                 | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)      |                        |                       | 2.5                              |     |                                  | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup> |                        |                       |                                  | 200 |                                  | ns   |

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overline{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

6. Data guaranteed by design, not tested in production.

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

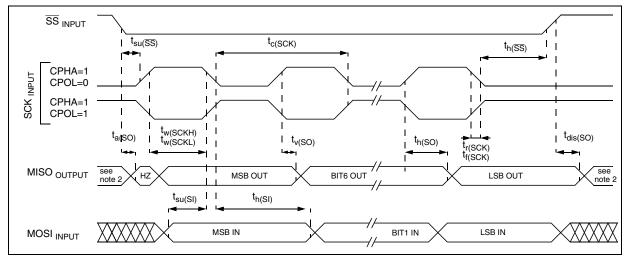

#### Figure 81. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

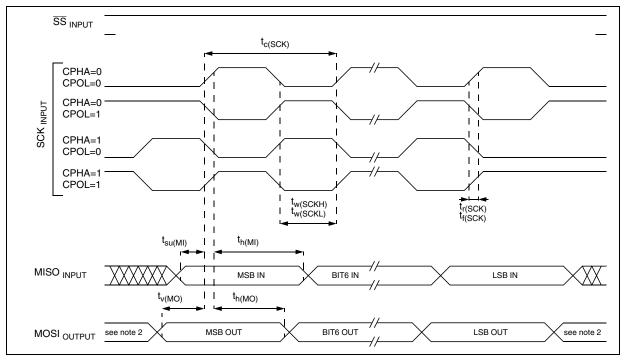

## Figure 82. SPI Master Timing Diagram 1)

#### Notes:

**\$7**

1. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

## **13.2 THERMAL CHARACTERISTICS**

| Symbol            | Ratings                                          | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

|                   | Package thermal resistance (junction to ambient) |       |      |

|                   | TQFP44 10x10                                     | 52    |      |

| R <sub>thJA</sub> | TQFP32 7x7                                       | 70    | °C/W |

|                   | SDIP42 600mil                                    | 55    |      |

|                   | SDIP32 200mil                                    | 50    |      |

| PD                | Power dissipation <sup>1)</sup>                  | 500   | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

#### Notes:

1. The power dissipation is obtained from the formula  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD}xV_{DD}$ ) and  $P_{PORT}$  is the port power dissipation determined by the user.

2. The average chip-junction temperature can be obtained from the formula  $T_J = T_A + P_D x$  RthJA.

## ST72324 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## **OPTION BYTE 1**

OPT7= **PKG1** *Pin package selection bit* This option bit selects the package.

| Version | Selected Package | PKG1 |

|---------|------------------|------|

| J       | TQFP44 / SDIP42  | 1    |

| К       | TQFP32 / SDIP32  | 0    |

**Note:** On the chip, each I/O port has 8 pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

#### OPT6 = RSTC RESET clock cycle selection

This option bit selects the number of CPU cycles applied during the RESET phase and when exiting HALT mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.

0: Reset phase with 4096 CPU cycles

1: Reset phase with 256 CPU cycles

#### OPT5:4 = OSCTYPE[1:0] Oscillator Type

These option bits select the ST7 main clock source type.

| Clock Source           | OSCTYPE |   |  |

|------------------------|---------|---|--|

| Clock Source           | 1       | 0 |  |

| Resonator Oscillator   | 0       | 0 |  |

| Reserved               | 0       | 1 |  |

| Internal RC Oscillator | 1       | 0 |  |

| External Source        | 1       | 1 |  |

#### OPT3:1 = **OSCRANGE[2:0]** Oscillator range

When the resonator oscillator type is selected,

these option bits select the resonator oscillator current source corresponding to the frequency range of the used resonator. Otherwise, these bits are used to select the normal operating frequency range.

| Typ. Freq. Range |         | OSCRANGE |   |   |  |

|------------------|---------|----------|---|---|--|

|                  |         | 2        | 1 | 0 |  |

| LP               | 1~2MHz  | 0        | 0 | 0 |  |

| MP               | 2~4MHz  | 0        | 0 | 1 |  |

| MS               | 4~8MHz  | 0        | 1 | 0 |  |

| HS               | 8~16MHz | 0        | 1 | 1 |  |

#### OPT0 = PLL OFF PLL activation

This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL must not be used with the internal RC oscillator. The PLL is guaranteed only with an input frequency between 2 and 4MHz.

0: PLL x2 enabled 1: PLL x2 disabled

**CAUTION**: the PLL can be enabled only if the "OSC RANGE" (OPT3:1) bits are configured to "MP - 2~4MHz". Otherwise, the device functionality is not guaranteed.

## **14.5 ST7 APPLICATION NOTES**

# Table 30. ST7 Application Notes

| IDENTIFICATION       | DESCRIPTION                                                                                   |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| APPLICATION EXAMPLES |                                                                                               |  |  |  |  |

| AN1658               | SERIAL NUMBERING IMPLEMENTATION                                                               |  |  |  |  |

| AN1720               | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                                    |  |  |  |  |

| AN1755               | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                                   |  |  |  |  |

| EXAMPLE DRIVER       | EXAMPLE DRIVERS                                                                               |  |  |  |  |

| AN 969               | SCI COMMUNICATION BETWEEN ST7 AND PC                                                          |  |  |  |  |

| AN 970               | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                                      |  |  |  |  |

| AN 972               | ST7 SOFTWARE SPI MASTER COMMUNICATION                                                         |  |  |  |  |

| AN 973               | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                               |  |  |  |  |

| AN 974               | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                                 |  |  |  |  |

| AN 976               | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                               |  |  |  |  |

| AN 979               | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                                   |  |  |  |  |

| AN 980               | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                             |  |  |  |  |

| AN1041               | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                                     |  |  |  |  |

| AN1044               | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                                            |  |  |  |  |

| AN1046               | UART EMULATION SOFTWARE                                                                       |  |  |  |  |

| AN1047               | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                                        |  |  |  |  |

| AN1048               | ST7 SOFTWARE LCD DRIVER                                                                       |  |  |  |  |

| AN1078               | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                                  |  |  |  |  |

| AN1445               | EMULATED 16 BIT SLAVE SPI                                                                     |  |  |  |  |

| AN1504               | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER                       |  |  |  |  |

| GENERAL PURPC        | DSE                                                                                           |  |  |  |  |

| AN1476               | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                                     |  |  |  |  |

| AN1709               | EMC DESIGN FOR ST MICROCONTROLLERS                                                            |  |  |  |  |

| AN1752               | ST72324 QUICK REFERENCE NOTE                                                                  |  |  |  |  |

| PRODUCT EVALU        |                                                                                               |  |  |  |  |

| AN 910               | PERFORMANCE BENCHMARKING                                                                      |  |  |  |  |

| AN 990               | ST7 BENEFITS VERSUS INDUSTRY STANDARD                                                         |  |  |  |  |

| AN1150               | BENCHMARK ST72 VS PC16                                                                        |  |  |  |  |

| AN1151               | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                                             |  |  |  |  |

| AN1278               | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                                    |  |  |  |  |

| PRODUCT MIGRA        |                                                                                               |  |  |  |  |

| AN1131               | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324                            |  |  |  |  |

| AN2197               | GUIDELINES FOR MIGRATING ST72F324 & ST72F321 APPLICATIONS TO ST72F324B, ST72F321B OR ST72F325 |  |  |  |  |

|                      | PRODUCT OPTIMIZATION                                                                          |  |  |  |  |

| AN 982               | USING ST7 WITH CERAMIC RESONATOR                                                              |  |  |  |  |

| AN1014               | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                                     |  |  |  |  |

| AN1015               | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                             |  |  |  |  |

| AN1070               | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                                         |  |  |  |  |

| AN1181               |                                                                                               |  |  |  |  |

| AN1502               | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                                  |  |  |  |  |

| AN1530               | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLA-<br>TOR              |  |  |  |  |

| AN1636               | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                                            |  |  |  |  |

| PROGRAMMING A        | AND TOOLS                                                                                     |  |  |  |  |

JP while\_loop

.call\_routine ; entry to call\_routine

PUSH A

PUSH X

PUSH CC

.ext1\_rt ; entry to interrupt routine

LD A,#\$00

LD sema,A

IRET

# 15.1.7 16-bit Timer PWM Mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R register (OC1HR, OC1LR). It leads to either full or no PWM during a period, depending on the OLVL1 and OLVL2 settings.

## 15.1.8 SCI Wrong Break duration

## Description

5/

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M=0

- 22 bits instead of 11 bits if M=1.

In the same way, as long as the SBK bit is set, break characters are sent to the TDO pin. This may lead to generate one break more than expected.

## Occurrence

The occurrence of the problem is random and proportional to the baudrate. With a transmit frequency of 19200 baud (fCPU=8MHz and SCI-BRR=0xC9), the wrong break duration occurrence is around 1%.

## Workaround

If this wrong duration is not compliant with the communication protocol in the application, software can request that an Idle line be generated before the break character. In this case, the break duration is always correct assuming the application is not doing anything between the idle and the break. This can be ensured by temporarily disabling interrupts.

The exact sequence is:

- Disable interrupts

- Reset and Set TE (IDLE request)

- Set and Reset SBK (Break Request)

- Re-enable interrupts

# **15.2 FLASH DEVICES ONLY**

## 15.2.1 Internal RC Operation

In ST72F324J and ST72F324K devices, the internal RC oscillator is not supported if the LVD is disabled.