Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | <u> </u>                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324k6tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **1 INTRODUCTION**

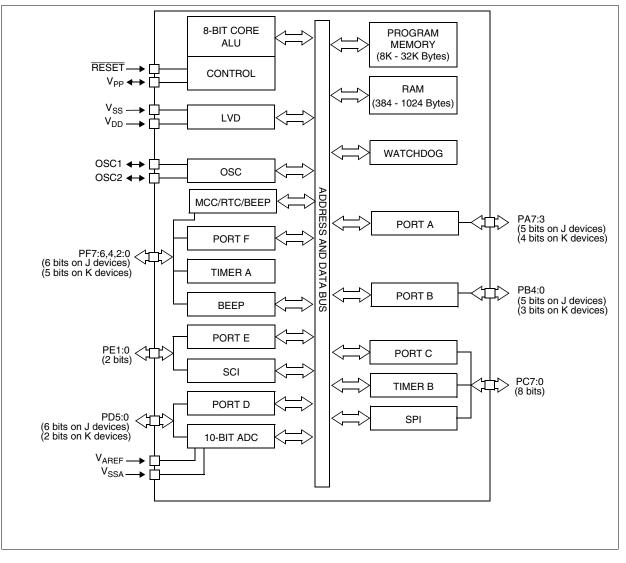

The ST72324 devices are members of the ST7 microcontroller family designed for the 5V operating range.

- The 32-pin devices are designed for mid-range applications

- The 42/44-pin devices target the same range of applications requiring more than 24 I/O ports.

For a description of the differences between ST72324 and ST72324B devices refer to Section 14.2 on page 152

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruc-

#### Figure 1. Device Block Diagram

57/

tion set and are available with FLASH program memory.

Under software control, all devices can be placed in WAIT, SLOW, ACTIVE-HALT or HALT mode, reducing power consumption when the application is in idle or stand-by state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

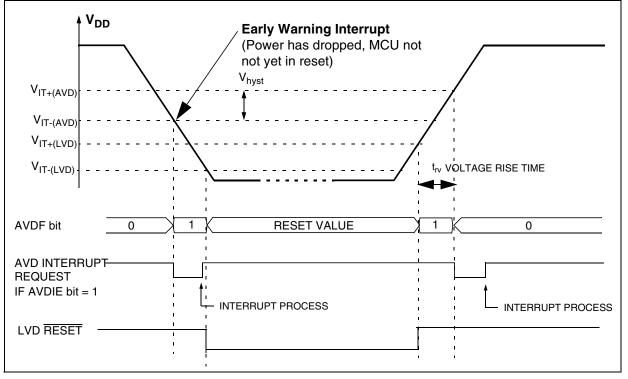

#### 6.4.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a  $V_{IT-(AVD)}$  and  $V_{IT+(AVD)}$  reference value and the  $V_{DD}$  main supply. The  $V_{IT-}$  reference value for falling voltage is lower than the  $V_{IT+}$  reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD function is active only if the LVD is enabled through the option byte (see Section 14.1 on page 150).

#### 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{IT+(AVD)}$  or  $V_{IT-(AVD)}$  threshold (AVDF bit toggles).

#### Figure 16. Using the AVD to Monitor V<sub>DD</sub>

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 16.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If t<sub>rv</sub> is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then 2 AVD interrupts will be received: the first when the AVDIE bit is set, and the second when the threshold is reached.

- If the AVD interrupt is enabled after the  $V_{\rm IT+(AVD)}$  threshold is reached then only one AVD interrupt will occur.

## INTERRUPTS (Cont'd)

#### Table 8. Interrupt Mapping

| N° | Source<br>Block | Description                               | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT/<br>ACTIVE<br>HALT <sup>1)</sup> | Address<br>Vector |

|----|-----------------|-------------------------------------------|-------------------|-------------------|-------------------------------------------------------|-------------------|

|    | RESET           | Reset                                     | N/A               |                   | yes                                                   | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                        |                   |                   | no                                                    | FFFCh-FFFDh       |

| 0  |                 | Not used                                  |                   |                   | FFFAh-FFFBh                                           |                   |

| 1  | MCC/RTC         | Main clock controller time base interrupt | MCCSR             | Higher            | yes                                                   | FFF8h-FFF9h       |

| 2  | ei0             | External interrupt port A30               |                   | Priority          | yes                                                   | FFF6h-FFF7h       |

| 3  | ei1             | External interrupt port F20               | N/A               |                   | yes                                                   | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt port B30               |                   |                   | yes                                                   | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt port B74               |                   |                   | yes                                                   | FFF0h-FFF1h       |

| 6  |                 | Not used                                  |                   |                   |                                                       | FFEEh-FFEFh       |

| 7  | SPI             | SPI peripheral interrupts                 | SPICSR            | ▼                 | yes                                                   | FFECh-FFEDh       |

| 8  | TIMER A         | TIMER A peripheral interrupts             | TASR              | Ī                 | no                                                    | FFEAh-FFEBh       |

| 9  | TIMER B         | TIMER B peripheral interrupts             | TBSR              | Ī                 | no                                                    | FFE8h-FFE9h       |

| 10 | SCI             | SCI Peripheral interrupts                 | SCISR             | Lower             | no                                                    | FFE6h-FFE7h       |

| 11 | AVD             | Auxiliary Voltage detector interrupt      | SICSR             | Priority          | no                                                    | FFE4h-FFE5h       |

#### Notes:

1. In Flash devices only a RESET or MCC/RTC interrupt can be used to wake-up from Active Halt mode.

## 7.6 EXTERNAL INTERRUPTS

## 7.6.1 I/O Port Interrupt Sensitivity

The external interrupt sensitivity is controlled by the IPA, IPB and ISxx bits of the EICR register (Figure 21). This control allows to have up to 4 fully independent external interrupt source sensitivities.

Each external interrupt source can be generated on four (or five) different events on the pin:

- Falling edge

- Rising edge

- Falling and rising edge

- Falling edge and low level

- Rising edge and high level (only for ei0 and ei2)

To guarantee correct functionality, the sensitivity bits in the EICR register can be modified only when the I1 and I0 bits of the CC register are both set to 1 (level 3). This means that interrupts must be disabled before changing sensitivity.

The pending interrupts are cleared by writing a different value in the ISx[1:0], IPA or IPB bits of the EICR.

# 9 I/O PORTS

## 9.1 INTRODUCTION

The I/O ports offer different functional modes: – transfer of data through digital inputs and outputs

- and for specific pins:

- external interrupt generation

- alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 8 pins. Each pin can be programmed independently as digital input (with or without interrupt generation) or digital output.

#### 9.2 FUNCTIONAL DESCRIPTION

Each port has 2 main registers:

Data Register (DR)

- Data Direction Register (DDR)

and one optional register:

- Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers: bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is shown in Figure 29

#### 9.2.1 Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

#### Notes:

5/

1. Writing the DR register modifies the latch value but does not affect the pin status.

2. When switching from input to output mode, the DR register has to be written first to drive the correct level on the pin as soon as the port is configured as an output.

3. Do not use read/modify/write instructions (BSET or BRES) to modify the DR register

#### External interrupt function

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU. Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several input pins are selected simultaneously as interrupt sources, these are first detected according to the sensitivity bits in the EICR register and then logically ORed.

The external interrupts are hardware interrupts, which means that the request latch (not accessible directly by the application) is automatically cleared when the corresponding interrupt vector is fetched. To clear an unwanted pending interrupt by software, the sensitivity bits in the EICR register must be modified.

#### 9.2.2 Output Modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

DR register value and output pin status:

| DR | Push-pull       | Open-drain |

|----|-----------------|------------|

| 0  | V <sub>SS</sub> | Vss        |

| 1  | V <sub>DD</sub> | Floating   |

#### 9.2.3 Alternate Functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

**Note:** Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

45/164

## WATCHDOG TIMER (Cont'd)

#### 10.1.5 Low Power Modes

| Mode | Description  |                        |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|------|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SLOW | No effect on | No effect on Watchdog. |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| WAIT | No effect on | Watchdog.              |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|      | OIE bit in   | WDGHALT bit            |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|      | MCCSR        | in Option              |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|      | register     | Byte                   |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|      | 0            | 0                      | No Watchdog reset is generated. The MCU enters Halt mode. The Watch-<br>dog counter is decremented once and then stops counting and is no longer<br>able to generate a watchdog reset until the MCU receives an external inter-<br>rupt or a reset.                                                                            |  |  |  |  |  |

| HALT | 0<br>HALT    | 0                      | If an external interrupt is received, the Watchdog restarts counting after 256 or 4096 CPU clocks. If a reset is generated, the Watchdog is disabled (reset state) unless Hardware Watchdog is selected by option byte. For application recommendations see Section 10.1.7 below.                                              |  |  |  |  |  |

|      | 0            | 1                      | A reset is generated.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|      | 1            | x                      | No reset is generated. The MCU enters Active Halt mode. The Watchdog counter is not decremented. It stop counting. When the MCU receives an oscillator interrupt or external interrupt, the Watchdog restarts counting immediately. When the MCU receives a reset the Watchdog restarts counting after 256 or 4096 CPU clocks. |  |  |  |  |  |

#### 10.1.6 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the WDGCR is not used. Refer to the Option Byte description.

# 10.1.7 Using Halt Mode with the WDG (WDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled.

Before executing the HALT instruction, refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller.

## 10.1.8 Interrupts

None.

## 10.1.9 Register Description CONTROL REGISTER (WDGCR)

#### Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | ТЗ | T2 | T1 | то |

#### Bit 7 = **WDGA** Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bit 6:0 = **T[6:0]** 7-bit counter (MSB to LSB).

These bits contain the value of the watchdog counter. It is decremented every 16384  $f_{OSC2}$  cycles (approx.). A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

## 16-BIT TIMER (Cont'd)

57

## Figure 42. Output Compare Timing Diagram, f<sub>TIMER</sub> =f<sub>CPU</sub>/2

| INTERNAL CPU CLOCK                   |                               |

|--------------------------------------|-------------------------------|

| TIMER CLOCK                          |                               |

| COUNTER REGISTER                     | 2ECFX2ED0X2ED1X2ED2X2ED3X2ED4 |

| OUTPUT COMPARE REGISTER i (OCRi)     | 2ED3                          |

| OUTPUT COMPARE FLAG i (OCFi)         |                               |

| OCMP <i>i</i> PIN (OLVL <i>i</i> =1) |                               |

|                                      |                               |

## Figure 43. Output Compare Timing Diagram, f<sub>TIMER</sub> =f<sub>CPU</sub>/4

## 16-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |     |     |     |       | 0     |

|------|------|-----|-----|-----|-----|-------|-------|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | EXEDG |

#### Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

#### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

**Note:** In Flash devices, this bit is not available for Timer A. It must be kept at its reset value.

#### Bit 5 = **OPM** One Pulse Mode.

0: One Pulse Mode is not active.

1: One Pulse Mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

## Bit 4 = **PWM** Pulse Width Modulation.

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

#### Bit 3, 2 = CC[1:0] Clock Control.

The timer clock mode depends on these bits:

#### Table 16. Clock Control Bits

| Timer Clock                      | CC1 | CC0 |

|----------------------------------|-----|-----|

| f <sub>CPU</sub> / 4             | 0   | 0   |

| f <sub>CPU</sub> / 2             | 0   | 1   |

| f <sub>CPU</sub> / 8             | 1   | 0   |

| External Clock (where available) | 1   | 1   |

**Note**: If the external clock pin is not available, programming the external clock configuration stops the counter.

#### Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

#### Bit 0 = **EXEDG** External Clock Edge.

This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.

0: A falling edge triggers the counter register.

1: A rising edge triggers the counter register.

## 16-BIT TIMER (Cont'd)

## OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, the Timer A OC2HR register is write-only.

# OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

**Note:** In Flash devices, the Timer A OC2LR register is write-only.

## **COUNTER HIGH REGISTER (CHR)**

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## **COUNTER LOW REGISTER (CLR)**

Read Only Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

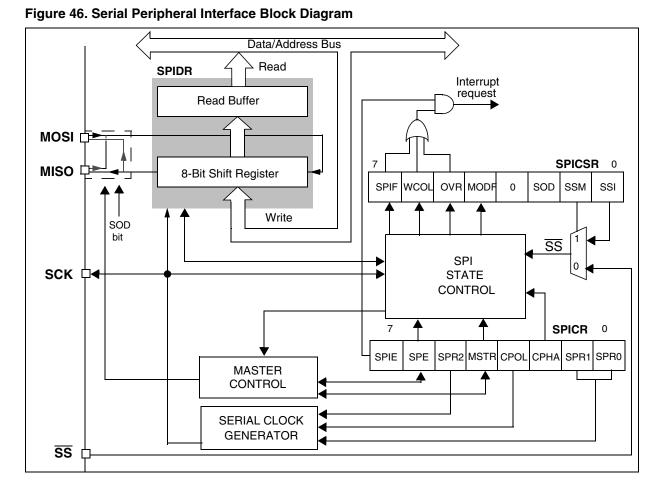

## **10.4 SERIAL PERIPHERAL INTERFACE (SPI)**

## 10.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves however the SPI interface can not be a master in a multi-master system.

#### 10.4.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

57/

Write collision, Master Mode Fault and Overrun flags **Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### 10.4.3 General Description

Figure 46 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 4 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1.).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

5/

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 2.).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### Idle Characters

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

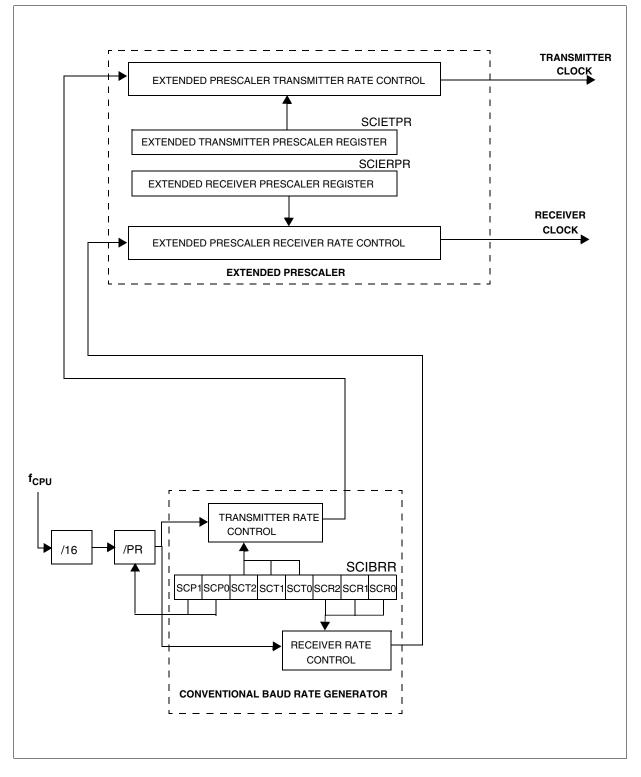

#### Figure 55. SCI Baud Rate and Extended Prescaler Block Diagram

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## 10.5.4.7 Parity Control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 1.

| Table 20. | <b>Frame Formats</b> |

|-----------|----------------------|

|-----------|----------------------|

| M bit | PCE bit | SCI frame                  |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 1     | 0       | SB   9-bit data   STB      |

| 1     | 1       | SB   8-bit data PB   STB   |

**Legend:** SB = Start Bit, STB = Stop Bit,

PB = Parity Bit

5/

**Note**: In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** the parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 0 if even parity is selected (PS bit = 0).

**Odd parity:** the parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an

even number of "1s" if even parity is selected (PS = 0) or an odd number of "1s" if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

#### 10.5.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: If the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value is "1", but the Noise Flag bit is set because the three samples values are not the same.

Consequently, the bit length must be long enough so that the 8th, 9th and 10th samples have the desired bit value. This means the clock frequency should not vary more than 6/16 (37.5%) within one bit. The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation must not exceed 3.75%.

**Note:** The internal sampling clock of the microcontroller samples the pin value on every falling edge. Therefore, the internal sampling clock and the time the application expects the sampling to take place may be out of sync. For example: If the baud rate is 15.625 Kbaud (bit length is 64µs), then the 8th, 9th and 10th samples are at 28µs, 32µs and 36µs respectively (the first sample starting ideally at 0µs). But if the falling edge of the internal clock occurs just before the pin value changes, the samples would then be out of sync by ~4us. This means the entire bit length must be at least 40µs (36µs for the 10th sample + 4µs for synchronization with the internal sampling clock).

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) DATA REGISTER (SCIDR)

#### Read/Write

#### Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 1.).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 1.).

## **BAUD RATE REGISTER (SCIBRR)**

Read/Write

Reset Value: 0000 0000 (00h)

7

0

SCP1

SCP0

SCT2

SCT1

SCT0

SCR2

SCR1

SCR0

#### Bits 7:6 = SCP[1:0] First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| 1                    | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | 1    | 0    |

| 13                   | 1    | 1    |

Bits 5:3 = SCT[2:0] SCI Transmitter rate divisor These 3 bits, in conjunction with the SCP1 & SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.* These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR Dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

## **10-BIT A/D CONVERTER** (Cont'd)

57

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

## Table 23. ADC Register Map and Reset Values

## **11 INSTRUCTION SET**

## **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in 7 main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

Table 24. CPU Addressing Mode Overview

so, most of the addressing modes may be subdivided in two sub-modes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

| Mode      |          |          | Syntax Destination  |          | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|----------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 |          |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |          |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF     |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF     |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE    |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF     | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE    | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127 |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127 | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF     |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF     | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF     |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF     | 00FF                         | byte                   | + 3               |

## INSTRUCTION SET OVERVIEW (Cont'd)

#### **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | СР   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a pre-byte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC opcode

57

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

## **12 ELECTRICAL CHARACTERISTICS**

## **12.1 PARAMETER CONDITIONS**

Unless otherwise specified, all voltages are referred to  $\ensuremath{\mathsf{V}_{SS}}\xspace.$

#### 12.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}C$  and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 12.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}$ C,  $V_{DD}=5$ V. They are given only as design guidelines and are not tested.

#### 12.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

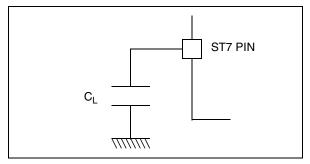

#### 12.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 58.

#### Figure 58. Pin loading conditions

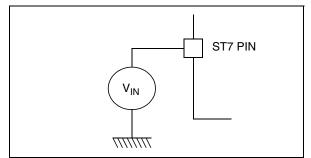

#### 12.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 59.

#### Figure 59. Pin input voltage

## CLOCK CHARACTERISTICS (Cont'd)

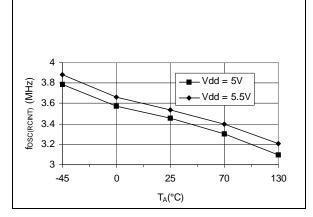

## 12.6.4 RC Oscillators

57

| Symbol       | Parameter                                         | Conditions                                | Min | Тур | Max | Unit |

|--------------|---------------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| fOSC (RCINT) | Internal RC oscillator frequency<br>See Figure 67 | T <sub>A</sub> =25°C, V <sub>DD</sub> =5V | 2   | 3.5 | 5.6 | MHz  |

## Figure 67. Typical f<sub>OSC(RCINT)</sub> vs T<sub>A</sub>

Note: To reduce disturbance to the RC oscillator, it is recommended to place decoupling capacitors between  $V_{DD}$  and  $V_{SS}$  as shown in Figure 86

## EMC CHARACTERISTICS (Cont'd)

# 12.8.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### 12.8.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

#### Absolute Maximum Ratings

| Symbol                | Ratings                                                    | Conditions            | Maximum value 1) | Unit |

|-----------------------|------------------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)     | T <sub>A</sub> =+25°C | 2000             |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)           | T <sub>A</sub> =+25°C | 200              | V    |

| V <sub>ESD(CD)</sub>  | Electro-static discharge voltage<br>(Charged Device Model) | T <sub>A</sub> =+25°C | 250              |      |

#### Notes:

1. Data based on characterization results, not tested in production.

- 12.8.3.2 Static and Dynamic Latch-Up

- LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

- DLU: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

#### **Electrical Sensitivities**

| Symbol | Parameter              | Conditions                                                    | Class <sup>1)</sup> |

|--------|------------------------|---------------------------------------------------------------|---------------------|

| LU     | Static latch-up class  | T <sub>A</sub> =+25°C                                         | А                   |

|        |                        | T <sub>A</sub> =+85°C                                         | A                   |

|        |                        | T <sub>A</sub> =+125°C                                        | А                   |

| DLU    | Dynamic latch-up class | $V_{DD}$ =5.5V, f <sub>OSC</sub> =4MHz, T <sub>A</sub> =+25°C | А                   |

#### Notes:

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

## ADC CHARACTERISTICS (Cont'd)

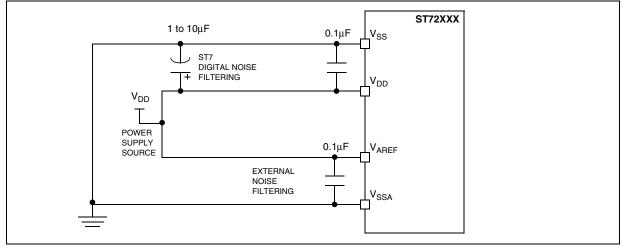

# 12.13.1 Analog Power Supply and Reference Pins

Depending on the MCU pin count, the package may feature separate  $V_{AREF}$  and  $V_{SSA}$  analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion. In some packages,  $V_{AREF}$  and  $V_{SSA}$  pins are not available (refer to Section 2 on page 8). In this case the analog supply and reference pads are internally bonded to the  $V_{DD}$  and  $V_{SS}$  pins.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see Section 12.13.2 General PCB Design Guidelines).

#### 12.13.2 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing  $0.1\mu$ F and optionally, if needed 10pF capacitors as close as possible to the ST7 power supply pins and a 1 to  $10\mu$ F capacitor close to the power source (see Figure 86).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>AREF</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

47/

#### Figure 86. Power Supply Filtering