Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detalls                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |

| Number of I/O              | 37                                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 4K x 8                                                                                  |

| RAM Size                   | 8K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 48-LQFP                                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc100ld2dn |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

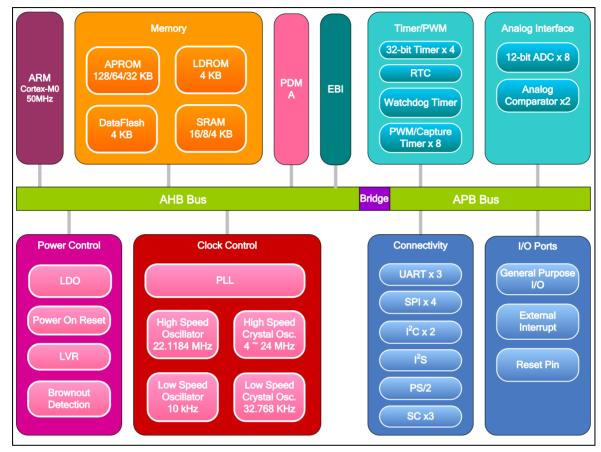

### **1 GENERAL DESCRIPTION**

The NuMicro<sup>®</sup> NUC100 series 32-bit microcontroller (MCU) is embedded with the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core with the cost equivalent to traditional 8-bit MCU. The NUC100 series can be used in consumer electronics, industrial control and applications which requiring rich communication interfaces such as industrial automation, alarm system, energy system and power system.

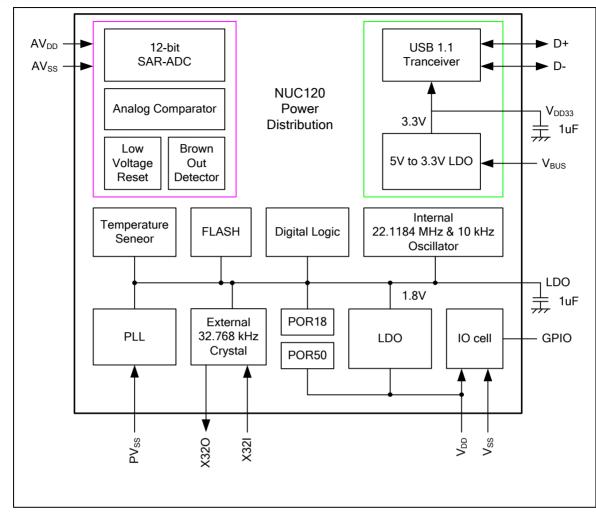

The NuMicro<sup>®</sup> NUC100 Advanced Line and NUC120 USB Line are embedded with the Cortex<sup>®</sup>-M0 core running up to 50 MHz and features 32/64/128 Kbytes Flash, 4/8/16 Kbytes embedded SRAM and 4 Kbytes loader ROM for the ISP. It operates at a wide voltage range of 2.5V ~ 5.5V and temperature range of -40°C ~ +85°C. The NUC100 series is also provided with plenty of peripheral devices, such as Timers, Watchdog Timer, Window Watchdog Timer, RTC, PDMA with CRC calculation unit, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, PWM Timer, GPIO, PS/2, EBI, Smart Card Host, 12-bit ADC, Analog Comparator, Low Voltage Reset Controller and Brown-out Detector. Additionally, the NUC120 USB Line is equipped with a USB 2.0 Full-speed Device. These peripherals have been incorporated into the NUC100 series to reduce component count, board space and system cost.

The NUC100 series is equipped with ISP (In-System Programming), IAP (In-Application-Programming) and ICP (In-Circuit Programming) functions, which allows the user to update the program under software control through the on-chip connectivity interface, such as SWD, UART and USB.

| Product Line | UART | SPI | I <sup>2</sup> C | USB | PS/2 | I <sup>2</sup> S | SC |

|--------------|------|-----|------------------|-----|------|------------------|----|

| NUC100xxxDN  | 3    | 4   | 2                | -   | 1    | 1                | 3  |

| NUC120xxxDN  | 3    | 4   | 2                | 1   | 1    | 1                | 3  |

Table 1-1 NuMicro® NUC100 Series Connectivity Support Table

- Supports 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit prescale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Supports event counting function

- Supports input capture function

- Watchdog Timer

- Multiple clock sources

- 8 selectable time-out period from 1.6 ms ~ 26.0 sec (depending on clock source)

- Wake-up from Power-down or Idle mode

- Interrupt or reset selectable on watchdog time-out

- Window Watchdog Timer

- 6-bit down counter with 11-bit prescale for wide range window selected

- RTC

- Supports software compensation by setting frequency compensate register (FCR)

- Supports RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Supports Alarm registers (second, minute, hour, day, month, year)

- Selectable 12-hour or 24-hour mode

- Automatic leap year recognition

- Supports periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Supports wake-up function

- PWM/Capture

- Up to four built-in 16-bit PWM generators providing eight PWM outputs or four complementary paired PWM outputs

- Each PWM generator equipped with one clock source selector, one clock divider, one 8-bit prescaler and one Dead-Zone generator for complementary paired PWM

- Up to eight 16-bit digital capture timers (shared with PWM timers) providing eight rising/falling capture inputs

- Supports Capture interrupt

- UART

- Up to three UART controllers

- UART ports with flow control (TXD, RXD, CTS and RTS)

- UART0 with 64-byte FIFO is for high speed

- UART1/2(optional) with 16-byte FIFO for standard device

- Supports IrDA (SIR) and LIN function

- Supports RS-485 9-bit mode and direction control

- Programmable baud-rate generator up to 1/16 system clock

- Supports PDMA mode

- SPI

- Up to four sets of SPI controllers

- SPI clock rate of Master can be up to 36 MHz (chip working at 5V); SPI clock rate of Slave can be up to 18 MHz (chip working at 5V)

- Supports SPI Master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- Two slave/device select lines in Master mode, and one slave/device select line in Slave mode

- Supports Byte Suspend mode in 32-bit transmission

- Supports PDMA mode

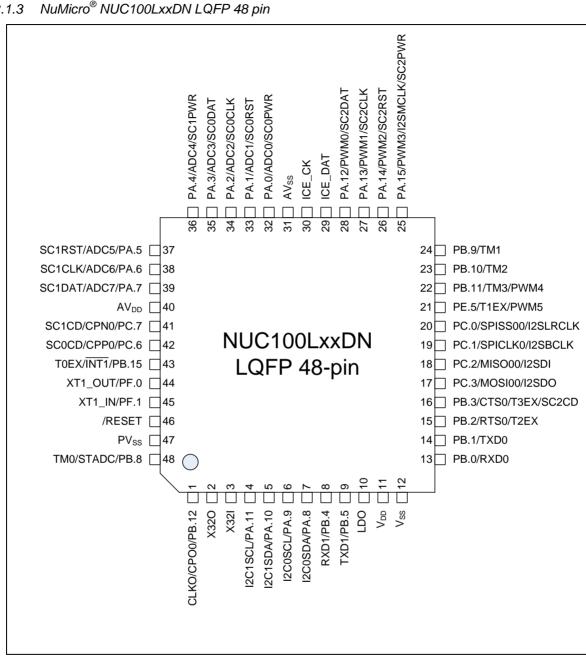

4.2.1.3

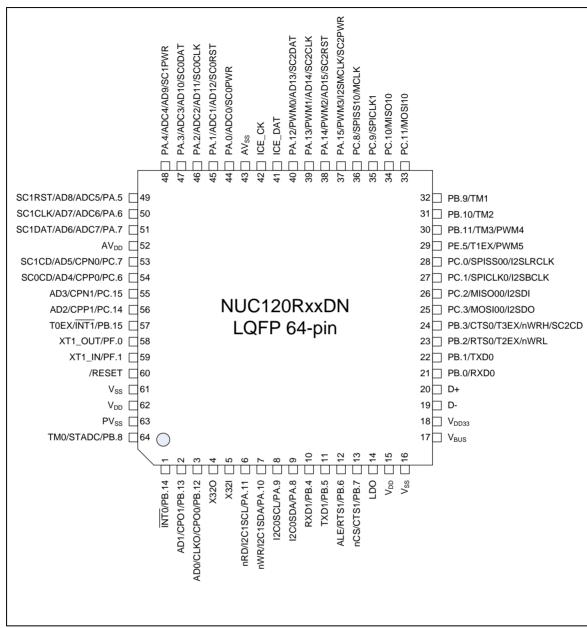

4.2.2.2 NuMicro<sup>®</sup> NUC120RxxDN LQFP 64 pin

| Pin No.         |                |                |                 |          |                                                                                 |

|-----------------|----------------|----------------|-----------------|----------|---------------------------------------------------------------------------------|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name        | Pin Type | Description                                                                     |

|                 |                |                | MISO30          | I/O      | 1 <sup>st</sup> SPI3 MISO (Master In, Slave Out) pin.                           |

| 10              |                |                | PD.11           | I/O      | General purpose digital I/O pin.                                                |

| 16              |                |                | MOSI30          | I/O      | 1 <sup>st</sup> SPI3 MOSI (Master Out, Slave In) pin.                           |

| 47              |                |                | PD.12           | I/O      | General purpose digital I/O pin.                                                |

| 17              |                |                | MISO31          | I/O      | 2 <sup>nd</sup> SPI3 MISO (Master In, Slave Out) pin.                           |

| 40              |                |                | PD.13           | I/O      | General purpose digital I/O pin.                                                |

| 18              |                |                | MOSI31          | I/O      | 2 <sup>nd</sup> SPI3 MOSI (Master Out, Slave In) pin.                           |

| 40              | 40             |                | PB.4            | I/O      | General purpose digital I/O pin.                                                |

| 19              | 10             | 8              | RXD1            | I        | Data receiver input pin for UART1.                                              |

|                 | 4.4            |                | PB.5            | I/O      | General purpose digital I/O pin.                                                |

| 20              | 11             | 9              | TXD1            | 0        | Data transmitter output pin for UART1.                                          |

|                 |                |                | PB.6            | I/O      | General purpose digital I/O pin.                                                |

| 21              | 12             |                | RTS1            | 0        | Request to Send output pin for UART1.                                           |

|                 |                |                | ALE             | 0        | EBI address latch enable output pin                                             |

|                 |                |                | PB.7            | I/O      | General purpose digital I/O pin.                                                |

| 22              | 13             |                | CTS1            | I        | Clear to Send input pin for UART1.                                              |

|                 |                |                | nCS             | 0        | EBI chip select enable output pin                                               |

| 23              | 14             | 10             | LDO             | Р        | LDO output pin                                                                  |

| 24              | 15             | 11             | V <sub>DD</sub> | Р        | Power supply for I/O ports and LDO source for internal PLL and digital circuit. |

| 25              | 16             | 12             | V <sub>SS</sub> | Р        | Ground pin for digital circuit.                                                 |

| 26              |                |                | PE.12           | I/O      | General purpose digital I/O pin.                                                |

| 27              |                |                | PE.11           | I/O      | General purpose digital I/O pin.                                                |

| 28              |                |                | PE.10           | I/O      | General purpose digital I/O pin.                                                |

| 29              |                |                | PE.9            | I/O      | General purpose digital I/O pin.                                                |

| 30              |                |                | PE.8            | I/O      | General purpose digital I/O pin.                                                |

| 31              |                |                | PE.7            | I/O      | General purpose digital I/O pin.                                                |

| 20              | 47             | 40             | PB.0            | I/O      | General purpose digital I/O pin.                                                |

| 32              | 17             | 13             | RXD0            | I        | Data receiver input pin for UART0.                                              |

| 22              | 10             | 4.4            | PB.1            | I/O      | General purpose digital I/O pin.                                                |

| 33              | 18             | 14             | TXD0            | 0        | Data transmitter output pin for UART0.                                          |

|                 | 40             | 45             | PB.2            | I/O      | General purpose digital I/O pin.                                                |

| 34              | 19             | 15             | RTS0            | 0        | Request to Send output pin for UART0.                                           |

| 4.3.2 | NuMicro <sup>®</sup> | <b>NUC120</b> | Pin | Description |

|-------|----------------------|---------------|-----|-------------|

|-------|----------------------|---------------|-----|-------------|

| Pin No.         |                |                |          |          |                                                       |

|-----------------|----------------|----------------|----------|----------|-------------------------------------------------------|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name | Pin Type | Description                                           |

| 1               |                |                | PE.15    | I/O      | General purpose digital I/O pin.                      |

| 2               |                |                | PE.14    | I/O      | General purpose digital I/O pin.                      |

| 3               |                |                | PE.13    | I/O      | General purpose digital I/O pin.                      |

|                 | 4              |                | PB.14    | I/O      | General purpose digital I/O pin.                      |

| 4               | 1              |                | /INT0    | I        | External interrupt0 input pin.                        |

|                 |                |                | SPISS31  | I/O      | 2 <sup>nd</sup> SPI3 slave select pin.                |

|                 |                |                | PB.13    | I/O      | General purpose digital I/O pin.                      |

| 5               | 2              |                | CPO1     | 0        | Comparator1 output pin.                               |

|                 |                |                | AD1      | I/O      | EBI Address/Data bus bit1                             |

|                 |                |                | PB.12    | I/O      | General purpose digital I/O pin.                      |

| c               | 2              | 1              | CPO0     | 0        | Comparator0 output pin                                |

| 6               | 3              |                | CLKO     | 0        | Frequency Divider output pin                          |

|                 |                |                | AD0      | I/O      | EBI Address/Data bus bit0                             |

| 7               | 4              | 2              | X32O     | 0        | External 32.768 kHz low speed crystal output pin      |

| 8               | 5              | 3              | X32I     | I        | External 32.768 kHz low speed crystal input pin       |

|                 |                | 4              | PA.11    | I/O      | General purpose digital I/O pin.                      |

| 9               | 6              | 4              | I2C1SCL  | I/O      | I <sup>2</sup> C1 clock pin.                          |

|                 |                |                | nRD      | 0        | EBI read enable output pin                            |

|                 |                | 5              | PA.10    | I/O      | General purpose digital I/O pin.                      |

| 10              | 7              | 5              | I2C1SDA  | I/O      | l <sup>2</sup> C1 data input/output pin.              |

|                 |                |                | nWR      | 0        | EBI write enable output pin                           |

| 11              | 8              | 6              | PA.9     | I/O      | General purpose digital I/O pin.                      |

|                 | 0              | 0              | I2C0SCL  | I/O      | I <sup>2</sup> C0 clock pin.                          |

| 12              | 9              | 7              | PA.8     | I/O      | General purpose digital I/O pin.                      |

| 12              | 9              | Ĩ              | I2C0SDA  | I/O      | I <sup>2</sup> C0 data input/output pin.              |

| 13              |                |                | PD.8     | I/O      | General purpose digital I/O pin.                      |

| 15              |                |                | SPISS30  | I/O      | 1 <sup>st</sup> SPI3 slave select pin.                |

| 14              |                |                | PD.9     | I/O      | General purpose digital I/O pin.                      |

| 14              |                |                | SPICLK3  | I/O      | SPI3 serial clock pin.                                |

| 15              |                |                | PD.10    | I/O      | General purpose digital I/O pin.                      |

| 10              |                |                | MISO30   | I/O      | 1 <sup>st</sup> SPI3 MISO (Master In, Slave Out) pin. |

| 16              |                |                | PD.11    | I/O      | General purpose digital I/O pin.                      |

| Pin No.         |                |                |          |          |                                                       |

|-----------------|----------------|----------------|----------|----------|-------------------------------------------------------|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name | Pin Type | Description                                           |

|                 |                |                | PB.3     | I/O      | General purpose digital I/O pin.                      |

|                 |                |                | CTS0     | I        | Clear to Send input pin for UART0.                    |

| 35              | 24             | 20             | ТЗЕХ     | I        | Timer3 external capture input pin.                    |

|                 |                |                | SC2CD    | I        | SmartCard2 card detect pin.                           |

|                 |                |                | nWRH     | 0        | EBI high byte write enable output pin                 |

| 36              |                |                | PD.6     | I/O      | General purpose digital I/O pin.                      |

| 37              |                |                | PD.7     | I/O      | General purpose digital I/O pin.                      |

| 38              |                |                | PD.14    | I/O      | General purpose digital I/O pin.                      |

| 50              |                |                | RXD2     | Т        | Data receiver input pin for UART2.                    |

|                 |                |                | PD.15    | I/O      | General purpose digital I/O pin.                      |

| 39              |                |                | TXD2     | 0        | Data transmitter output pin for UART2.                |

| 40              |                |                | PC.5     | I/O      | General purpose digital I/O pin.                      |

| 40              |                |                | MOSI01   | I/O      | 2 <sup>nd</sup> SPI0 MOSI (Master Out, Slave In) pin. |

| 41              |                |                | PC.4     | I/O      | General purpose digital I/O pin.                      |

| 41              |                |                | MISO01   | I/O      | 2 <sup>nd</sup> SPI0 MISO (Master In, Slave Out) pin. |

|                 |                |                | PC.3     | I/O      | General purpose digital I/O pin.                      |

| 42              | 25             | 21             | MOSI00   | I/O      | 1 <sup>st</sup> SPI0 MOSI (Master Out, Slave In) pin. |

|                 |                |                | I2SDO    | 0        | I <sup>2</sup> S data output.                         |

|                 |                |                | PC.2     | I/O      | General purpose digital I/O pin.                      |

| 43              | 26             | 22             | MISO00   | I/O      | 1 <sup>st</sup> SPI0 MISO (Master In, Slave Out) pin. |

|                 |                |                | I2SDI    | I        | I <sup>2</sup> S data input.                          |

|                 |                |                | PC.1     | I/O      | General purpose digital I/O pin.                      |

| 44              | 27             | 23             | SPICLK0  | I/O      | SPI0 serial clock pin.                                |

|                 |                |                | I2SBCLK  | I/O      | I <sup>2</sup> S bit clock pin.                       |

|                 |                |                | PC.0     | I/O      | General purpose digital I/O pin.                      |

| 45              | 28             | 24             | SPISS00  | I/O      | 1 <sup>st</sup> SPI0 slave select pin.                |

|                 |                |                | I2SLRCLK | I/O      | I <sup>2</sup> S left right channel clock.            |

| 46              |                |                | PE.6     | I/O      | General purpose digital I/O pin.                      |

|                 |                |                | PE.5     | I/O      | General purpose digital I/O pin.                      |

| 47              | 29             |                | PWM5     | I/O      | PWM5 output/Capture input.                            |

|                 |                |                | T1EX     | I        | Timer1 external capture input pin.                    |

| 48              | 30             |                | PB.11    | I/O      | General purpose digital I/O pin.                      |

| Pin No.         |                |                |                  |          |                                                                                 |

|-----------------|----------------|----------------|------------------|----------|---------------------------------------------------------------------------------|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name         | Pin Type | Description                                                                     |

|                 |                |                | PA.14            | I/O      | General purpose digital I/O pin.                                                |

|                 | 00             | 26             | PWM2             | I/O      | PWM2 output/Capture input.                                                      |

| 63              | 38             |                | SC2RST           | 0        | SmartCard2 reset pin.                                                           |

|                 |                |                | AD15             | I/O      | EBI Address/Data bus bit15                                                      |

|                 |                |                | PA.13            | I/O      | General purpose digital I/O pin.                                                |

| 64              | 20             | 27             | PWM1             | I/O      | PWM1 output/Capture input.                                                      |

| 64              | 39             |                | SC2CLK           | 0        | SmartCard2 clock pin.                                                           |

|                 |                |                | AD14             | I/O      | EBI Address/Data bus bit14                                                      |

|                 |                |                | PA.12            | I/O      | General purpose digital I/O pin.                                                |

| CE.             | 40             | 28             | PWM0             | I/O      | PWM0 output/Capture input.                                                      |

| 65              | 40             |                | SC2DAT           | 0        | SmartCard2 data pin.                                                            |

|                 |                |                | AD13             | I/O      | EBI Address/Data bus bit13                                                      |

| 66              | 41             | 29             | ICE_DAT          | I/O      | Serial Wire Debugger Data pin                                                   |

| 67              | 42             | 30             | ICE_CLK          | Т        | Serial Wire Debugger Clock pin                                                  |

| 68              |                |                | V <sub>DD</sub>  | Р        | Power supply for I/O ports and LDO source for internal PLL and digital circuit. |

| 69              |                |                | V <sub>SS</sub>  | Р        | Ground pin for digital circuit.                                                 |

| 70              | 43             | 31             | AV <sub>SS</sub> | AP       | Ground pin for analog circuit.                                                  |

|                 |                |                | PA.0             | I/O      | General purpose digital I/O pin.                                                |

| 71              | 44             | 32             | ADC0             | AI       | ADC0 analog input.                                                              |

|                 |                |                | SC0PWR           | 0        | SmartCard0 power pin.                                                           |

|                 |                |                | PA.1             | I/O      | General purpose digital I/O pin.                                                |

| 72              | 45             | 33             | ADC1             | AI       | ADC1 analog input.                                                              |

| 72              | 45             |                | SCORST           | 0        | SmartCard0 reset pin.                                                           |

|                 |                |                | AD12             | I/O      | EBI Address/Data bus bit12                                                      |

|                 |                |                | PA.2             | I/O      | General purpose digital I/O pin.                                                |

| 73              | 46             | 34             | ADC2             | AI       | ADC2 analog input.                                                              |

| 13              | 40             |                | SC0CLK           | 0        | SmartCard0 clock pin.                                                           |

|                 |                |                | AD11             | I/O      | EBI Address/Data bus bit11                                                      |

|                 |                |                | PA.3             | I/O      | General purpose digital I/O pin.                                                |

| 74              | 47             | 35             | ADC3             | AI       | ADC3 analog input.                                                              |

| /4              | 47             |                | SC0DAT           | 0        | SmartCard0 data pin.                                                            |

|                 |                |                | AD10             | I/O      | EBI Address/Data bus bit10                                                      |

| Pin No.         |                |                |                  |          |                                                                                                           |

|-----------------|----------------|----------------|------------------|----------|-----------------------------------------------------------------------------------------------------------|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name         | Pin Type | Description                                                                                               |

|                 |                |                | SC1CD            | I        | SmartCard1 card detect pin.                                                                               |

|                 |                |                | AD5              | I/O      | EBI Address/Data bus bit5                                                                                 |

|                 |                |                | PC.6             | I/O      | General purpose digital I/O pin.                                                                          |

| 88              | 54             | 42             | CPP0             | AI       | Comparator0 positive input pin.                                                                           |

| 00              | 54             |                | SC0CD            | I        | SmartCard0 card detect pin.                                                                               |

|                 |                |                | AD4              | I/O      | EBI Address/Data bus bit4                                                                                 |

|                 |                |                | PC.15            | I/O      | General purpose digital I/O pin.                                                                          |

| 89              | 55             |                | CPN1             | AI       | Comparator1 negative input pin.                                                                           |

|                 |                |                | AD3              | I/O      | EBI Address/Data bus bit3                                                                                 |

|                 |                |                | PC.14            | I/O      | General purpose digital I/O pin.                                                                          |

| 90              | 56             |                | CPP1             | AI       | Comparator1 positive input pin.                                                                           |

|                 |                |                | AD2              | I/O      | EBI Address/Data bus bit2                                                                                 |

|                 |                |                | PB.15            | I/O      | General purpose digital I/O pin.                                                                          |

| 91              | 57             | 43             | /INT1            | I        | External interrupt1 input pin.                                                                            |

|                 |                |                | TOEX             | I        | Timer0 external capture input pin.                                                                        |

| 92              | 58             | 44             | PF.0             | I/O      | General purpose digital I/O pin.                                                                          |

| 92              | 50             | 44             | XT1_OUT          | 0        | External 4~24 MHz (high speed) crystal output pin.                                                        |

| 93              | 59             | 45             | PF.1             | I/O      | General purpose digital I/O pin.                                                                          |

| 93              | 39             | 40             | XT1_IN           | I        | External 4~24 MHz (high speed) crystal input pin.                                                         |

| 94              | 60             | 46             | /RESET           | I        | External reset input: active LOW, with an internal pull-up. Set this pin low reset chip to initial state. |

| 95              | 61             |                | V <sub>SS</sub>  | Р        | Ground pin for digital circuit.                                                                           |

| 96              | 62             |                | V <sub>dd</sub>  | Р        | Power supply for I/O ports and LDO source for internal PLL and digital circuit.                           |

| 07              |                |                | PF.2             | I/O      | General purpose digital I/O pin.                                                                          |

| 97              |                |                | PS2DAT           | I/O      | PS/2 data pin.                                                                                            |

| 00              |                |                | PF.3             | I/O      | General purpose digital I/O pin.                                                                          |

| 98              |                |                | PS2CLK           | I/O      | PS/2 clock pin.                                                                                           |

| 99              | 63             | 47             | PV <sub>ss</sub> | Р        | PLL ground.                                                                                               |

|                 |                |                | PB.8             | I/O      | General purpose digital I/O pin.                                                                          |

| 100             | 64             | 48             | STADC            | I        | ADC external trigger input.                                                                               |

|                 |                |                | тмо              | I/O      | Timer0 event counter input / toggle output.                                                               |

Note: Pin Type I = Digital Input, O = Digital Output; AI = Analog Input; P = Power Pin; AP = Analog Power

# ηυνοτοη

### 5 BLOCK DIAGRAM

### 5.1 NuMicro<sup>®</sup> NUC100 Block Diagram

Figure 5-1 NuMicro® NUC100 Block Diagram

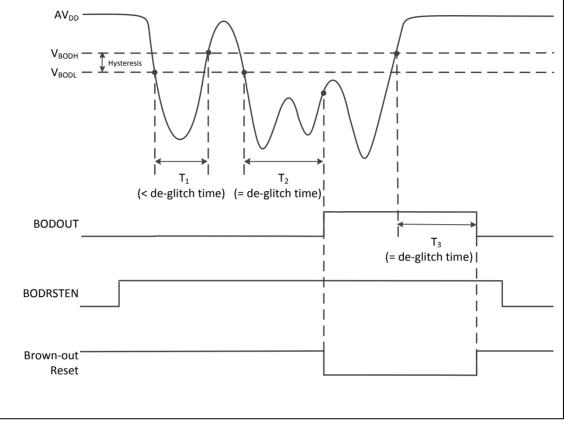

Figure 6-6 Brown-Out Detector (BOD) Waveform

#### 6.2.2.5 Watchdog Timer Reset

In most industrial applications, system reliability is very important. To automatically recover the MCU from failure status is one way to improve system reliability. The watchdog timer (WDT) is widely used to check if the system works fine. If the MCU is crashed or out of control, it may cause the watchdog time-out. User may decide to enable system reset during watchdog time-out to recover the system and take action for the system crash/out-of-control after reset.

Software can check if the reset is caused by watchdog time-out to indicate the previous reset is a watchdog reset and handle the failure of MCU after watchdog time-out reset by checking RSTS\_WDT (RSTSRC[2]).

### 6.2.2.6 CPU Reset, CHIP Reset and MCU Reset

The CPU Reset means only Cortex<sup>®</sup>-M0 core is reset and all other peripherals remain the same status after CPU reset. User can set the CPU Reset CPU\_RST (IPRSTC1[1]) to 1 to assert the CPU Reset signal.

The CHIP Reset is same with Power-On Reset. The CPU and all peripherals are reset and BS (ISPCON[1]) bit is automatically reloaded from CONFIG0 setting. User can set the CHIP Reset CHIP\_RST (IPRSTC1[0]) to 1 to assert the CHIP Reset signal.

The MCU Reset is similar with CHIP Reset. The difference is that BS (ISPCON[1]) will not be reloaded from CONFIG0 setting and keep its original software setting for booting from APROM or LDROM. User can set the MCU Reset SYSRESETREQ(AIRCR[2]) to 1 to assert the MCU Reset.

# nuvoton

Figure 6-9 NuMicro<sup>®</sup> NUC120 Power Distribution Diagram

#### 6.2.6 System Timer (SysTick)

The Cortex<sup>®</sup>-M0 includes an integrated system timer, SysTick, which provides a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

When system timer is enabled, it will count down from the value in the SysTick Current Value Register (SYST\_CVR) to 0, and reload (wrap) to the value in the SysTick Reload Value Register (SYST\_RVR) on the next clock cycle, then decrement on subsequent clocks. When the counter transitions to 0, the COUNTFLAG status bit is set. The COUNTFLAG bit clears on reads.

The SYST\_CVR value is UNKNOWN on reset. Software should write to the register to clear it to 0 before enabling the feature. This ensures the timer will count from the SYST\_RVR value rather than an arbitrary value when it is enabled.

If the SYST\_RVR is 0, the timer will be maintained with a current value of 0 after it is reloaded with this value. This mechanism can be used to disable the feature independently from the timer enable bit.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>®</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

#### 6.3.4 Peripherals Clock

The peripherals clock can be selected as different clock source depends on the clock source select control registers (CLKSEL1, CLKSEL2 and CLKSEL3).

#### 6.3.5 Power-down Mode Clock

When chip enters Power-down mode, system clocks, some clock sources, and some peripheral clocks will be disabled. Some clock sources and peripherals clocks are still active in Power-down mode.

The clocks still kept active are listed below:

- Clock Generator

- Internal 10 kHz low speed oscillator clock

- External 32.768 kHz low speed crystal clock

- Peripherals Clock (when IP adopt external 32.768 kHz low speed crystal oscillator or 10 kHz low speed oscillator as clock source)

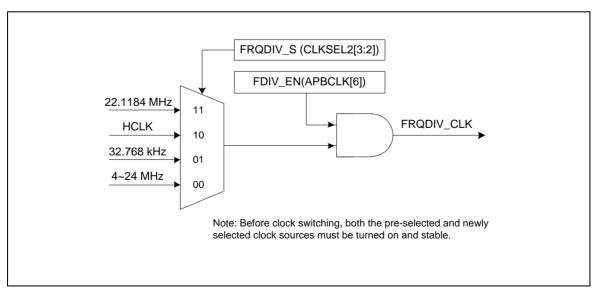

#### 6.3.6 Frequency Divider Output

This device is equipped with a power-of-2 frequency divider which is composed by16 chained divide-by-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to CLKO function pin. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^1$  to  $F_{in}/2^{16}$  where Fin is input clock frequency to the clock divider.

The output formula is  $F_{out} = F_{in}/2^{(N+1)}$ , where  $F_{in}$  is the input clock frequency,  $F_{out}$  is the clock divider output frequency and N is the 4-bit value in FSEL (FRQDIV[3:0]).

When writing 1 to DIVIDER\_EN (FRQDIV[4]), the chained counter starts to count. When writing 0 to DIVIDER\_EN (FRQDIV[4]), the chained counter continuously runs till divided clock reaches low state and stay in low state.

Figure 6-14 Clock Source of Frequency Divider

### 6.7 PDMA Controller (PDMA)

#### 6.7.1 Overview

The NuMicro<sup>®</sup> NUC100 series DMA contains nine-channel peripheral direct memory access (PDMA) controller and a cyclic redundancy check (CRC) generator.

The PDMA that transfers data to and from memory or transfer data to and from APB devices. For PDMA channel (PDMA CH0~CH8), there is one-word buffer as transfer buffer between the Peripherals APB devices and Memory. Software can stop the PDMA operation by disable PDMA PDMA\_CSRx[PDMACEN]. The CPU can recognize the completion of a PDMA operation by software polling or when it receives an internal PDMA interrupt. The PDMA controller can increase source or destination address or fixed them as well.

The DMA controller contains a cyclic redundancy check (CRC) generator that can perform CRC calculation with programmable polynomial settings. The CRC engine supports CPU PIO mode and DMA transfer mode.

#### 6.7.2 Features

- Supports nine PDMA channels and one CRC channel. Each PDMA channel can support a unidirectional transfer

- AMBA AHB master/slave interface compatible, for data transfer and register read/write

- Hardware round robin priority scheme. DMA channel 0 has the highest priority and channel 8 has the lowest priority

- PDMA operation

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed.

- Cyclic Redundancy Check (CRC)

- Supports four common polynomials CRC-CCITT, CRC-8, CRC-16, and CRC-32

- CRC-CCITT:  $X^{16} + X^{12} + X^5 + 1$

- CRC-8:  $X^8 + X^2 + X + 1$

- CRC-16:  $X^{16} + X^{15} + X^2 + 1$

- CRC-32:  $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Supports programmable CRC seed value.

- Supports programmable order reverse setting for input data and CRC checksum.

- Supports programmable 1's complement setting for input data and CRC checksum.

- Supports CPU PIO mode or DMA transfer mode.

- Supports the follows write data length in CPU PIO mode

- 8-bit write mode (byte): 1-AHB clock cycle operation.

- 16-bit write mode (half-word): 2-AHB clock cycle operation.

- 32-bit write mode (word): 4-AHB clock cycle operation.

- Supports byte alignment transfer data length and word alignment transfer source address in CRC DMA mode.

#### 6.8 Timer Controller (TMR)

#### 6.8.1 Overview

The timer controller includes four 32-bit timers, TIMER0~TIMER3, allowing user to easily implement a timer control for applications. The timer can perform functions, such as frequency measurement, event counting, interval measurement, clock generation, and delay timing. The timer can generate an interrupt signal upon time-out, or provide the current value during operation.

#### 6.8.2 Features

- Four sets of 32-bit timers with 24-bit up counter and one 8-bit prescale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Time-out period = (Period of timer clock input) \* (8-bit prescale counter + 1) \* (24-bit TCMP)

- Maximum counting cycle time =  $(1 / T MHz) * (2^8) * (2^{24})$ , T is the period of timer clock

- 24-bit up counter value is readable through TDR (Timer Data Register)

- Supports event counting function to count the event from external pin

- Supports external pin capture function for interval measurement

- Supports external pin capture function for reset timer counter

- Supports chip wake-up from Idle/Power-down mode if a timer interrupt signal is generated (TIF set to 1)

### 6.17 I<sup>2</sup>C Serial Interface Controller (I<sup>2</sup>C)

#### 6.17.1 Overview

$I^2C$  is a two-wire, bidirectional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

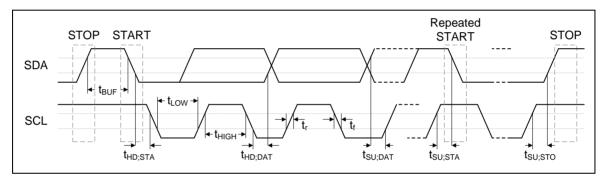

Data is transferred between a Master and a Slave. Data bits transfer on the SCL and SDA lines are synchronously on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first, and an acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to Figure 6-17 for more detailed I<sup>2</sup>C BUS Timing.

Figure 6-17 I<sup>2</sup>C Bus Timing

The device's on-chip  $I^2C$  logic provides a serial interface that meets the  $I^2C$  bus standard mode specification. The  $I^2C$  port handles byte transfers autonomously. To enable this port, the bit ENS1 in I2CON should be set to '1'. The  $I^2C$  hardware interfaces to the  $I^2C$  bus via two pins: SDA and SCL. Pull-up resistor is needed for  $I^2C$  operation as the SDA and SCL are open drain pins. When I/O pins are used as  $I^2C$  ports, user must set the pins function to  $I^2C$  in advance.

| η υνο 1 | no |

|---------|----|

|---------|----|

| DADAMETED                      | 0)/14               | SPECIFICATION |      |      |       |                 | TEST CONDITIONS |     |        |  |

|--------------------------------|---------------------|---------------|------|------|-------|-----------------|-----------------|-----|--------|--|

| PARAMETER                      | SYM.                | MIN.          | TYP. | MAX. | UNIT  | TEST CONDITIONS |                 |     |        |  |

|                                | I <sub>DD16</sub>   |               | 125  |      | μΑ    | 3.3V            | 32.768<br>kHz   | Х   | х      |  |

|                                | I <sub>DD17</sub>   |               | 125  |      |       | $V_{\text{DD}}$ | LIRC            | PLL | All IP |  |

| Operating Current              | IDD17               |               | 125  |      | μA    | 5.5V            | 10 kHz          | Х   | V      |  |

| Normal Run Mode                | I <sub>DD18</sub>   |               | 120  |      | μΑ    | 5.5V            | 10 kHz          | Х   | Х      |  |

| at 10 kHz                      | I <sub>DD19</sub>   |               | 125  |      | μA    | 3.3V            | 10 kHz          | Х   | V      |  |

|                                | I <sub>DD20</sub>   |               | 120  |      | μΑ    | 3.3V            | 10 kHz          | Х   | Х      |  |

|                                | I <sub>IDLE1</sub>  |               | 28   |      | mA    | $V_{\text{DD}}$ | XTAL            | PLL | All IP |  |

| Operating Current              | IDLET               |               | 20   |      | 110.0 | 5.5V            | 12 MHz          | V   | V      |  |

| Idle Mode                      | I <sub>IDLE2</sub>  |               | 10   |      | mA    | 5.5V            | 12 MHz          | V   | Х      |  |

| at 50 MHz                      | I <sub>IDLE3</sub>  |               | 27   |      | mA    | 3.3V            | 12 MHz          | V   | V      |  |

|                                | I <sub>IDLE4</sub>  |               | 9    |      | mA    | 3.3V            | 12 MHz          | V   | Х      |  |

|                                | I <sub>IDLE5</sub>  |               | 7.5  |      | mA    | $V_{\text{DD}}$ | XTAL            | PLL | All IP |  |

| Operating Current              | IDLE5               |               | 7.0  |      |       | 5.5V            | 12 MHz          | Х   | V      |  |

| Idle Mode                      | I <sub>IDLE6</sub>  |               | 2.4  |      | mA    | 5.5V            | 12 MHz          | Х   | Х      |  |

| at 12 MHz                      | I <sub>IDLE7</sub>  |               | 6.5  |      | mA    | 3.3V            | 12 MHz          | Х   | V      |  |

|                                | I <sub>IDLE8</sub>  |               | 1.5  |      | mA    | 3.3V            | 12 MHz          | Х   | Х      |  |

|                                |                     |               | 3.3  |      | mA    | V <sub>DD</sub> | XTAL            | PLL | All IP |  |

| Operating Current              | I <sub>IDLE9</sub>  |               | 3.3  |      | ШA    | 5.5V            | 4 MHz           | Х   | V      |  |

| Idle Mode                      | I <sub>IDLE10</sub> |               | 1.7  |      | mA    | 5.5V            | 4 MHz           | Х   | Х      |  |

| at 4 MHz                       | I <sub>IDLE11</sub> |               | 2.4  |      | mA    | 3.3V            | 4 MHz           | Х   | V      |  |

|                                | I <sub>IDLE12</sub> |               | 0.8  |      | mA    | 3.3V            | 4 MHz           | Х   | Х      |  |

|                                |                     |               |      |      |       | $V_{\text{DD}}$ | XTAL            | PLL | All IP |  |

|                                | I <sub>IDLE13</sub> |               | 133  |      | μA    | 5.5V            | 32.768<br>kHz   | х   | V      |  |

| Operating Current<br>Idle Mode | I <sub>IDLE14</sub> |               | 120  |      | μΑ    | 5.5V            | 32.768<br>kHz   | х   | х      |  |

| at 32.768 kHz                  | I <sub>IDLE15</sub> |               | 133  |      | μA    | 3.3V            | 32.768<br>kHz   | х   | V      |  |

|                                | I <sub>IDLE16</sub> |               | 120  |      | μA    | 3.3V            | 32.768<br>kHz   | х   | х      |  |

| Operating Current              | I <sub>IDLE13</sub> |               | 122  |      | μΑ    | $V_{\text{DD}}$ | LIRC            | PLL | All IP |  |

### 8.4.3 Low Voltage Reset Specification

| PARAMETER             | CONDITION              | MIN. | TYP. | MAX. | UNIT |

|-----------------------|------------------------|------|------|------|------|

| Operation Voltage     | -                      | 0    | -    | 5.5  | V    |

| Quiescent Current     | V <sub>DD</sub> =5.5 V | -    | 1    | 5    | μΑ   |

| Operation Temperature | -                      | -40  | 25   | 85   | °C   |

|                       | Temperature=25℃        | 1.7  | 2.0  | 2.3  | V    |

| Threshold Voltage     | Temperature=-40°C      | -    | 2.4  | -    | V    |

|                       | Temperature=85℃        | -    | 1.6  | -    | V    |

| Hysteresis            | -                      | 0    | 0    | 0    | V    |

### 8.4.4 Brown-out Detector Specification

| PARAMETER         | CONDITION        | MIN. | TYP. | MAX. | UNIT |

|-------------------|------------------|------|------|------|------|

| Operation Voltage | -                | 0    | -    | 5.5  | V    |

| Temperature       | -                | -40  | 25   | 85   | °C   |

| Quiescent Current | $AV_{DD}$ =5.5 V | -    | -    | 125  | μA   |

|                   | BOD_VL[1:0]=11   | 4.2  | 4.4  | 4.6  | V    |

| Brown-out Voltage | BOD_VL [1:0]=10  | 3.5  | 3.7  | 3.9  | V    |

|                   | BOD_VL [1:0]=01  | 2.6  | 2.7  | 2.8  | V    |

|                   | BOD_VL [1:0]=00  | 2.1  | 2.2  | 2.3  | V    |

| Hysteresis        | -                | 30   | -    | 150  | mV   |

### 8.4.5 Power-on Reset Specification

| PARAMETER             | CONDITION           | MIN. | TYP. | MAX. | UNIT |

|-----------------------|---------------------|------|------|------|------|

| Operation Temperature | -                   | -40  | 25   | 85   | °C   |

| Reset Voltage         | V+                  | -    | 2    | -    | V    |

| Quiescent Current     | Vin > reset voltage | -    | 1    | -    | nA   |

### **10 REVISION HISTORY**

| Date       | Revision | Description                                                                                                                                                                                                                |  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2014.05.13 | 1.00     | 1. Preliminary version.                                                                                                                                                                                                    |  |

|            |          | 1. Reorganized the chapter sequence.                                                                                                                                                                                       |  |

| 2015.08.31 | 1.01     | <ol> <li>Added a note in all clock source block diagrams of all peripheral sections<br/>that "Before clock switching, both the pre-selected and newly selected<br/>clock sources must be turned on and stable."</li> </ol> |  |

|            |          | <ol> <li>Revised package size of 64-pin LQFP (10x10x1.4 mm footprint 2.0 mm)<br/>in section 9.2.</li> </ol>                                                                                                                |  |