Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 26x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512gpd064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-20: POWER, GROUND, AND VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS

|                     | Pin N                                  | umber                  |             |                |                                                                                                  |  |  |

|---------------------|----------------------------------------|------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------|--|--|

| Pin Name            | 100-pin<br>TQFP                        | 64-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                      |  |  |

|                     |                                        |                        |             |                | Power and Ground                                                                                 |  |  |

| AVDD                | 30                                     | 19                     | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times.                     |  |  |

| AVss                | 31                                     | 20                     | Р           | Р              | Ground reference for analog modules. This pin must be connected at all times.                    |  |  |

| Vdd                 | 2, 16, 37,<br>46, 62, 86               | 10, 26,<br>38, 57      | Р           | —              | Positive supply for peripheral logic and I/O pins. This pin must be con-<br>nected at all times. |  |  |

| Vss                 | 15, 36,<br>45, 65,<br>75, 85           | 9, 25, 41,<br>56       | Р           | —              | Ground reference for logic, I/O pins, and USB. This pin must be connected at all times.          |  |  |

| VBAT <sup>(1)</sup> | 68                                     | 42                     | Р           | Р              | Battery backup for selected peripherals; otherwise connect to VDD.                               |  |  |

|                     |                                        |                        |             |                | Voltage Reference                                                                                |  |  |

| VREF+               | 29                                     | 16                     | I           | Analog         | Analog Voltage Reference (High) Input                                                            |  |  |

| VREF-               | 28                                     | 15                     | I           | Analog         | Analog Voltage Reference (Low) Input                                                             |  |  |

| Legend:             | CMOS = CM<br>ST = Schmi<br>TTL = Trans | tt Trigger in          | put with    | CMOS leve      | ls O = Output I = Input                                                                          |  |  |

Note 1: VBAT functionality is compromised, see errata for additional information. This pin should be connected to VDD.

# 3.1.4 FLOATING POINT UNIT (FPU)

The Floating Point Unit (FPU), Coprocessor (CP1), implements the MIPS Instruction Set Architecture for floating point computation. The implementation supports the ANSI/IEEE Standard 754 (IEEE for Binary Floating Point Arithmetic) for single- and double-precision data formats. The FPU can be programmed to have thirty-two 32-bit or 64-bit floating point registers used for floating point operations.

The performance is optimized for single precision formats. Most instructions have one FPU cycle throughput and four FPU cycle latency. The FPU implements the multiply-add (MADD) and multiply-sub (MSUB) instructions with intermediate rounding after the multiply function. The result is guaranteed to be the same as executing a MUL and an ADD instruction separately, but the instruction latency, instruction fetch, dispatch bandwidth, and the total number of register accesses are improved.

IEEE denormalized input operands and results are supported by hardware for some instructions. IEEE denormalized results are not supported by hardware in general, but a fast flush-to-zero mode is provided to optimize performance. The fast flush-to-zero mode is enabled through the FCCR register, and use of this mode is recommended for best performance when denormalized results are generated.

The FPU has a separate pipeline for floating point instruction execution. This pipeline operates in parallel with the integer core pipeline and does not stall when the integer pipeline stalls. This allows long-running FPU operations, such as divide or square root, to be partially masked by system stalls and/or other integer unit instructions. Arithmetic instructions are always dispatched and completed in order, but loads and stores can complete out of order. The exception model is "precise" at all times.

Table 3-4 contains the floating point instruction latencies and repeat rates for the processor core. In this table, 'Latency' refers to the number of FPU cycles necessary for the first instruction to produce the result needed by the second instruction. The "Repeat Rate" refers to the maximum rate at which an instruction can be executed per FPU cycle.

#### TABLE 3-4: FPU INSTRUCTION LATENCIES AND REPEAT RATES

| Op code                                                                                                            | Latency<br>(FPU<br>Cycles) | Repeat<br>Rate<br>(FPU<br>Cycles) |

|--------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| ABS.[S,D], NEG.[S,D],<br>ADD.[S,D], SUB.[S,D],<br>C.cond.[S,D], MUL.S                                              | 4                          | 1                                 |

| MADD.S, MSUB.S,<br>NMADD.S, NMSUB.S,<br>CABS.cond.[S,D]                                                            | 4                          | 1                                 |

| CVT.D.S, CVT.PS.PW,<br>CVT.[S,D].[W,L]                                                                             | 4                          | 1                                 |

| CVT.S.D,<br>CVT.[W,L].[S,D],<br>CEIL.[W,L].[S,D],<br>FLOOR.[W,L].[S,D],<br>ROUND.[W,L].[S,D],<br>TRUNC.[W,L].[S,D] | 4                          | 1                                 |

| MOV.[S,D], MOVF.[S,D],<br>MOVN.[S,D],<br>MOVT.[S,D], MOVZ.[S,D]                                                    | 4                          | 1                                 |

| MUL.D                                                                                                              | 5                          | 2                                 |

| MADD.D, MSUB.D,<br>NMADD.D, NMSUB.D                                                                                | 5                          | 2                                 |

| RECIP.S                                                                                                            | 13                         | 10                                |

| RECIP.D                                                                                                            | 26                         | 21                                |

| RSQRT.S                                                                                                            | 17                         | 14                                |

| RSQRT.D                                                                                                            | 36                         | 31                                |

| DIV.S, SQRT.S                                                                                                      | 17                         | 14                                |

| DIV.D, SQRT.D                                                                                                      | 32                         | 29                                |

| MTC1, DMTC1, LWC1,<br>LDC1, LDXC1, LUXC1,<br>LWXC1                                                                 | 4                          | 1                                 |

| MFC1, DMFC1, SWC1,<br>SDC1, SDXC1, SUXC1,<br>SWXC1                                                                 | 1                          | 1                                 |

Legend: S = Single D = DoubleW = Word L = Long word

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | -                 | —                 | _                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | -                 | —                 | _                 | -                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | -                 | —                 | -                 | -                | —                |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | FCC<              | 7:0>              |                   |                  |                  |

# REGISTER 3-8: FCCR: FLOATING POINT CONDITION CODES REGISTER; CP1 REGISTER 25

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FCC<7:0>:** Floating Point Condition Code bits These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

# 4.1.1 BOOT FLASH SEQUENCE AND CONFIGURATION SPACES

Sequence space is used to identify which boot Flash is aliased by aliased regions. If the value programmed into the TSEQ<15:0> bits of the BF1SEQ word is equal to or greater than the value programmed into the TSEQ<15:0> bits of the BF2SEQ word, Boot Flash 1 is aliased by the lower boot alias region, and Boot Flash 2 is aliased by the upper boot alias region. If the TSEQ<15:0> bits of the BF2SEQ word is greater than the TSEQ<15:0> bits of the BF2SEQ word is greater than the TSEQ<15:0> bits of the BF1SEQ word, the opposite is true (see Table 4-2 and Table 4-3 for BFxSEQ word memory locations).

Once boot Flash memories are aliased, configuration space located in the lower boot alias region is used as the basis for the Configuration words, DEVSIGN0, DEVCP0, and DEVCFGx. This means that the boot Flash region to be aliased by lower boot alias region memory must contain configuration values in the appropriate memory locations.

| Note: | Use only Quad Word program operation |

|-------|--------------------------------------|

|       | (NVMOP<3:0> = 0010) when program-    |

|       | ming data into the sequence and      |

|       | configuration spaces.                |

The System Bus arbitration scheme implements a nonprogrammable, Least Recently Serviced (LRS) priority, which provides Quality Of Service (QOS) for most initiators. However, some initiators can use Fixed High Priority (HIGH) arbitration to guarantee their access to data.

The arbitration scheme for the available initiators is shown in Table 4-5.

| Name             | ID | QOS  |

|------------------|----|------|

| CPU-IS           | 1  | LRS  |

| CPU-DS           | 2  | LRS  |

| DMA Read         | 3  | LRS  |

| DMA Write        | 4  | LRS  |

| Flash Controller | 5  | HIGH |

| ICD-JTAG         | 6  | LRS  |

| ADC              | 7  | LRS  |

| USB1             | 8  | LRS  |

| USB2             | 9  | LRS  |

| CAN1             | 10 | LRS  |

| CAN2             | 11 | LRS  |

| CAN3             | 12 | LRS  |

| CAN4             | 13 | LRS  |

TABLE 4-5:INITIATOR ID AND QOS

# 4.3 Permission Access and System Bus Registers

The System Bus on PIC32MK GP/MC family of microcontrollers provides access control capabilities for the transaction initiators on the System Bus.

The System Bus divides the entire memory space into fourteen target regions and permits access to each target by initiators through permission groups. Four Permission Groups (0 through 3) can be assigned to each initiator. Each permission group is independent of the others and can have exclusive or shared access to a region.

Using the CFGPG register (see Register 33-8 in **33.0** "**Special Features**"), Boot firmware can assign a permission group to each initiator, which can make requests on the System Bus.

The available targets and their regions, as well as the associated control registers to assign protection, are described and listed in Table 4-6.

Register 4-2 through Register 4-10 are used for setting and controlling access permission groups and regions.

To change these registers, they must be unlocked in hardware. The register lock is controlled by the PGLOCK Configuration bit (CFGCON<11>). Setting the PGLOCK bit prevents writes to the control registers and clearing the PGLOCK bit allows writes.

To set or clear the PGLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators** with Enhanced PLL" (DS60001250) in the *"PIC32 Family Reference Manual"* for details.

# 8.2 Interrupts

The PIC32MK GP/MC family uses variable offsets for vector spacing. This allows the interrupt vector spacing to be configured according to application needs. A unique interrupt vector offset can be set for each vector using its associated OFFx register.

For details on the Variable Offset feature, refer to **8.5.2 "Variable Offset"** in **Section 8. "Interrupt Controller"** (DS60001108) of the *"PIC32 Family Reference Manual"*.

Table 8-3 provides the Interrupt IRQ, vector and bit location information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | —                      | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | —                      | _                 | _                 | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0                  | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | _                 | SUSPEND <sup>(1)</sup> | DMABUSY           | -                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 | _                 | _                      | _                 |                   | _                | _                |

### REGISTER 11-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** DMA On bit

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit<sup>(1)</sup>

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active and is transferring data

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the DMA module completes the current transaction and responds to this request. The user application should poll the BUSY bit to verify that the request has been honored.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 21.24        | U-0                   | U-0              |

| 31:24        | -                 | —                 | —                 | —                 | —                 | -                 | —                     | —                |

| 23:16        | U-0                   | U-0              |

| 23.10        | -                 | —                 |                   | _                 | _                 | _                 | _                     | _                |

| 15:8         | U-0                   | U-0              |

| 10.0         | —                 | —                 | _                 | _                 | _                 | _                 | _                     |                  |

|              | R/W-0                 | R/W-0            |

| 7:0          | DTOFE             |                   | 5.4455            | DTOFE             | DENGEE            | 0004055           | CRC5EE <sup>(1)</sup> |                  |

|              | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |

|              |                   |                   |                   |                   |                   |                   |                       |                  |

#### **REGISTER 12-9:** UxEIE: USB ERROR INTERRUPT ENABLE REGISTER ('x' = 1 AND 2)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>BTSEE:</b> Bit Stuff Error Interrupt Enable bit |

|-------|----------------------------------------------------|

|       |                                                    |

- 1 = BTSEF interrupt is enabled

- 0 = BTSEF interrupt is disabled

- bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt is enabled

- 0 = BMXEF interrupt is disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt is enabled

- 0 = DMAEF interrupt is disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt is enabled

- 0 = BTOEF interrupt is disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 **PIDEE:** PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- **Note 1:** Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (UxIE<1>) must be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | -                 | —                 | —                 | -                 | -                 | _                 | -                | -                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | -                 | —                 | —                 | -                 | -                 | _                 | -                | -                |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | _                 | —                 |                   | _                 | _                 | _                 | _                | _                |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |  |  |  |

## REGISTER 12-16: UxSOF: USB SOF THRESHOLD REGISTER ('x' = 1 AND 2)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

Typical values of the threshold are:

- 01001010 = 64-byte packet

- 00101010 = 32-byte packet

- 00011010 = 16-byte packet

00010010 = 8-byte packet

#### REGISTER 12-17: UxBDTP1: USB BDT PAGE 1 REGISTER ('x' = 1 AND 2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | -                 | -                 | -                 | -                 | -                 | —                 | -                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   |                   |                   |                   |                   | —                 |                  | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 10.0         | -                 |                   |                   |                   |                   | —                 | -                | —                |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |

| 7.0          | BDTPTRL<15:9>     |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-1 **BDTPTRL<15:9>:** BDT Base Address bits This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory. The 32-bit BDT base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

# TABLE 13-16: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                  |               |       |       |       |       |       |       |      | B    | its  |      |      |      |        |                |      |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|--------|----------------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3   | 18/2           | 17/1 | 16/0 | All Resets |

| 16D0                        | RPD4R            | 31:16<br>15:0 |       |       |       |       | _     |       |      |      |      |      | _    | _    | —<br>F | —<br>RPD4R<4:0 | -    | -    | 0000       |

| 16D4                        | RPD5R            | 31:16<br>15:0 | _     | _     |       |       | _     | _     | _    | _    |      |      | _    | —    | _      |                | _    | —    | 0000       |

| 16D8                        | RPD6R            | 31:16<br>15:0 | _     |       |       |       |       |       |      |      |      |      | _    | _    | —      | —<br>RPD6R<4:0 | _    | _    | 0000       |

| 1700                        | RPE0R            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      | _    |      | F      | —<br>RPE0R<4:0 | -    | —    | 0000       |

| 1704                        | RPE1R            | 31:16<br>15:0 | _     |       |       |       |       |       |      |      |      |      | _    | -    | — F    | —<br>RPE1R<4:0 | -    | _    | 0000       |

| 1738                        | RPE14R           | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      | _    | _    | —      | —<br>PF14R<4:( | >    | -    | 0000       |

| 173C                        | RPE15R           | 31:16<br>15:0 |       | _     |       |       | _     | _     | _    | _    |      |      | _    | _    | R      | —<br>PE15R<4:( | )>   | _    | 0000       |

| 1740                        | RPF0R            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      | _    | -    | —F     | —<br>RPF0R<4:0 | -    | _    | 0000       |

| 1744                        | RPF1R            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      | _    | -    | —F     | —<br>RPF1R<4:0 | -    | _    | 0000       |

| 1780                        | RPG0R            | 31:16<br>15:0 | -     |       |       |       |       |       |      |      |      |      | _    | _    | — F    | —<br>RPG0R<4:0 | -    | —    | 0000       |

| 1784                        | RPG1R            | 31:16<br>15:0 | -     |       |       |       |       |       |      |      | -    |      | _    | -    | —<br>F | —<br>RPG1R<4:0 | -    | —    | 0000       |

| 1798                        | RPG6R            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      | -    | — F    | —<br>RPG6R<4:0 | -    | —    | 0000       |

| 179C                        | RPG7R            | 31:16<br>15:0 | -     |       |       |       |       |       |      |      |      |      | _    | _    | — F    | —<br>RPG7R<4:0 | -    | —    | 0000       |

| 17A0                        | RPG8R            | 31:16<br>15:0 | -     |       |       |       |       |       |      |      |      |      | _    |      | — F    | —<br>RPG8R<4:0 | -    | —    | 0000       |

| 17A4                        | RPG9R            | 31:16<br>15:0 | _     |       |       |       |       |       |      |      |      |      | _    | _    | — F    | —<br>RPG9R<4:0 | -    | —    | 0000       |

| 17B0                        | RPG12R           | 31:16<br>15:0 | _     | —     | _     | _     | _     | —     | —    | _    | _    | _    | _    |      | — R    | —<br>PG12R<4:( | )>   | —    | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## **REGISTER 18-1:** ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER ('x' = 1-16) (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- Note 1: Refer to Table 18-1 for Timerx and Timery selections.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            |                   | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   | _                 |                   |                       | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            |                   | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                     | MODIF             | CTMRIF            | RBIF             | TBIF             |

# **REGISTER 26-3:** CxINT: CAN INTERRUPT REGISTER ('x' = 1-4)

IVRIE: Invalid Message Received Interrupt Enable bit

## Legend:

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

|           | 1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | CERRIE: CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                   |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                |

| bit 19    | MODIE: Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                       |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                             |

| bit 15    | IVRIF: Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CxCON<15>).                                          |

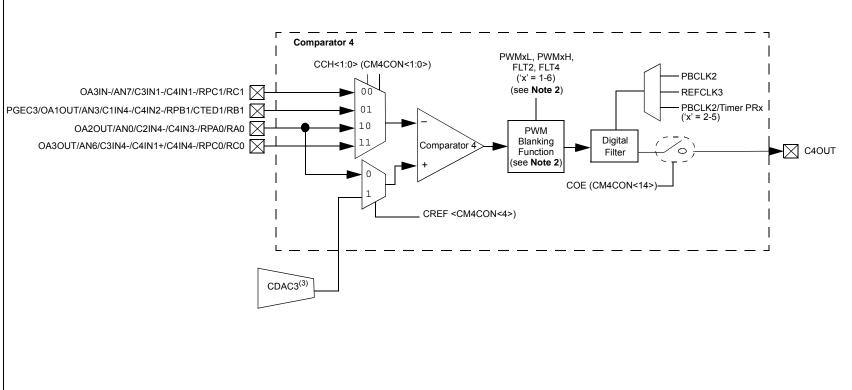

# FIGURE 27-4: COMPARATOR 4 MODULE BLOCK DIAGRAM

- Note 1: Refer to the device pin tables (Table 3 and Table 5) for other analog inputs that may be also be connected to the Op amp and Comparator inputs.

- 2: The PWM Blank Function is only available on PIC32MKXXMCXXX devices.

- 3: Caution: To avoid false comparator output faults or glitches when using the internal DAC as a comparator reference, always initialize the DAC before initializing and enabling the comparator.

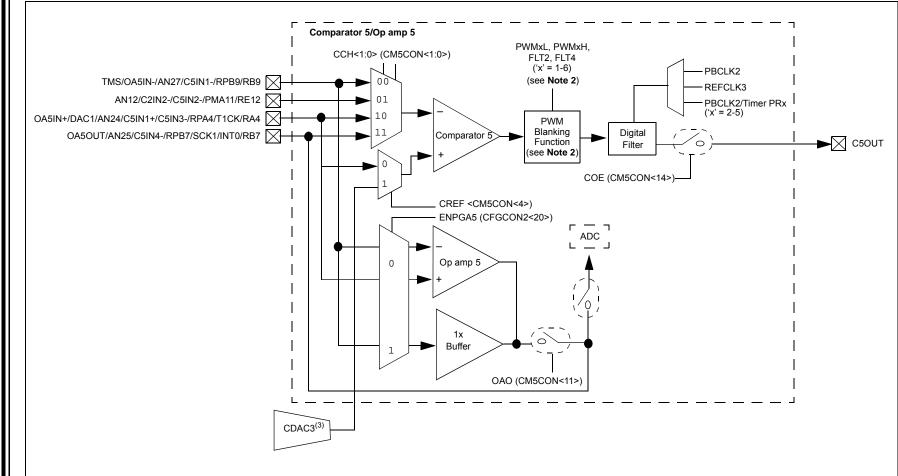

# FIGURE 27-5: OP AMP 5/COMPARATOR 5 MODULE BLOCK DIAGRAM

- Note 1: Refer to the device pin tables (Table 3 and Table 5) for other analog inputs that may be also be connected to the Op amp and Comparator inputs.

- 2: The PWM Blank Function is only available on PIC32MKXXMCXXX devices.

- 3: Caution: To avoid false comparator output faults or glitches when using the internal DAC as a comparator reference, always initialize the DAC before initializing and enabling the comparator.

# REGISTER 28-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

| REGIST    | R 28-1: CTMUCON: CTMU CONTROL                                                | . REGISTER (CONTINUED)                                     |

|-----------|------------------------------------------------------------------------------|------------------------------------------------------------|

| bit 25    | EDG2STAT: Edge 2 Status bit                                                  |                                                            |

|           | Indicates the status of Edge 2 and can be writ                               | ten to control edge source                                 |

|           | 1 = Edge 2 has occurred                                                      |                                                            |

|           | 0 = Edge 2 has not occurred                                                  |                                                            |

| bit 24    | EDG1STAT: Edge 1 Status bit                                                  |                                                            |

|           | Indicates the status of Edge 1 and can be write                              | ten to control edge source                                 |

|           | 1 = Edge 1 has occurred                                                      |                                                            |

|           | 0 = Edge 1 has not occurred                                                  |                                                            |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                     |                                                            |

|           | 1 = Input is edge-sensitive                                                  |                                                            |

|           | 0 = Input is level-sensitive                                                 |                                                            |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                          |                                                            |

|           | 1 = Edge 2 programmed for a positive edge re                                 | esponse                                                    |

|           | 0 = Edge 2 programmed for a negative edge                                    | esponse                                                    |

| bit 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                      |                                                            |

|           | 1111 = C5OUT Capture Event is selected                                       |                                                            |

|           | 1110 = C4OUT pin is selected                                                 |                                                            |

|           | 1101 = C1OUT pin is selected                                                 |                                                            |

|           | 1100 = IC6 Capture Event is selected                                         |                                                            |

|           | 1011 = IC5 Capture Event is selected<br>1010 = IC4 Capture Event is selected |                                                            |

|           | 1001 = IC3 pin is selected                                                   |                                                            |

|           | 1000 = IC2  pin is selected                                                  |                                                            |

|           | 0111 = IC1 pin is selected                                                   |                                                            |

|           | 0110 = OC4 pin is selected                                                   |                                                            |

|           | 0101 = OC3 pin is selected                                                   |                                                            |

|           | 0100 = OC2 pin is selected                                                   |                                                            |

|           | 0011 = CTED1 pin is selected<br>0010 = CTED2 pin is selected                 |                                                            |

|           | 0001 = OC1 Compare Event is selected                                         |                                                            |

|           | 0000 = Timer1 Event is selected                                              |                                                            |

| bit 17-16 | Unimplemented: Read as '0'                                                   |                                                            |

| bit 15    | <b>ON:</b> ON Enable bit                                                     |                                                            |

|           | 1 = Module is enabled                                                        |                                                            |

|           | 0 = Module is disabled                                                       |                                                            |

| bit 14    | Unimplemented: Read as '0'                                                   |                                                            |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                              |                                                            |

|           | 1 = Discontinue module operation when device                                 | e enters Idle mode                                         |

|           | 0 = Continue module operation in Idle mode                                   |                                                            |

| Note 1:   | When this bit is set for Pulse Delay Generation                              | n, the EDG2SEL<3:0> bits must be set to '1101' to select   |

|           | C1OUT.                                                                       |                                                            |

| 2:        |                                                                              | is not automatically discharged between sample/conversion  |

|           |                                                                              | apacitive measurement, must discharge the ADC capacitor    |

|           | perore conducting the measurement. The IDI                                   | SSEN bit, when set to '1', performs this function. The ADC |

- cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 36-43) in Section 36.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

- 5: For CTMU temperature measurements on this range, ADC sampling time  $\geq$  1.6  $\mu s.$

- 6: For CTMU temperature measurements on this range, ADC sampling time  $\geq$  300 ns.

# 33.3 On-Chip Voltage Regulator

The core and digital logic for all PIC32MK GP/MC devices is designed to operate at a nominal 1.2V. To simplify system designs, devices in the PIC32MK GP/ MC family incorporate an on-chip regulator providing the required core logic voltage from VDD.

### 33.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

### 33.3.2 ON-CHIP REGULATOR AND BOR

PIC32MK GP/MC devices also have a simple brownout capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **36.1 "DC Characteristics"**.

# 33.4 On-chip Temperature Sensor

PIC32MK GP/MC devices include a temperature sensor that provides accurate measurement of a device's junction temperature (see **36.2** "AC **Characteristics and Timing Parameters**" for more information).

The temperature sensor is connected to the ADC module and can be measured using the shared S&H circuit (see 25.0 "12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC)" for more information).

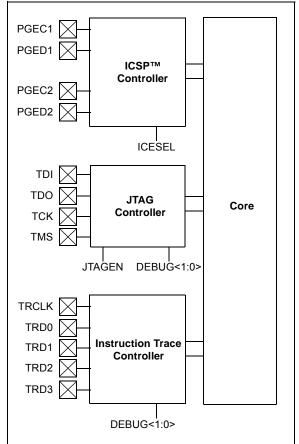

# 33.5 Programming and Diagnostics

PIC32MK GP/MC devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32MK devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

#### FIGURE 33-1:

#### BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

## TABLE 36-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

| DC CHA | DC CHARACTERISTICS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.2V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                             |  |  |  |

|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------|--|--|--|

| Param. | Sym.               | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min. | Тур.                                                                                                                                                                                                                                                                                 | Max. | Units | Conditions <sup>(1)</sup>   |  |  |  |

|        |                    | Output High Voltage           I/O Pins:           4x Source Driver Pins -           RA0, RA4, RA11, RA12, RA14, RA15           RB0-RB3, RB8, RB9           RC0, RC1, RC2, RC10, RC12, RC13           RD8, RD12-RD15           RE0, RE1, RE8, RE9           RF5, RF6, RF7, RF9, RF10, RF12, RF13           RG0, RG1, RG6-RG15           Output High Voltage           I/O Pins:           8x Source Driver Pins -           8x Source Driver Pins -           RA1, RA7, RA8, RA10           RB4-RB7, RB10-RB15           RC6, RC7, RC8, RC9, RC11, RC15           RD1-RD6           RE12-RE15           RF0, RF1 | 1.5  | _                                                                                                                                                                                                                                                                                    | _    | v     | IOH ≥ -14 mA, VDD = 3.3V    |  |  |  |

|        |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.0  | _                                                                                                                                                                                                                                                                                    |      | V     | ІОн ≥ -12 mA, VDD = 3.3V    |  |  |  |

| DO20a  | Vон1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.0  | _                                                                                                                                                                                                                                                                                    | _    | v     | IOH $\ge$ -7 mA, VDD = 3.3V |  |  |  |

| DOZUA  | VONT               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.5  | _                                                                                                                                                                                                                                                                                    | _    | V     | IOH ≥ -22 mA, VDD = $3.3$ V |  |  |  |

|        |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.0  | _                                                                                                                                                                                                                                                                                    |      | V     | ІОн ≥ -18 mA, VDD = 3.3V    |  |  |  |

|        |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.0  | _                                                                                                                                                                                                                                                                                    | _    | v     | Іон ≥ -10 mA, Vod = 3.3V    |  |  |  |

Note 1: Parameters are characterized, but not tested.

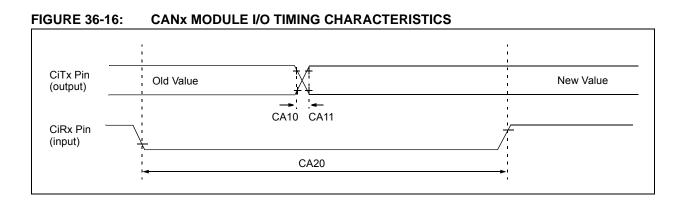

### TABLE 36-38: CANX MODULE I/O TIMING REQUIREMENTS

| AC CHARA     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                               |      |                     |      |       |                    |

|--------------|-------------------------------------------------------|-------------------------------|------|---------------------|------|-------|--------------------|

| Param<br>No. | Symbol                                                | Characteristic <sup>(1)</sup> | Min. | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| CA10         | TioF                                                  | Port Output Fall Time         | —    |                     | _    | ns    | See parameter DO32 |

| CA11         | TioR                                                  | Port Output Rise Time         |      | _                   | _    | ns    | See parameter DO31 |

| CA20         |                                                       |                               |      |                     |      | ns    | —                  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

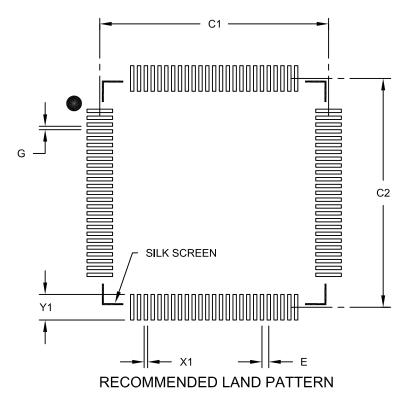

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units |      |          |      |  |

|---------------------------|-------|------|----------|------|--|

| Dimension                 | MIN   | NOM  | MAX      |      |  |

| Contact Pitch             | E     |      | 0.40 BSC |      |  |

| Contact Pad Spacing       | C1    |      | 13.40    |      |  |

| Contact Pad Spacing       | C2    |      | 13.40    |      |  |

| Contact Pad Width (X100)  | X1    |      |          | 0.20 |  |

| Contact Pad Length (X100) | Y1    |      |          | 1.50 |  |

| Distance Between Pads     | G     | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support