Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                          |

| Number of I/O              | 77                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                      |

| Data Converters            | A/D 42x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512gpd100-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For additional information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

## 2.5 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.6 Trace

When present on select pin counts, the trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

## 2.7 External Oscillator Pins

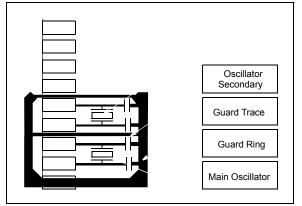

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: The microAptiv<sup>™</sup> CPU core resources are available at: www.imgtec.com.

The MIPS32<sup>®</sup> microAptiv<sup>™</sup> MCU Core is the heart of the PIC32MK GP/MC family device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

Key features include:

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 5):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- Virtual memory support

- microMIPS<sup>™</sup> compatible instruction set:

- Improves code size density over MIPS32, while maintaining MIPS32 performance.

- Supports all MIPS32 instructions (except branchlikely instructions)

- Fifteen additional 32-bit instructions and 39 16-bit instructions corresponding to commonly-used MIPS32 instructions

- Stack pointer implicit in instruction

- MIPS32 assembly and ABI compatible

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x32 multiply per clock

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value breakpoints

- Hardware breakpoint supports both address match and address range triggering.

- Eight instruction and four data complex breakpoints

- iFlowtrace<sup>®</sup> version 2.0 support:

- Real-time instruction program counter

- Special events trace capability

- Two performance counters with 34 userselectable countable events

- Disabled if the processor enters Debug mode

- Program Counter sampling

- DSP ASE Extension:

- Native fractional format data type operations

- Register Single Instruction Multiple Data (SIMD) operations (add, subtract, multiply, shift)

- GPR-based shift

- Bit manipulation

- Compare-Pick

- DSP Control Access

- Indexed-Load

- Branch

- Multiplication of complex operands

- Variable bit insertion and extraction

- Virtual circular buffers

- Arithmetic saturation and overflow handling

- Zero-cycle overhead saturation and rounding operations

- Floating Point Unit (FPU):

- 1985 IEEE-754 compliant Floating Point Unit

- Supports single and double precision datatypes

- 2008 IEEE-754 compatibility control of NaN handling and Abs/Neg instructions

- Runs at 1:1 core/FPU clock ratio

# 8.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108) and Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MK GP/MC devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Controller module exists outside of the CPU and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in **8.1 "CPU Exceptions"**.

The Interrupt Controller module includes the following features:

- Up to 216 interrupt sources and vectors with dedicated programmable offsets, eliminating the need for redirection

- Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- · Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Two shadow register sets that can be used for any priority level, eliminating software context switch and reducing interrupt latency

- · Software can generate any interrupt

Table 8-1 provides Interrupt Service routine (ISR) latency information.

## 8.2 Interrupts

The PIC32MK GP/MC family uses variable offsets for vector spacing. This allows the interrupt vector spacing to be configured according to application needs. A unique interrupt vector offset can be set for each vector using its associated OFFx register.

For details on the Variable Offset feature, refer to **8.5.2 "Variable Offset"** in **Section 8. "Interrupt Controller"** (DS60001108) of the *"PIC32 Family Reference Manual"*.

Table 8-3 provides the Interrupt IRQ, vector and bit location information.

## TABLE 13-15: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| ss                          |                  |           |       |       |       |       |       |       |      | B    | Bits |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 1480                        | U4CTSR           | 31:16     | _     | —     | —     | _     | _     | _     | —    | _    | —    | —    | _    | —    | _    | _     | _      | -    | 0000       |

| 1460                        | 04015R           | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | U4CTS | R<3:0> |      | 0000       |

| 1484                        | U5RXR            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | —    | —    | -    | _    | -    |       |        | —    | 0000       |

| 1404                        | USKAR            | 15:0      |       | —     | —     | _     | _     | _     | _    | _    | —    | —    | -    | _    |      | U5RXI | R<3:0> | •    | 0000       |

| 1488                        | U5CTSR           | 31:16     | —     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    | —    | _     | —      | —    | 0000       |

| 1400                        | USCISK           | 15:0      | —     | —     | —     | —     | _     | —     | —    | _    | —    | —    | _    | —    |      | U5CTS | R<3:0> |      | 0000       |

| 148C                        | U6RXR            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | —    | —    | -    | _    | -    |       |        | —    | 0000       |

| 1400                        | UORAR            | 15:0      | —     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | U6RXI | R<3:0> | •    | 0000       |

| 1490                        | U6CTSR           | 31:16     | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| 1490                        | UCISK            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | U6CTS | R<3:0> |      | 0000       |

| 1498                        | SDI1R            | 31:16     | _     | —     | —     | _     | —     | _     | —    | _    | —    | —    | —    | —    | —    | _     | _      | —    | 0000       |

| 1490                        | SDIIK            | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI1F | R<3:0> |      | 0000       |

| 149C                        | SS1R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    | _    | —     | —      | —    | 0000       |

| 1490                        | 55 IK            | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | SS1R  | <3:0>  | •    | 0000       |

| 1444                        | SDI2R            | 31:16     | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| 14A4                        | SDIZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | SDI2F | <3:0>  |      | 0000       |

| 14A8                        | SS2R             | 31:16     | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    | —    | _     | —      | —    | 0000       |

| 14A0                        | 332R             | 15:0      | _     | —     | —     | _     | —     | _     | —    | —    | —    | —    | —    | —    |      | SS2R  | <3:0>  |      | 0000       |

| 14AC                        | SCK3R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    | _    | —     | —      | —    | 0000       |

| 14AC                        | SCRJR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | SCK3  | R<3:0> |      | 0000       |

| 14B0                        | SDI3R            | 31:16     | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| 1460                        | SDISK            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | SDI3F | <3:0>  |      | 0000       |

| 14B4                        | SS3R             | 31:16     | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    | —    | _     | —      | —    | 0000       |

| 1404                        | 333K             | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | SS3R  | <3:0>  |      | 0000       |

| 14B8                        | SCK4R            | 31:16     | _     | —     | —     | —     | _     | —     | —    | _    | —    | —    | _    | —    | _    | —     | —      | —    | 0000       |

| 1400                        | 30N4K            | 15:0      |       | —     | —     | —     |       | —     | —    |      | —    | —    |      | —    |      | SCK4  | R<3:0> |      | 0000       |

| 14BC                        | SDI4R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | _      | —    | 0000       |

| 14BC                        | SDI4K            | 15:0      |       | —     | —     | —     |       | —     | —    |      | —    | —    |      | —    |      | SDI4F | <3:0>  |      | 0000       |

| 1400                        | SS4R             | 31:16     | -     | —     | —     | —     |       | —     |      |      | —    | —    | -    | —    | _    | —     | —      | —    | 0000       |

| 14C0                        | 554K             | 15:0      | -     | —     | —     | —     |       | —     |      |      | —    | —    | -    | —    |      | SS4R  | <3:0>  |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

3: This register is only available on PIC32MKXXXGPEXXX devices.

# DS60001402E-page 266

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | -                |                  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | —                 | —                 | —                 | _                 | _                |                  |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0      | —                 | —                 | —                 | —                 | —                 | _                 | -                | _                |

| 7:0       | R-0, HC           | R-0, HC           | R-0, HC           | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R-0              |

| 7:0       | BAD1              | BAD2              | DMTEVENT          |                   |                   |                   |                  | WINOPN           |

## REGISTER 16-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared |                       |                    |

|-------------------|-----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared  | x = Bit is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

|          | Note: This bit is cleared only on a Reset.                                                                                          |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

## TABLE 19-3: OUTPUT COMPARE 10 THROUGH OUTPUT COMPARE 16 REGISTER MAP (CONTINUED)

| ess                       |                                 | 6             |       |                   |       |       |       |       |      | В     | its     |      |      |       |        |      |          |      | s          |

|---------------------------|---------------------------------|---------------|-------|-------------------|-------|-------|-------|-------|------|-------|---------|------|------|-------|--------|------|----------|------|------------|

| Virtual Address<br>BF84_# | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14             | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets |

| 5000                      | OC15CON                         | 31:16         | —     | —                 | _     | —     |       | _     | —    | _     | _       | —    | _    |       | —      |      | —        |      | 0000       |

| 5000                      |                                 | 15:0          | ON    | —                 | SIDL  | —     | _     | —     | —    | _     | —       | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000       |

| 5C10                      | OC15R                           | 31:16         |       |                   |       |       |       |       |      | 00155 | <31:0>  |      |      |       |        |      |          |      | xxxx       |

| 0010                      | OCIDIC                          | 15:0          |       |                   |       |       |       |       |      | 00101 | 1.05    |      |      |       |        |      |          |      | xxxx       |

| 5C20                      | OC15RS                          | 31:16         |       |                   |       |       |       |       |      | 0C15P | S<31:0> |      |      |       |        |      |          |      | xxxx       |

| 3020                      | 0013K3                          | 15:0          |       |                   |       |       |       |       |      | 00156 | 3~31.02 |      |      |       |        |      |          |      | xxxx       |

| 5500                      | OC16CON                         | 31:16         | —     | —                 | —     | -     |       | —     | —    | —     | —       | —    | —    | —     | -      | -    | —        |      | 0000       |

| 3200                      |                                 | 15:0          | ON    | —                 | SIDL  | —     | _     | _     | —    | _     | —       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000       |

| 5E10                      | OC16R                           | 31:16         |       |                   |       |       |       |       |      | 00165 | <31:0>  |      |      |       |        |      |          |      | xxxx       |

| 5210                      | CONK                            | 15:0          |       |                   |       |       |       |       |      | 00106 |         |      |      |       |        |      |          |      | xxxx       |

| 5E20                      | OC16RS                          | 31:16<br>15:0 |       | OC16RS<31:0> xxxx |       |       |       |       |      |       |         |      |      |       |        |      |          |      |            |

PIC32MK GP/MC Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5           | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-----------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0                         | U-0               | U-0               | U-0 U-0           |                  | U-0              |  |  |  |  |  |

| 31.24        | —                 | —                 | —                           | —                 | —                 |                   |                  | —                |  |  |  |  |  |

|              | R/W-0             | R/W-0             | R/W-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | CS2a              | CS1a              |                             | ADDR<21:16>       |                   |                   |                  |                  |  |  |  |  |  |

|              | WADDR23           | WADDR22           |                             |                   |                   |                   |                  |                  |  |  |  |  |  |

|              | R/W-0             | R/W-0             | R/W-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | CS2               | CS1               |                             |                   |                   | -12:05            |                  |                  |  |  |  |  |  |

|              | ADDR15            | ADDR14            |                             |                   | ADDR              | <13:8>            |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                  |                  |  |  |  |  |  |

| ADDR<7:0>    |                   |                   |                             |                   |                   |                   |                  |                  |  |  |  |  |  |

## REGISTER 23-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

| Note:     | If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                                                                                                                                                        |

| bit 13-0  | ADDR<13:0>: Address bits                                                                                                                                                                               |

|           | This bit is only valid when the CSF<1:0> bits = 01 or 00 or EXADR bit = 1.                                                                                                                             |

| bit 14    | ADDR<14>: Target Address bit 14                                                                                                                                                                        |

|           | 0 = Chip Select 1 is disabled                                                                                                                                                                          |

|           | 1 = Chip Select 1 is enabled                                                                                                                                                                           |

| S.C. 1 1  | This bit is only valid when the CSF<1:0> bits = $10$ or $01$ or EXADR bit = $0$ .                                                                                                                      |

| bit 14    | <b>CS1:</b> Chip Select 1 bit                                                                                                                                                                          |

| SIL IO    | This bit is only valid when the CSF<1:0> bits = $10$ or $01$ and the EXADDR bit = $0$ .                                                                                                                |

| bit 15    | ADDR<15>: Target Address bit 15                                                                                                                                                                        |

|           | <ul> <li>1 = Chip Select 2 is enabled</li> <li>0 = Chip Select 2 is disabled</li> </ul>                                                                                                                |

|           | This bit is only valid when the CSF<1:0> bits = $10$ or $01$ and the EXADR bit = $0$ .                                                                                                                 |

| bit 15    | <b>CS2:</b> Chip Select 2 bit                                                                                                                                                                          |

|           | These bits are only valid when the EXADR bit = 1 and the DUALBUF bit = $0$ .                                                                                                                           |

| bit 21-16 | ADDR<21:16>: Address bits                                                                                                                                                                              |

|           | This bit is only valid when the CSF<1:0> bits = 00 and the EXADR bit = 1 and the DUALBUF bit = 0.                                                                                                      |

| bit 22    | WADDR22: Address bits                                                                                                                                                                                  |

|           | 0 = Chip Select 1a is disabled                                                                                                                                                                         |

|           | 1 = Chip Select 1a is enabled                                                                                                                                                                          |

|           | This bit is only valid when the CSF<1:0> bits = $10$ .                                                                                                                                                 |

| bit 22    | <b>CS1a:</b> Chip Select 1a bit                                                                                                                                                                        |

| 511 20    | This bit is only valid when the CSF<1:0> bits = $0.0$ and the EXADR bit = $1$ and the DUALBUF bit = $0.0$                                                                                              |

| bit 23    | WADDR23: Address bits                                                                                                                                                                                  |

|           | 1 = Chip Select 2a is enabled<br>0 = Chip Select 2a is disabled                                                                                                                                        |

|           | This bit is only valid when the CSF<1:0> bits = $10 \text{ or } 01$ .                                                                                                                                  |

| bit 23    | CS2a: Chip Select 2a bit                                                                                                                                                                               |

| 1.1.00    |                                                                                                                                                                                                        |

| Bit<br>Range | Bit<br>31/23/15/7 |       |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | -                 |       | _     | _                 | _                 | _                 | _                | —                |  |  |

| 00.40        | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | —     | _     | _                 | _                 | _                 | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |       |       | RDATAIN<          | 15:8>             |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | RDATAIN<7:0>      |       |       |                   |                   |                   |                  |                  |  |  |

## REGISTER 23-10: PMRDIN: PARALLEL PORT READ INPUT DATA REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 **RDATAIN<15:8>:** Port Data <15:8> Input bits Only valid when MODE16 = 1. Used for read operations in Dual Buffer Master mode only. bit 7-0 **RDATAIN<7:0>:** Port Data <7:0> Input bits

Used for read operations in Dual Buffer Master mode only.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1' and exclusively for reads. If the DUALBUF bit is '0', the PMDIN register (Register 23-5) is used for reads instead of PMRDIN.

## REGISTER 25-1: ADCCON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 12 AICPMPEN: Analog Input Charge Pump Enable bit

- 1 = Analog input charge pump is enabled

- 0 = Analog input charge pump is disabled (default)

- **Note 1:** For proper analog operation at VDD less than 2.5V, the AICPMPEN bit must be = 1, and the IOANCPEN bit in the CFGCON register must be set to '1'. This bit must not be set if VDD is greater than 2.5V.

- 2: ADC throughput rate performance is reduced, as defined in the following table, if AICPMPEN = 1 or IOANCPEN (CFGCON<7) = 1.

| ADC0 | ADC1 | ADC2 | ADC3 | ADC4 | ADC5 | ADC7 | Maximum Sum of Total<br>ADC Throughputs |

|------|------|------|------|------|------|------|-----------------------------------------|

| ON   | OFF  | OFF  | OFF  | OFF  | OFF  | OFF  | 2 Msps                                  |

| ON   | ON   | OFF  | OFF  | OFF  | OFF  | OFF  | 4 Msps                                  |

| ON   | ON   | ON   | OFF  | OFF  | OFF  | OFF  | 5 Msps                                  |

| OFF  | OFF  | OFF  | ON   | OFF  | OFF  | OFF  | 2 Msps                                  |

| OFF  | OFF  | OFF  | ON   | ON   | OFF  | OFF  | 4 Msps                                  |

| OFF  | OFF  | OFF  | ON   | ON   | ON   | OFF  | 5 Msps                                  |

| OFF  | OFF  | OFF  | ON   | ON   | ON   | ON   | 5 Msps                                  |

| ON   | ON   | ON   | ON   | OFF  | OFF  | OFF  | 7 Msps                                  |

| ON   | ON   | ON   | ON   | ON   | OFF  | OFF  | 9 Msps                                  |

| ON   | ON   | ON   | ON   | ON   | ON   | OFF  | 10 Msps                                 |

| ON   | OFF  | OFF  | ON   | ON   | ON   | ON   | 7 Msps                                  |

| ON   | ON   | OFF  | ON   | ON   | ON   | ON   | 9 Msps                                  |

| ON   | 10 Msps                                 |

bit 11 CVDEN: Capacitive Voltage Division Enable bit

1 = CVD operation is enabled

0 = CVD operation is disabled

bit 10 **FSSCLKEN:** Fast Synchronous System Clock to ADC Control Clock bit

- 1 = Fast synchronous system clock to ADC control clock is enabled

- 0 = Fast synchronous system clock to ADC control clock is disabled

bit 9 FSPBCLKEN: Fast Synchronous Peripheral Clock to ADC Control Clock bit

- 1 = Fast synchronous peripheral clock to ADC control clock is enabled

- 0 = Fast synchronous peripheral clock to ADC control clock is disabled

#### bit 8-7 Unimplemented: Read as '0'

#### bit 6-4 IRQVS<2:0>: Interrupt Vector Shift bits

To determine interrupt vector address, this bit specifies the amount of left shift done to the AIRDYx status bits in the ADCDSTAT1 and ADCDSTAT2 registers, prior to adding with the ADCBASE register.

Interrupt Vector Address = Read Value of ADCBASE and Read Value of ADCBASE = Value written to ADCBASE +  $x \ll$  IRQVS<2:0>, where 'x' is the smallest active input ID from the ADCDSTAT1 or ADCDSTAT2 registers (which has highest priority).

- 111 = Shift x left 7 bit position

- 110 = Shift x left 6 bit position

- 101 = Shift x left 5 bit position

- 100 = Shift x left 4 bit position

- 011 =Shift x left 3 bit position

- 010 =Shift x left 2 bit position

- 001 =Shift x left 1 bit position

- 000 = Shift x left 0 bit position

#### REGISTER 25-1: ADCCON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 3 STRGLVL: Scan Trigger High Level/Positive Edge Sensitivity bit

- 1 = Scan trigger is high level sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), the scan trigger will continue for all selected analog inputs, until the STRIG option is removed.

- 0 = Scan trigger is positive edge sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), only a single scan trigger will be generated, which will complete the scan of all selected analog inputs.

#### bit 2-0 **DMABL<2:0>:** DMA to System RAM Buffer Length Size bits

These bits define the number of locations in system memory allocated per analog input for DMA interface use.

Because each output data is 16-bit wide, one location consists of 2 bytes. Therefore the actual size reserved in the System RAM follows the formula: RAM Buffer Length in bytes = 2(DMABL+1).

The DMABL field can also be thought of as a "Left Shift Amount +1" needed for the channel ID to create the DMA byte address offset to be added to the contents of ADDMAB in order to obtain the byte address of the beginning of the System RAM buffer area allocated for the given channel.

111 = Allocates 128 locations in system memory to each analog input, actually 256 bytes

110 = Allocates 64 locations in system memory to each analog input, actually 128 bytes

- 101 = Allocates 32 locations in system memory to each analog input, actually 64 bytes

- 100 = Allocates 16 locations in system memory to each analog input, actually 32 bytes

011 = Allocates 8 locations in system memory to each analog input, actually 16 bytes

010 = Allocates 4 locations in system memory to each analog input, actually 8 bytes

001 = Allocates 2 locations in system memory to each analog input, actually 4 bytes

000 = Allocates 1 location in system memory to each analog input, actually 2 bytes

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                     | U-0                | U-0               | U-0 U-0           |                   | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | _                       | _                  | _                 | _                 | -                 | -                 | —                | —                |  |  |  |  |

| 23:16        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        | —                       | WAKFIL             | _                 | _                 | _                 | SEG               | ,4)              |                  |  |  |  |  |

| 15.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | ę                 | SEG1PH<2:0        | >                 | PRSEG<2:0>        |                  |                  |  |  |  |  |

| 7:0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | SJW<1:                  | 0>(3)              |                   | BRP<5:0>          |                   |                   |                  |                  |  |  |  |  |

## **REGISTER 26-2:** CxCFG: CAN BAUD RATE CONFIGURATION REGISTER ('x' = 1-4)

| Legend:           | HC = Hardware Clear | S = Settable bit                   |                    |  |  |  |

|-------------------|---------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

- bit 22 WAKFIL: CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|-----------|-------------------------------------------------------------------------------|

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | <b>SAM</b> : Sample of the CAN Bus Line bit <sup>(2)</sup>                    |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | $SJW \leq SEG2PH.$                                                            |

| 4:        | The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).          |

|           |                                                                               |

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CxCON<23:21>) = 100).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit Bit<br>29/21/13/5 28/20/12/4 |            | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|----------------------------------|------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0                            | R/W-0      | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|           | FLTEN3            | MSEL:             | 3<1:0>                           | FSEL3<4:0> |                   |                   |                  |                  |  |  |

| 22:46     | R/W-0             | R/W-0             | R/W-0                            | R/W-0      | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | FLTEN2            | MSEL              | 2<1:0>                           | FSEL2<4:0> |                   |                   |                  |                  |  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0                            | R/W-0      | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0      | FLTEN1            | MSEL              | 1<1:0>                           | FSEL1<4:0> |                   |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0                            | R/W-0      | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | FLTEN0            | MSEL              | 0<1:0>                           | FSEL0<4:0> |                   |                   |                  |                  |  |  |

# **REGISTER 26-10:** CxFLTCON0: CAN FILTER CONTROL REGISTER 0 ('x' = 1-4)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit<br>1 = Filter is enabled                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                                   |

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits                                                                                    |

|           | 11 = Reserved                                                                                                            |

|           | 10 = Acceptance Mask 2 is selected                                                                                       |

|           | 01 = Acceptance Mask 1 is selected<br>00 = Acceptance Mask 0 is selected                                                 |

| bit 28-24 | FSEL3<4:0>: FIFO Selection bits                                                                                          |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           |                                                                                                                          |

|           | :                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN2: Filter 2 Enable bit                                                                                              |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 22-21 | MSEL2<1:0>: Filter 2 Mask Select bits                                                                                    |

|           | 11 = Reserved                                                                                                            |

|           | 10 = Acceptance Mask 2 is selected                                                                                       |

|           | 01 = Acceptance Mask 1 is selected<br>00 = Acceptance Mask 0 is selected                                                 |

| bit 20-16 | FSEL2<4:0>: FIFO Selection bits                                                                                          |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | :                                                                                                                        |

|           |                                                                                                                          |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

|           |                                                                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 26-11: CxFLTCON1: CAN FILTER CONTROL REGISTER 1 ('x' = 1-4) (CONTINUED)

| L:1 4 F   |                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 15    | FLTEN5: Filter 17 Enable bit                                                                           |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL5<1:0>: Filter 5 Mask Select bits                                                                  |

|           | 11 = Reserved                                                                                          |

|           | 10 = Acceptance Mask 2 is selected                                                                     |

|           | 01 = Acceptance Mask 1 is selected                                                                     |

|           | 00 = Acceptance Mask 0 is selected                                                                     |

| bit 12-8  | FSEL5<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN4: Filter 4 Enable bit                                                                            |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 6-5   | MSEL4<1:0>: Filter 4 Mask Select bits                                                                  |

|           | 11 = Reserved                                                                                          |

|           | 10 = Acceptance Mask 2 is selected                                                                     |

|           | 01 = Acceptance Mask 1 is selected                                                                     |

|           | 00 = Acceptance Mask 0 is selected                                                                     |

| bit 4-0   | FSEL4<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

|           |                                                                                                        |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

|           |                                                                                                        |

NOTES:

| s                           |                                 |                       |        |        |          |            |            |          |         | Bits       |        |        |           |          |        |        |        |                 |            |

|-----------------------------|---------------------------------|-----------------------|--------|--------|----------|------------|------------|----------|---------|------------|--------|--------|-----------|----------|--------|--------|--------|-----------------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range             | 31/15  | 30/14  | 29/13    | 28/12      | 27/11      | 26/10    | 25/9    | 24/8       | 23/7   | 22/6   | 21/5      | 20/4     | 19/3   | 18/2   | 17/1   | 16/0            | All Resets |

| B650                        | VEL3CNT                         | 31:16                 |        |        |          | •          |            |          | V       | ELCNT<31:1 | 6>     |        |           |          | •      |        |        |                 | 0000       |

| B030                        | VELOCINI                        | 15:0                  |        |        |          |            |            |          |         |            |        |        |           |          | 0000   |        |        |                 |            |

| B660                        | VEL3HLD                         | 31:16                 |        |        |          |            |            |          |         |            |        |        |           |          | 0000   |        |        |                 |            |

| DUUU                        | VELONED                         | 15:0                  |        |        |          |            |            |          |         | /ELHLD<15: |        |        |           |          |        |        |        |                 | 0000       |

| B670                        | INT3TMR                         | 31:16                 |        |        |          |            |            |          |         | NTTMR<31:1 |        |        |           |          |        |        |        |                 | 0000       |

| 20.0                        |                                 | 15:0                  |        |        |          |            |            |          |         | NTTMR<15:  |        |        |           |          |        |        |        |                 | 0000       |

| B680                        | INT3HLD                         | 31:16                 |        |        |          |            |            |          |         | NTHLD<31:1 |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 15:0                  |        |        |          |            |            |          |         | NTHLD<15:0 |        |        |           |          |        |        |        |                 | 0000       |

| B690                        | INDX3CNT                        | 31:16                 |        |        |          |            |            |          |         | DXCNT<31:  |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 15:0                  |        |        |          |            |            |          |         | NDXCNT<15  |        |        |           |          |        |        |        |                 | 0000       |

| B6A0                        | INDX3HLD                        | 31:16                 |        |        |          |            |            |          |         |            |        |        |           |          | 0000   |        |        |                 |            |

|                             |                                 | 15:0                  |        |        |          |            |            |          |         |            |        |        |           |          | 0000   |        |        |                 |            |

| B6B0                        | <b>QEI3ICC</b>                  | 31:16                 |        |        |          |            |            |          |         |            |        |        |           | 0000     |        |        |        |                 |            |

|                             |                                 | 15:0                  |        |        |          |            |            |          |         |            |        |        |           | 0000     |        |        |        |                 |            |

| B6C0                        | QEI3CMPL                        | 31:16                 |        |        |          |            |            |          |         |            |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 15:0                  |        |        |          |            |            |          | Q       | EICMPL<15  |        |        |           |          |        |        | 1      |                 | 0000       |

| B800                        | QEI4CON                         | 31:16                 | -      | —      | -        | —          | —          | —        | —       |            | _      | —      | -         |          | —      | -      | -      | —               | 0000       |

|                             |                                 | 15:0                  | QEIEN  | —      | QEISIDL  |            | PIMOD<2:0> |          | IMV<    | :1:0>      | _      |        | INTDIV<2: |          | CNTPOL | GATEN  |        | <1:0><br>HCAPEN | 0000       |

| B810                        | QEI4IOC                         | 31:16                 |        |        |          |            | —          |          | -       | -          | -      |        |           |          | -      |        |        |                 | _          |

|                             |                                 |                       | QCAPEN | FLIREN |          | QFDIV<2:0> |            | OUTER    | IC<1:0> | SWPAB      | HOMPOL | IDXPOL | QEBPOL    | QEAPOL   | HOME   | INDEX  | QEB    | QEA             | 0000       |

| B820                        | QEI4STAT                        | 31:16<br>15:0         | _      |        |          |            |            |          |         |            |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 31:16                 | —      |        | PUTEQIRQ | PUTEQIEN   | PULEQIRQ   | POLEQIEN |         | OSCNT<31:  |        | PUIEN  | VELOVIRQ  | VELOVIEN | HUMIRQ | HOMIEN | IDXIRQ | IDAIEN          | 0000       |

| B830                        | POS4CNT                         | 15:0                  |        |        |          |            |            |          |         | OSCNT<51.  |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 31:16                 |        |        |          |            |            |          |         | OSHLD<31:1 |        |        |           |          |        |        |        |                 | -          |

| B840                        | POS4HLD                         | 15:0                  |        |        |          |            |            |          |         | OSHLD<01:  |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 31:16                 |        |        |          |            |            |          |         | ELCNT<31:1 |        |        |           |          |        |        |        |                 | 0000       |

| B850                        | VEL4CNT                         | 15:0                  |        |        |          |            |            |          |         | ELCNT<15:  |        |        |           |          |        |        |        |                 | 0000       |

|                             |                                 | 31:16                 |        |        |          |            |            |          |         | ELHLD<31:1 |        |        |           |          |        |        |        |                 | 0000       |

| B860                        | VEL4HLD                         | 15:0                  |        |        |          |            |            |          |         |            |        |        | 0000      |          |        |        |        |                 |            |

|                             |                                 | 31:16                 |        |        |          |            |            |          |         | NTTMR<31:1 |        |        |           |          |        |        |        |                 | 0000       |

| B870                        | INT4TMR                         | 15:0                  |        |        |          |            |            |          |         |            |        |        |           |          |        |        |        |                 | 0000       |

|                             | du                              | 15:0 INTTMR<15:0> 000 |        |        |          |            |            |          |         |            | 0000   |        |           |          |        |        |        |                 |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 13.2 "CLR, SET, and INV Registers" for more information.

# TABLE 31-1: MCPWM REGISTER MAP (CONTINUED)

| ess                              |                  |           |         |         |        |        |          |         |        | Bits    |        |         |        |         |          |        |         |         |              |

|----------------------------------|------------------|-----------|---------|---------|--------|--------|----------|---------|--------|---------|--------|---------|--------|---------|----------|--------|---------|---------|--------------|

| Virtual Address<br>(BF82_#)<br>a | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13  | 28/12  | 27/11    | 26/10   | 25/9   | 24/8    | 23/7   | 22/6    | 21/5   | 20/4    | 19/3     | 18/2   | 17/1    | 16/0    | All Resets   |

|                                  | STRIG5           | 31:16     | _       | _       |        | _      | _        | _       | _      | _       | —      | _       | _      | _       | _        | _      | _       | _       | 000          |

|                                  |                  | 15:0      |         |         |        |        |          |         | ç      | STRGCMP | <15:0> |         |        |         |          |        |         |         | 000          |

| A570                             | CAP5             | 31:16     | —       | —       | _      | _      | _        | —       | —      | _       | —      | —       | _      | —       | —        | —      | —       | —       | 000          |

|                                  |                  | 15:0      |         |         |        | •      |          |         |        | CAP<15  | 5:0>   |         |        |         |          |        | •       |         | 000          |

| A580                             | LEBCON5          | 31:16     | —       | —       | _      | —      | _        | —       | —      | _       | _      | —       | —      | _       | —        | _      | —       | _       | 000          |

|                                  |                  | 15:0      | PHR     | PHF     | PLR    | PLF    | FLTLEBEN | CLLEBEN |        |         | —      | —       | —      |         | —        | _      | —       | _       | 000          |

| A590                             | LEBDLY5          | 31:16     | _       | —       | _      | _      | _        | _       | —      | _       | _      | _       | _      | _       | —        | _      | —       | _       | 000          |

|                                  |                  | 15:0      | _       | _       |        | —      |          |         |        |         |        | LEB     | <11:0> |         |          |        | •       |         | 000          |

| A5A0                             | AUXCON5          | 31:16     | _       | _       |        | —      | —        | —       | —      | _       | _      | —       | —      | _       | —        | _      | —       | _       | 000          |

|                                  |                  | 15:0      | _       | —       | _      | _      | _        | _       | —      | _       | _      | _       |        | CHOPS   | SEL<3:0> |        | CHOPHEN | CHOPLEN | <b>V</b> 000 |

| A5B0                             | PTMR5            | 31:16     | _       | —       |        | —      | _        | —       | _      | -       |        | —       | _      | _       | —        | _      | —       | _       | 000          |

|                                  |                  | 15:0      |         |         |        | •      |          |         |        | TMR<1   | 5:0>   |         |        |         |          |        | •       |         | 000          |

| A5C0 PWMCON6                     | PWMCON6          | 31:16     | FLTIF   | CLIF    | TRGIF  | PWMLIF | PWMHIF   | _       | —      | _       | FLTIEN | CLIEN   | TRGIEN | PWMLIEN | PWMHIEN  | _      | —       | _       | 000          |

|                                  |                  | 15:0      | FLTSTAT | CLTSTAT | -      | —      | ECAN     | 1<1:0>  | ITB    | -       | DTC    | <1:0>   | DTCP   | PTDIR   | MTBS     | _      | XPRES   | _       | 000          |

| A5D0                             | IOCON6           | 31:16     | —       | —       |        | CLSR   | C<3:0>   |         | CLPOL  | CLMOD   | —      |         | FLTS   | RC<3:0> | •        | FLTPOL | FLTMC   | D<1:0>  | 007          |

|                                  |                  | 15:0      | PENH    | PENL    | POLH   | POLL   | PMOD     | )<1:0>  | OVRENH | OVRENL  | OVRDA  | AT<1:0> | FLTDA  | AT<1:0> | CLDAT    | <1:0>  | SWAP    | OSYNC   | 000          |

| A5E0                             | PDC6             | 31:16     |         | —       | _      | —      |          | —       | —      | _       |        | —       | —      | —       | —        |        | —       | _       | 000          |

|                                  |                  | 15:0      |         |         |        |        |          |         |        | PDC<15  | 5:0>   |         |        |         |          |        |         |         | 000          |

| A5F0                             | SDC6             | 31:16     | _       | _       | —      | _      | _        | _       | —      | _       |        | —       | -      | _       | —        | _      | —       | _       | 000          |

|                                  |                  | 15:0      |         |         |        |        |          |         |        | SDC<15  | 5:0>   |         |        |         |          |        |         |         | 000          |

| A600                             | PHASE6           | 31:16     | —       | —       | —      | —      | _        | —       | —      | —       | _      | —       | —      | —       | —        | —      | —       | —       | 000          |

|                                  |                  | 15:0      |         |         |        |        |          |         |        | PHASE<  | 15:0>  |         |        |         |          |        |         |         | 000          |

| A610                             | DTR6             | 31:16     |         | —       | _      | —      | _        | —       | —      | —       | —      | —       | —      | —       | —        | —      | —       | —       | 000          |

|                                  |                  | 15:0      |         |         |        |        |          |         |        | DTR<15  | 5:0>   |         |        |         |          |        |         |         | 000          |

| A620                             | ALTDTR6          | 31:16     | _       | —       | _      | -      | _        | —       | —      | —       | _      | —       | —      | —       | —        | _      | —       | _       | 000          |

|                                  |                  | 15:0      |         |         |        |        |          |         |        | ALTDTR< | 15:0>  |         |        |         |          |        |         |         | 000          |