Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 77                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 42x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512gpd100t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       |                 | Pin Number             |      | Pin Number |                                                                                | Pin Number |  | Pin Number |  | Pin Number |  | Pin Number |  | Pin Number |  | Pin Number |  | Pin Number |  | Buffer | Description |

|-------|-----------------|------------------------|------|------------|--------------------------------------------------------------------------------|------------|--|------------|--|------------|--|------------|--|------------|--|------------|--|------------|--|--------|-------------|

|       | 100-pin<br>TQFP | 64-pin<br>QFN/<br>TQFP | Туре | Туре       |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD0  | 93              | 60                     | I/O  | TTL/ST     | Parallel Master Port Data (Demultiplexed Master mode) or Address/Data          |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD1  | 94              | 61                     | I/O  | TTL/ST     | (Multiplexed Master modes)                                                     |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD2  | 98              | 62                     | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD3  | 99              | 63                     | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD4  | 100             | 64                     | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD5  | 3               | 1                      | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD6  | 4               | 2                      | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD7  | 5               | 3                      | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD8  | 90              | _                      | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD9  | 89              |                        | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD10 | 88              |                        | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD11 | 87              |                        | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD12 | 79              |                        | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD13 | 80              |                        | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD14 | 83              | _                      | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMD15 | 84              | _                      | I/O  | TTL/ST     |                                                                                |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMALH | 43              | 29                     | 0    | TTL/CMOS   | Parallel Master Port Address Latch Enable High Byte (Multiplexed Master modes) |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

| PMALL | 44              | 30                     | 0    | —          | Parallel Master Port Address Latch Enable Low Byte (Multiplexed Master modes)  |            |  |            |  |            |  |            |  |            |  |            |  |            |  |        |             |

TABLE 1-10: PMP PINOUT I/O DESCRIPTIONS (CONTINUED)

**nd:** CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels

TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select I = Input

#### TABLE 1-20: POWER, GROUND, AND VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS

|                     | Pin N                                  | umber                  |             |                |                                                                                                  |  |  |  |  |

|---------------------|----------------------------------------|------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name            | 100-pin<br>TQFP                        | 64-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                      |  |  |  |  |

|                     |                                        |                        |             |                | Power and Ground                                                                                 |  |  |  |  |

| AVDD                | 30                                     | 19                     | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times.                     |  |  |  |  |

| AVss                | 31                                     | 20                     | Р           | Р              | Ground reference for analog modules. This pin must be connected at all times.                    |  |  |  |  |

| Vdd                 | 2, 16, 37,<br>46, 62, 86               | 10, 26,<br>38, 57      | Р           | —              | Positive supply for peripheral logic and I/O pins. This pin must be con-<br>nected at all times. |  |  |  |  |

| Vss                 | 15, 36,<br>45, 65,<br>75, 85           | 9, 25, 41,<br>56       | Р           | —              | Ground reference for logic, I/O pins, and USB. This pin must be connected at all times.          |  |  |  |  |

| VBAT <sup>(1)</sup> | 68                                     | 42                     | Р           | Р              | Battery backup for selected peripherals; otherwise connect to VDD.                               |  |  |  |  |

|                     |                                        |                        |             |                | Voltage Reference                                                                                |  |  |  |  |

| VREF+               | 29                                     | 16                     | I           | Analog         | Analog Voltage Reference (High) Input                                                            |  |  |  |  |

| VREF-               | 28                                     | 15                     | I           | Analog         | Analog Voltage Reference (Low) Input                                                             |  |  |  |  |

| Legend:             | CMOS = CM<br>ST = Schmi<br>TTL = Trans | tt Trigger in          | put with    | CMOS leve      | ls O = Output I = Input                                                                          |  |  |  |  |

Note 1: VBAT functionality is compromised, see errata for additional information. This pin should be connected to VDD.

#### 3.1 Architecture Overview

The MIPS32 microAptiv MCU core in the PIC32MK GP/ MC family devices contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- · Execution unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System control coprocessor (CP0)

- Floating Point Unit (FPU)

- · Power Management

- microMIPS support

- Enhanced JTAG (EJTAG) controller

#### 3.1.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow sets (containing thirty-two registers) are added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Trap condition comparator

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- Shifter and store aligner

- DSP ALU and logic block for performing DSP instructions, such as arithmetic/shift/compare operations

#### 3.1.2 MULTIPLY/DIVIDE UNIT (MDU)

The processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations, and DSP ASE multiply instructions. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 Booth recoded multiplier, a pair of result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the rs operand. The second number '16' of 32x16) represents the *rt* operand.

The MDU supports execution of one multiply or multiply-accumulate operation every clock cycle.

Divide operations are implemented with a simple 1-bitper-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the processor core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> microAptiv<sup>™</sup> MCU CORE HIGH-PERFORMANCE INTEGER MULTIPLY/<br/>DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                         | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |  |  |

|--------------------------------|------------------------------------------------|---------|-------------|--|--|

| MULT/MULTU, MADD/MADDU,        | 16 bits                                        | 5       | 1           |  |  |

| MSUB/MSUBU (HI/LO destination) | 32 bits                                        | 5       | 1           |  |  |

| MUL (GPR destination)          | 16 bits                                        | 5       | 1           |  |  |

|                                | 32 bits                                        | 5       | 1           |  |  |

| DIV/DIVU                       | 8 bits                                         | 12/14   | 12/14       |  |  |

|                                | 16 bits                                        | 20/22   | 20/22       |  |  |

|                                | 24 bits                                        | 28/30   | 28/30       |  |  |

|                                | 32 bits                                        | 36/38   | 36/38       |  |  |

The MIPS architecture defines that the result of a multiply or divide operation be placed in one of four pairs of HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

The MDU also implements various shift instructions operating on the HI/LO register and multiply instructions as defined in the DSP ASE. The MDU supports all of the data types required for this purpose and includes three extra HI/LO registers as defined by the ASE.

Table 3-2 lists the latencies and repeat rates for the DSP multiply and dot-product operations. The approximate latencies and repeat rates are listed in terms of pipeline clocks.

| <b>TABLE 3-2:</b> | DSP-RELATED LATENCIES |

|-------------------|-----------------------|

|                   | AND REPEAT RATES      |

| Op code                                                        | Latency | Repeat<br>Rate |

|----------------------------------------------------------------|---------|----------------|

| Multiply and dot-product without saturation after accumulation | 5       | 1              |

| Multiply and dot-product with saturation after accumulation    | 5       | 1              |

| Multiply without accumulation                                  | 5       | 1              |

#### 3.1.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as the presence of options like microMIPS is also available by accessing the CP0 registers, listed in Table 3-3.

| Register<br>Number | Register<br>Name | Function                                                                                                                                  |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0-6                | Reserved         | Reserved in the PIC32MK GP Family core.                                                                                                   |

| 7                  | HWREna           | Enables access via the RDHWR instruction to selected hardware registers in Non-privileged mode.                                           |

| 8                  | BadVAddr         | Reports the address for the most recent address-related exception.                                                                        |

|                    | BadInstr         | Reports the instruction that caused the most recent exception.                                                                            |

|                    | BadInstrP        | Reports the branch instruction if a delay slot caused the most recent exception.                                                          |

| 9                  | Count            | Processor cycle count.                                                                                                                    |

| 10                 | Reserved         | Reserved in the PIC32MK GP Family core.                                                                                                   |

| 11                 | Compare          | Core timer interrupt control.                                                                                                             |

| 12                 | Status           | Processor status and control.                                                                                                             |

|                    | IntCtl           | Interrupt control of vector spacing.                                                                                                      |

|                    | SRSCtl           | Shadow register set control.                                                                                                              |

|                    | SRSMap           | Shadow register mapping control.                                                                                                          |

|                    | View_IPL         | Allows the Priority Level to be read/written without extracting or inserting that bit from/to the Status register.                        |

|                    | SRSMAP2          | Contains two 4-bit fields that provide the mapping from a vector number to the shadow set number to use when servicing such an interrupt. |

| 13                 | Cause            | Describes the cause of the last exception.                                                                                                |

|                    | NestedExc        | Contains the error and exception level status bit values that existed prior to the current exception.                                     |

|                    | View_RIPL        | Enables read access to the RIPL bit that is available in the Cause register.                                                              |

| 14                 | EPC              | Program counter at last exception.                                                                                                        |

|                    | NestedEPC        | Contains the exception program counter that existed prior to the current exception.                                                       |

#### TABLE 3-3:COPROCESSOR 0 REGISTERS

# FIGURE 4-3: BOOT AND ALIAS MEMORY MAP

| Physical I              | Memory Map <sup>(1)</sup>                                     |                |

|-------------------------|---------------------------------------------------------------|----------------|

| -                       |                                                               | 0x1FC64FFF     |

|                         |                                                               | 0x1FC64000     |

|                         | Seq/Configuration                                             | 0x1FC63FFF     |

| Boot Flash 2            | Word Space                                                    | 0x1FC63FB0     |

|                         |                                                               | 0x1FC63FAC     |

|                         |                                                               | 0x1FC60000     |

|                         |                                                               | 0x1FC5FFFF     |

|                         |                                                               |                |

| R                       | eserved                                                       |                |

|                         |                                                               | 0x1FC45800     |

|                         |                                                               | 0x1FC457FF     |

|                         |                                                               | 0x1FC45040     |

|                         | DATA EE CAL                                                   | 0x1FC4503C     |

|                         | (DEVEE0-DEVEE3)                                               | 0x1FC45030     |

|                         |                                                               | 0x1FC4502F     |

|                         | Device Serial Number <sup>(4)</sup>                           | 0x1FC4502C     |

|                         | DEVSNx, x=0-3                                                 | 0x1FC45020     |

| Public Test Flash       | - ,                                                           | 0x1FC4501C     |

| FUDIIC TEST FIASIT      |                                                               | 0x1FC4501C     |

|                         | DEVADC7<br>DEVADC5                                            | 0x1FC45016     |

|                         |                                                               |                |

|                         | DEVADC4                                                       | 0x1FC45010     |

|                         | DEVADC3                                                       | 0x1FC4500C     |

|                         | DEVADC2                                                       | 0x1FC45008     |

|                         | DEVADC1                                                       | 0x1FC45004     |

|                         | DEVADC0                                                       | 0x1FC45000     |

|                         |                                                               | 0x1FC44FFF     |

|                         |                                                               | 0x1FC44000     |

| Boot Flash 1            | Seq/Configuration                                             | 0x1FC43FFF     |

| Bootridon               | Word Space                                                    | 0x1FC43FB0     |

|                         |                                                               | 0x1FC43FAC     |

|                         |                                                               | 0x1FC40000     |

| D                       | eserved                                                       | 0x1FC3FFFF     |

|                         | eserveu                                                       | 0x1FC25000     |

|                         |                                                               | 0x1FC24FFF     |

| Uppe                    | r Boot Alias                                                  |                |

| oppo                    |                                                               |                |

|                         |                                                               | 0x1FC20000     |

| R                       | eserved                                                       | 0x1FC1FFFF     |

|                         |                                                               | 0x1FC05000     |

|                         |                                                               | 0x1FC04FFF     |

|                         |                                                               | 0x1FC04000     |

| Lower Post Alice        | Seq/Configuration                                             | 0x1FC03FFF     |

| Lower Boot Alias        | Word Space                                                    | 0x1FC03FB0     |

|                         |                                                               | 0x1FC03FAC     |

|                         |                                                               | 0x1FC00000     |

| Note 1: Memo            | ory areas are not shown to                                    | scale.         |

|                         | ory locations 0x1FC03FB0                                      |                |

|                         | C03FFC are used to initialize<br>guration registers (see 33.0 |                |

|                         | lires").                                                      | opeciai        |

| <ol><li>Refer</li></ol> | to 4.1.1 "Boot Flash Seq                                      |                |

| Confi                   | guration Spaces" for mor<br>bry locations 0x1FC5020 ar        | e information. |

|                         | in a unique device serial ni                                  |                |

| 33.0 "                  | Special Features").                                           |                |

|                         | configuration space cannot<br>ting code in the upper Boo      |                |

| EXECU                   | ang oode in the upper DOC                                     |                |

|                         |                                                               |                |

#### TABLE 4-1: SFR MEMORY MAP

|               | Virtual Address |                 |  |  |  |  |

|---------------|-----------------|-----------------|--|--|--|--|

| Peripheral    | Base            | Offset<br>Start |  |  |  |  |

| CFG-PMD       |                 | 0x0000          |  |  |  |  |

| CACHE         |                 | 0x0800          |  |  |  |  |

| FC-NVM        |                 | 0x0A00          |  |  |  |  |

| WDT           |                 | 0x0C00          |  |  |  |  |

| DMT           | 0xBF800000      | 0x0E00          |  |  |  |  |

| ICD           |                 | 0x1000          |  |  |  |  |

| CRU           |                 | 0x1200          |  |  |  |  |

| PPS           |                 | 0x1400          |  |  |  |  |

| PLVD          |                 | 0x1800          |  |  |  |  |

| EVIC          | 0.000           | 0x0000          |  |  |  |  |

| DMA           | 0xBF810000      | 0x1000          |  |  |  |  |

| Timer1-Timer9 |                 | 0x0000          |  |  |  |  |

| IC1-IC9       |                 | 0x2000          |  |  |  |  |

| OC1-OC9       |                 | 0x4000          |  |  |  |  |

| I2C1-I2C2     |                 | 0x6000          |  |  |  |  |

| SPI1-SPI2     |                 | 0x7000          |  |  |  |  |

| UART1-UART2   |                 | 0x8000          |  |  |  |  |

| DATAEE        | 0xBF820000      | 0x9000          |  |  |  |  |

| PWM1-PWM12    |                 | 0xA000          |  |  |  |  |

| QEI1-QEI6     |                 | 0xB200          |  |  |  |  |

| CMP           |                 | 0xC000          |  |  |  |  |

| CDAC1         |                 | 0xC200          |  |  |  |  |

| CTMU          |                 | 0xD000          |  |  |  |  |

| PMP           |                 | 0xE000          |  |  |  |  |

| IC10-IC16     |                 | 0x3200          |  |  |  |  |

| OC10-OC16     |                 | 0x5200          |  |  |  |  |

| I2C3-I2C4     | 0xBF840000      | 0x6400          |  |  |  |  |

| SPI3-SPI6     | 0107040000      | 0x7400          |  |  |  |  |

| UART3-UART6   | ]               | 0x8400          |  |  |  |  |

| CDAC2-CDAC3   |                 | 0xC400          |  |  |  |  |

| PORTA-PORTG   | 0xBF860000      | 0x0000          |  |  |  |  |

| CAN1-CAN4     |                 | 0x0000          |  |  |  |  |

| ADC           | 0xBF880000      | 0x7000          |  |  |  |  |

| USB1-USB2     |                 | 0x9000          |  |  |  |  |

| RTCC          |                 | 0x0000          |  |  |  |  |

| Deep Sleep    | 0xBF8C0000      | 0x0200          |  |  |  |  |

| SSX CTL       | 0xBF8F0000      | 0x0000          |  |  |  |  |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

#### TABLE 4-9: SYSTEM BUS TARGET 1 REGISTER MAP

|                             | LE 4-9.          | 0.0           |       | 000   | IARGEI | TREO          |          |       |       |         | <b>D</b> '4   |       |          |          |        |        |          |          | т —           |

|-----------------------------|------------------|---------------|-------|-------|--------|---------------|----------|-------|-------|---------|---------------|-------|----------|----------|--------|--------|----------|----------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13  | 28/12         | 27/11    | 26/10 | 25/9  | 24/8    | Bits<br>23/7  | 22/6  | 21/5     | 20/4     | 19/3   | 18/2   | 17/1     | 16/0     | All<br>Resets |

| 8420                        | SBT1ELOG1        | 31:16         | MULTI | —     | —      |               |          | CODE  | <3:0> |         | _             | —     | —        |          | —      | —      | —        |          | 0000          |

| 0420                        | SBITEEOOT        | 15:0          |       |       |        | INI           | TID<7:0> |       |       |         |               | REGIO | N<3:0>   |          | —      | C      | CMD<2:0> |          | 0000          |

| 8424                        | SBT1ELOG2        | 31:16         | —     | —     | —      | —             | —        | —     | _     | —       | _             | _     | _        | _        | —      | —      | —        | —        | 0000          |

| 0424                        | OBTILLOOZ        | 15:0          | _     | —     | —      | —             | —        | —     | —     | —       | _             | —     | —        | —        | —      | —      | GROU     | P<1:0>   | 0000          |

| 8428                        | SBT1ECON         | 31:16         | —     | —     | —      | —             | —        |       |       | ERRP    |               |       | —        |          | —      | —      | —        | —        | 0000          |

| 0420                        | OBTILOON         | 15:0          | _     | —     | —      | —             | —        | —     | —     | —       | _             | —     | —        | —        | —      | —      | —        | —        | 0000          |

| 8430                        | SBT1ECLRS        | 31:16         | —     | —     | —      | —             | —        |       |       | —       |               |       | —        |          | —      | —      | —        | —        | 0000          |

| 0100                        | OBTIEGENO        | 15:0          |       | —     | —      | —             | —        | —     | —     | —       | _             | —     | —        | —        | —      | —      | —        | CLEAR    | 0000          |

| 8438                        | SBT1ECLRM        | 31:16         |       | —     | —      | —             | —        | —     | —     | —       | _             | —     | —        | —        | —      | —      | —        | —        | 0000          |

| 0.00                        | 021120214        | 15:0          |       | —     | —      | —             | —        | —     | —     | —       | —             | —     | —        | —        | —      | —      | —        | CLEAR    | 0000          |

| 8440                        | SBT1REG0         | 31:16         |       |       |        |               |          |       | 1     | BAS     | SE<21:6>      |       |          |          |        |        |          |          | xxxx          |

|                             |                  | 15:0          |       |       | BA     | \SE<5:0>      |          |       | PRI   | —       |               |       | SIZE<4:0 | >        | 1      | —      | —        | —        | XXXX          |

| 8450                        | SBT1RD0          | 31:16         | _     | —     | —      | —             | —        |       | —     | _       |               | —     | —        | —        |        | —      | —        | —        | XXXX          |

|                             |                  | 15:0          |       | —     |        | —             | —        | —     | —     | —       |               | —     | —        | —        | GROUP3 | GROUP2 | GROUP1   | GROUP0   | xxxx          |

| 8458                        | SBT1WR0          | 31:16         |       | —     |        | —             | —        | —     | —     | —       |               | —     | —        | —        | —      | —      | —        | —        | XXXX          |

|                             |                  | 15:0          |       | —     | —      | _             | —        | —     | —     | -       | —             | —     | _        | _        | GROUP3 | GROUP2 | GROUP1   | GROUP0   | +             |

| 8480                        | SBT1REG2         | 31:16         |       |       |        |               |          |       |       |         | SE<21:6>      |       |          |          |        |        |          |          | XXXX          |

|                             |                  | 15:0          |       |       | BA     | \SE<5:0>      |          |       | PRI   | —       | SIZE<4:0>     |       |          |          |        | -      | —        | -        | XXXX          |

| 8490                        | SBT1RD2          | 31:16         |       |       |        | _             | _        | _     | _     | _       | _             | _     | _        | _        | -      | -      | -        | -        | XXXX          |

|                             |                  | 15:0          |       |       |        | _             | _        | _     | _     | _       | _             | _     | _        | _        | GROUP3 | GROUP2 | GROUP1   | GROUP0   |               |

| 8498                        | SBT1WR2          | 31:16         |       |       |        | _             | _        | _     | _     | _       | _             | _     | _        | _        | -      | -      | -        | -        | XXXX          |

|                             |                  | 15:0          |       | —     | _      |               |          | _     | _     | —       | -             |       |          |          | GROUP3 | GROUP2 | GROUP1   | GROUP0   |               |

| 84A0                        | SBT1REG3         | 31:16         |       |       | DA     |               |          |       |       |         | SE<21:6>      |       |          |          |        |        | r        |          | XXXX          |

|                             |                  | 15:0          |       | _     | BA     | ASE<5:0>      | _        | _     | PRI   |         | _             |       | SIZE<4:0 | >        |        | _      |          |          | XXXX          |

| 84B0                        | SBT1RD3          | 31:16<br>15:0 |       |       |        |               |          |       |       |         |               |       |          |          | GROUP3 | GROUP2 | GROUP1   | GROUP0   | XXXX          |

|                             |                  | 31:16         |       |       |        |               | —        | _     |       |         | _             |       |          |          | GROUPS | GROUPZ | GROUPT   | GROUPU   |               |

| 84B8                        | SBT1WR3          | 15:0          |       |       | _      |               |          | _     |       |         |               | _     |          | _        | GROUP3 | GROUP2 |          | GROUP0   | XXXX          |

|                             |                  | 31:16         |       | —     |        |               |          | —     |       | —<br>BA | —<br>SE<21:6> | —     | _        | _        | GROUPS | GROUPZ | GROUPI   | GROUPU   | -             |

| 84C0                        | SBT1REG4         | 15:0          |       |       | D /    | ASE<5:0>      |          |       | PRI   | ВА      | 52~21.02      |       | SIZE<4:0 | <b>`</b> |        |        |          |          | XXXX          |

| <u> </u>                    |                  | 31:16         | _     | _     | BA     | ASE<5.0>      | _        | _     |       |         |               |       | 5IZE<4.0 |          | _      |        |          |          | xxxx<br>xxxx  |

| 84D0                        | SBT1RD4          | 15:0          |       | _     |        |               |          |       |       | _       |               |       | _        |          | GROUP3 | GROUP2 | GROUP1   | GROUP0   |               |

|                             |                  | 31:16         |       | _     | _      |               | _        |       |       |         |               |       |          |          | GROUPS | GROUPZ |          |          |               |

| 84D8                        | SBT1WR4          | 15:0          |       | _     |        |               |          |       |       |         |               | _     |          |          | GROUP3 | GROUP2 |          | GROUP0   | XXXX          |

| Leaen                       |                  | ļ             |       |       |        | ented, read a |          |       |       |         |               | _     | _        | _        |        | 010012 | 51.0011  | 51.00110 | ~~~~          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

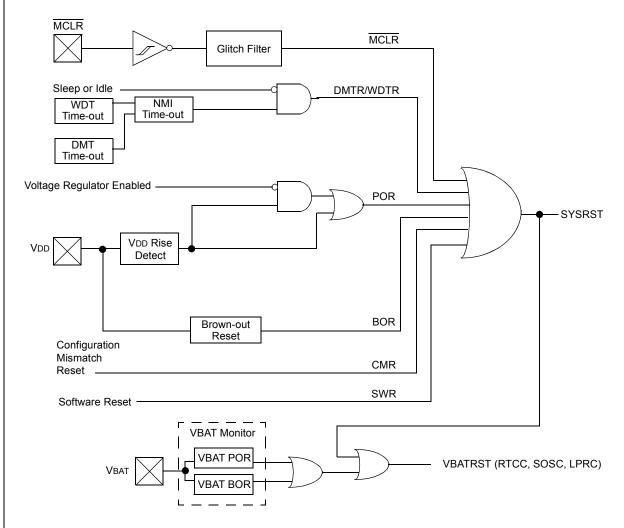

#### 7.0 RESETS

FIGURE 7-1:

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Resets" (DS60001118), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

SYSTEM RESET BLOCK DIAGRAM

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The device Reset sources are as follows:

- · Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

- Deadman Timer Reset (DMTR)

A simplified block diagram of the Reset module is illustrated in Figure 7-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0                |  |

| 31:24        | —                 | —                 | -                 | —                 | _                 | F                 | RCDIV<2:0>       |                      |  |

| 00.40        | R/W-0             | U-0               | R/W-y             | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 23:16        | DRMEN             | —                 | SLP2SPD           | _                 | _                 | _                 | —                | —                    |  |

| 45.0         | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y                |  |

| 15:8         | —                 |                   | COSC<2:0>         |                   | _                 |                   | NOSC<2:0>        |                      |  |

| 7.0          | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0, HS         | R/W-0             | R/W-y            | R/W-y                |  |

| 7:0          | CLKLOCK           |                   | _                 | SLPEN             | CF                | UFRCEN            | SOSCEN           | OSWEN <sup>(1)</sup> |  |

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Config | HS = Hardware Set                  |                    |  |  |

|-------------------|---------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-27 Unimplemented: Read as '0'

bit 26-24 **FRCDIV<2:0>:** Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2

- 000 = FRC divided by 1 (default setting)

#### bit 23 DRMEN: Dream Mode Enable bit

- 1 = Dream mode is enabled

- 0 = Dream mode is disabled

- bit 22 Unimplemented: Read as '0'

- bit 21 SLP2SPD: Sleep Two-speed Start-up Control bit 1 = Use FRC as SYSCLK until the selected clock is ready 0 = Use the selected clock directly

- 0 4 C Unimplemented Deed es (o)

- bit 20-15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Reserved

- 110 = Reserved

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (SOSC)

- 011 = USB PLL (UPLL) input clock and divider are set by UPLLCON

- 010 = Primary Oscillator (Posc) (HS or EC)

- 001 = System PLL (SPLL) input clock and divider set by SPLLCON

- 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV) supports FRN divided by N, where 'N' is 1, 2, 4, 8, 16, 32, 64, and 256

- bit 11 Unimplemented: Read as '0'

- **Note 1:** The reset value for this bit depends on the setting of the IESO bit (DEVCFG1<7>). When IESO = 1, the reset value is '1'. When IESO = 0, the reset value is '0'.

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

#### TABLE 13-15: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| ss                          |                  |           |       |       |       |       |       |       |      | B    | Bits |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 1480                        | U4CTSR           | 31:16     | _     | —     | —     | _     | _     | _     | —    | _    | —    | —    | _    | —    | _    | _     | -      | —    | 0000       |

| 1460                        | 04015R           | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | U4CTS | R<3:0> |      | 0000       |

| 1484                        | U5RXR            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | —    | —    | -    | _    | -    |       |        | —    | 0000       |

| 1404                        | USKAR            | 15:0      |       | —     | —     | _     | _     | _     | _    | _    | —    | —    | _    | _    |      | U5RXI | R<3:0> | •    | 0000       |

| 1488                        | U5CTSR           | 31:16     | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    | —    | _     | —      | —    | 0000       |

| 1400                        | USCISK           | 15:0      | _     | —     | —     | —     | _     | —     | —    | _    | —    | —    | _    | -    |      | U5CTS | R<3:0> |      | 0000       |

| 148C                        | U6RXR            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | —    | —    | -    | _    | -    |       |        | —    | 0000       |

| 1400                        | UORAR            | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | U6RXI | R<3:0> | •    | 0000       |

| 1490                        | U6CTSR           | 31:16     | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| 1490                        | UCISK            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | U6CTS | R<3:0> |      | 0000       |

| 1498                        | SDI1R            | 31:16     | _     | —     | —     | _     | —     | _     | —    | —    | —    | —    | —    | —    | —    | _     | _      | —    | 0000       |

| 1490                        | SDIIK            | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI1F | R<3:0> |      | 0000       |

| 149C                        | SS1R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    | _    | —     | —      | —    | 0000       |

| 1490                        | 55 IK            | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | SS1R  | <3:0>  | •    | 0000       |

| 1444                        | SDI2R            | 31:16     | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| 14A4                        | SDIZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | SDI2F | <3:0>  |      | 0000       |

| 14A8                        | SS2R             | 31:16     | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    | —    | _     | —      | —    | 0000       |

| 14A0                        | 332R             | 15:0      | _     | —     | —     | _     | —     | _     | —    | —    | —    | —    | —    | —    |      | SS2R  | <3:0>  |      | 0000       |

| 14AC                        | SCK3R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    | _    | —     | —      | —    | 0000       |

| 14AC                        | SCRJR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | SCK3  | R<3:0> |      | 0000       |

| 14B0                        | SDI3R            | 31:16     | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| 1460                        | SDISK            | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | _    | —    |      | SDI3F | <3:0>  |      | 0000       |

| 14B4                        | SS3R             | 31:16     | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    | —    | _     | —      | —    | 0000       |

| 1404                        | 333K             | 15:0      | _     | —     | —     | _     | —     | _     | _    | _    | —    | —    | —    | _    |      | SS3R  | <3:0>  |      | 0000       |

| 14B8                        | SCK4R            | 31:16     | —     | —     | —     | —     | _     | —     | —    | _    | —    | —    | _    | —    | _    | —     | —      | —    | 0000       |

| 1400                        | 30N4K            | 15:0      |       | —     | —     | —     |       | —     | —    |      | —    | —    |      | —    |      | SCK4  | R<3:0> |      | 0000       |

| 14BC                        | SDI4R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | _      | —    | 0000       |

| 14BC                        | SUI4K            | 15:0      |       | —     | —     | —     |       | —     | —    |      | —    | —    |      | —    |      | SDI4F | <3:0>  |      | 0000       |

| 1400                        | SS4R             | 31:16     | -     | —     | —     | —     | -     | —     |      |      | —    | —    | -    | —    | _    | —     | —      | —    | 0000       |

| 14C0                        | 554K             | 15:0      | -     | —     | —     | —     | -     | —     |      |      | —    | —    | -    | —    |      | SS4R  | <3:0>  |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

3: This register is only available on PIC32MKXXXGPEXXX devices.

# DS60001402E-page 266

## 16.1 Deadman Timer Control Registers

#### TABLE 16-1: DEADMAN TIMER REGISTER MAP

| ess                         |                  |           |            |                                                                              |                |       |       |       |      |      | Bits       |          |          |      |        |      |      |        |            |

|-----------------------------|------------------|-----------|------------|------------------------------------------------------------------------------|----------------|-------|-------|-------|------|------|------------|----------|----------|------|--------|------|------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15      | 30/14                                                                        | 29/13          | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7       | 22/6     | 21/5     | 20/4 | 19/3   | 18/2 | 17/1 | 16/0   | All Resets |

| 0E00                        | DMTCON           | 31:16     | _          |                                                                              |                |       |       |       |      |      |            |          |          |      |        |      |      |        |            |

| UEUU                        | DIMITCON         | 15:0      | ON         |                                                                              |                |       |       |       |      |      |            |          |          |      |        | 0000 |      |        |            |

| 0E10                        | DMTPRECLR        | 31:16     | _          |                                                                              |                |       |       |       |      |      |            |          |          |      |        | 0000 |      |        |            |

| UEIU                        | DMTPRECLR        | 15:0      |            |                                                                              | STEP1<7:0> 000 |       |       |       |      |      |            |          |          |      |        |      | 0000 |        |            |

| 0E20                        | DMCLR            | 31:16     | —          |                                                                              |                |       |       |       |      |      |            |          |          |      |        | 0000 |      |        |            |

| UEZU                        | DIVICER          | 15:0      | —          | —                                                                            | _              |       |       |       |      | -    |            |          |          | STEP | 2<7:0> |      |      |        | 0000       |

| 0E30                        | DMTSTAT          | 31:16     | —          | —                                                                            | _              |       |       |       |      | -    | —          |          | —        | —    | _      |      |      | _      | 0000       |

| 0230                        | DIVITSTAT        | 15:0      | _          | —                                                                            | —              | —     | _     | _     | _    | _    | BAD1       | BAD2     | DMTEVENT | _    | —      | _    | _    | WINOPN | 0000       |

| 0E40                        | DMTCNT           | 31:16     |            |                                                                              |                |       |       |       |      | COLL | NTER<31:0  | 15       |          |      |        |      |      |        | 0000       |

| 0240                        | DIVITCINT        | 15:0      |            |                                                                              |                |       |       |       |      | 000  |            | <u> </u> |          |      |        |      |      |        | 0000       |

| 0E60                        | DMTPSCNT         | 31:16     |            |                                                                              |                |       |       |       |      | DS   | CNT<31:0>  |          |          |      |        |      |      |        | 0000       |

|                             | DIVITESCINT      | 15:0      |            |                                                                              |                |       |       |       |      | FO   | 5111-51.02 |          |          |      |        |      |      |        | 0000       |

| 0E70                        | DMTPSINTV        | 31:16     |            |                                                                              |                |       |       |       |      | PSI  | NT\/<31.05 |          |          |      |        |      |      |        | 0000       |

| 0270                        | Diviti Silvi V   | 15:0      |            | PSIN I V<31'U>                                                               |                |       |       |       |      |      |            |          |          |      |        |      | 0000 |        |            |

| Legen                       | d: x = unkn      | own va    | lue on Res | eset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                |       |       |       |      |      |            |          |          |      |        |      |      |        |            |

PIC32MK GP/MC Family

The timer source for each Output Compare module depends on the setting of the OCACLK bit in the CFGCON register, the OC32 bit in the OCxCON register, and the OCTSEL bit in the OCxCON register. The available configurations are shown in Table 19-1.

| OCx       | OCACLK<br>CFGCON<16> | OC32<br>(OCxCON<5> | OCTSEL<br>OCxCON<3> | Timerx     | Timery     | Output Compare<br>Timer Source |

|-----------|----------------------|--------------------|---------------------|------------|------------|--------------------------------|

| OC1-OC3   |                      |                    | 0                   | TMR2<15:0> | —          | TMR2<15:0>                     |

|           | 0                    | 0                  | 1                   | _          | TMR3<15:0> | TMR3<15:0>                     |

|           |                      | -                  | 0                   | TMR2<31:0> | —          | TMR2<31:0>                     |

|           | 0                    | 1                  | 1                   | _          | TMR2<31:0> | TMR2<31:0>                     |

|           |                      | _                  | 0                   | TMR4<15:0> | —          | TMR4<15:0>                     |

|           | 1                    | 0                  | 1                   | _          | TMR5<15:0> | TMR5<15:0>                     |

|           |                      | _                  | 0                   | TMR4<31:0> | —          | TMR4<31:0>                     |

|           | 1                    | 1                  | 1                   | _          | TMR4<31:0> | TMR4<31:0>                     |

| OC4-OC6,  | _                    | _                  | 0                   | TMR2<15:0> | —          | TMR2<15:0>                     |

| OC13-OC16 | 0                    | 0                  | 1                   | _          | TMR3<15:0> | TMR3<15:0>                     |

|           |                      |                    | 0                   | TMR2<31:0> | —          | TMR2<31:0>                     |

|           | 0                    | 1                  | 1                   | _          | TMR2<31:0> | TMR2<31:0>                     |

|           |                      |                    | 0                   | TMR2<15:0> | —          | TMR2<15:0>                     |

|           | 1                    | 0                  | 1                   | _          | TMR3<15:0> | TMR3<15:0>                     |

|           |                      | _                  | 0                   | TMR2<31:0> | —          | TMR2<31:0>                     |

|           | 1                    | 1                  | 1                   | _          | TMR2<31:0> | TMR2<31:0>                     |

| OC7-OC9   |                      |                    | 0                   | TMR2<15:0> | —          | TMR2<15:0>                     |

|           | 0                    | 0                  | 1                   | _          | TMR3<15:0> | TMR3<15:0>                     |

|           |                      | -                  | 0                   | TMR2<31:0> | —          | TMR2<31:0>                     |

|           | 0                    | 1                  | 1                   | _          | TMR2<31:0> | TMR2<31:0>                     |

|           | 1                    |                    | 0                   | TMR6<15:0> | —          | TMR6<15:0>                     |

|           | 1                    | 0                  | 1                   | _          | TMR7<15:0> | TMR7<15:0>                     |

|           |                      | -                  | 0                   | TMR6<31:0> | —          | TMR6<31:0>                     |

|           | 1                    | 1                  | 1                   | _          | TMR6<31:0> | TMR6<31:0>                     |

| OC10-OC12 |                      |                    | 0                   | TMR2<15:0> | —          | TMR2<15:0>                     |

|           | 0                    | 0                  | 1                   | _          | TMR3<15:0> | TMR3<15:0>                     |

|           |                      | -                  | 0                   | TMR2<31:0> | —          | TMR2<31:0>                     |

|           | 0                    | 1                  | 1                   | —          | TMR2<31:0> | TMR2<31:0>                     |

|           |                      | <u>_</u>           | 0                   | TMR8<15:0> | —          | TMR8<15:0>                     |

|           | 1                    | 0                  | 1                   | _          | TMR9<15:0> | TMR9<15:0>                     |

|           | 1                    | 1                  | 0                   | TMR8<31:0> | —          | TMR8<31:0>                     |

|           | 1                    | 1                  | 1                   | _          | TMR8<31:0> | TMR8<31:0>                     |

#### TABLE 19-1: TIMER SOURCE CONFIGURATIONS

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                                                                                                                          | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|

| 04-04     | R/W-0                                                                                                                                                                     | R/W-0            |  |  |  |  |  |  |  |

| 31:24     |                   |                   |                   | DATA<3            | 1:24>             |                   |                                                                                                                                                                           |                  |  |  |  |  |  |  |  |

| 00:40     | R/W-0                                                                                                                                                                     | R/W-0            |  |  |  |  |  |  |  |

| 23:16     |                   |                   |                   | DATA<2            | 3:16>             |                   | 8/10/2         25/17/9/1         24/16/8           /W-0         R/W-0         R/W-0           /W-0         R/W-0         R/W-0           /W-0         R/W-0         R/W-0 |                  |  |  |  |  |  |  |  |

| 45.0      | R/W-0                                                                                                                                                                     | R/W-0            |  |  |  |  |  |  |  |

| 15:8      |                   | DATA<15:8>        |                   |                   |                   |                   |                                                                                                                                                                           |                  |  |  |  |  |  |  |  |

| 7.0       | R/W-0                                                                                                                                                                     | R/W-0            |  |  |  |  |  |  |  |

| 7:0       | DATA<7:0>         |                   |                   |                   |                   |                   |                                                                                                                                                                           |                  |  |  |  |  |  |  |  |

#### **REGISTER 20-4:** SPIxBUF: SPIx BUFFER REGISTER ('x' = 1-6)

#### Legend:

| Legenu.           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-0 DATA<31:0> FIFO Data bits

When MODE32 or MODE16 selects 32-bit data, the SPI uses DATA<31:0>. When MODE32 or MODE16 selects 24-bit data, the SPI only uses DATA<24:0>. When MODE32 or MODE16 selects 16-bit data, the SPI only uses DATA<15:0>. When MODE32 or MODE16 selects 8-bit data, the SPI only uses DATA<7:0>.

#### **REGISTER 20-5:** SPIxBRG: SPIx BAUD RATE GENERATOR REGISTER ('x' = 1-6)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 | —                 | -                 | —                 | -                 | -                | —                |

| 00.10     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 45.0      | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | —                 | —                 | —                 |                   |                   | BRG<12:8>         |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | BRG<              | 7:0>              |                   |                  |                  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-13 Unimplemented: Read as '0'

bit 12-0 **BRG<12:0>** Baud Rate Generator Divisor bits Baud Rate = FPBCLKx / (2 \* (SPIxBRG + 1)), where x = 2 and 3, (FPBCLK2 for SPI1-SPI2, FPBCLK3 for SPI3-SPI6.) Therefore, the maximum baud rate possible is FPBCLKx / 2 (SPIXBRG = 0) and the minimum baud rate possible is FPBCLKx / 16384.

**Note:** Changing the BRG value when the ON bit is equal to '1' causes undefined behavior.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R-0, HS, HC       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | TRBEN             | TRBERR            | ٦                 | RBMST<2:0>        | > TRBSLV<2:0>     |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-1             | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | FRACT             | SELRES            | S<1:0>            | STRGSRC<4:0>      |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |  |  |

| 15.0         | ON                |                   | SIDL              | AICPMPEN          | CVDEN             | FSSCLKEN          | FSPBCLKEN        | -                |  |  |  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | —                 |                   | RQVS<2:0>         |                   | STRGLVL           |                   |                  |                  |  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 25-1: ADCCON1: ADC CONTROL REGISTER 1

| Legend:           | HC = Hardware Set | HS = Hardware Cleared                   |

|-------------------|-------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |

- bit 31 TRBEN: Turbo Channel Enable bit

- 1 = Enable the Turbo channel

- 0 = Disable the Turbo channel

- bit 30 **TRBERR:** Turbo Channel Error Status bit

- 1 = An error occurred while setting the Turbo channel and Turbo channel function to be disabled regardless of the TRBEN bit being set to '1'.

- 0 = Turbo channel error did not occur

- Note: The status of this bit is valid only after the TRBEN bit is set.

#### bit 29-27 TRBMST<2:0>: Turbo Master ADCx bits

- 111 = Reserved

- 110 = Reserved

- 101 **= ADC5**

- 100 **= ADC4**

- 011 = ADC3

- 010 = ADC2

- 001 = ADC1

- 000 = ADC0

#### bit 26-24 TRBSLV<2:0>: Turbo Slave ADCx bits

- 111 = Reserved

- 110 = Reserved

- 101 = ADC5

- 100 = ADC4

- 011 = ADC3

- 010 = ADC2

- 001 = ADC1

- 000 **= ADC0**

- bit 23 FRACT: Fractional Data Output Format bit

- 1 = Fractional

- 0 = Integer

#### bit 22-21 SELRES<1:0>: Shared ADC7 (i.e., AN6-AN53) Resolution bits

- 11 = 12 bits (default)

- 10 = 10 bits

- 01 = 8 bits

- 00 = 6 bits

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6    | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|----------------------|----------------------|----------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0                  | U-0                  | U-0                  | U-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     | _                    | —                    | _                    | _                    | CSS27             | CSS26             | CSS25            | CSS24            |

| 00.40     | R/W-0                | R/W-0 R/W-0          |                      | R/W-0                | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | CSS23 <sup>(1)</sup> | CSS22 <sup>(1)</sup> | CSS21 <sup>(1)</sup> | CSS20 <sup>(1)</sup> | CSS19             | CSS18             | CSS17            | CSS16            |

| 15.0      | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | CSS15                | CSS14                | CSS13                | CSS12                | CSS11             | CSS10             | CSS9             | CSS8             |

| 7:0       | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | CSS7                 | CSS6                 | CSS5                 | CSS4                 | CSS3              | CSS2              | CSS1             | CSS0             |

#### REGISTER 25-11: ADCCSS1: ADC COMMON SCAN SELECT REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-28 Unimplemented: Read as '0'

bit 27-0 CSS27:CSS0: Analog Common Scan Select bits

Analog inputs AN27-AN6 are always Class 3 shared ADC7.