Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 77                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 42x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512gpd100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 100-PIN MOTOR CONTROL (MCF) DEVICES

**100-PIN TQFP (TOP VIEW)**

#### PIC32MK0512MCF100 PIC32MK1024MCF100

100

|       |                                                              |            | 1                                                                  |

|-------|--------------------------------------------------------------|------------|--------------------------------------------------------------------|

| Pin # | Full Pin Name                                                | Pin #      | Full Pin Name                                                      |

| 1     | AN23/CVD23/PMPA23/RG15                                       | 36         | Vss                                                                |

| 2     | VDD                                                          | 37         | Vdd                                                                |

| 3     | TCK/RPA7/PWM10H/PWM4L/PMPD5/RA7                              | 38         | AN35/CVD35/RG11                                                    |

| 4     | RPB14/PWM1H/VBUSON1/PMPD6/RB14                               | 39         | AN36/CVD36/RF13                                                    |

| 5     | RPB15/PWM7H/PWM1L/PMPD7/RB15                                 | 40         | AN37/CVD37/RF12                                                    |

| 6     | PWM11H/PWM5L/RD1                                             | 41         | AN12/CVD12/C2IN2-/C5IN2-/FLT5/PMPA11/RE12 <sup>(6)</sup>           |

| 7     | PWM5H/RD2                                                    | 42         | AN13/CVD13/C3IN2-/FLT6/PMPA10/RE13 <sup>(5)</sup>                  |

| 8     | RPD3/PWM12H/PWM6L/RD3                                        | 43         | AN14/CVD14/RPE14/FLT7/PMPA1/PSPA1/RE14                             |

| 9     | RPD4/PWM6H/RD4                                               | 44         | AN15/CVD15/RPE15/FLT8/PMPA0/PSPA0/RE15                             |

| 10    | AN19/CVD19/RPG6/VBUSON2/PMPA5/RG6                            | 45         | Vss                                                                |

| 11    | AN18/CVD18/RPG7/PMPA4/RG7 <sup>(5)</sup>                     | 46         | Vdd                                                                |

| 12    | AN17/CVD17/RPG8/PMPA3/RG8 <sup>(6)</sup>                     | 47         | AN38/CVD38/RD14                                                    |

| 13    | MCLR                                                         | 48         | AN39/CVD39/RD15                                                    |

| 14    | AN16/CVD16/RPG9/PMPA2/RG9                                    | 49         | TDI/DAC3/AN26/CVD26/RPA8/PMPA9/RA8 <sup>(6)</sup>                  |

| 15    | Vss                                                          | 50         | FLT15/RPB4/PMPA8/RB4 <sup>(5)</sup>                                |

| 16    | VDD                                                          | 51         | OA5IN+/DAC1/AN24/CVD24/C5IN1+/C5IN3-/RPA4/T1CK/T1G/RA4             |

| 17    | AN22/CVD22/RG10                                              | 52         | AN40/CVD40/RPE0/RE0                                                |

| 18    | AN21/CVD21/RE8                                               | 53         | AN41/CVD41/RPE1/RE1                                                |

| 19    | AN20/CVD20/RE9                                               | 54         | VBUS                                                               |

| 20    | AN10/CVD10/RPA12/USBOEN2/RA12                                | 55         | VUSB3V3                                                            |

| 21    | AN9/CVD9/RPA11/USBOEN1/RA11                                  | 56         | D1-                                                                |

| 22    | OA2OUT/AN0/C2IN4-/C4IN3-/RPA0/RA0                            | 57         | D1+                                                                |

| 23    | OA2IN+/AN1/C2IN1+/RPA1/RA1                                   | 58         | VBUS2                                                              |

| 24    | PGED3/OA2IN-/AN2/C2IN1-/RPB0/CTED2/RB0                       | 59         | D2-                                                                |

| 25    | PGEC3/OA1OUT/AN3/C1IN4-/C4IN2-/RPB1/CTED1/RB1                | 60         | D2+                                                                |

| 26    | PGEC1/OA1IN+/AN4/C1IN1+/C1IN3-/C2IN3-/RPB2/RB2               | 61         | AN45/CVD45/RF5                                                     |

| 27    | PGED1/OA1IN-/AN5/CTCMP/C1IN1-/RTCC/RPB3/RB3                  | 62         | Vdd                                                                |

| 28    | VREF-/AN33/CVD33/PMPA7/RF9                                   | 63         | OSCI/CLKI/AN49/CVD49/RPC12/RC12                                    |

| 29    | VREF+/AN34/CVD34/PMPA6/RF10                                  | 64         | OSCO/CLKO/RPC15/RC15                                               |

| 30    | AVDD                                                         | 65         | Vss                                                                |

| 31    | AVss                                                         | 66         | AN46/CVD46/RPA14/RA14                                              |

| 32    | OA3OUT/AN6/CVD6/C3IN4-/C4IN1+/C4IN4-/RPC0/RC0                | 67         | AN47/CVD47/RPA15/RA15                                              |

| 33    | OA3IN-/AN7/CVD7/C3IN1-/C4IN1-/RPC1/RC1                       | 68         | RD8                                                                |

| 34    | OA3IN+/AN8/CVD8/C3IN1+/C3IN3-/RPC2/FLT3/PMPA13/RC2           | 69         | PGED2/RPB5/USBID1/RB5 <sup>(6)</sup>                               |

| 35    | AN11/CVD11/C1IN2-/FLT4/PMPA12/RC11                           | 70         | PGEC2/RPB6/SCK2/PMPA15/RB6 <sup>(5)</sup>                          |

| Note  | 1: The RPn pins can be used by remappable peripherals. See 1 | Table 1 fo | r the available peripherals and 13.3 "Peripheral Pin Select (PPS)" |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 13.3 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See 13.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: Functions are restricted to input functions only and inputs will be slower than standard inputs.

5: The I<sup>2</sup>C library is available in MPLAB Harmony. For future hardware or silicon compatibility, it is recommended to use these pins for the I<sup>2</sup>C master/slave clock. (i.e., SCL).

6: The I<sup>2</sup>C library is available in MPLAB Harmony. For future hardware or silicon compatibility, it is recommended to use these pins for the I<sup>2</sup>C data I/O, (i.e., SDA).

## REGISTER 4-8: SBTxREGy: SYSTEM BUS TARGET 'x' REGION 'y' REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| R/W0         |                   | R/W-0             | R/W0              | R/W-0             | R/W0              | R/W-0             | R/W0             | R/W-0            |  |  |

| 31:24        | BASE<21:14>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | BASE<13:6>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | U-0              |  |  |

| 15:8         |                   |                   |                   | PRI               | —                 |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |

| 7:0          |                   |                   | SIZE<4:0>         |                   |                   | _                 | _                | —                |  |  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-10 BASE<21:0>: Region Base Address bits

bit 9 PRI: Region Priority Level bit 1 = Level 2 0 = Level 1 bit 2

## bit 8 Unimplemented: Read as '0'

- bit 7-3 SIZE<4:0>: Region Size bits

- Permissions for a region are only active is the SIZE is non-zero. 11111 = Region size =  $2^{(SIZE - 1)} \times 1024$  (bytes)

•

- .

- .

00001 = Region size =  $2^{(SIZE - 1)} \times 1024$  (bytes)

00000 = Region is not present

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Refer to Table 4-6 for the list of available targets and their descriptions.

2: For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | NMIKI             | EY<7:0>           |                   |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-24 **NMIKEY<7:0>:** Software Generated NMI Key Register bits Software NMI event when the correct key (4Eh) is written. Software NMI event not generated when any other value (not the key) is written.

#### bit 23-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

```

0 = Falling edge

```

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

**REGISTER 8-7:** IPCx: INTERRUPT PRIORITY CONTROL REGISTER 'x' ('x' = 0-63) (CONTINUED)

bit 12-10 IP1<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 . 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 9-8 **IS1<1:0>:** Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Unimplemented: Read as '0' bit 7-5 bit 4-2 IP0<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 1-0 ISO<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Note: This register represents a generic definition of the IPCx register. Refer to Table 8-3 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        |                   | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   | —                 | _                      |                   | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0 U-0           |                        | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 | _                      |                   | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 10.0         | _                 | _                 | -                 | —                 | _                      | —                 | —                | —                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | —                 | —                 | USLPGRD           | USBBUSY <sup>(1)</sup> | —                 | USUSPEND         | USBPWR           |

#### **REGISTER 12-5:** UxPWRC: USB POWER CONTROL REGISTER ('x' = 1 AND 2)

## Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB hardware has detected a change in link status; however, an interrupt is pending and has not yet been generated. Software should not put the device into Sleep mode.

- 0 = An interrupt is not pending

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

#### bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

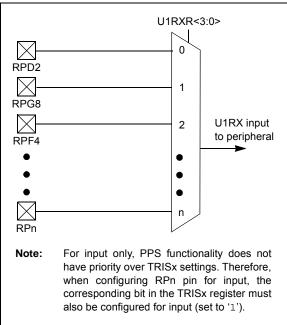

### FIGURE 13-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

## TABLE 13-15: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       |      | E    | Bits |      |      |      |      |       |         |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1    | 16/0 | All Resets |

| 153C                        | INDX3R           | 31:16     | _     | -     | —     | —     | —     | —     | —    | -    | —    | —    | —    | —    | -    | —     | —       | —    | 0000       |

| 1000                        |                  | 15:0      | —     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INDX3 | R<3:0>  |      | 0000       |

| 1540                        | HOME3R           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —       | —    | 0000       |

| 1040                        | HOMEOR           | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | HOME  | 3R<3:0> |      | 0000       |

| 1544                        | QEA4R            | 31:16     | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    | _    | —     |         | —    | 0000       |

| 1044                        |                  | 15:0      | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | QEA4  | R<3:0>  | _    | 0000       |

| 1548                        | QEB4R            | 31:16     | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    | _    | —     | _       | —    | 0000       |

| 1040                        | QLDHK            | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | QEB4  | R<3:0>  |      | 0000       |

| 154C                        | INDX4R           | 31:16     | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | _    | —     | —       | —    | 0000       |

| 1010                        |                  | 15:0      | —     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INDX4 | R<3:0>  |      | 0000       |

| 1550                        | HOME4R           | 31:16     | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    | _    | —     |         | —    | 0000       |

| 1000                        | HOME III         | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | HOME4 | R<3:0>  |      | 0000       |

| 1554                        | QEA5R            | 31:16     | —     | _     | —     | _     | _     | _     | —    | _    | _    | _    | _    | _    | _    | —     | —       | —    | 0000       |

| 1004                        | QL/ (OIX         | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | QEA5  | R<3:0>  |      | 0000       |

| 1558                        | QEB5R            | 31:16     | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | _    | —     | —       | —    | 0000       |

| 1000                        | QLDOIX           | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | QEB5  | R<3:0>  |      | 0000       |

| 155C                        | INDX5R           | 31:16     | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    | _    | —     |         | —    | 0000       |

| 1000                        | INDICIN          | 15:0      | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | INDX5 | R<3:0>  | _    | 0000       |

| 1560                        | HOME5R           | 31:16     | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | _    | —     | —       | —    | 0000       |

| 1000                        | HOMEOR           | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | HOME  | 5R<3:0> |      | 0000       |

| 1564                        | QEA6R            | 31:16     | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | _    | —     | —       | —    | 0000       |

| 1004                        | QL/IOR           | 15:0      | —     | _     | —     | _     |       |       |      | _    |      |      | _    | _    |      | QEA6  | R<3:0>  |      | 0000       |

| 1568                        | QEB6R            | 31:16     | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    |       | —       | —    | 0000       |

| 1300                        | QLDUK            | 15:0      | —     | _     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | QEB6  | R<3:0>  | _    | 0000       |

| 156C                        | INDX6R           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | —    | _    | _    |       | _       | —    | 0000       |

| 1000                        | INDAUX           | 15:0      | _     | -     | —     | —     | —     | —     | —    | -    | —    | —    | _    | —    |      | INDX6 | R<3:0>  |      | 0000       |

| 1570                        | HOME6P           | 31:16     | _     |       | —     | —     | —     | —     | —    |      | —    | —    | —    | —    |      | _     | _       | —    | 0000       |

| 1370                        | 1570 HOME6R      | 15:0      | _     | —     |       | _     |       | —     | _    | —    | —    | _    |      | _    |      | HOME  | 6R<3:0> |      | 0000       |

PIC32MK GP/MC Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

3: This register is only available on PIC32MKXXXGPEXXX devices.

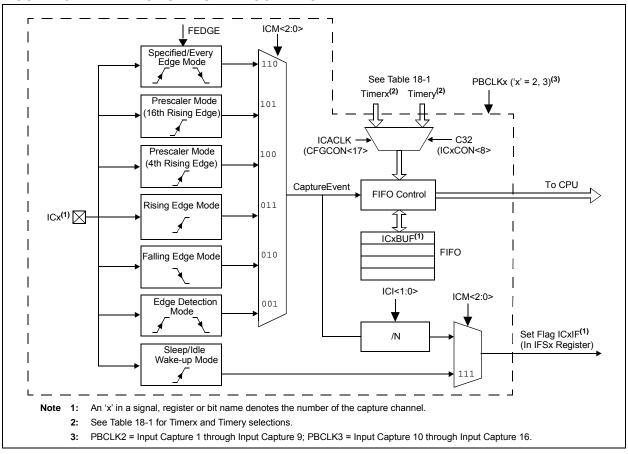

## **18.0 INPUT CAPTURE**

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin.

Capture events are caused by the following factors:

- Capture timer value on every edge (rising and falling), specified edge first

- · Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between either four 16-bit time bases or two 32-bit time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values; Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

#### FIGURE 18-1: INPUT CAPTURE BLOCK DIAGRAM

## TABLE 25-2: ADC REGISTER MAP (CONTINUED)

|                    |                          | e         |                  |                  |       |       |       |       |      | Bit    | 5     |      |      |      |      |      |      |      | s          |

|--------------------|--------------------------|-----------|------------------|------------------|-------|-------|-------|-------|------|--------|-------|------|------|------|------|------|------|------|------------|

| Virtual<br>Address | Register<br>Name         | Bit Range | 31/15            | 30/14            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 76E0               | ADCDATA14                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<  | 5:0>  |      |      |      |      |      |      |      | 000        |

| 76F0               | ADCDATA15                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<  | 5:0>  |      |      |      |      |      |      |      | 000        |

| 7700               | ADCDATA16                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<  | 5:0>  |      |      |      |      |      |      |      | 000        |

| 7710               | ADCDATA17                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  | DATA<15:0> 0000  |       |       |       |       |      |        |       |      |      |      |      |      |      |      |            |

| 7720               | ADCDATA18                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<  | 5:0>  |      |      |      |      |      |      |      | 000        |

| 7730               | ADCDATA19                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 000        |

| 7740               | ADCDATA20 <sup>(1)</sup> | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 000        |

|                    |                          | 15:0      |                  | DATA<15:0> 0000  |       |       |       |       |      |        |       |      |      |      |      |      |      |      |            |

| 7750               | ADCDATA21 <sup>(1)</sup> | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

| 7760               | ADCDATA22 <sup>(1)</sup> | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

| 7770               | ADCDATA23 <sup>(1)</sup> | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

| 7780               | ADCDATA24                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

| 7790               | ADCDATA25                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

| 77A0               | ADCDATA26                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

| 77B0               | ADCDATA27                | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  | DATA<15:0> 0000  |       |       |       |       |      |        |       |      |      |      |      |      |      |      |            |

| 7810               | ADCDATA33 <sup>(1)</sup> | 31:16     | DATA<31:16> 0000 |                  |       |       |       |       |      |        |       |      |      |      |      |      |      |      |            |

|                    |                          | 15:0      |                  | DATA<15:0> 0000  |       |       |       |       |      |        |       |      |      |      |      |      |      |      |            |

| 7820               | ADCDATA34 <sup>(1)</sup> | 31:16     |                  | DATA<31:16> 0000 |       |       |       |       |      |        |       |      |      |      |      |      |      |      |            |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<  |       |      |      |      |      |      |      |      | 0000       |

| 7830               | ADCDATA35 <sup>(1)</sup> | 31:16     |                  |                  |       |       |       |       |      | DATA<3 | 1:16> |      |      |      |      |      |      |      | 0000       |

|                    |                          | 15:0      |                  |                  |       |       |       |       |      | DATA<1 | 5:0>  |      |      |      |      |      |      |      | 0000       |

Note

This bit or register is not available on 64-pin devices. This register is for internal ADC input sources (i.e., VBAT, and CTMU Temperature Sensor. Before enabling the ADC, the user application must initialize the ADC calibration values by copying them from the factory programmed DEVADCx Flash locations starting at 0xBFC45000 into the ADCxCFG registers starting at 0xBF887D00, respectively. 1: 2: 3:

| Bit Bit<br>Range 31/23/15/7 |             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------|-------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24 U-0<br>—              |             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|                             |             | —                 |                   |                   | SH5AL             | .T<1:0>           | SH4AL            | .T<1:0>          |

| 23:16                       | R/W-0 R/W-0 |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10                       | SH3A        | LT<1:0>           | SH2AL             | T<1:0>            | SH1AL             | .T<1:0>           | SH0AL            | .T<1:0>          |

| 15:8                        | U-0         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0                        | —           | —                 | STRGEN5           | STRGEN4           | STRGEN3           | STRGEN2           | STRGEN1          | STRGEN0          |

| 7:0                         | U-0         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0                         | _           | _                 | SSAMPEN5          | SSAMPEN4          | SSAMPEN3          | SSAMPEN2          | SSAMPEN1         | SSAMPEN0         |

#### REGISTER 25-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-28 Unimplemented: Read as '0'

bit 27-26 SH5ALT<1:0>: ADC5 Analog Input Select bit

$11 = AN25^{(1)}$  $10 = AN6^{(1)}$

01 = AN2<sup>(1)</sup>

00 **= AN5**

bit 25-24 SH4ALT<1:0>: ADC4 Analog Input Select bit

- $11 = AN0^{(1)}$

- 10 = AN9<sup>(1)</sup>

- $01 = AN1^{(1)}$

- 00 = AN4

bit 23-22 SH3ALT<1:0>: ADC3 Analog Input Select bit

- $11 = AN26^{(1)}$

- $10 = AN8^{(1)}$

- $01 = AN0^{(1)}$

- 00 **= AN3**

#### bit 21-20 SH2ALT<1:0>: ADC2 Analog Input Select bit

- $11 = AN25^{(1)}$

- $10 = AN6^{(1)}$

- $01 = AN5^{(1)}$

- 00 **= AN2**

bit 19-18 SH1ALT<1:0>: ADC1 Analog Input Select bit

- $11 = AN0^{(1)}$

- $10 = AN7^{(1)}$

- 01 = AN4<sup>(1)</sup>

- 00 **= AN1**

bit 17-16 SH0ALT<1:0>: ADC0 Analog Input Select bit

- $11 = AN24^{(1)}$

- $10 = AN5^{(1)}$

- 01 = AN3<sup>(1)</sup>

- 00 **= AN0**

- bit 15-14 Unimplemented: Read as '0'

- **Note 1:** Regardless of which alternate input is selected by SHxALT, for ADC0-ADC5 only, all control and results are handled by the native SHxALT = `0b00 input. For example, SH0ALT = `0b11 = AN24. However, from a software and silicon hardware control and results register perspective, the user must initialize the ADC0 module as if AN24 were actually AN0.

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6    | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|----------------------|----------------------|----------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0                  | U-0                  | U-0                  | U-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     | _                    | —                    | _                    | -                    | CSS27             | CSS26             | CSS25            | CSS24            |

| 00.40     | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | CSS23 <sup>(1)</sup> | CSS22 <sup>(1)</sup> | CSS21 <sup>(1)</sup> | CSS20 <sup>(1)</sup> | CSS19             | CSS18             | CSS17            | CSS16            |

| 15:8      | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | CSS15                | CSS14                | CSS13                | CSS12                | CSS11             | CSS10             | CSS9             | CSS8             |

| 7:0       | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | CSS7                 | CSS6                 | CSS5                 | CSS4                 | CSS3              | CSS2              | CSS1             | CSS0             |

#### REGISTER 25-11: ADCCSS1: ADC COMMON SCAN SELECT REGISTER 1

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-28 Unimplemented: Read as '0'

bit 27-0 CSS27:CSS0: Analog Common Scan Select bits

Analog inputs AN27-AN6 are always Class 3 shared ADC7.

- 1 = Select AN*x* for input scan (i.e., ANx = CSSx and scan is sequential starting with the lowest to highest enabled CSSx analog input pin)

- 0 = Skip ANx for input scan

**Note 1:** This bit is not available on 64-pin devices.

- **Note 1:** In addition to setting the appropriate bits in this register, Class 1 and Class 2 analog inputs must select the STRIG input as the trigger source if they are to be scanned through the CSS*x* bits. Refer to the bit descriptions in the ADCTRGx registers for selecting the STRIG option.

- 2: If a Class 1 or Class 2 input is included in the scan by setting the CSSx bit to '1' and by setting the TRGSRCx<4:0> bits to STRIG mode (`0b11), the user application must ensure that no other triggers are generated for that input using the RQCNVRT bit in the ADCCON3 register or the hardware input or any digital filter. Otherwise, the scan behavior is unpredictable.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|------------------------|------------------------|------------------------|------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                    | U-0                    | U-0                    | U-0                    | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |

|              | —                      | —                      | —                      | —                      | AIRDY27           | AIRDY26           | AIRDY25          | AIRDY24          |  |  |  |

| 00.40        | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |

| 23:16        | AIRDY23 <sup>(1)</sup> | AIRDY22 <sup>(1)</sup> | AIRDY21 <sup>(1)</sup> | AIRDY20 <sup>(1)</sup> | AIRDY19           | AIRDY18           | AIRDY17          | AIRDY16          |  |  |  |

| 15:8         | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |

| 15.0         | AIRDY15                | AIRDY14                | AIRDY13                | AIRDY12                | AIRDY11           | AIRDY10           | AIRDY9           | AIRDY8           |  |  |  |

| 7:0          | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |

| 7:0          | AIRDY7                 | AIRDY6                 | AIRDY5                 | AIRDY4                 | AIRDY3            | AIRDY2            | AIRDY1           | AIRDY0           |  |  |  |

|              |                        |                        |                        |                        |                   |                   |                  |                  |  |  |  |

#### REGISTER 25-13: ADCDSTAT1: ADC DATA READY STATUS REGISTER 1

| Legend:           | HS = Hardware Set | HC = Hardware Clear                | ed                 |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-28 Unimplemented: Read as '0'

- bit 27-0 AIRDY27:AIRDY0: Conversion Data Ready for Corresponding Analog Input Ready bits

- 1 = This bit is set when converted data is ready in the data register

- 0 = This bit is cleared when the associated data register is read

- Note 1: This bit is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 31:24        | U-0                    |

| 51.24        | —                      | _                      | —                      | —                      | —                      | _                      | _                      | —                      |

| 23:16        | U-0                    | U-0                    | R-0, HS, HC            |

| 23.10        | —                      | —                      | AIRDY53                | AIRDY52                | AIRDY51                | AIRDY50                | AIRDY49                | AIRDY48                |

| 15:8         | R-0, HS, HC            | R-0, HS, HC            | R-0, HS, HC            | U-0                    | U-0                    | U-0                    | R-0, HS, HC            | R-0, HS, HC            |

| 15.0         | AIRDY47 <sup>(1)</sup> | AIRDY46 <sup>(1)</sup> | AIRDY45 <sup>(1)</sup> | —                      | —                      | —                      | AIRDY41 <sup>(1)</sup> | AIRDY40 <sup>(1)</sup> |

| 7:0          | R-0, HS, HC            | U-0                    |

| 7.0          | AIRDY39 <sup>(1)</sup> | AIRDY38 <sup>(1)</sup> | AIRDY37 <sup>(1)</sup> | AIRDY36 <sup>(1)</sup> | AIRDY35 <sup>(1)</sup> | AIRDY34 <sup>(1)</sup> | AIRDY33 <sup>(1)</sup> | —                      |

#### REGISTER 25-14: ADCDSTAT2: ADC DATA READY STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared              |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-22 Unimplemented: Read as '0'

- bit 23-13 AIRDY53:AIRDY45: Conversion Data Ready for Corresponding Analog Input Ready bits

- 1 = This bit is set when converted data is ready in the data register

- 0 = This bit is cleared when the associated data register is read

- bit 12-10 Unimplemented: Read as '0'

- bit 23-13 AIRDY41:AIRDY33: Conversion Data Ready for Corresponding Analog Input Ready bits

- 1 = This bit is set when converted data is ready in the data register

- 0 = This bit is cleared when the associated data register is read

Note 1: This bit is not available on 64-pin devices.

## TABLE 26-1: CAN1 THROUGH CAN4 REGISTER SUMMARY (CONTINUED)

| esa                         |                                 |           |          |          |          |          |          |             |         | Bit       | S       |         |         |         |           |            |         |         |            |

|-----------------------------|---------------------------------|-----------|----------|----------|----------|----------|----------|-------------|---------|-----------|---------|---------|---------|---------|-----------|------------|---------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14    | 29/13    | 28/12    | 27/11    | 26/10       | 25/9    | 24/8      | 23/7    | 22/6    | 21/5    | 20/4    | 19/3      | 18/2       | 17/1    | 16/0    | All Resets |

|                             | OAINIT                          | 31:16     | IVRIE    | WAKIE    | CERRIE   | SERRIE   | RBOVIE   | _           |         |           |         | —       | _       | _       | MODIE     | CTMRIE     | RBIE    | TBIE    | 0000       |

| 5020                        | C4INT                           | 15:0      | IVRIF    | WAKIF    | CERRIF   | SERRIF   | RBOVIF   | _           | _       | _         | _       | _       | _       | _       | MODIF     | CTMRIF     | RBIF    | TBIF    | 0000       |

| 5020                        | C4VEC                           | 31:16     | —        | _        | _        | —        | _        | _           |         | _         | _       | _       | —       | _       | —         | _          | —       | —       | 0000       |

| 5030                        | C4VEC                           | 15:0      | _        | _        | _        |          |          | FILHIT<4:0> | >       |           | _       |         |         |         | CODE<6:0> |            |         |         | 0040       |

| 50.40                       | 0.47050                         | 31:16     | _        | _        | _        | _        | _        | —           | _       | —         | _       | _       | TXBO    | TXBP    | RXBP      | TXWARN     | RXWARN  | EWARN   | 0000       |

| 5040                        | C4TREC                          | 15:0      |          |          |          | TERRC    | NT<7:0>  |             |         |           |         |         |         | RERRCM  | VT<7:0>   |            |         |         | 0000       |

| 5050                        | CAFOTAT                         | 31:16     | —        | —        | —        | —        | _        | —           | _       | —         | _       | —       | _       | _       | —         | —          | —       | —       | 0000       |

| 5050                        | C4FSTAT                         | 15:0      | FIFOIP15 | FIFOIP14 | FIFOIP13 | FIFOIP12 | FIFOIP11 | FIFOIP10    | FIFOIP9 | FIFOIP8   | FIFOIP7 | FIFOIP6 | FIFOIP5 | FIFOIP4 | FIFOIP3   | FIFOIP2    | FIFOIP1 | FIFOIP0 | 0000       |

| 5000                        | 060 C4RXOVF                     | 31:16     | _        | _        | _        | _        | —        | _           | —       | —         | _       | _       | _       | _       | —         | _          | —       | —       | 0000       |

| 5060                        | C4RXUVF                         | 15:0      | RXOVF15  | RXOVF14  | RXOVF13  | RXOVF12  | RXOVF11  | RXOVF10     | RXOVF9  | RXOVF8    | RXOVF7  | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3    | RXOVF2     | RXOVF1  | RXOVF0  | 0000       |

| 5070                        | CATMO                           | 31:16     |          |          |          |          |          |             |         |           |         |         |         | 0000    |           |            |         |         |            |

| 5070                        | C4TMR                           | 15:0      |          |          |          |          |          |             | CAI     | NTSPRE<15 | :0>     |         |         |         |           |            |         |         | 0000       |

| 5000                        | 0.453/440                       | 31:16     |          |          |          |          |          | SID<10:0>   |         |           |         |         |         |         | MIDE      | —          | EID<1   | 7:16>   | xxxx       |

| 5080                        | C4RXM0                          | 15:0      |          |          |          |          |          |             |         | EID<1     | 5:0>    |         |         |         |           |            |         |         | xxxx       |

|                             |                                 | 31:16     |          |          |          |          |          |             |         |           |         |         |         | xxxx    |           |            |         |         |            |

| 5090                        | C4RXM1                          | 15:0      |          |          |          |          |          |             |         |           |         |         | xxxx    |         |           |            |         |         |            |

|                             |                                 | 31:16     |          |          |          |          |          | SID<10:0>   |         |           |         |         |         |         | MIDE      | _          | EID<1   | 7:16>   | xxxx       |

| 50A0                        | C4RXM2                          | 15:0      |          |          |          |          |          |             |         | EID<1     | 5:0>    |         |         |         |           |            |         |         | xxxx       |

|                             |                                 | 31:16     |          |          |          |          |          | SID<10:0>   |         |           |         |         |         |         | MIDE      | _          | EID<1   | 7:16>   | xxxx       |

| 50B0                        | C4RXM3                          | 15:0      |          |          |          |          |          |             |         | EID<1     | 5.0>    |         |         |         |           |            |         |         | XXXX       |

|                             |                                 | 31:16     | FLTEN3   | MSEL     | 3<1:0>   |          |          | FSEL3<4:0>  | >       | 2.0       | FLTEN2  | MSEL    | 2<1:0>  |         | F         |            |         |         | 0000       |

| 50C0                        | C4FLTCON0                       | 15:0      | FLTEN1   | -        | 1<1:0>   |          |          | FSEL1<4:0   |         |           | FLTEN0  | -       | 0<1:0>  |         |           | SEL0<4:0>  |         |         | 0000       |

|                             |                                 | 31:16     | FLTEN7   |          | 7<1:0>   |          |          | FSEL7<4:0>  |         |           | FLTEN6  |         | 6<1:0>  |         |           | SEL6<4:0>  |         |         | 0000       |

| 50D0                        | C4FLTCON1                       | 15:0      | FLTEN5   |          | 5<1:0>   |          |          | FSEL5<4:0>  |         |           | FLTEN4  |         | 4<1:0>  |         |           | SEL4<4:0>  |         |         | 0000       |

|                             |                                 | 31:16     | FLTEN11  | MSEL1    |          |          |          | FSEL11<4:0  |         |           | FLTEN10 | MSEL1   |         |         |           | SEL10<4:0> |         |         | 0000       |

| 50E0                        | C4FLTCON2                       | 15:0      | FLTEN9   | MSEL     |          |          |          | FSEL9<4:0>  |         |           | FLTEN8  | MSEL    |         |         |           | SEL8<4:0>  |         |         | 0000       |

|                             |                                 | 31:16     | FLTEN15  | MSEL1    |          |          |          | FSEL15<4:0  |         |           | FLTEN14 | MSEL1   |         |         |           | SEL14<4:0> |         |         | 0000       |

| 50F0                        | C4FLTCON3                       | 15:0      | FLTEN13  | MSEL1    |          |          |          | FSEL13<4:0  |         |           | FLTEN12 |         | 2<1:0>  |         |           | SEL12<4:0> |         |         | 0000       |

|                             | C4RXFn                          | 31:16     |          |          |          |          |          | SID<10:0>   |         |           |         |         |         |         | EXID      | _          | EID<1   | 7:16>   | xxxx       |

| 5140                        | (n = 0.15)                      | 15:0      |          |          |          |          |          | 2.12 .0.0.  |         | EID<1     | 5.0>    |         |         |         |           |            | 1 2.5 1 |         | XXXX       |

|                             | ,                               | 31:16     |          |          |          |          |          |             |         |           |         |         |         |         |           |            |         |         | 0000       |

| 5340                        | C4FIFOBA                        | 15:0      |          |          |          |          |          |             |         | C4FIFOB/  | A<31:0> |         |         |         |           |            |         |         | 0000       |

|                             | C4FIFOCONn                      | 31:16     | _        | _        | _        | _        |          | _           |         | _         | _       | _       |         |         |           | FSIZE<4:0> |         |         | 0000       |

| 5350                        |                                 | S         |          |          |          |          |          |             |         |           |         |         |         | 1       |           | 0.22 0.04  |         |         | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See Section13.2 "CLR, SET, and INV Registers" for more Note 1: information.

## **REGISTER 26-2:** CxCFG: CAN BAUD RATE CONFIGURATION REGISTER ('x' = 1-4) (CONTINUED)

- bit 10-8 **PRSEG<2:0>:** Propagation Time Segment bits<sup>(4)</sup> 111 = Length is  $8 \times TQ$  $000 = \text{Length is } 1 \times TQ$ SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup> bit 7-6 11 = Length is  $4 \times TQ$  $10 = \text{Length is } 3 \times TQ$ 01 = Length is 2 x TQ 00 = Length is 1 x TQ bit 5-0 BRP<5:0>: Baud Rate Prescaler bits 111111 = TQ = (2 x 64) / PBCLK5 111110 = TQ = (2 x 63) / PBCLK5 • 000001 = Tq = (2 x 2) / PBCLK5  $000000 = TQ = (2 \times 1) / PBCLK5$ Note 1: SEG2PH  $\leq$  SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. **2:** 3 Time bit sampling is not allowed for BRP < 2.

- **3:** SJW  $\leq$  SEG2PH.

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CxCON<23:21>) = 100).

# PIC32MK GP/MC Family

#### REGISTER 26-17: CxFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('x' = 1-4); n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |  |  |  |  |  |  |

| 31:24        | _                 | _                 | —                 | _                 | _                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |  |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |  |  |  |  |  |  |

| 15:8         | —                 | —                 | —                 | —                 | _                 | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |  |  |  |  |  |  |

| 7:0          | _                 | _                 |                   |                   | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |  |  |  |  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

## bit 31-27 Unimplemented: Read as '0'

| DIL 31-21 | Unimplemented. Read as 0                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|           | 1 = Interrupt enabled for FIFO not full                                                                         |

|           | 0 = Interrupt disabled for FIFO not full                                                                        |

| bit 25    | TXHALFIE: Transmit FIFO Half Full Interrupt Enable bit                                                          |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit                                                      |

|           | 1 = Interrupt enabled for FIFO empty                                                                            |

| h:+ 00 00 | 0 = Interrupt disabled for FIFO empty                                                                           |

|           | Unimplemented: Read as '0'                                                                                      |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                         |

|           | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

|           | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | <ul> <li>1 = Interrupt enabled for FIFO half full</li> <li>0 = Interrupt disabled for FIFO half full</li> </ul> |

| bit 16    |                                                                                                                 |

| DIL 10    | RXNEMPTYIE: Empty Interrupt Enable bit                                                                          |

|           | <ul> <li>1 = Interrupt enabled for FIFO not empty</li> <li>0 = Interrupt disabled for FIFO not empty</li> </ul> |

| hit 15_11 | Unimplemented: Read as '0'                                                                                      |

| bit 10    | •                                                                                                               |

|           | <b>TXNFULLIF:</b> Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                      |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full                                 |

|           | 0 = FIFO is full                                                                                                |

|           | TXEN = 0: (FIFO configured as a receive buffer)                                                                 |

|           | Unused, reads '0'                                                                                               |

|           |                                                                                                                 |

| Note 1:   | This bit is read-only and reflects the status of the FIFO.                                                      |

|           |                                                                                                                 |

| REGIST  | TER 26-17: CxFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n'<br>('x' = 1-4); n' = 0 THROUGH 15) (CONTINUED)                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9   | <b>TXHALFIF:</b> FIFO Transmit FIFO Half Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1</u> : (FIFO configured as a transmit buffer)<br>1 = FIFO is $\leq$ half full<br>0 = FIFO is > half full                       |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                                                                                                   |

| bit 8   | <b>TXEMPTYIF:</b> Transmit FIFO Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is empty<br>0 = FIFO is not empty, at least 1 message queued to be transmitted |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                                                                                                   |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 3   | <b>RXOVFLIF:</b> Receive FIFO Overflow Interrupt Flag bit<br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                     |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = Overflow event has occurred<br>0 = No overflow event occured                                                                                                    |

| bit 2   | <b>RXFULLIF:</b> Receive FIFO Full Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                          |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is full<br>0 = FIFO is not full                                                                                                                            |

| bit 1   | <b>RXHALFIF:</b> Receive FIFO Half Full Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                     |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is $\geq$ half full<br>0 = FIFO is < half full                                                                                                             |

| bit 0   | <b>RXNEMPTYIF:</b> Receive Buffer Not Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                 |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is not empty, has at least 1 message<br>0 = FIFO is empty                                                                                                  |

Note 1: This bit is read-only and reflects the status of the FIFO.

| Bit Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6 | Bit Bit<br>29/21/13/5 28/20/12/4 |        | Bit<br>27/19/11/3 |                      |                      | Bit<br>24/16/8/0     |  |  |  |

|-----------|------------------------------|-------------------|----------------------------------|--------|-------------------|----------------------|----------------------|----------------------|--|--|--|

| 31:24     | U-0                          | U-0               | U-0                              | U-0    | U-0               | U-0                  | U-0                  | U-0                  |  |  |  |

| 51.24     | —                            | —                 | —                                | _      | —                 | _                    | _                    | —                    |  |  |  |

| 23:16     | U-0                          | U-0               | U-0                              | U-0    | U-0               | U-0                  | U-0                  | U-0                  |  |  |  |

| 23.10     | —                            | —                 | —                                | _      | —                 | _                    | _                    | —                    |  |  |  |

| 15:8      | R/W-0                        | R/W-0             | R/W-0                            | R/W-0  | R/W-0             | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| 15.0      | PTPER<15:8> <sup>(1,2)</sup> |                   |                                  |        |                   |                      |                      |                      |  |  |  |

| 7:0       | R/W-0                        | R/W-0             | R/W-1                            | R/W-0  | R/W-0             | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> |  |  |  |

| 7.0       |                              |                   |                                  | PTPER• | <7:0>(1,2)        |                      |                      |                      |  |  |  |

## REGISTER 31-2: PTPER: PRIMARY MASTER TIME BASE PERIOD REGISTER

## Legend:

| Togonal           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **PTPER<15:0>:** Primary Master Time Base Period Value bits<sup>(1,2,4)</sup>

**Note 1:** Minimum LSb = 1 / FSYSCLK.

- **2:** Minimum value is 0x0008.

- **3:** If a period value is lesser than 0x0008 is chosen, the internal hardware forcefully sets the period to a minimum value of 0x0008.

- **4:** PTPER = (FSYSCLK / (FPWM \* PCLKDIV<2:0> bits (PTCON<6:4>)). FPWM = User-desired PWM Frequency.

## 32.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32MK GP/MC devices include two features to prevent alterations to enabled or disabled peripherals:

- Control Register Lock Sequence

- Configuration Bit Select Lock

#### 32.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting the PMDLOCK bit prevents writes to the control registers and clearing the PMDLOCK bit allows writes.

To set or clear the PMDLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators** with Enhanced PLL" (DS60001250) in the *"PIC32 Family Reference Manual"* for details.

#### 32.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If the PMDLOCK bit remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

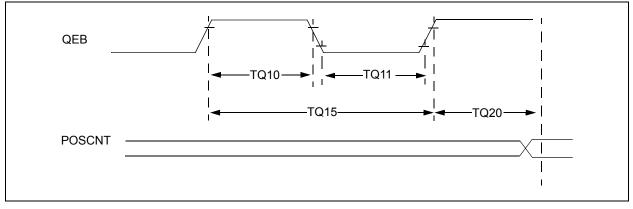

#### FIGURE 36-14: QEI MODULE EXTERNAL CLOCK TIMING CHARACTERISTICS