Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | CANbus, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                          |

| Number of I/O              | 48                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                      |

| Data Converters            | A/D 26x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512gpe064-i-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

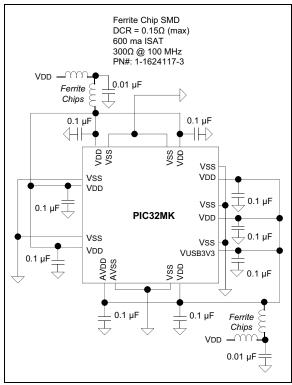

# 2.10.1.3 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/Boost regulators as the local power source for PIC32MK GP devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-9. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

FIGURE 2-9: EMI/EMC/EFT SUPPRESSION CIRCUIT

#### REGISTER 7-3: RNMICON: NON-MASKABLE INTERRUPT (NMI) CONTROL REGISTER

bit 16 WDTS: Watchdog Timer Time-out in Sleep Mode Flag bit

1 = WDT time-out has occurred during Sleep mode and caused a wake-up from sleep

0 = WDT time-out has not occurred during Sleep mode

Setting this bit will cause a WDT NMI.

bit 15-0 NMICNT<15:0>: NMI Reset Counter Value bits

These bits specify the reload value used by the NMI reset counter.

11111111-00000001 = Number of SYSCLK cycles before a device Reset occurs (1)

00000000 = No delay between NMI assertion and device Reset event

Note 1: When a Watchdog Timer NMI event (when not in Sleep mode) or a Deadman Timer NMI event is triggered the NMICNT will start decrementing. When NMICNT reaches zero, the device is Reset. This NMI reset counter is only applicable to these two specific NMI events.

Note: The system unlock sequence must be performed before the SWRST bit is written. Refer to the Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

#### REGISTER 12-2: UxOTGIE: USB OTG INTERRUPT ENABLE REGISTER ('x' = 1 AND 2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | 1                 | -                 | -                 | _                 | -                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 |                   | -                 | -                 | -                 | _                 | _                |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7.0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 IDIE: ID Interrupt Enable bit

1 = ID interrupt is enabled

0 = ID interrupt is disabled

bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

1 = 1 millisecond timer interrupt is enabled0 = 1 millisecond timer interrupt is disabled

bit 5 LSTATEIE: Line State Interrupt Enable bit

1 = Line state interrupt is enabled

0 = Line state interrupt is disabled

bit 4 ACTVIE: Bus Activity Interrupt Enable bit

1 = ACTIVITY interrupt is enabled

0 = ACTIVITY interrupt is disabled

bit 3 SESVDIE: Session Valid Interrupt Enable bit

1 = Session valid interrupt is enabled

0 = Session valid interrupt is disabled

bit 2 SESENDIE: B-Session End Interrupt Enable bit

1 = B-session end interrupt is enabled

0 = B-session end interrupt is disabled

bit 1 Unimplemented: Read as '0'

bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

1 = A-VBUS valid interrupt is enabled

0 = A-VBUS valid interrupt is disabled

#### 13.4 I/O Ports Control Registers

TABLE 13-3: PORTA REGISTER MAP FOR 100-PIN DEVICES ONLY

| Oncord   O | ess                         | _                               | ø         |         |         |       |         |         |         |      | Bit    | ts     |      |      |        |      |      |        |        |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|-----------|---------|---------|-------|---------|---------|---------|------|--------|--------|------|------|--------|------|------|--------|--------|---------------|

| 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13 | 28/12   | 27/11   | 26/10   | 25/9 | 24/8   | 23/7   | 22/6 | 21/5 | 20/4   | 19/3 | 18/2 | 17/1   | 16/0   | All<br>Resets |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000                        | ANSFI A                         |           |         | _       | _     |         | _       | _       | _    |        | _      | _    | _    |        | _    | _    | _      |        | 0000          |

| 0010   TRISA   15:0   TRISA15   TRISA14     TRISA12   TRISA11   TRISA10     TRISA6   TRISA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0000                        | , a voll, v                     |           | ANSA15  | ANSA14  | _     | ANSA12  | ANSA11  | _       | _    | ANSA8  | _      |      | _    | ANSA4  |      | _    | ANSA1  | ANSA0  | D813          |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0010                        | TRISA                           |           |         | _       | _     | _       | _       | _       |      |        |        | _    | _    | _      | _    | _    | _      |        | 0000          |

| 0020   PORTA   15.0   RA15   RA14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0010                        | 11110/1                         |           | TRISA15 | TRISA14 | _     | TRISA12 | TRISA11 | TRISA10 | _    | TRISA8 | TRISA7 | _    | _    | TRISA4 | _    | _    | TRISA1 | TRISA0 | DD93          |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0020                        | PORTA                           | 31:16     |         | _       | _     | _       | _       | _       | _    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

| 0050 LATA 15:0 LATA15 LATA14 — LATA12 LATA10 — LATA6 LATA7 — LATA4 — — LATA4 — — LATA1 LATA0 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0020                        | 1 01(1)(                        | 15:0      | RA15    | RA14    | _     | RA12    | RA11    | RA10    | _    | RA8    | RA7    | _    | _    | RA4    | _    | _    | RA1    | RA0    | xxxx          |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0030                        | ΙΑΤΑ                            | 31:16     |         | _       |       | _       | _       | _       | _    | _      | _      |      | _    | _      |      | _    | _      | _      | 0000          |

| ODCA   ODCA   15:0   ODCA15   ODCA14   ODCA12   ODCA11   ODCA10   ODCA8   ODCA7   ODCA4   ODCA4   ODCA1   ODCA0   OD | 0000                        | D, (i), (                       | 15:0      | LATA15  | LATA14  |       | LATA12  | LATA11  | LATA10  | _    | LATA8  | LATA7  |      | _    | LATA4  |      | _    | LATA1  | LATA0  | xxxx          |

| 15:0   ODCA15   ODCA14   - ODCA12   ODCA11   ODCA10   - ODCA8   ODCA7   ODCA4   ODCA4   ODCA0   ODCA         | 0040                        | ODCA                            | 31:16     | _       | _       |       | _       | _       | _       | _    | _      | _      |      | _    | _      |      | _    | _      | _      | 0000          |

| 0050   CNPUA   15:0   CNPUA15   CNPUA14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0040                        | ODOM                            | 15:0      | ODCA15  | ODCA14  |       | ODCA12  | ODCA11  | ODCA10  | _    | ODCA8  | ODCA7  |      | _    | ODCA4  |      | _    | ODCA1  | ODCA0  | 0000          |

| 15:0   CNPUA15 CNPUA14   — CNPUA12 CNPUA10   — CNPUA8   CNPUA7   — CNPUA4   — CNPUA4   CNPUA0   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000   000  | 0050                        | CNPHA                           |           | _       | _       |       | _       | _       | _       | _    | _      | _      |      | _    | _      |      | _    | _      | _      | 0000          |

| 0060   CNPDA   15:0   CNPDA15   CNPDA14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000                        | OIVI O/V                        | 15:0      | CNPUA15 | CNPUA14 |       | CNPUA12 | CNPUA11 | CNPUA10 | _    | CNPUA8 | CNPUA7 |      | _    | CNPUA4 |      | _    | CNPUA1 | CNPUA0 | 0000          |

| 15:0   CNPDA15 CNPDA14   — CNPDA12 CNPDA11   CNPDA10   — CNPDA8 CNPDA7   — CNPDA4   — CNPDA1 CNPDA0   000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   00000   0000   0000   0000   00000   0000   0000   00 | 0060                        | CNDDA                           | 31:16     | _       | _       | _     | _       | _       | _       | 1    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

| OTO   ONCONA   15:0   ON   -   SIDL   -   EDGE   DETECT   -   -   -   -   -   -   -   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0000                        | ON DA                           | 15:0      | CNPDA15 | CNPDA14 |       | CNPDA12 | CNPDA11 | CNPDA10 | _    | CNPDA8 | CNPDA7 |      | _    | CNPDA4 |      | _    | CNPDA1 | CNPDA0 | 0000          |

| 15:0   ON   -   SIDL   -   DETECT   -   -   -   -   -   -   -   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             | L                               | 31:16     | _       | _       |       | _       | _       | _       | _    | _      | _      |      | _    | _      |      | _    | _      | _      | 0000          |

| ONE   ONE  | 0070                        | CNCONA                          | 15:0      | ON      | _       | SIDL  | _       |         | _       | _    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

| 15:0   CNIEA15   CNIEA14   —   CNIEA12   CNIEA10   —   CNIEA8   CNIEA7   —   CNIEA4   —   —   CNIEA1   CNIEA0   000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0080                        | CNENA                           | 31:16     | _       | _       | _     |         | -       | _       | I    | _      | _      | _    | -    | _      | _    | _    | _      | -      | 0000          |

| 0090   CNSTATA   15:0   CN   CN   STATA15   STATA14   -   STATA12   STATA11   STATA10   -   STATA8   STATA7   -   -   CN   STATA4   -   -   CN   STATA1   STATA0   0000   CNNEA   15:0   CNNEA15   CNNEA14   -   CNNEA12   CNNEA11   CNNEA10   -   CNNEA8   CNNEA7   -   -   CNNEA4   -   -   CNNEA1   CNNEA0   0000   CNFA   15:0   CNFA15   CNFA14   -   CNFA12   CNFA11   CNFA10   -   CNFA8   CNFA7   -   -   -   -   -   -   -   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0000                        | CINLINA                         | 15:0      | CNIEA15 | CNIEA14 | _     | CNIEA12 | CNIEA11 | CNIEA10 | ı    | CNIEA8 | CNIEA7 | _    |      | CNIEA4 | _    | _    | CNIEA1 | CNIEA0 | 0000          |

| 15:0   STATA15   STATA14   STATA12   STATA11   STATA10   STATA8   STATA7   STATA4   STATA4   STATA1   STATA0   000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             | L                               | 31:16     | _       | _       | _     |         | -       | _       | I    | _      | _      | _    | -    | _      | _    | _    | _      | -      | 0000          |

| 00A0         CNNEA         15:0         CNNEA15         CNNEA14         —         CNNEA12         CNNEA10         —         CNNEA8         CNNEA7         —         —         CNNEA4         —         —         CNNEA1         CNNEA0         0000           00B0         CNFA         31:16         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0090                        | CNSTATA                         | 15:0      |         |         | _     |         |         |         | ı    |        |        | _    | ı    |        | _    | 1    |        |        | 0000          |

| 15:0   CNNEA15   CNNEA14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00.40                       | CNINEA                          | 31:16     | _       | _       | _     | _       | 1       | _       | _    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

| 00B0         CNFA         15:0         CNFA15         CNFA14         —         CNFA12         CNFA11         CNFA10         —         CNFA7         —         —         CNFA4         —         —         CNFA0         000           00C0         SRCON0A         31:16         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         — <td>UUAU</td> <td>CININEA</td> <td>15:0</td> <td>CNNEA15</td> <td>CNNEA14</td> <td>_</td> <td>CNNEA12</td> <td>CNNEA11</td> <td>CNNEA10</td> <td>-</td> <td>CNNEA8</td> <td>CNNEA7</td> <td>_</td> <td>_</td> <td>CNNEA4</td> <td>_</td> <td>_</td> <td>CNNEA1</td> <td>CNNEA0</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | UUAU                        | CININEA                         | 15:0      | CNNEA15 | CNNEA14 | _     | CNNEA12 | CNNEA11 | CNNEA10 | -    | CNNEA8 | CNNEA7 | _    | _    | CNNEA4 | _    | _    | CNNEA1 | CNNEA0 | 0000          |

| 15:0   CNFA15   CNFA14   -   CNFA12   CNFA11   CNFA10   -   CNFA8   CNFA7   -   -   CNFA4   -   -   CNFA1   CNFA0   0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0000                        | CNITA                           | 31:16     | -       | -       | _     | -       | 1       | _       | _    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

| 15:0 — — — — SROA10 — SROA8 SROA7 — — — — — — — — — 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ООВО                        | CNFA                            | 15:0      | CNFA15  | CNFA14  | _     | CNFA12  | CNFA11  | CNFA10  | _    | CNFA8  | CNFA7  | _    | _    | CNFA4  | _    | _    | CNFA1  | CNFA0  | 0000          |

| 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00C0                        | SRCON0A                         | 31:16     | _       | _       | _     | _       | _       | _       | _    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | •                               | 15:0      | _       | _       | _     | _       | _       | SR0A10  | _    | SR0A8  | SR0A7  | _    | _    | _      | _    | _    | _      | _      | 0000          |

| IOODO LEDCONIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |                                 | 31:16     | _       | _       | _     | _       | _       | _       | _    | _      | _      | _    | _    | _      | _    | _    | _      | _      | 0000          |

| OUDU   SRCONTA   15:0             SR1A10     SR1A8   SR1A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00D0                        | SRCON1A                         |           | _       | _       | _     | _       | _       | SR1A10  | _    | SR1A8  | SR1A7  | _    |      | _      | _    |      | _      | _      | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

#### REGISTER 16-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 |                   | _                 | _                 | _                 | _                | _                |

| 22:46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 |                   | _                 | _                 | _                 | _                | _                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6      | _                 | _                 |                   | _                 | _                 | _                 | _                |                  |

| 7:0       | R-0, HC           | R-0, HC           | R-0, HC           | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R-0              |

| 7:0       | BAD1              | BAD2              | DMTEVENT          |                   |                   |                   |                  | WINOPN           |

**Legend:** HC = Hardware Cleared

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BAD1: Bad STEP1<7:0> Value Detect bit

1 = Incorrect STEP1<7:0> value was detected 0 = Incorrect STEP1<7:0> value was not detected

bit 6 BAD2: Bad STEP2<7:0> Value Detect bit

1 = Incorrect STEP2<7:0> value was detected 0 = Incorrect STEP2<7:0> value was not detected

bit 5 DMTEVENT: Deadman Timer Event bit

1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment)

0 = Deadman timer even was not detected

Note: This bit is cleared only on a Reset.

bit 4-1 **Unimplemented:** Read as '0'

bit 0 WINOPN: Deadman Timer Clear Window bit

1 = Deadman timer clear window is open

0 = Deadman timer clear window is not open

#### REGISTER 22-3: UXRXREG: UARTX RECEIVE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | -                 | _                 | -                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | -                 | 1                 | _                 | 1                 |                  | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | _                 | _                 | _                 | -                 | _                 | _                 | _                | RX<8>            |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 7:0          |                   |                   |                   | RX<7              | ':0>              |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-9 Unimplemented: Read as '0'

bit 8 **RX<8>:** Data bit 8 of the received character (in 9-bit mode)

bit 7-0 RX<7:0>: Data bits 7-0 of the received character

#### REGISTER 22-4: UXTXREG: UARTX TRANSMIT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-x               | U-x               | U-x               | U-x               | U-x               | U-x               | U-x              | U-x              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22.46        | U-x               | U-x               | U-x               | U-x               | U-x               | U-x               | U-x              | U-x              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-x               | U-x               | U-x               | U-x               | U-x               | U-x               | U-x              | W-x              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | TX<8>            |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 7:0          |                   |                   |                   | TX<7              | :0>               |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-9 Unimplemented: Read as initialized data

bit 8 **TX<8>:** Data bit 8 of the transmitted character (in 9-bit mode)

bit 7-0 **TX<7:0>:** Data bits 7-0 of the transmitted character

#### 22.2 UART Broadcast Mode Example

As shown in Table 22-4, the group hardware address identifier bit was arbitrarily chosen as bit 7 with bit 4 chosen as the software group or individual UART target ID. Therefore, the collective group address assigned for all UARTs (i.e, [w, x, y, z]) is 0b100100xx, while the individual addresses are 0b10000000 through 0b10000011, respectively.

Any MASK register bit = 0 means the corresponding ADDR<7:0> bit is a "don't care" from a hardware address matching point of view. Using this scheme, multiple UART subnet groups could be created within a network. If not using address match with a broadcast mode, set the ADDRMSK<7:0> bits (UxSTAT<31:24) = 0x00, which is the default.

To send a broadcast message to all UARTs in the group identified by bit 7=1, send UxTXREG = (0x190), address bit 9 set. All the UARTs in that group, bit 7=1, would generate an interrupt for an address match because of the bit <7:5>,<3:2> match, Logic AND of MASK and ADDR registers equal "true". User software would check if bit 4=1, and if true, the RX<7:0> bits register value is valid for all UARTS.