Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 77                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 42x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512gpe100t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

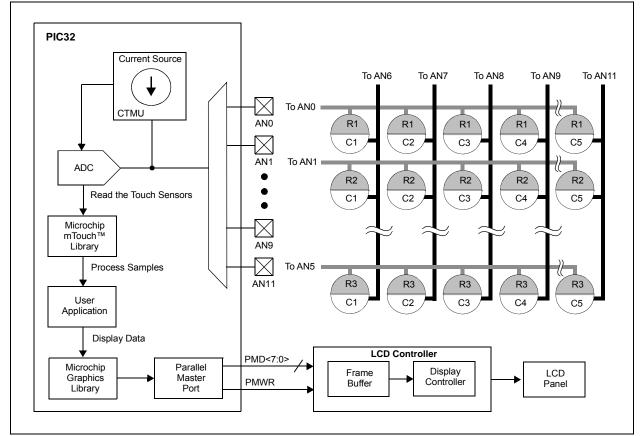

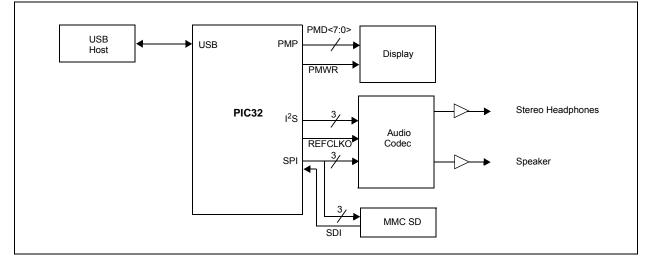

## 2.11 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-10, Figure 2-11, and Figure 2-12.

## FIGURE 2-10: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

FIGURE 2-11: AUDIO PLAYBACK APPLICATION

## TABLE 4-11: SYSTEM BUS TARGET 3 REGISTER MAP

| ess                         |                  |           |       |       |       |          |          |       |       |      | Bits     |       |          |      |        |        |          |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|----------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1     | 16/0   | All<br>Resets |

| 8C20                        | SBT3ELOG1        | 31:16     | MULTI |       | _     | _        |          | CODE  | <3:0> |      | —        | _     | -        | _    | —      | _      | _        | _      | 0000          |

| 0020                        | SBISELOGI        | 15:0      |       |       |       | INI      | TID<7:0> |       |       |      |          | REGIO | N<3:0>   |      | —      | C      | CMD<2:0> |        | 0000          |

| 8C24                        | SBT3ELOG2        | 31:16     |       | —     |       | _        | _        | _     |       | _    | _        |       | _        | _    | —      | _      | —        |        | 0000          |

| 0024                        | 3B13ELOG2        | 15:0      |       | —     |       | _        | _        | _     |       | _    | _        |       | _        | _    | —      | _      | GROU     | P<1:0> | 0000          |

| 8C28                        | SBT3ECON         | 31:16     | _     | _     | _     | —        | —        | —     | —     | ERRP | —        | _     | —        | —    | —      | —      | _        | —      | 0000          |

| 0020                        | SBISECON         | 15:0      | _     | _     | _     | —        | —        | —     | —     | —    | —        | _     | —        | —    | —      | —      | _        | —      | 0000          |

| 8C30                        | SBT3ECLRS        | 31:16     | —     | —     | _     | _        | —        |       | —     | —    | _        | _     |          | _    | _      | _      |          | —      | 0000          |

| 0000                        | OBIOLOLINO       | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —        | _     | —        | —    | —      | —      | —        | CLEAR  | 0000          |

| 8C38                        | SBT3ECLRM        | 31:16     | —     | —     | —     | —        | —        | —     | —     | —    | —        | _     | —        | —    | —      | —      | —        | —      | 0000          |

| 0000                        | OBTOLOLIUM       | 15:0      | —     | —     | —     | —        | —        | —     |       | —    | —        | —     | —        | —    | —      |        | —        | CLEAR  | 0000          |

| 8C40                        | SBT3REG0         | 31:16     |       |       |       |          |          |       | 1     | BA   | SE<21:6> |       |          |      |        |        | T        |        | xxxx          |

|                             |                  | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0 | >    |        | _      | _        | —      | xxxx          |

| 8C50                        | SBT3RD0          | 31:16     | —     | _     | _     | _        | _        |       | _     | _    |          |       |          | _    | —      | _      | _        | _      | XXXX          |

|                             |                  | 15:0      | _     | —     | _     | —        | —        | —     | —     | —    | —        | —     |          | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C58                        | SBT3WR0          | 31:16     |       | -     | _     | _        | —        | —     |       | —    | —        | _     | —        | —    |        |        | —        |        | xxxx          |

|                             |                  | 15:0      |       | -     | —     |          |          |       |       |      |          | —     | —        |      | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C60                        | SBT3REG1         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        |        |          |        | XXXX          |

|                             |                  | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0 | >    |        | _      | _        | _      | XXXX          |

| 8C70                        | SBT3RD1          | 31:16     |       | _     | _     | _        | —        | —     | _     | —    | —        | _     |          | _    | —      | —      | —        | —      | XXXX          |

|                             |                  | 15:0      | _     |       |       | _        |          | _     | _     |      | _        |       |          |      | GROUP3 | GROUP2 | GROUP1   | GROUP0 | XXXX          |

| 8C78                        | SBT3WR1          | 31:16     |       | _     |       | _        | _        |       | _     | _    |          |       |          | _    | —      | —      | —        | —      | XXXX          |

|                             |                  | 15:0      |       | —     | —     | —        | —        | —     | —     |      |          | —     | —        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 |               |

| 8C80                        | SBT3REG2         | 31:16     |       |       |       |          |          |       |       |      | SE<21:6> |       |          |      |        |        |          |        | XXXX          |

|                             |                  | 15:0      |       |       |       | ASE<5:0> |          |       | PRI   | _    |          |       | SIZE<4:0 |      |        | —      | -        | _      | XXXX          |

| 8C90                        | SBT3RD2          | 31:16     |       | _     |       | —        | —        |       | —     | —    |          | _     | -        | —    | -      | -      | -        | -      | XXXX          |

| <u> </u>                    |                  | 15:0      |       | _     |       | —        | —        |       | —     | —    |          |       | -        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 |               |

| 8C98                        | SBT3WR2          | 31:16     |       | _     |       | —        | —        |       | —     | —    |          | _     | -        | —    | -      | -      | -        | -      | XXXX          |

|                             |                  | 15:0      | _     | —     | —     |          | —        | —     |       | —    | —        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | XXXX          |

PIC32MK GP/MC Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

## TABLE 8-3: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interrupt Course(1)       | Interrupt Source <sup>(1)</sup> XC32 Vector Name IRQ Vector # Interrupt Bit Location |        |                  |          |          |             |              |           |  |  |

|---------------------------|--------------------------------------------------------------------------------------|--------|------------------|----------|----------|-------------|--------------|-----------|--|--|

| Interrupt Source."        | XC32 vector Name                                                                     | #      | Vector #         | Flag     | Enable   | Priority    | Sub-priority | Interrupt |  |  |

|                           | Highest                                                                              | Natura | I Order Priority |          |          |             |              |           |  |  |

| Core Timer Interrupt      | _CORE_TIMER_VECTOR                                                                   | 0      | OFF000<17:1>     | IFS0<0>  | IEC0<0>  | IPC0<4:2>   | IPC0<1:0>    | No        |  |  |

| Core Software Interrupt 0 | _CORE_SOFTWARE_0_VECTOR                                                              | 1      | OFF001<17:1>     | IFS0<1>  | IEC0<1>  | IPC0<12:10> | IPC0<9:8>    | No        |  |  |

| Core Software Interrupt 1 | _CORE_SOFTWARE_1_VECTOR                                                              | 2      | OFF002<17:1>     | IFS0<2>  | IEC0<2>  | IPC0<20:18> | IPC0<17:16>  | No        |  |  |

| External Interrupt 0      | _EXTERNAL_0_VECTOR                                                                   | 3      | OFF003<17:1>     | IFS0<3>  | IEC0<3>  | IPC0<28:26> | IPC0<25:24>  | No        |  |  |

| Timer1                    | _TIMER_1_VECTOR                                                                      | 4      | OFF004<17:1>     | IFS0<4>  | IEC0<4>  | IPC1<4:2>   | IPC1<1:0>    | No        |  |  |

| Input Capture 1 Error     | _INPUT_CAPTURE_1_ERROR_VECTOR                                                        | 5      | OFF005<17:1>     | IFS0<5>  | IEC0<5>  | IPC1<12:10> | IPC1<9:8>    | Yes       |  |  |

| Input Capture 1           | _INPUT_CAPTURE_1_VECTOR                                                              | 6      | OFF006<17:1>     | IFS0<6>  | IEC0<6>  | IPC1<20:18> | IPC1<17:16>  | Yes       |  |  |

| Output Compare 1          | _OUTPUT_COMPARE_1_VECTOR                                                             | 7      | OFF007<17:1>     | IFS0<7>  | IEC0<7>  | IPC1<28:26> | IPC1<25:24>  | No        |  |  |

| External Interrupt 1      | _EXTERNAL_1_VECTOR                                                                   | 8      | OFF008<17:1>     | IFS0<8>  | IEC0<8>  | IPC2<4:2>   | IPC2<1:0>    | No        |  |  |

| Timer2                    | _TIMER_2_VECTOR                                                                      | 9      | OFF009<17:1>     | IFS0<9>  | IEC0<9>  | IPC2<12:10> | IPC2<9:8>    | No        |  |  |

| Input Capture 2 Error     | _INPUT_CAPTURE_2_ERROR_VECTOR                                                        | 10     | OFF010<17:1>     | IFS0<10> | IEC0<10> | IPC2<20:18> | IPC2<17:16>  | Yes       |  |  |

| Input Capture 2           | _INPUT_CAPTURE_2_VECTOR                                                              | 11     | OFF011<17:1>     | IFS0<11> | IEC0<11> | IPC2<28:26> | IPC2<25:24>  | Yes       |  |  |

| Output Compare 2          | _OUTPUT_COMPARE_2_VECTOR                                                             | 12     | OFF012<17:1>     | IFS0<12> | IEC0<12> | IPC3<4:2>   | IPC3<1:0>    | No        |  |  |

| External Interrupt 2      | _EXTERNAL_2_VECTOR                                                                   | 13     | OFF013<17:1>     | IFS0<13> | IEC0<13> | IPC3<12:10> | IPC3<9:8>    | No        |  |  |

| Timer3                    | _TIMER_3_VECTOR                                                                      | 14     | OFF014<17:1>     | IFS0<14> | IEC0<14> | IPC3<20:18> | IPC3<17:16>  | No        |  |  |

| Input Capture 3 Error     | _INPUT_CAPTURE_3_ERROR_VECTOR                                                        | 15     | OFF015<17:1>     | IFS0<15> | IEC0<15> | IPC3<28:26> | IPC3<25:24>  | Yes       |  |  |

| Input Capture 3           | _INPUT_CAPTURE_3_VECTOR                                                              | 16     | OFF016<17:1>     | IFS0<16> | IEC0<16> | IPC4<4:2>   | IPC4<1:0>    | Yes       |  |  |

| Output Compare 3          | _OUTPUT_COMPARE_3_VECTOR                                                             | 17     | OFF017<17:1>     | IFS0<17> | IEC0<17> | IPC4<12:10> | IPC4<9:8>    | No        |  |  |

| External Interrupt 3      | _EXTERNAL_3_VECTOR                                                                   | 18     | OFF018<17:1>     | IFS0<18> | IEC0<18> | IPC4<20:18> | IPC4<17:16>  | No        |  |  |

| Timer4                    | _TIMER_4_VECTOR                                                                      | 19     | OFF019<17:1>     | IFS0<19> | IEC0<19> | IPC4<28:26> | IPC4<25:24>  | No        |  |  |

| Input Capture 4 Error     | _INPUT_CAPTURE_4_ERROR_VECTOR                                                        | 20     | OFF020<17:1>     | IFS0<20> | IEC0<20> | IPC5<4:2>   | IPC5<1:0>    | Yes       |  |  |

| Input Capture 4           | _INPUT_CAPTURE_4_VECTOR                                                              | 21     | OFF021<17:1>     | IFS0<21> | IEC0<21> | IPC5<12:10> | IPC5<9:8>    | Yes       |  |  |

| Output Compare 4          | _OUTPUT_COMPARE_4_VECTOR                                                             | 22     | OFF022<17:1>     | IFS0<22> | IEC0<22> | IPC5<20:18> | IPC5<17:16>  | No        |  |  |

| External Interrupt 4      | _EXTERNAL_4_VECTOR                                                                   | 23     | OFF023<17:1>     | IFS0<23> | IEC0<23> | IPC5<28:26> | IPC5<25:24>  | No        |  |  |

| Timer5                    | _TIMER_5_VECTOR                                                                      | 24     | OFF024<17:1>     | IFS0<24> | IEC0<24> | IPC6<4:2>   | IPC6<1:0>    | No        |  |  |

| Input Capture 5 Error     | _INPUT_CAPTURE_5_ERROR_VECTOR                                                        | 25     | OFF025<17:1>     | IFS0<25> | IEC0<25> | IPC6<12:10> | IPC6<9:8>    | Yes       |  |  |

| Input Capture 5           | _INPUT_CAPTURE_5_VECTOR                                                              | 26     | OFF026<17:1>     | IFS0<26> | IEC0<26> | IPC6<20:18> | IPC6<17:16>  | Yes       |  |  |

| Output Compare 5          | _OUTPUT_COMPARE_5_VECTOR                                                             | 27     | OFF027<17:1>     | IFS0<27> | IEC0<27> | IPC6<28:26> | IPC6<25:24>  | No        |  |  |

| Reserved                  | —                                                                                    | 28     | —                | —        | —        | —           | —            | _         |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MK General Purpose (GP) Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

**3:** This interrupt source is not available on 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2          | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|----------------------|-------------------|----------------------------|----------------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0                      | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | PRI7SS            | <3:0> <sup>(1)</sup> |                   |                            | PRI6SS<3:0> <sup>(1)</sup> |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0                      | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup> |                   |                            | PRI4SS<3:0> <sup>(1)</sup> |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0                      | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | PRI3S             | S<3:0>               |                   | PRI2SS<3:0> <sup>(1)</sup> |                            |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | U-0                        | U-0                        | U-0              | R/W-0            |  |  |  |

| 7:0          |                   | PRI1SS            | <3:0> <sup>(1)</sup> |                   | _                          |                            | _                | SS0              |  |  |  |

## REGISTER 8-2: PRISS: PRIORITY SHADOW SELECT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-28 PRI7SS<3:0>: Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

|       |      | 1111 = Reserved                                                             |

|-------|------|-----------------------------------------------------------------------------|

|       |      | •                                                                           |

|       |      | •                                                                           |

|       |      | 0010 = Reserved                                                             |

|       |      | 0001 = Interrupt with a priority level of 7 uses Shadow Set 1               |

|       |      | 0000 = Interrupt with a priority level of 7 uses Shadow Set 0 (default)     |

| bit 2 | 7-24 | PRI6SS<3:0>: Interrupt with Priority Level 6 Shadow Set bits <sup>(1)</sup> |

|       |      | 1111 = Reserved                                                             |

|       |      | •                                                                           |

|       |      |                                                                             |

|       |      | 0010 = Reserved                                                             |

|       |      | 0001 = Interrupt with a priority level of 6 uses Shadow Set 1               |

|       |      | 0000 = Interrupt with a priority level of 6 uses Shadow Set 0 (default)     |

| bit 2 | 3-20 | PRI5SS<3:0>: Interrupt with Priority Level 5 Shadow Set bits <sup>(1)</sup> |

|       |      | 1111 = Reserved                                                             |

|       |      | •                                                                           |

|       |      | •                                                                           |

|       |      | 0010 = Reserved                                                             |

|       |      | 0001 = Interrupt with a priority level of 5 uses Shadow Set 1               |

|       |      | 0000 = Interrupt with a priority level of 5 uses Shadow Set 0 (default)     |

| bit 1 | 9-16 | PRI4SS<3:0>: Interrupt with Priority Level 4 Shadow Set bits <sup>(1)</sup> |

|       |      | 1111 = Reserved                                                             |

|       |      |                                                                             |

|       |      | •                                                                           |

|       |      | •<br>0010 = Reserved                                                        |

|       |      | 0001 = Interrupt with a priority level of 4 uses Shadow Set 1               |

|       |      | 0000 = Interrupt with a priority level of 4 uses Shadow Set 1 (default)     |

|       |      |                                                                             |

|       |      |                                                                             |

## **Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

#### **TABLE 9-2: OSCILLATOR CONFIGURATION REGISTER MAP (CONTINUED)**

| ess                         |                       |           |       |       |       |       |          |       |            |         | Bits    |      |         |         |           |         |          |        | (                         |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|----------|-------|------------|---------|---------|------|---------|---------|-----------|---------|----------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11    | 26/10 | 25/9       | 24/8    | 23/7    | 22/6 | 21/5    | 20/4    | 19/3      | 18/2    | 17/1     | 16/0   | All Resets <sup>(1)</sup> |

| 1340                        | PB5DIV                | 31:16     | _     | _     | _     | _     | —        | _     | —          | —       | —       | —    | -       | _       | _         | —       | _        | _      | 0000                      |

| 1340                        | FB3DIV                | 15:0      | ON    |       | _     | _     | PBDIVRDY | _     | _          | —       | —       |      |         |         | PBDIV<6:0 | >       |          |        | 8801                      |

| 1350                        | PB6DIV <sup>(2)</sup> | 31:16     | _     | Ι     | _     | _     | —        | _     | _          | _       | —       | _    | —       | _       | _         | —       | _        | _      | 0000                      |

| 1330                        | PB0DIV-               | 15:0      | ON    |       | _     | _     | PBDIVRDY | _     | _          | —       | —       |      |         |         | PBDIV<6:0 | >       |          |        | 8801                      |

| 1360                        | PB7DIV <sup>(3)</sup> | 31:16     | _     | Ι     | _     | _     | —        | _     | _          | _       | —       | _    | —       | _       | _         | —       | _        | _      | 0000                      |

| 1300                        | FDIDIV                | 15:0      | ON    |       | _     | _     | PBDIVRDY | _     | _          | —       | —       |      |         |         | PBDIV<6:0 | >       |          |        | 8800                      |

| 1200                        | SLEWCON               | 31:16     | _     | Ι     | _     | _     | —        | _     | _          | _       | —       | _    | —       | _       |           | SYSD    | 01V<3:0> |        | 0000                      |

| 1300                        | SLEWCON .             | 15:0      | —     | —     | —     | —     | —        | Ś     | SLWDIV<2:0 | >       | —       | —    | —       | —       | —         | UPEN    | DNEN     | BUSY   | 0000                      |

| 1390                        | CLKSTAT               | 31:16     | _     | _     | _     | _     | _        | _     | _          | —       | —       | _    | —       | _       | _         | _       | _        | _      | 0000                      |

| 1390                        | GENGIAI               | 15:0      | _     | _     | _     | _     | —        |       | —          | UPLLRDY | SPLLRDY | _    | LPRCRDY | SOSCRDY | _         | POSCRDY | _        | FRCRDY | 0000                      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

Reset values are dependent on the DEVCFGx Configuration bits and the type of reset. Refer to Table 36-16 in **36.0** "Electrical Characteristics" for PBCLK6 frequency limitations. 2:

3: The PB7DIV register is read-only.

#### REGISTER 9-4: UPLLCON: USB PLL CONTROL REGISTER

- bit 22-16 PLLMULT<6:0>: System PLL Multiplier Output Clock Divider bits

- 1111111 = Multiply by 128 1111110 = Multiply by 127 1111101 = Multiply by 126 . 0000010 = Multiply by 3 0000001 = Multiply by 2 0000000 = Multiply by 1

The default setting is specified by the FPLLMULT<6:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "**Special Features**" for information.

- bit 15-11 Unimplemented: Read as '0'

- bit 10-8 PLLIDIV<2:0>: System PLL Input Clock Divider bits

- 111 = Divide by 8 110 = Divide by 7 101 = Divide by 6 100 = Divide by 5

- 011 = Divide by 4

- 010 = Divide by 3

- 001 = Divide by 2

- 000 = Divide by 1

The default setting is specified by the FPLLIDIV<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "**Special Features**" for information. If the PLLICLK is set for FRC, this setting is ignored by the PLL and the divider is set to Divide-by-1.

- bit 7-3 Unimplemented: Read as '0'

- bit 2-0 PLLRANGE<2:0>: System PLL Frequency Range Selection bits

- 111 = Reserved

- 110 = 54-90 MHz

- 101 = 34-68 MHz

- 100 = 21-42 MHz

- 011 = 13-26 MHz

- 010 = 8-16 MHz

- 001 = 5-10 MHz

- 000 = Bypass

Use the highest filter range that covers the input freq to the VCO multiplier block that corresponds to the PLLIDIV output freq to minimize PLL system jitter (see Figure 9-1). For example, Crystal = 20 MHz, PLLIDIV<2:0> = 0b1; therefore, the filter input frequency is equal to 10 MHz and UPLLRANGE<2:0> = 0b010. The default setting is specified by the FPLLRNG<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "**Special Features**" for information.

| Note | 1: | Writes to this register require an unlock sequence. Refer to <b>Section 42. "Oscillators with Enhanced PLL"</b> (DS60001250) in the <i>"PIC32 Family Reference Manual"</i> for details.                                                                                                                                                                                                                                         |

|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 2: | Writes to this register are not allowed if the UPLL is selected as a clock source (COSC<2:0> = 001).                                                                                                                                                                                                                                                                                                                            |

|      | 3: | While the PLL is active, and if updating the PLL bits in the OSCCON register at run-time, the user application must remain within the following limits at all times for all nodes in the PLL clock tree. Therefore, the order in which the PLL values may be modified, (i.e., PLLODIV, PLLMULT, PLLODIV) becomes important. Failure to maintain PLL nodes within min/max ranges may result in unstable PLL and system behavior. |

|      |    | <ul> <li>Output and input to PLLIDIV block (i.e., FPLLI) 5 MHz to 64 MHz (min/max at all times)</li> </ul>                                                                                                                                                                                                                                                                                                                      |

|      |    | <ul> <li>VCO output, (i.e., FVCO) 350 MHz to 700 MHz (min/max at all times)</li> </ul>                                                                                                                                                                                                                                                                                                                                          |

|      |    | • Output of PLLODIV (i.e., EPLL) 10 MHz to 120 MHz (min/max at all times)                                                                                                                                                                                                                                                                                                                                                       |

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24             | _                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 22:16             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16             | _                 |                   | _                 | -                 | —                 | —                 | —                | —                |  |

| 45.0              | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8 CHDPTR<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0               | 7:0 CHDPTR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |

## **REGISTER 11-15: DCHxDPTR: DMA CHANNEL x DESTINATION POINTER REGISTER**

## Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

|              |                   |                   |                   | (// // // // // // // // // // // // // |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | U-0               | U-0               | U-0               | U-0                                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 51.24        | —                 | —                 | —                 | —                                       |                   | —                 | -                | _                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0                                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                                       | -                 | —                 | —                | _                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0                                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 | —                 | —                                       | —                 | —                 | -                | —                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0                                   | R/W-0             | U-0               | U-0              | R/W-0            |  |  |  |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL                                 | LSDEV             |                   |                  | UASUSPND         |  |  |  |

## REGISTER 12-20: UxCNFG1: USB CONFIGURATION 1 REGISTER ('x' = 1 AND 2)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB <u>OE</u> Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

#### bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3 **LSDEV:** Low-Speed Device Enable bit

- 1 = USB module to operate in Low-Speed Device mode

- 0 = USB module to operate in OTG, Host, or Full-Speed Device mode

#### bit 2-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (UxPWRC<1>) in Register 12-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (UxPWRC<1>) to suspend the module, including the USB 48 MHz clock

## 13.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

## 13.3 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 13.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

## 13.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART, SPI, and CAN), general purpose timer clock inputs, timer-related peripherals (input capture and output compare), interrupt-on-change inputs, and reference clocks (input and output).

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

## 13.3.3 CONTROLLING PPS

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 13.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 13-1, are used to configure peripheral input mapping (see Register 13-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 13-1.

Figure 13-2 illustrates the remappable pin selection for the U1RX input.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | —                 | _                 | _                 | _                 |                   | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 | _                 | _                 | _                 | BRG<19:16>        |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | BRG<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | BRG<              | 7:0>              |                   |                  |                  |  |

## REGISTER 22-5: UxBRG: UARTx BAUD RATE GENERATOR REGISTER

## Legend:

| =ogona.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-20 Unimplemented: Read as '0'

bit 19-0 BRG<19:0>: Baud Rate Generator Divisor bits

Note: The UxBRG register cannot be changed while UARTx is enabled (ON bit (UxMODE<15>) = 1)).

## TABLE 22-3: UART BAUD RATE CALCULATIONS

| UART Baud Rate With                                            | UxBRG Equals                                                |  |  |  |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| BRGH = 0                                                       | UxBRG = ((CLKSEL Frequency / (16 * Desired Baud Rate)) – 1) |  |  |  |  |  |

| BRGH = 1                                                       | UxBRG = ((CLKSEL Frequency / (4 * Desired Baud Rate)) – 1)  |  |  |  |  |  |

| Note: UADT4 and UADT9 an DD0UK9, UADT9 through UADT9 an DD0UK9 |                                                             |  |  |  |  |  |

**Note:** UART1 and UART2 on PBCLK2; UART3 through UART6 on PBCLK3.

## 23.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable.

The following are key features of the PMP module:

- · 8-bit or 16-bit data interface

- · 14/22 address lines with two Chip Selects

- 15/23 address lines with one Chip Select

- 16/24 address lines without Chip Select

- · Address auto-increment/auto-decrement

- Selectable address bus width for resource limited  $\ensuremath{\text{I/O}}$

- Individual read and write strobes or read/write strobe with enable strobe

- Partially multiplexed address/data mode (eight bits of address) with an address latch strobe

- Fully multiplexed address/data mode (16 bits of address) with address latch high and low strobes

- Programmable wait states

- · Programmable polarity on selected control signals

- · Interrupt on cycle end, busy flag for polling

- · Persistent Interrupt capability for DMA access

- Little and Big-Endian Compatible addressing styles

- Extended address mode with addresses up to 24

bits

- Dual (4) word buffer mode with separate read and write registers.

- Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

- Freeze option for in-circuit debugging

| Note: | On 64-pin devices, data pins PMD<15:8> |

|-------|----------------------------------------|

|       | and PMA<23:16> are not available.      |

# TABLE 23-1:PMP SUPPORTED<br/>CONFIGURATIONS

| Pins       | Alternate PMP<br>Pin Functions           | 100-pin<br>Devices | 64-pin<br>Devices |

|------------|------------------------------------------|--------------------|-------------------|

| PMD<7:0>   | Multiplexed<br>PMA<7:0> and<br>PMA<15:8> | х                  | х                 |

| PMD<15:8>  | Multiplexed<br>PMA<7:0> and<br>PMA<15:8> | х                  | —                 |

| PMA<0>     | PMALL                                    | Х                  | Х                 |

| PMA<1>     | PMALH                                    | Х                  | Х                 |

| PMA<13:2>  | —                                        | Х                  | Х                 |

| PMA<14>    | PMCS1 or<br>PMCS                         | х                  | х                 |

| PMA<15>    | PMCS2                                    | Х                  | Х                 |

| PMA<21:16> | —                                        | Х                  | —                 |

| PMA<22>    | PMCS1A                                   | Х                  | —                 |

| PMA<23>    | PMCS2A                                   | Х                  | —                 |

| PMRD       | PMWR                                     | Х                  | Х                 |

| PMWR       | PMENB                                    | Х                  | Х                 |

#### ADRMUX<1:0> bits:

- 11 = All 16 bits of address are multiplexed with the 16 bits of data (PMA<15:0>/PMD<15:0>) using two phases.

- 10 = All 16 bits of address are multiplexed with the lower 8 bits of data (PMA<15:8>/PMA<7:0>/ PMD<7:0>) using three phases

- 01 = Lower 8 bits of address are multiplexed with lower 8 bits of data (PMA<7:0>/PMD<7:0>)

- 00 = Address and data pins are not multiplexed

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|

| 31:24        | R/W-0                     | R/W-0            |  |

| 51.24        | ADCSEL<1:0>       |                   |                   | CONCLKDIV<5:0>    |                   |                   |                           |                  |  |

| 22:16        | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |

| 23:16        | DIGEN7            | —                 | DIGEN5            | DIGEN4            | DIGEN3            | DIGEN2            | DIGEN1                    | DIGEN0           |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0                     | R-0, HS, HC      |  |

| 15.0         | V                 | VREFSEL<2:0>      |                   |                   | UPDIEN            | UPDRDY            | SAMP <sup>(1,2,3,4)</sup> | RQCNVRT          |  |

| 7:0          | R/W-0             | R-0, HS, HC       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |

| 7:0          | GLSWTRG           | GSWTRG            |                   |                   | ADINS             | SEL<5:0>          |                           |                  |  |

#### REGISTER 25-3: ADCCON3: ADC CONTROL REGISTER 3

| Legend:           | HC = Hardware Set | HS = Hardware Cleared              |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-30 ADCSEL<1:0>: Analog-to-Digital Clock Source (TCLK) bits

- 11 = SYSCLK 10 = REFCLK3

- 01 = FRC

- 00 = PBCLK5

- bit 29-24 CONCLKDIV<5:0>: Analog-to-Digital Control Clock (TQ) Divider bits

- 111111 = 126 \* TCLK = TQ . . . 000011 = 6 \* TCLK = TQ 000010 = 4 \* TCLK = TQ

- 000001 = 2 \* TCLK = TQ

- 000000 = TCLK = TQ

- bit 23 **DIGEN7:** Shared ADC (ADC7) Digital Enable bit 1 = ADC7 is digital enabled

- 0 = ADC7 is digital disabled

- bit 22 Unimplemented: Read as '0'

- bit 21 **DIGEN5:** ADC5 Digital Enable bit 1 = ADC5 is digital enabled (required for active operation) 0 = ADC5 is digital disabled (power-saving mode)

- bit 20 **DIGEN4:** ADC4 Digital Enable bit 1 = ADC4 is digital enabled (required for active operation) 0 = ADC4 is digital disabled (power-saving mode)

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | ADCCNTB<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | ADCCNTB<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | ADCCNTB<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | ADCCN             | TB<7:0>           |                   |                  |                  |  |  |

#### REGISTER 25-29: ADCCNTB: ADC CHANNEL SAMPLE COUNT BASE ADDRESS REGISTER

## Legend:

| Legena.           |                                   |                      |                                    |  |  |

|-------------------|-----------------------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

#### bit 31-0 ADCCNTB<31:0>: ADC Channel Count Base Address bits

SRAM address for the DMA interface at which to save the first class channel buffer A sample count values into the System RAM. If First Class Channel 'x' (where 'x' = 0-5), is ready with a new available sample data, and the DMA interface is currently saving data for Channel 'x' to RAM Buffer 'z' (where 'z' == 0 means Buffer A and 'z' == 1 means Buffer B, with 'z' depending on 'x'), the DMA interface will increment (+1) the 1 byte count value stored at System RAM address (ADCCNTB + 2 \* x + z). ADCCNTB works in conjunction with ADCDMAB. The DMA interface will use ADCCNTB to save the buffer sample counts only if the DMACEN bit in the ADCDSTAT register is set to '1'.

#### REGISTER 25-30: ADCDMAB: ADC CHANNEL SAMPLE COUNT BASE ADDRESS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24     | ADCDMAB<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10     | ADCDMAB<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0      | ADCDMAB<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       |                   |                   |                   | ADCDM             | AB<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-0 ADCDMAB<31:0>: DMA Interface Base Address bits

Address at which to save first class channels data into the System RAM. If First Class Channel 'x' (where 'x' = 0-5), is ready with a new available sample data, and the DMA interface is currently saving data for Channel 'x' to RAM Buffer 'z' (where 'z' == 0 means Buffer A and 'z' == 1 means Buffer B, 'z' depending on 'x'), and the current DMA x-counter value is 'y' (with 'y' depending on 'x'), the DMA interface will store the 2-byte output data value at System RAM address (ADCDMAB + (2 \* x + z) \* 2(DMABL+1) + 2 \* y. Also, if the DMACEN bit in the ADCDSTAT register is set to '1', the DMA interface will store without delay the value 'y' itself at the System RAM address (ADCCNTB + 2 \* x + z).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | FLTEN11           | MSEL11<1:0>       |                   | FSEL11<4:0>       |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN10           | MSEL10<1:0>       |                   | FSEL10<4:0>       |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN9 MSEL9<1:0> |                   |                   | F                 | SEL9<4:0>         |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | FLTEN8            | MSEL              | MSEL8<1:0>        |                   | FSEL8<4:0>        |                   |                  |                  |  |

## **REGISTER 26-12:** CxFLTCON2: CAN FILTER CONTROL REGISTER 2 ('x' = 1-4)

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | FLTEN11: Filter 11 Enable bit                                            |

|-----------|--------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                    |

|           | 0 = Filter is disabled                                                   |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                                  |

|           | 11 = Reserved                                                            |

|           | 10 = Acceptance Mask 2 is selected                                       |

|           | 01 = Acceptance Mask 1 is selected                                       |

|           | 00 = Acceptance Mask 0 is selected                                       |

| bit 28-24 | FSEL11<4:0>: FIFO Selection bits                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30              |

|           | •                                                                        |

|           | •                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0               |

| bit 23    | FLTEN10: Filter 10 Enable bit                                            |

|           | 1 = Filter is enabled                                                    |

|           | 0 = Filter is disabled                                                   |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                                  |

|           | 11 = Reserved                                                            |

|           | 10 = Acceptance Mask 2 is selected<br>01 = Acceptance Mask 1 is selected |

|           | 00 = Acceptance Mask 0 is selected                                       |

| bit 20-16 | FSEL10<4:0>: FIFO Selection bits                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30              |

|           | •                                                                        |

|           | •                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1               |

|           |                                                                          |

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | U-0                          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24     | —                            | _                 | —                 | _                 | —                 | _                 | —                | —                |  |

| 23:16     | U-0                          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10     | —                            | _                 | —                 | _                 | —                 | _                 | —                | _                |  |

| 15:8      | R/W-0                        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6      | SEVTCMP<15:8> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0                        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       |                              |                   |                   | SEVTCM            | IP<7:0>(1)        |                   |                  |                  |  |

#### REGISTER 31-3: SEVTCMP: PWM PRIMARY SPECIAL EVENT COMPARE REGISTER

## Γ.

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

SEVTCMP<15:0>: Special Event Compare Count Value bits<sup>(1)</sup> bit 15-0

> The special event trigger allows analog-to-digital conversions to be synchronized to the master PWM time base. The analog-to-digital sampling and conversion time may be programmed to occur at any point within the PWM period.

Note 1: Minimum LSb = 1 / FSYSCLK.

| Bit Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     | _                          | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16     | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                          | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8      | R-0                        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15.6      | PMTMR<15:8> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R-0                        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0       |                            |                   |                   | PMTMR             | <7:0>(1)          |                   |                  |                  |

#### REGISTER 31-4 PMTMR· PRIMARY MASTER TIME BASE TIMER REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

Unimplemented: Read as '0' bit 31-16

PMTMR<15:0>: Primary Master Time Base Timer Value bits<sup>(1)</sup> bit 15-0 This timer increments with each PWM clock until the PTPER value is reached.

Note 1: LSb = 1 / FSYSCLK.

# PIC32MK GP/MC Family

| Bit Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |  |

|-----------|--------------------------------|-------------------|-------------------|-------------------|---------------------|----------------------|----------------------|----------------------|--|

| 31:24     | U-0                            | U-0               | U-0               | U-0               | U-0                 | U-0                  | U-0                  | U-0                  |  |

| 51.24     | —                              | _                 |                   | _                 | —                   | _                    | _                    | _                    |  |

| 23:16     | U-0                            | U-0               | U-0               | U-0               | U-0                 | U-0                  | U-0                  | U-0                  |  |

| 23.10     | —                              | —                 |                   | —                 | —                   | —                    | —                    | —                    |  |

| 15:8      | R/W-0                          | R/W-1             | R/W-0             | R/W-0             | R/W-0               | R/W-0                | R/W-0                | R/W-0                |  |

| 15.6      | STPER<15:8> <sup>(1,2,4)</sup> |                   |                   |                   |                     |                      |                      |                      |  |

| 7.0       | R/W-0                          | R/W-0             | R/W-1             | R/W-0             | R/W-0               | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> |  |

| 7:0       |                                |                   |                   | STPER<            | 7:0> <b>(1,2,4)</b> |                      |                      |                      |  |

## REGISTER 31-6: STPER: SECONDARY MASTER TIME BASE PERIOD REGISTER

## Legend:

| Legenu    | •         |                  |                          |                    |

|-----------|-----------|------------------|--------------------------|--------------------|

| R = Rea   | dable bit | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Valu | ue at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 STPER<15:0>: Secondary Master Time Base Period Value bits<sup>(1,2,4)</sup>

**Note 1:** Minimum LSb = 1/FSYSCLK.

- **2:** Minimum value is 0x0008.

- **3:** If a period value lesser than 0x0008 is chosen, the internal hardware forcefully sets the period to a minimum value of 0x0008.

- **4:** STPER = (FSYSCLK/(FPWM \* PCLKDIV<2:0> bits (PTCON<6:4>)). FPWM = User-desired PWM Frequency.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                   | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------------------------------------|------------------|

| 31:24     | U-0                                                | U-0              |

| 31.24     | —                 | _                 | —                 | _                 | —                 | _                 | —                                                  | —                |

| 23:16     | U-0                                                | U-0              |

| 23.10     | —                 | —                 | —                 | -                 | —                 | —                 | —                                                  | —                |

| 15:8      | R/W-0                                              | R/W-0            |

| 15.0      |                   | SSEVTCMP<15:8>    |                   |                   |                   |                   | - — — —<br>0 U-0 U-0<br>- — — —<br>(-0 R/W-0 R/W-0 |                  |

| 7.0       | R/W-0                                              | R/W-0            |

| 7:0       |                   |                   |                   | SSEVTC            | MP<7:0>           |                   |                                                    |                  |

#### REGISTER 31-7: SSEVTCMP: PWM SECONDARY SPECIAL EVENT COMPARE REGISTER

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 SSEVTCMP<15:0>: Secondary Special Event Compare Value bits

The secondary special event trigger allows analog-to-digital conversions to be synchronized to the secondary master PWM time base. The analog-to-digital sampling and conversion time may be programmed to occur at any point within the PWM period.

## REGISTER 31-12: IOCONX: PWMX I/O CONTROL REGISTER 'x' ('x' = 1 THROUGH 12) (CONTINUED)

bit 22-19 **FLTSRC<3:0>:** Fault Control Signal Source Select bits for PWM Generator 'x'<sup>(2,4)</sup> These bits specify the Fault control source.

1111 **= FLT15**

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Comparator 5

- 1011 = Comparator 4

- 1010 =Comparator 3