Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | CANbus, IrDA, LINbus, PMP, QEI, SPI, UART/USART, USB OTG                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, Motor Control PWM, WDT       |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                      |

| Data Converters            | A/D 27x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512mcf064-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# REGISTER 6-1: EECON: EEPROM CONTROL REGISTER (CONTINUED)

bit 5-4 **ERR<1:0>:** Data EEPROM Sequence Error Status bits

- 11 = A BOR event has occurred

- 10 = An attempted execution of a read or write operation with an invalid write OR command with a misaligned address (EEADDR<1:0> ≠ 00)

- 01 = A Bulk or Page Erase or a Word Program verify error has occurred

00 = No error condition

These bits can be cleared by software, or as the result of the successful execution of the next operation, or when the ON bit = 0. These bits may also be set by software (when the RW bit = 0) without affecting the operation of the module.

#### bit 3 ILW: Data EEPROM Imminent Long Write Status bit

- 1 = The next write to the EEPROM address (held in the EEADDR register) will require more time (~ 20 ms) than usual

- 0 = The next write to the EEPROM address (held in the EEADDR register) will be a normal write cycle

This bit can be cleared by software, or as the result of a write to the EEADDR register. This bit is set by hardware after a write command.

### bit 2-0 CMD<2:0>: Data EEPROM Command Selection bits<sup>(1)</sup>

These bits are cleared only on a POR event.

111 = Reserved

- •

- •

- •

100 = Configuration register Write command (WREN bit must be set)<sup>(2)</sup>

011 = Data EEPROM memory Bulk Erase command (WREN bit must be set)

010 = Data EEPROM memory Page Erase command (WREN bit must be set)

001 = Word Write command (WREN bit must be set)

000 = Word Read command (WREN bit must be clear)

- **Note 1:** This bit (or bits) cannot be modified when the RW bit = 1.

- The Configuration Write command (CMD<2:0> = 100) must be executed after any power-up before the Data EEPROM is ready for use. Refer to Example 58-1 "Data EEPROM Initialization Code" in Section 58. "Data EEPROM" (DS60001341) for details.

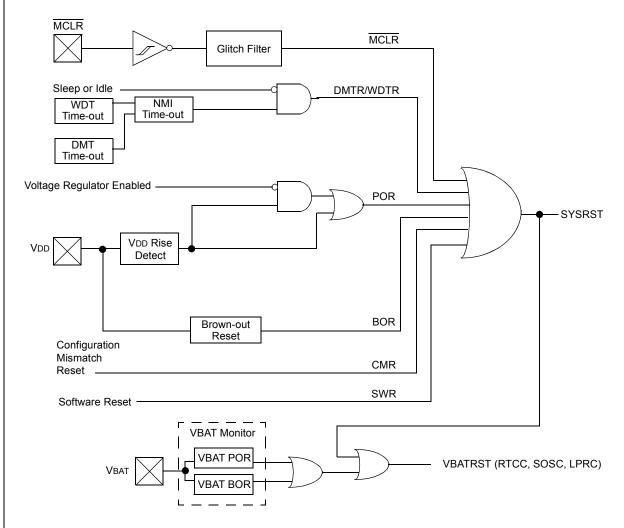

#### 7.0 RESETS

FIGURE 7-1:

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Resets" (DS60001118), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

SYSTEM RESET BLOCK DIAGRAM

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The device Reset sources are as follows:

- · Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

- Deadman Timer Reset (DMTR)

A simplified block diagram of the Reset module is illustrated in Figure 7-1.

# TABLE 8-3: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name              | IRQ | Vector #     | Interrupt Bit Location |          |              |              | Persistent |

|---------------------------------|-------------------------------|-----|--------------|------------------------|----------|--------------|--------------|------------|

| Interrupt Source."              | AC32 vector Name              | #   | vector #     | Flag                   | Enable   | Priority     | Sub-priority | Interrupt  |

| SPI2 Fault                      | _SPI2_FAULT_VECTOR            | 53  | OFF053<17:1> | IFS1<21>               | IEC1<21> | IPC13<12:10> | IPC13<9:8>   | Yes        |

| SPI2 Receive Done               | _SPI2_RX_VECTOR               | 54  | OFF054<17:1> | IFS1<22>               | IEC1<22> | IPC13<20:18> | IPC13<17:16> | Yes        |

| SPI2 Transfer Done              | _SPI2_TX_VECTOR               | 55  | OFF055<17:1> | IFS1<23>               | IEC1<23> | IPC13<28:26> | IPC13<25:24> | Yes        |

| UART2 Fault                     | _UART2_FAULT_VECTOR           | 56  | OFF056<17:1> | IFS1<24>               | IEC1<24> | IPC14<4:2>   | IPC14<1:0>   | Yes        |

| UART2 Receive Done              | _UART2_RX_VECTOR              | 57  | OFF057<17:1> | IFS1<25>               | IEC1<25> | IPC14<12:10> | IPC14<9:8>   | Yes        |

| UART2 Transfer Done             | _UART2_TX_VECTOR              | 58  | OFF058<17:1> | IFS1<26>               | IEC1<26> | IPC14<20:18> | IPC14<17:16> | Yes        |

| Reserved                        | —                             | 59  | —            | _                      | —        | —            | —            | —          |

| Reserved                        | —                             | 60  | —            | _                      | —        | —            | —            | _          |

| Reserved                        | -                             | 61  | —            |                        | _        | —            | —            | _          |

| UART3 Fault                     | _UART3_FAULT_VECTOR           | 62  | OFF062<17:1> | IFS1<30>               | IEC1<30> | IPC15<20:18> | IPC15<17:16> | Yes        |

| UART3 Receive Done              | _UART3_RX_VECTOR              | 63  | OFF063<17:1> | IFS1<31>               | IEC1<31> | IPC15<28:26> | IPC15<25:24> | Yes        |

| UART3 Transfer Done             | _UART3_TX_VECTOR              | 64  | OFF064<17:1> | IFS2<0>                | IEC2<0>  | IPC16<4:2>   | IPC16<1:0>   | Yes        |

| UART4 Fault                     | _UART4_FAULT_VECTOR           | 65  | OFF065<17:1> | IFS2<1>                | IEC2<1>  | IPC16<12:10> | IPC16<9:8>   | Yes        |

| UART4 Receive Done              | _UART4_RX_VECTOR              | 66  | OFF066<17:1> | IFS2<2>                | IEC2<2>  | IPC16<20:18> | IPC16<17:16> | Yes        |

| UART4 Transfer Done             | _UART4_TX_VECTOR              | 67  | OFF067<17:1> | IFS2<3>                | IEC2<3>  | IPC16<28:26> | IPC16<25:24> | Yes        |

| UART5 Fault                     | _UART5_FAULT_VECTOR           | 68  | OFF068<17:1> | IFS2<4>                | IEC2<4>  | IPC17<4:2>   | IPC17<1:0>   | Yes        |

| UART5 Receive Done              | _UART5_RX_VECTOR              | 69  | OFF069<17:1> | IFS2<5>                | IEC2<5>  | IPC17<12:10> | IPC17<9:8>   | Yes        |

| UART5 Transfer Done             | _UART5_TX_VECTOR              | 70  | OFF070<17:1> | IFS2<6>                | IEC2<6>  | IPC17<20:18> | IPC17<17:16> | Yes        |

| CTMU Interrupt                  | _CTMU_VECTOR                  | 71  | OFF071<17:1> | IFS2<7>                | IEC2<7>  | IPC17<28:26> | IPC17<25:24> | Yes        |

| DMA Channel 0                   | _DMA0_VECTOR                  | 72  | OFF072<17:1> | IFS2<8>                | IEC2<8>  | IPC18<4:2>   | IPC18<1:0>   | Yes        |

| DMA Channel 1                   | _DMA1_VECTOR                  | 73  | OFF073<17:1> | IFS2<9>                | IEC2<9>  | IPC18<12:10> | IPC18<9:8>   | Yes        |

| DMA Channel 2                   | _DMA2_VECTOR                  | 74  | OFF074<17:1> | IFS2<10>               | IEC2<10> | IPC18<20:18> | IPC18<17:16> | Yes        |

| DMA Channel 3                   | _DMA3_VECTOR                  | 75  | OFF075<17:1> | IFS2<11>               | IEC2<11> | IPC18<28:26> | IPC18<25:24> | Yes        |

| Timer6                          | _TIMER_6_VECTOR               | 76  | OFF076<17:1> | IFS2<12>               | IEC2<12> | IPC19<4:2>   | IPC19<1:0>   | Yes        |

| Input Capture 6 Error           | _INPUT_CAPTURE_6_ERROR_VECTOR | 77  | OFF077<17:1> | IFS2<13>               | IEC2<13> | IPC19<12:10> | IPC19<9:8>   | Yes        |

| Input Capture 6                 | _INPUT_CAPTURE_6_VECTOR       | 78  | OFF078<17:1> | IFS2<14>               | IEC2<14> | IPC19<20:18> | IPC19<17:16> | Yes        |

| Output Compare 6                | _OUTPUT_COMPARE_6_VECTOR      | 79  | OFF079<17:1> | IFS2<15>               | IEC2<15> | IPC19<28:26> | IPC19<25:24> | Yes        |

| Timer7                          | _TIMER_7_VECTOR               | 80  | OFF080<17:1> | IFS2<16>               | IEC2<16> | IPC20<4:2>   | IPC20<1:0>   | Yes        |

| Input Capture 7 Error           | _INPUT_CAPTURE_7_ERROR_VECTOR | 81  | OFF081<17:1> | IFS2<17>               | IEC2<17> | IPC20<12:10> | IPC20<9:8>   | Yes        |

| Input Capture 7                 | _INPUT_CAPTURE_7_VECTOR       | 82  | OFF082<17:1> | IFS2<18>               | IEC2<18> | IPC20<20:18> | IPC20<17:16> | Yes        |

| Output Compare 7                | _OUTPUT_COMPARE_7_VECTOR      | 83  | OFF083<17:1> | IFS2<19>               | IEC2<19> | IPC20<28:26> | IPC20<25:24> | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MK General Purpose (GP) Family Features" for the list of available peripherals.

**2:** This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   | -                 | _                 | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | —                 | —                 | —                 |                   | SRIPL<2:0>       |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | SIRC              | Q<7:0>            |                   |                  |                  |

# REGISTER 8-3: INTSTAT: INTERRUPT STATUS REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

bit 10-8 **SRIPL<2:0>:** Requested Priority Level bits for Single Vector Mode bits 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 7-0 SIRQ<7:0>: Last Interrupt Request Serviced Status bits 1111111-00000000 = The last interrupt request number serviced by the CPU

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | 4 IPTMR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        |                   |                   |                   | IPTMF             | 23:16>            |                   |                  |                  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |

#### REGISTER 8-4: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 IPTMR<31:0>: Interrupt Proximity Timer Reload bits

Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.04        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        |                     |                   |                   | CHPIG             | N<7:0>            |                   |                  |                       |

| 23:16        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23.10        | -                   | -                 | —                 | -                 | —                 | —                 | -                | —                     |

| 45.0         | R/W-0               | U-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | _                 | CHIPGNEN          | —                 | CHPATLEN          | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | —                 | CHEDET            | CHPF             | RI<1:0>               |

# **REGISTER 11-7:** DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER ('x' = 0-7)

# Legend:

bit 7

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-24 CHPIGN<7:0>: Channel Register Data bits

Pattern Terminate mode:

Any byte matching these bits during a pattern match may be ignored during the pattern match determination when the CHPIGNEN bit is set. If a byte is read that is identical to this data byte, the pattern match logic will treat it as a "don't care" when the pattern matching logic is enabled and the CHPIGEN bit is set.

- bit 23-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 CHPIGNEN: Enable Pattern Ignore Byte bit

- 1 = Treat any byte that matches the CHPIGN<7:0> bits as a "don't care" when pattern matching is enabled

- 0 = Disable this feature

- bit 12 Unimplemented: Read as '0'

- bit 11 CHPATLEN: Pattern Length bit

- 1 = 2 byte length

- 0 = 1 byte length

- bit 10-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

- bit 5 CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | —                 | —                 | _                 | _                 | —                 | -                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   |                   |                   | CHSSIZ            | <15:8>            |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CHSSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

# REGISTER 11-12: DCHxSSIZ: DMA CHANNEL x SOURCE SIZE REGISTER

# Legend:

| R = Readable bit  | R = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|-----------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | _                 | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |

## REGISTER 11-13: DCHxDSIZ: DMA CHANNEL x DESTINATION SIZE REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | —                 | —                 | —                 | —                 |                   | —                 |                  | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | -                 | —                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | LSDEV             |                   |                  | UASUSPND         |

# REGISTER 12-20: UxCNFG1: USB CONFIGURATION 1 REGISTER ('x' = 1 AND 2)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB <u>OE</u> Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

#### bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3 **LSDEV:** Low-Speed Device Enable bit

- 1 = USB module to operate in Low-Speed Device mode

- 0 = USB module to operate in OTG, Host, or Full-Speed Device mode

#### bit 2-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (UxPWRC<1>) in Register 12-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (UxPWRC<1>) to suspend the module, including the USB 48 MHz clock

# TABLE 13-16: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                  |               |       |       |       |       |       |       |      | В    | its  |      |      |      |      |                |      |          |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|----------------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2           | 17/1 | 16/0     | All Resets |

| 1600                        | RPA0R            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      | _    | —<br>RPA0R<4:0 |      | <u> </u> | 000        |

| 1604                        | RPA1R            | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | _              | —    | —        | 000        |

| 1004                        |                  | 15:0          |       |       |       | —     |       | _     |      | _    |      |      |      |      |      | RPA1R<4:0      | >    |          | 000        |

| 1608                        | RPA2R            | 31:16         | _     |       |       | _     |       |       | _    | _    | _    |      | _    | _    | —    |                | _    | —        | 000        |

|                             |                  | 15:0<br>31:16 | _     |       |       |       |       |       |      |      |      |      |      | _    |      | RPA2R<4:0      | _    | _        | 000        |

| 160C                        | RPA3R            | 15:0          |       | _     |       | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | <br>RPA3R<4:0  |      |          | 000        |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —              | _    | _        | 000        |

| 1610                        | RPA4R            | 15:0          | _     | _     | _     | _     | _     |       | _    | _    | _    | _    | _    |      |      | RPA4R<4:0      | >    |          | 000        |

| 161C                        | RPA7R            | 31:16         |       | —     | —     | _     | _     |       |      | —    |      | _    | _    |      |      |                | _    | —        | 000        |

| 1010                        |                  | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    |      |      | RPA7R<4:0      | >    | -        | 000        |

| 1620                        | RPA8R            | 31:16         | _     |       | —     | —     | —     | —     |      | —    | —    | —    | —    |      | —    |                | —    | —        | 000        |

|                             |                  | 15:0          | _     |       |       | _     |       | _     | _    | _    | _    |      |      |      |      | RPA8R<4:0      |      | -        | 000        |

| 162C                        | RPA11R           | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      |      | <br>RPA11R<4:0 | -    | —        | 000        |

|                             |                  | 31:16         |       |       |       | _     |       | _     |      | _    | _    | _    | _    |      |      |                | _    | _        | 000        |

| 1630                        | RPA12R           | 15:0          | _     | _     | _     |       |       |       |      |      |      |      |      |      |      | RPA12R<4:0     | >    |          | 000        |

| 4000                        | DD4.44D          | 31:16         | _     | _     | _     | _     | _     |       | _    | _    | _    | _    | _    |      | —    |                |      | —        | 000        |

| 1638                        | RPA14R           | 15:0          |       | —     | —     | _     | _     |       |      | —    |      | _    | _    |      | F    | RPA14R<4:0     | >    |          | 000        |

| 163C                        | RPA15R           | 31:16         | _     | —     | —     | —     | —     | —     | _    | —    | -    | —    | —    | —    | —    |                | _    | —        | 000        |

| 1000                        |                  | 15:0          | _     |       |       | —     | —     | —     |      | —    | —    | —    | —    |      |      | RPA15R<4:(     |      |          | 000        |

| 1640                        | RPB0R            | 31:16<br>15:0 |       |       | -     |       |       |       |      |      |      |      |      | _    |      | <br>RPB0R<4:0  | —    | —        | 000        |

|                             |                  | 31:16         |       |       |       |       | _     |       |      |      |      |      |      |      |      | RPB0R<4:0      | >    | _        | 000        |

| 1644                        | RPB1R            | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      |      | <br>RPB1R<4:0  | >    |          | 000        |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _              | _    | _        | 000        |

| 1648                        | RPB2R            | 15:0          | _     | -     | —     | —     | _     | _     | _    | —    | _    | _    | _    |      |      | RPB2R<4:0      | >    |          | 000        |

| 164C                        | RPB3R            | 31:16         | _     | _     | —     | _     | —     | —     | _    | —    | _    | —    | —    | _    | —    | _              | _    | —        | 000        |

| 1040                        | IN DOIN          | 15:0          |       |       |       | —     | —     | —     |      | —    | _    | —    | —    |      |      | RPB3R<4:0      | >    |          | 000        |

| 1650                        | RPB4R            | 31:16         | _     | _     |       | _     | _     | _     | _    | —    | _    | _    | _    |      | —    |                | _    | —        | 000        |

|                             |                  | 15:0          |       |       |       | —     |       | _     |      |      | _    |      |      |      |      | RPB4R<4:0<br>T | >    | _        | 000        |

| 1654                        | RPB5R            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      | —    |      | <br>RPB5R<4:0  | >    |          | 000        |

|                             |                  | 31:16         |       |       |       |       |       |       |      |      |      |      |      |      | _    | —              | _    | _        | 000        |

| 1658                        | RPB6R            | 15:0          | _     |       | _     | _     | _     | _     | _    | _    | _    | _    | _    |      |      | RPB6R<4:0      | >    |          | 000        |

| 1650                        |                  | 31:16         | _     | _     | —     | _     | _     | _     | _    |      | _    | _    |      |      |      |                |      | —        | 000        |

| 165C                        | RPB7R            | 15:0          | _     | _     | _     | _     | _     | _     |      |      | _    | _    |      |      |      | RPB7R<4:0      | >    |          | 000        |

PIC32MK GP/MC Family

# 14.3 Timer1 Control Register

# TABLE 14-1: TIMER1 REGISTER MAP

| ess                       |                                 |           | Bits  |                 |       |       |       |       |      |       |        |      | ts    |        |      |       |      |      |           |

|---------------------------|---------------------------------|-----------|-------|-----------------|-------|-------|-------|-------|------|-------|--------|------|-------|--------|------|-------|------|------|-----------|

| Virtual Addre<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0000                      | T400N                           | 31:16     | _     | _               | _     | _     | _     | —     | _    | _     | _      | _    | _     | _      | _    | _     | _    | _    | 0000      |

| 0000                      | T1CON                           | 15:0      | ON    | _               | SIDL  | TWDIS | TWIP  | _     | TECS | <1:0> | TGATE  | _    | TCKPS | S<1:0> | _    | TSYNC | TCS  | _    | 0000      |

| 0010                      | TMR1                            | 31:16     | —     |                 | —     | —     | —     | _     | _    | —     | —      | —    | _     | _      | —    | —     | _    | _    | 0000      |

| 0010                      |                                 | 15:0      |       | TMR1<15:0> 0000 |       |       |       |       |      |       |        |      | 0000  |        |      |       |      |      |           |

| 0020                      | PR1                             | 31:16     | —     | _               |       |       |       | -     |      | -     | —      | -    | _     | -      | -    | —     | —    | _    | 0000      |

| 0020                      |                                 | 15:0      |       |                 |       |       |       |       |      | PR1<  | <15:0> |      |       |        |      |       |      |      | FFFF      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

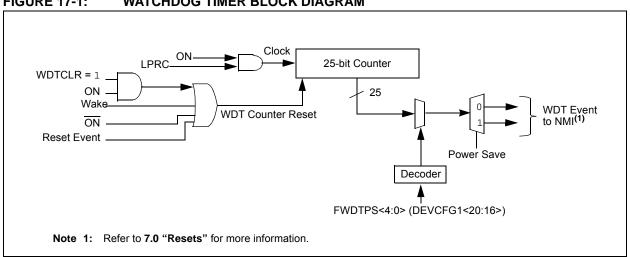

# 17.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MK GP/MC Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or software controlled

- · User-configurable time-out period

- Can wake the device from Sleep or Idle

# FIGURE 17-1: WATCHDOG TIMER BLOCK DIAGRAM

# 21.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Inter-Integrated Circuit" (DS0000000), which from is available the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The  $I^2C$  software library is available in MPLAB Harmony. If the user application is to implement  $I^2C$ , for future device pin compatibility, it is recommended to assign software  $I^2C$  functions according to the details provided in the device pin tables (Table 3 through Table 6):

- For 64-pin packages, refer to Notes 6 and 7 in Table 3 and Table 4

- For 100-lead packages, refer to Notes 5 and 6 in Table 5 and Table 6.

# 21.1 Software I<sup>2</sup>C Performance

Table 21-1 provides the performance details of the  $l^2C$ .

| I <sup>2</sup> C Baud<br>Rate | I <sup>2</sup> C Transactions/<br>Second | I <sup>2</sup> C CPU<br>Utilization |

|-------------------------------|------------------------------------------|-------------------------------------|

|                               | 22070 (continuous)                       | 50.76%                              |

| 400 kHz                       | 16841                                    | 38.73%                              |

| 400 KHZ                       | 4079                                     | 9.38%                               |

|                               | 429                                      | 0.99%                               |

|                               | 5581 (continuous)                        | 12.84%                              |

| 100 kHz                       | 4077                                     | 9.38%                               |

|                               | 429                                      | 0.99%                               |

# TABLE 21-1: I<sup>2</sup>C PERFORMANCE

# **REGISTER 22-1: UXMODE: UARTX MODE REGISTER (CONTINUED)**

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits<sup>(2)</sup>

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- bit 5 ABAUD: Auto-Baud Enable bit

- 1 = Enable baud rate measurement on the next reception of Sync character (0x55); cleared by hardware upon completion

- 0 = Baud rate measurement disabled or completed

- bit 4 RXINV: Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 **BRGH:** High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- Note 1: These bits can be changed only when the ON bit (UxMODE<15>) is set to '0'.

- 2: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see 13.3 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|------------------------|------------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                    | U-0                    | U-0                    | U-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | _                      |                        | _                      | —                      | AGIEN27           | AGIEN26           | AGIEN25          | AGIEN24          |

| 22:16        | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | AGIEN23 <sup>(1)</sup> | AGIEN22 <sup>(1)</sup> | AGIEN21 <sup>(1)</sup> | AGIEN20 <sup>(1)</sup> | AGIEN19           | AGIEN18           | AGIEN17          | AGIEN16          |

| 15:8         | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | AGIEN15                | AGIEN14                | AGIEN13                | AGIEN12                | AGIEN11           | AGIEN10           | AGIEN9           | AGIEN8           |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | AGIEN7                 | AGIEN6                 | AGIEN5                 | AGIEN4                 | AGIEN3            | AGIEN2            | AGIEN1           | AGIEN0           |

# REGISTER 25-9: ADCGIRQEN1: ADC GLOBAL INTERRUPT ENABLE REGISTER 1

# Legend:

| •                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-28 Unimplemented: Read as '0'

bit 27-0 AGIEN27: AGIEN0: ADC Global Interrupt Enable bits

1 = Interrupts are enabled for the selected analog input. The interrupt is generated after the converted data is ready (indicated by the AIRDYx bit of the ADCDSTAT1 register)

0 = Interrupts are disabled

Note 1: This bit is not available on 64-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31.24     | 1:24 DATA<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23.10     |                   |                   |                   | DATA<             | 23:16>            |                   |                  |                  |  |  |

| 15:8      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 10.0      |                   |                   |                   | DATA<             | <15:8>            |                   |                  |                  |  |  |

| 7:0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7.0       | DATA<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

# REGISTER 25-31: ADCDATAX: ADC OUTPUT DATA REGISTER 'x' ('x' = 0-27, 33-41, AND 45-53)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 DATA<31:0>: ADC Converted Data Output bits.

- Note 1: The registers, ADCDATA23-20, ADCDATA41-33, and ADCDATA45-47, are not available on 64-pin devices.

- **2:** The registers, ADCDATA32-28 and ADCDATA44-42, are not available on 64-pin and 100-pin devices.

**3:** When an alternate input is used as the input source for a dedicated ADC module, the data output is still read from the Primary input Data Output Register.

4: Reading the ADCDATAx register value after changing the FRACT bit converts the data into the format specified by FRACT bit.

# 32.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32MK GP/MC devices include two features to prevent alterations to enabled or disabled peripherals:

- Control Register Lock Sequence

- Configuration Bit Select Lock

# 32.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting the PMDLOCK bit prevents writes to the control registers and clearing the PMDLOCK bit allows writes.

To set or clear the PMDLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators** with Enhanced PLL" (DS60001250) in the *"PIC32 Family Reference Manual"* for details.

# 32.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If the PMDLOCK bit remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 21.24        | r-x               | R/P               | r-1               | r-1               | r-1               | r-1                   | r-1              | r-1              |

| 31:24        | —                 | EJTAGBEN          | —                 | _                 | —                 | —                     | _                | —                |

| 00.40        | r-1               | r-1               | R/P               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 23:16        | —                 | —                 | POSCBOOST         | POSCGA            | AIN<1:0>          | SOSCBOOST             | SOSCG            | AIN<1:0>         |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-y               | R/P                   | r-1              | r-1              |

| 15:8         | SMCLR             |                   | DBGPER<2:0>       |                   | —                 | FSLEEP                | _                | —                |

| 7.0          | r-1               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          | _                 | BOOTISA           | TRCEN             | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |

### REGISTER 33-3: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit  |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31 Reserved: The reset value of this bit is the same as DEVSIGN0<31>.

- bit 30 EJTAGBEN: EJTAG Boot Enable bit

- 1 = Normal EJTAG functionality

- 0 = Reduced EJTAG functionality

- bit 29-22 **Reserved:** Write as '1'

- bit 21 POSCBOOST: Primary Oscillator Boost Kick Start Enable bit

- 1 = Boost the kick start of the oscillator

- 0 = Normal start of the oscillator

- **Note:** For Revision A1 silicon, the POSBOOST bit should be set and do not use an external gain resistor (i.e., RSHUNT).

- bit 20-19 POSCGAIN<1:0>: Primary Oscillator Gain Control bits

- 11 = Gain Level 3 (highest)

- 10 = Gain Level 2

- 01 = Gain Level 1

- 00 = Gain Level 0 (lowest)

- bit 18 SOSCBOOST: Secondary Oscillator Boost Kick Start Enable bit

- 1 = Boost the kick start of the oscillator

- 0 = Normal start of the oscillator

- bit 17-16 SOSCGAIN<1:0>: Secondary Oscillator Gain Control bits

- 11 = Gain Level 3 (highest)

- 10 = Gain Level 2

- 01 = Gain Level 1

- 00 = Gain Level 0 (lowest)

- bit 15 **SMCLR:** Soft Master Clear Enable bit

- $1 = \overline{MCLR}$  pin generates a normal system Reset

- 0 = MCLR pin generates a POR Reset

- Note 1: This bit sets the value of the JTAGEN bit in the CFGCON register.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 51.24     | SN<31:24>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16     | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23.10     | SN<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8      | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15.0      | SN<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7.0       | SN<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |  |

# **REGISTER 33-12: DEVSNx: DEVICE SERIAL NUMBER REGISTER** 'x' ('x' = 0-3)

# Legend:

| - <b>J</b>        |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-0 SN<31:0>: Device Unique Serial Number bits

These registers contain a value, programmed during factory production test, that is unique to each unit and are user read only. These values are persistent and not erased even when a new application code is programmed into the device. These values can be used if desired as an encryption key in combination with the Microchip encryption library.

# TABLE 36-25: TIMER2-TIMER9 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS | TICS                     |                                | (unless          | d Operating Conditions:<br>otherwise stated)<br>Ig temperature $-40^{\circ}C \le -40^{\circ}C \le$ | :<br>Ta ≤ + | 85°C for I | ndustrial<br>Extended                  |                                                      |

|---------------|-----------|--------------------------|--------------------------------|------------------|----------------------------------------------------------------------------------------------------|-------------|------------|----------------------------------------|------------------------------------------------------|

| Param.<br>No. | Symbol    | Cha                      | racteristic                    | s <sup>(1)</sup> | Min.                                                                                               | Max.        | Units      | Con                                    | ditions                                              |

| TB10          | ТтхН      | TxCK<br>High Time        | Synchronous, witl<br>prescaler |                  | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                             | —           | ns         | Must also<br>meet<br>parameter<br>TB15 | N = prescale<br>value<br>(1, 2, 4, 8,<br>16, 32, 64, |

| TB11          | TTXL      | TxCK<br>Low Time         | Synchron<br>prescaler          | ous, with        | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                             | —           | ns         | Must also<br>meet<br>parameter<br>TB15 | 256)                                                 |

| TB15          | T⊤xP      | TxCK<br>Input            | Synchron<br>prescaler          | ous, with        | [(Greater of [(25 ns or<br>2 TPBCLK3)/N] + 30 ns                                                   | -           | ns         | VDD > 2.7V                             |                                                      |

|               |           | Period                   |                                |                  | [(Greater of [(25 ns or<br>2 TPBCLK3)/N] + 50 ns                                                   | —           | ns         | VDD < 2.7V                             |                                                      |

| TB20          | TCKEXTMRL | Delay from<br>Clock Edge |                                |                  | —                                                                                                  | 1           | TPBCLK3    |                                        | _                                                    |

Note 1: These parameters are characterized, but not tested in manufacturing.

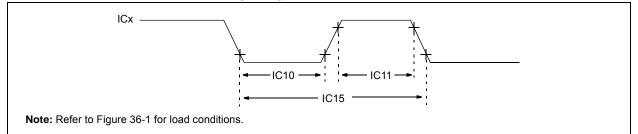

# FIGURE 36-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

# TABLE 36-26: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHA                       | RACTER | ISTICS                   | (unless of | Operating Conditions: 2herwise stated)temperature $-40^{\circ}C \le TA$ $-40^{\circ}C \le TA$ | ×≤+85° | C for In   |                                      |                                                                |

|------------------------------|--------|--------------------------|------------|-----------------------------------------------------------------------------------------------|--------|------------|--------------------------------------|----------------------------------------------------------------|

| Param.<br>No. Symbol Charact |        | teristics <sup>(1)</sup> | Min.       | Max.                                                                                          | Units  | Conditions |                                      |                                                                |

| IC10                         | TccL   | ICx Input Low<br>Time    |            | ((TPBCLKx/N) + 25 ns)                                                                         |        | ns         | Must also meet<br>parameter<br>IC15. | x = 2 for IC1-IC9<br>x = 3 for IC10-IC16<br>N = prescale value |

| IC11                         | ТссН   | ICx Inpu<br>Time         | ut High    | ((TPBCLKx/N) + 25 ns)                                                                         | _      | ns         | Must also meet<br>parameter<br>IC15. | (1, 4, 16)                                                     |

| IC15                         | TCCP   | ICx Inpu                 | ut Period  | ((TPBCLKx/N) + 50 ns)                                                                         | _      | ns         | —                                    |                                                                |

| Note 1: | These parameters are | characterized, but | not tested in m | anufacturing. |

|---------|----------------------|--------------------|-----------------|---------------|

|         |                      |                    |                 |               |

# TABLE 36-34:SPIX MODULE SLAVE MODE (CKE = 0, SMP = 1) TIMING<br/>REQUIREMENTS (CONTINUED) (CONTINUED)

| AC CHA        | ARACTERIS             | TICS                                          | Standard Operating Conditions: 2.2V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                                                                                                                                                                                                                           |  |

|---------------|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                | Min.                                                                                                                                                                                                        | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                                                                                                                                                |  |

| SP9b          | Тзск                  | SCKx Period                                   | 22                                                                                                                                                                                                          |                     |      | ns    | $(VDD \ge 3.0V \text{ and the SMP bit}$<br>(SPIxCON<9> = 1), I/O Pin Slew Rate Control (x = A-F, y = port pin), SRCON0x.y = 0, SRCON1x.y = 0 All other remappable SPI pins not contained in conditions for parameter SP9a.                |  |

|               |                       |                                               | 41                                                                                                                                                                                                          |                     | _    | ns    | $(VDD \ge 3.0V \text{ and the SMP bit}$<br>(SPIxCON<9> = 1), I/O Pin Slew Rate Control (x = A-F, y = port pin), SRCON0x.y = 1, SRCON1x.y = 0 All other remappable SPI pins not contained in conditions for parameter SP9a.                |  |

|               |                       |                                               | 59                                                                                                                                                                                                          |                     |      | ns    | $(VDD \ge 3.0V \text{ and the SMP bit}$<br>(SPIxCON<9> = 1), I/O Pin Slew<br>Rate Control (x = A-F, y = port pin),<br>SRCON0x.y = 0, SRCON1x.y = 1<br>All other remappable SPI pins not<br>contained in conditions for<br>parameter SP9a. |  |

|               |                       |                                               | 74                                                                                                                                                                                                          | _                   | _    | ns    | $(VDD \ge 3.0V \text{ and the SMP bit}$<br>(SPIxCON<9> = 1), I/O Pin Slew Rate Control (x = A-F, y = port pin), SRCON0x.y = 1, SRCON1x.y = 1 All other remappable SPI pins not contained in conditions for parameter SP9a.                |  |

| SP70          | TscL                  | SCKx Input Low Time                           | Tsck/2                                                                                                                                                                                                      | _                   | —    | ns    | _                                                                                                                                                                                                                                         |  |

| SP71          | TscH                  | SCKx Input High Time                          | Tsck/2                                                                                                                                                                                                      | _                   | _    | ns    |                                                                                                                                                                                                                                           |  |

| SP72          | TscF                  | SCKx Input Fall Time                          | <u> </u>                                                                                                                                                                                                    | —                   | —    | ns    | See parameter DO32                                                                                                                                                                                                                        |  |

| SP73          | TSCR                  | SCKx Input Rise Time                          | <u>                                      </u>                                                                                                                                                               | —                   |      | ns    | See parameter DO31                                                                                                                                                                                                                        |  |

| SP30          | TDOF                  | SDOx Data Output Fall<br>Time<br>(Note 3)     |                                                                                                                                                                                                             | —                   | _    | ns    | See parameter DO32                                                                                                                                                                                                                        |  |

| SP31          | TDOR                  | SDOx Data Output Rise<br>Time <b>(Note 3)</b> | -                                                                                                                                                                                                           | —                   |      | ns    | See parameter DO31                                                                                                                                                                                                                        |  |

| SP35          |                       | SDOx Data Output Valid                        |                                                                                                                                                                                                             | —                   | 7    | ns    | VDD > 2.7V                                                                                                                                                                                                                                |  |

|               |                       | after SCKx Edge                               | <u>                                      </u>                                                                                                                                                               | —                   | 10   | ns    | VDD < 2.7V                                                                                                                                                                                                                                |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 5                                                                                                                                                                                                           | —                   | _    | ns    | -                                                                                                                                                                                                                                         |  |

| SP41          | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data<br>Input to SCKx Edge  | 5                                                                                                                                                                                                           | —                   | _    | ns    | —                                                                                                                                                                                                                                         |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** Assumes 10 pF load on all SPIx pins.

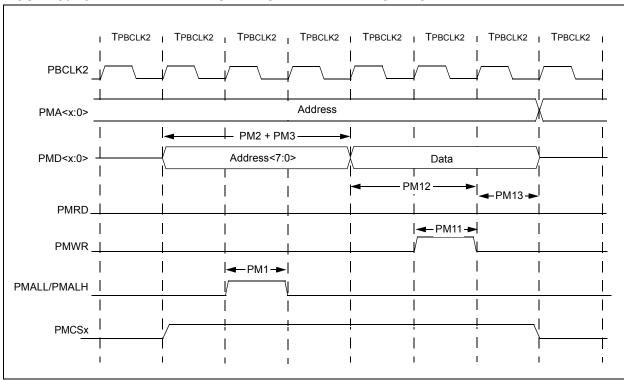

# FIGURE 36-19: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

# TABLE 36-46: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| АС СНА        | RACTERI | STICS                                                                     | (unless | d Operating<br>otherwise s<br>g temperatu | stated)<br>ire -40°( | $C \le TA \le +8$ | <b>to 3.6V</b><br>85°C for Industrial<br>125°C for Extended |

|---------------|---------|---------------------------------------------------------------------------|---------|-------------------------------------------|----------------------|-------------------|-------------------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.    | Тур.                                      | Max.                 | Units             | Conditions                                                  |

| PM11          | Twr     | PMWR Pulse Width                                                          |         | 1 TPBCLK2                                 | _                    |                   | _                                                           |

| PM12          | Tovsu   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —       | 2 TPBCLK2                                 | _                    | _                 | _                                                           |

| PM13          | Tdvhold | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             |         | 1 TPBCLK2                                 | —                    |                   | —                                                           |

Note 1: These parameters are characterized, but not tested in manufacturing.