Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, IrDA, LINbus, PMP, QEI, SPI, UART/USART, USB OTG                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, Motor Control PWM, WDT        |

| Number of I/O              | 49                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 27x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512mcf064t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4: **PIN NAMES FOR 64-PIN MOTOR CONTROL (MCF) DEVICES**

|          | 64-PIN QFN <sup>(4)</sup> AND TQFP (TOP VIEW)             |     |                                                       |

|----------|-----------------------------------------------------------|-----|-------------------------------------------------------|

|          | PIC32MK0512MCF064<br>PIC32MK1024MCF064                    |     | 1 64 1                                                |

| Pin<br># | Full Pin Name                                             | QFN | I <sup>(4)</sup> TQFP<br>Full Pin Name                |

|          |                                                           |     |                                                       |

| 1        | TCK/RPA7/PWM10H/PWM4L/PMPD5/RA7                           |     | OA5IN+/DAC1/AN24/CVD24/C5IN1+/C5IN3-/RPA4/T1CK/T1G/RA |

| 2        | RPB14/PWM1H/VBUSON1/PMPD6/RB14                            | 34  | VBUS                                                  |

|          | RPB15/PWM7H/PWM1L/PMPD7/RB15                              |     | VUSB3V3                                               |

|          | AN19/CVD19/RPG6/PMPA5/RG6                                 |     | D-                                                    |

| -        | AN18/CVD18/RPG7/PMPA4/RG7 <sup>(6)</sup>                  |     | D+                                                    |

| 6        | AN17/CVD17/RPG8/PMPA3/RG8 <sup>(7)</sup>                  | 38  | Vdd                                                   |

| 7        | MCLR                                                      | 39  | OSCI/CLKI/AN49/CVD49/RPC12/RC12                       |

| 8        | AN16/CVD16/RPG9/PMPA2/RG9                                 | 40  | OSCO/CLKO/RPC15/RC15                                  |

| 9        | Vss                                                       | 41  | Vss                                                   |

| 10       | VDD                                                       | 42  | RD8                                                   |

| 11       | AN10/CVD10/RPA12/RA12                                     | 43  | PGED2/RPB5/USBID1/RB5 <sup>(7)</sup>                  |

| 12       | AN9/CVD9/RPA11/USBOEN1/RA11                               | 44  | PGEC2/RPB6/SCK2/PMPA15/RB6 <sup>(6)</sup>             |

| 13       | OA2OUT/ANO/C2IN4-/C4IN3-/RPA0/RA0                         | 45  | DAC2/AN48/CVD48/RPC10/PMPA14/PSPCS/RC10               |

| 14       | OA2IN+/AN1/C2IN1+/RPA1/RA1                                | 46  | OA5OUT/AN25/CVD25/C5IN4-/RPB7/SCK1/INT0/RB7           |

| 15       | PGED3/VREF-/OA2IN-/AN2/C2IN1-/RPB0/CTED2/RB0              | 47  | SOSCI/RPC13 <sup>(5)</sup> /RC13 <sup>(5)</sup>       |

| 16       | PGEC3/OA1OUT/VREF+/AN3/C1IN4-/C4IN2-/RPB1/CTED1/PMPA6/RB1 | 48  | SOSCO/RPB8 <sup>(5)</sup> /RB8 <sup>(5)</sup>         |

| 17       | PGEC1/OA1IN+/AN4/C1IN1+/C1IN3-/C2IN3-/RPB2/RB2            | 49  | TMS/OA5IN-/AN27/CVD27/C5IN1-/RPB9/RB9                 |

| 18       | PGED1/OA1IN-/AN5/CTCMP/C1IN1-/RTCC/RPB3/RB3               | 50  | TRCLK/RPC6/PWM6H/RC6                                  |

| 19       | AVDD                                                      | 51  | TRD0/RPC7/PWM12H/PWM6L/RC7                            |

| 20       | AVss                                                      | 52  | TRD1/RPC8/PWM5H/PMPWR/PSPWR/RC8                       |

| 21       | OA3OUT/AN6/CVD6/C3IN4-/C4IN1+/C4IN4-/RPC0/RC0             | 53  | TRD2/RPD5/PWM12H/PMPRD/PSPRD/RD5                      |

| 22       | OA3IN-/AN7/CVD7/C3IN1-/C4IN1-/RPC1/PMPA7/RC1              | 54  | TRD3/RPD6/PWM12L/RD6                                  |

| 23       | OA3IN+/AN8/CVD8/C3IN1+/C3IN3-/RPC2/FLT3/PMPA13/RC2        | 55  | RPC9/PWM11H/PWM5L/RC9                                 |

| 24       | AN11/CVD11/C1IN2-/FLT4/PMPA12/RC11                        | 56  | Vss                                                   |

| 25       | Vss                                                       | 57  | Vdd                                                   |

| 26       | Vdd                                                       | 58  | RPF0/PWM11H/RF0                                       |

| 27       | AN12/CVD12/C2IN2-/C5IN2-/FLT5/PMPA11/RE12 <sup>(7)</sup>  | 59  | RPF1/PWM11L/RF1                                       |

| 28       | AN13/CVD13/C3IN2-/FLT6/PMPA10/RE13 <sup>(6)</sup>         | 60  | RPB10/PWM3H/PMPD0/RB10                                |

|          | AN14/CVD14/RPE14/FLT7/PMPA1/PSPA1/RE14                    | 61  | RPB11/PWM9H/PWM3L/PMPD1/RB11                          |

|          | AN15/CVD15/RPE15/FLT8/PMPA0/PSPA0/RE15                    | 62  | RPB12/PWM2H/PMPD2/RB12                                |

| 31       | TDI/DAC3/AN26/CVD26/RPA8/PMPA9/RA8 <sup>(7)</sup>         | 63  | RPB13/PWM8H/PWM2L/CTPLS/PMPD3/RB13                    |

|          |                                                           |     |                                                       |

be used by remappable peripherals. See Table 1 for the available peripherals and 13.3 "Peripheral Pin Select (PPS) for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See 13.0 "I/O Ports" for more information.

3:

Shaded pins are 5V tolerant. The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 4:

5:

Functions are restricted to input functions only and inputs will be slower than standard inputs. The I<sup>2</sup>C Library is available in MPLAB Harmony. For future hardware or silicon compatibility, it is recommended to use these pins for the 6:

I<sup>2</sup>C master/slave clock. (i.e., SCL). The I<sup>2</sup>C Library is available in MPLAB Harmony. For future hardware or silicon compatibility, it is recommended to use these pins for the I<sup>2</sup>C data I/O, (i.e., SDA). 7:

## REGISTER 4-9: SBTxRDy: SYSTEM BUS TARGET 'x' REGION 'y' READ PERMISSIONS REGISTER ('x' = 0-3; 'y' = 0-2)

|              |                   | 1                 | <u> </u>          | /                 |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 |                   | —                 | _                 | -                 | —                 | -                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | _                 | —                 |                   | —                 |                  | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          |                   |                   |                   | _                 | GROUP3            | GROUP2            | GROUP1           | GROUP0           |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-4 Unimplemented: Read as '0'

bit 3 GROUP3: Group 3 Read Permissions bits 1 = Privilege Group 3 has read permission 0 = Privilege Group 3 does not have read permission bit 2 GROUP2: Group 2 Read Permissions bits 1 = Privilege Group 2 has read permission 0 = Privilege Group 2 does not have read permission GROUP1: Group 1 Read Permissions bits bit 1 1 = Privilege Group 1 has read permission 0 = Privilege Group 1 does not have read permission bit 0 GROUP0: Group 0 Read Permissions bits 1 = Privilege Group 0 has read permission 0 = Privilege Group 0 does not have read permission

Note 1: Refer to Table 4-6 for the list of available targets and their descriptions.

2: For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for more information.

NOTES:

#### 9.2 **Oscillator Control Registers**

| TABL          | E 9-2:      | 0    | SCILL | ATOR C | ONFIG | JRATIO | N REGI | STER N | IAP |

|---------------|-------------|------|-------|--------|-------|--------|--------|--------|-----|

| ess           |             |      |       |        |       |        |        |        |     |

| Addr<br>30_#) | ister<br>me | ange |       |        |       |        |        |        |     |

| Virtual Addre<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13     | 28/12      | 27/11      | 26/10    | 25/9        | 24/8       | 23/7            | 22/6 | 21/5    | 20/4  | 19/3      | 18/2      | 17/1        | 16/0  |

|---------------------------|------------------|---------------|-------|-------|-----------|------------|------------|----------|-------------|------------|-----------------|------|---------|-------|-----------|-----------|-------------|-------|

| 1200                      | OSCCON           | 31:16         |       | _     | —         | —          | —          | F        | FRCDIV<2:0  | >          | DRMEN           | _    | SLP2SPD | _     | —         | —         | —           | —     |

| 1200                      | 0000011          | 15:0          | —     | (     | COSC<2:0> |            | —          |          | NOSC<2:0>   |            | CLKLOCK         | —    | —       | SLPEN | CF        | UFRCEN    | SOSCEN      | OSWEN |

| 1210                      | OSCTUN           | 31:16         |       | —     | _         | _          | —          |          | —           | _          | _               | _    | _       | —     | —         |           | —           | —     |

|                           |                  | 15:0          | —     | _     |           | —          | —          | —        | —           | —          | _               | —    |         |       |           | N<5:0>    |             |       |

| 1220                      | SPLLCON          | 31:16         | _     | —     | —         | —          | —          |          | PLLODIV<2:0 |            | —               |      | r       |       | LLMULT<6  |           |             |       |

|                           |                  | 15:0          | _     | —     | —         |            |            |          | PLLIDIV<2:0 |            | PLLICLK         | _    | —       |       |           |           | LLRANGE<2:0 | >     |

| 1230                      | UPLLCON          | 31:16         | _     | —     | UPOSCEN   | _          |            |          | PLLODIV<2:0 |            | _               |      | r       |       | LLMULT<6  |           |             |       |

|                           |                  | 15:0          |       | —     | —         |            | —          | ŀ        | PLLIDIV<2:0 | >          | —               | _    | _       | _     | _         | Р         | LLRANGE<2:0 | >     |

| 1280                      | REF01CON         | 31:16         | -     |       | 0101      | 05         |            |          |             | 1 OT 1 / F | RODIV<14:0      | )>   | 1       |       | 1         |           | =           |       |

|                           |                  | 15:0          | ON    | _     | SIDL      | OE         | RSLP       |          | DIVSWEN     | ACTIVE     | —               |      | _       |       |           | ROS       | EL<3:0>     |       |

| 1290                      | REF01TRIM        | 31:16<br>15:0 |       |       | 1         |            | ROTRIM<8:0 | )>       |             |            |                 | _    | -       | _     | _         | _         |             |       |

|                           |                  | 31:16         | _     | _     | _         |            | _          | _        | —           | _          | —<br>RODIV<14:( | -    | —       | _     | —         |           | —           | —     |

| 12A0                      | 12A0 REFO2CON    |               | ON    |       | SIDL      | OE         | RSLP       | _        | DIVSWEN     | ACTIVE     |                 |      |         |       |           | DOS       | EL<3:0>     |       |

|                           |                  |               |       |       |           | ROTRIM<8:0 |            | DIVSWEIN | ACTIVE      | _          |                 |      |         |       |           |           | _           |       |

| 12B0                      | REF02TRIM        | 15:0          |       | _     | _         |            |            |          | _           | _          | _               |      |         |       |           |           |             |       |

|                           |                  | 31:16         | _     |       |           |            |            |          |             |            | RODIV<14:0      |      |         |       |           |           |             |       |

| 12C0                      | REF03CON         | 15:0          | ON    | _     | SIDL      | OE         | RSLP       | _        | DIVSWEN     | ACTIVE     | _               | _    | _       | _     |           | ROS       | EL<3:0>     |       |

|                           |                  | 31:16         |       |       |           | -          | ROTRIM<8:0 | )>       |             |            |                 |      | _       | _     | _         | _         |             |       |

| 12D0                      | REF03TRIM        | 15:0          | _     | _     | _         | _          | _          | _        | _           | _          |                 | _    | _       | _     | _         | _         | _           | _     |

|                           |                  | 31:16         | _     |       |           | 1          |            |          |             |            | RODIV<14:       | )>   | 1       |       |           |           |             |       |

| 12E0                      | REFO4CON         | 15:0          | ON    | _     | SIDL      | OE         | RSLP       | _        | DIVSWEN     | ACTIVE     | _               | _    | _       | _     |           | ROS       | EL<3:0>     |       |

| 4050                      | DEFOATDINA       | 31:16         |       |       |           |            | ROTRIM<8:0 | )>       |             |            |                 | _    | _       | _     | _         | —         | _           | _     |

| 12F0                      | REFO4TRIM        | 15:0          | _     | —     | _         | _          | —          | —        | _           | —          | _               | _    | —       | _     | _         | —         | —           | _     |

| 1000                      |                  | 31:16         | _     | _     | _         | —          | _          | _        | _           | _          | _               | _    | —       | _     | _         | —         | —           | _     |

| 1300                      | PB1DIV           | 15:0          | _     | _     | —         | _          | PBDIVRDY   |          | —           | _          | _               |      |         |       | PBDIV<6:0 | )>        | •           |       |

| 1210                      | PB2DIV           | 31:16         | —     |       | —         | —          | —          |          | —           |            | _               |      | —       | —     | —         | —         | —           | —     |

| 1310                      | PBZDIV           | 15:0          | ON    |       | —         | —          | PBDIVRDY   |          | —           | —          | _               |      |         |       | PBDIV<6:0 | )>        |             |       |

| 1320                      | PB3DIV           | 31:16         | _     | _     | _         | —          | —          | _        | —           | —          | —               |      | —       | _     | —         | —         | —           | —     |

| 1520                      | FB3DIV           | 15:0          | ON    |       | —         | _          | PBDIVRDY   |          | —           |            | _               |      |         |       | PBDIV<6:0 | )>        |             |       |

| 1330                      | PB4DIV           | 31:16         | _     | -     | —         | —          | -          | _        | _           | -          | —               | _    | _       | _     | _         | · · · · · | _           | _     |

| 1550                      |                  | 15:0          | ON    | -     | _         | _          | PBDIVRDY   | -        | _           | -          | _               |      |         |       | PBDIV<6:0 | )>        |             |       |

Bits

Legend: Note

DS60001402E-page 165

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. 1:

Reset values are dependent on the DEVCFGx Configuration bits and the type of reset. Refer to Table 36-16 in **36.0** "Electrical Characteristics" for PBCLK6 frequency limitations. 2:

The PB7DIV register is read-only. 3:

All Resets<sup>(1)</sup>

0xx0

xxxx

0000

0020 0xxx

0xxx 0xxx

0x0x 0000

0000 0000

0000

0000

0000 0000

0000

0000

0000

0000

0000

0000 0000

0000

0000

8801 0000

8801 0000

8801 0000

8801

|              |                   |                   |                   |                   |                   | •                 |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |  |  |

| 31:24        | _                 | —                 | _                 | PLLODIV<2:0>      |                   |                   |                  |                  |  |  |  |  |

| 23:16        | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-y             | R/W-y             | R/W-y            | R/W-y            |  |  |  |  |

| 23.10        | —                 | PLLMULT<6:0>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |  |  |

| 10.0         | —                 |                   |                   |                   |                   | I                 | PLLIDIV<2:0>     | >                |  |  |  |  |

| 7:0          | R/W-y             | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |  |  |

| 7:0          | PLLICLK           |                   | _                 | _                 |                   | PL                | LRANGE<2:        | 0>               |  |  |  |  |

## REGISTER 9-3: SPLLCON: SYSTEM PLL CONTROL REGISTER

| Legend:         y = Value set from Configuration bits on POR |                   |                  |                                                   |                    |  |  |  |

|--------------------------------------------------------------|-------------------|------------------|---------------------------------------------------|--------------------|--|--|--|

|                                                              | R = Readable bit  | W = Writable bit | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

|                                                              | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                              | x = Bit is unknown |  |  |  |

## bit 31-27 Unimplemented: Read as '0'

bit 26-24 PLLODIV<2:0>: System PLL Output Clock Divider bits

111 = Reserved 110 = Reserved 101 = PLL Divide by 32 100 = PLL Divide by 16 011 = PLL Divide by 8 010 = PLL Divide by 4 001 = PLL Divide by 2 000 = Reserved

The default setting is specified by the FPLLODIV<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "Special Features" for information.

## bit 23 Unimplemented: Read as '0'

bit 22-16 PLLMULT<6:0>: System PLL Multiplier bits

1111111 = Multiply by 128 1111110 = Multiply by 127 1111101 = Multiply by 126 1111100 = Multiply by 125

•

•

0000000 = Multiply by 1

The default setting is specified by the FPLLMULT<6:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "**Special Features**" for information.

## bit 15-11 Unimplemented: Read as '0'

| Note 1: | Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced |

|---------|-----------------------------------------------------------------------------------------------------|

|         | PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.                               |

| -       |                                                                                                     |

- 2: Writes to this register are not allowed if the SPLL is selected as a clock source (COSC<2:0> = 001).

- 3: While the PLL is active, and if updating the PLL bits in the OSCCON register at run-time, the user application must remain within the following limits at all times for all nodes in the PLL clock tree. Therefore, the order in which the PLL values may be modified, (i.e., PLLODIV, PLLMULT, PLLODIV) becomes important. Failure to maintain PLL nodes within min/max ranges may result in unstable PLL and system behavior.

- Output and input to PLLIDIV block (i.e., FPLLI) 5 MHz to 64 MHz (min/max at all times)

- VCO output, (i.e., FVCO) 350 MHz to 700 MHz (min/max at all times)

- Output of PLLODIV, (i.e., FPLL) 10 MHz to 120 MHz (min/max at all times)

NOTES:

## TABLE 11-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

|                             | LL 11-J.                        |                       |       |       |       |       |        |       |      |        |        | ,      |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------------------|-------|-------|-------|-------|--------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| ess                         |                                 |                       |       |       |       |       |        |       |      | Bit    | s      |        |        |        |        |        |        |        |            |

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range             | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 15 <b>P</b> 0               | DCH7ECON                        | 201 31:16 CHAIRQ<7:0> |       |       |       |       |        |       |      |        |        | 00FF   |        |        |        |        |        |        |            |

| 1360                        |                                 | 15:0                  |       |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN |        | _      | _      | FF00       |

| 1500                        | DCH7INT                         | 31:16                 | _     | -     | -     | _     | -      | —     | -    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1300                        | DCHI/INT                        | 15:0                  | _     | _     | _     | —     | _      | —     | _    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 1500                        | DCH7SSA                         | 31:16                 |       |       |       |       |        |       |      | CHSSA  | 31.0>  |        |        |        |        |        |        |        | 0000       |

| 1300                        | DOINGON                         | 15:0                  |       |       |       |       |        |       |      | CHOOA  | -01.02 |        |        |        |        |        |        |        | 0000       |

| 15E0                        | DCH7DSA                         | 31:16                 |       |       |       |       |        |       |      | CHDSA  | <31.0> |        |        |        |        |        |        |        | 0000       |

| IOLO                        |                                 | 15:0                  |       |       |       |       |        |       |      |        | -01.04 |        |        |        |        |        |        |        | 0000       |

| 15E0                        | DCH7SSIZ                        | 31:16                 | —     | —     | —     | —     | —      | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1600                        | DCH7DSIZ                        | 31:16                 | —     | —     | —     |       | —      | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHDSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1610                        | DCH7SPTR                        | 31:16                 | —     | —     | —     | —     | —      | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHSPTR | <15:0> |        |        |        |        |        | -      |        | 0000       |

| 1620                        | DCH7DPTR                        | 31:16                 | —     | —     | —     | —     | _      | —     | —    | —      | —      | —      | _      | —      | _      | —      | —      | —      | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1630                        | DCH7CSIZ                        | 31:16                 | _     | —     | —     |       | _      | —     | —    | —      | —      | -      | _      | —      | —      | —      | —      | _      | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHCSIZ |        |        |        |        |        |        |        |        | 0000       |

| 1640                        | DCH7CPTR                        | 31:16                 | _     | —     | —     | —     | —      | —     | _    | -      | -      | —      | _      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1650                        | DCH7DAT                         | 31:16                 | _     | —     | _     | —     | _      | _     | _    |        | -      | _      | _      | —      | _      | _      | —      |        | 0000       |

|                             |                                 | 15:0                  |       |       |       |       |        |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 |                   |                   |                   |                  | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

## REGISTER 11-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-24 Unimplemented: Read as '0'

| bit 23   | CHSDIE: Channel Source Done Interrupt Enable bit                                |

|----------|---------------------------------------------------------------------------------|

|          | 1 = Interrupt is enabled                                                        |

|          | 0 = Interrupt is disabled                                                       |

| bit 22   | CHSHIE: Channel Source Half Empty Interrupt Enable bit                          |

|          | 1 = Interrupt is enabled                                                        |

|          | 0 = Interrupt is disabled                                                       |

| bit 21   | CHDDIE: Channel Destination Done Interrupt Enable bit                           |

|          | 1 = Interrupt is enabled                                                        |

|          | 0 = Interrupt is disabled                                                       |

| bit 20   | CHDHIE: Channel Destination Half Full Interrupt Enable bit                      |

|          | 1 = Interrupt is enabled                                                        |

|          | 0 = Interrupt is disabled                                                       |

| bit 19   | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                    |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |

| h:+ 40   |                                                                                 |

| bit 18   | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                     |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit                             |

|          | 1 = Interrupt is enabled                                                        |

|          | 0 = Interrupt is disabled                                                       |

| bit 16   | CHERIE: Channel Address Error Interrupt Enable bit                              |

|          | 1 = Interrupt is enabled                                                        |

|          | 0 = Interrupt is disabled                                                       |

| bit 15-8 | Unimplemented: Read as '0'                                                      |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                  |

|          | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)          |

|          | 0 = No interrupt is pending                                                     |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                            |

|          | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)   |

|          | 0 = No interrupt is pending                                                     |

|          |                                                                                 |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24     |                   |                   |                   | COUNTER           | <31:24>           |                   |                  |                  |

| 22:40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16     | COUNTER<23:16>    |                   |                   |                   |                   |                   |                  |                  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8      |                   |                   |                   | COUNTER           | R<15:8>           |                   |                  |                  |

| 7.0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0       |                   |                   |                   | COUNTE            | R<7:0>            |                   |                  |                  |

## REGISTER 16-5: DMTCNT: DEADMAN TIMER COUNT REGISTER

# Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-8 **COUNTER<31:0>:** Read current contents of DMT counter

## REGISTER 16-6: DMTPSCNT: POST STATUS CONFIGURE DMT COUNT STATUS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24     | PSCNT<31:24>      |                   |                   |                   |                   |                   |                  |                  |

| 22:16     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16     | PSCNT<23:16>      |                   |                   |                   |                   |                   |                  |                  |

| 15.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8      | PSCNT<15:8>       |                   |                   |                   |                   |                   |                  |                  |

| 7.0       | R-0               | R-0               | R-0               | R-y               | R-y               | R-y               | R-y              | R-y              |

| 7:0       |                   |                   |                   | PSCNT             | <7:0>             |                   |                  |                  |

| Legend:           |                  | y= Value set from Config | guration bits on POR |

|-------------------|------------------|--------------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit,   | read as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown   |

bit 31-8 **PSCNT<31:0>:** DMT Instruction Count Value Configuration Status bits

This is always the value of the DMTCNT<4:0> bits in the DEVCFG1 Configuration register.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 | —                 | _                 | _                 | —                 | _                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | DATAOUT           | <15:8>            |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| DATA         |                   |                   |                   | DATAOUT           | [<7:0>            |                   |                  |                  |

#### REGISTER 23-4: PMDOUT: PARALLEL PORT OUTPUT DATA REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 DATAOUT<15:0>: Port Data Output bits

This register is used for Read operations in the Enhanced Parallel Slave mode and Write operations for Dual Buffer Master mode.

In Dual Buffer Master mode, the DUALBUF bit (PMPCON<17>) = 1, a write to the MSB triggers the transaction on the PMP port. When MODE16 = 1, MSB = DATAOUT<15:8>. When MODE16 = 0, MSB = DATAOUT<7:0>.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   |                   |                   | DATAIN<           | 15:8>             |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | DATAIN<7:0>       |                   |                   |                   |                   |                   |                  |                  |

## REGISTER 23-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAIN<15:0>: Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode. In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port. When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note: This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

**Note:** In Master mode, a read will return the last value written to the register. In Slave mode, a read will return indeterminate results.

## REGISTER 25-2: ADCCON2: ADC CONTROL REGISTER 2 (CONTINUED)

bit 25-16 **SAMC<9:0>:** Sample Time for the Shared ADC (ADC7) bits

1111111111 = 1025 TAD . . . 00000000001 = 3 TAD

0000000000 = 2 TAD

Where  $T_{AD}$  = period of the ADC conversion clock for the Shared ADC (ADC7) controlled by the ADCDIV<6:0> bits.

**Note:** Unlike the High-Speed Class 1 ADC modules, the trigger event for the shared Class 3 ADC7 module initiates the SAMC *sampling* sequence, rather than the *convert* sequence.

Shared ADC7 Throughput rate:

= ((1/((Sample time + Conversion Time)(TAD))) / Number of ADC inputs used in scan list)

= ((1 / ((SAMC + Number of Bit Resolution + 1)(TAD))) / Number of ADC inputs used in scan list)

#### Example:

Scan mode enabled with two ANx inputs in the scan list (i.e., ADCCSSx<CSSy>), SAMC = 4 TAD, 12-bit mode, TAD = 16.667 ns = 60 MHz:

Throughput rate = ((1 / ((4+12 + 1)(16.667 ns))) / 2)

= ((1 / (17 \* 16.667 ns)) / 2)

- = 1.764706 msps

- bit 15 **BGVRIEN:** Band Gap/VREF Voltage Ready Interrupt Enable bit

- 1 = Interrupt will be generated when the BGVRDDY bit is set

- 0 = No interrupt is generated when the BGVRRDY bit is set

- bit 14 **REFFLTIEN:** Band Gap/VREF Voltage Fault Interrupt Enable bit

- 1 = Interrupt will be generated when the REFFLT bit is set

- 0 = No interrupt is generated when the REFFLT bit is set

- bit 13 **EOSIEN:** End of Scan Interrupt Enable bit

- 1 = Interrupt will be generated when EOSRDY bit is set

- 0 = No interrupt is generated when the EOSRDY bit is set

- bit 12 ADCEIOVR: Early Interrupt Request Override bit

- 1 = Early interrupt generation is overridden and interrupt generation is controlled by the ADCGIRQEN1 and ADCGIRQEN2 registers

- Early interrupt generation is not overridden and interrupt generation is controlled by the ADCEIEN1 and ADCEIEN2 registers

- bit 11 Unimplemented: Read as '0'

- bit 10-8 ADCEIS<2:0>: Shared ADC (ADC7) Early Interrupt Select bits

These bits select the number of clocks (TAD7) prior to the arrival of valid data that the associated interrupt is generated.

- 111 = The data ready interrupt is generated 8 ADC clocks prior to end of conversion

- 110 = The data ready interrupt is generated 7 ADC clocks prior to end of conversion

001 = The data ready interrupt is generated 2 ADC module clocks prior to end of conversion

- 000 = The data ready interrupt is generated 1 ADC module clock prior to end of conversion

- **Note:** All options are available when the selected resolution, set by the SELRES<1:0> bits (ADCCON1<22:21>), is 12-bit or 10-bit. For a selected resolution of 8-bit, options from '000' to '101' are valid. For a selected resolution of 6-bit, options from '000' to '011' are valid.

bit 7 Unimplemented: Read as '0'

| REGIS    | TER 25-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER                                                                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13   | STRGEN5: ADC5 Presynchronized Triggers bit                                                                                                                   |

|          | 1 = ADC5 uses presynchronized triggers                                                                                                                       |

|          | 0 = ADC5 does not use presynchronized triggers                                                                                                               |

| bit 12   | STRGEN4: ADC4 Presynchronized Triggers bit                                                                                                                   |

|          | 1 = ADC4 uses presynchronized triggers                                                                                                                       |

|          | 0 = ADC4 does not use presynchronized triggers                                                                                                               |

| bit 11   | STRGEN3: ADC3 Presynchronized Triggers bit                                                                                                                   |

|          | 1 = ADC3 uses presynchronized triggers                                                                                                                       |

| 1.11.4.0 | 0 = ADC3 does not use presynchronized triggers                                                                                                               |

| bit 10   | STRGEN2: ADC2 Presynchronized Triggers bit                                                                                                                   |

|          | 1 = ADC2 uses presynchronized triggers<br>0 = ADC2 does not use presynchronized triggers                                                                     |

| bit 9    | STRGEN1: ADC1 Presynchronized Triggers bit                                                                                                                   |

| DIL 9    | 1 = ADC1 uses presynchronized triggers                                                                                                                       |

|          | 0 = ADC1 does not use presynchronized triggers                                                                                                               |

| bit 8    | STRGEN0: ADC0 Presynchronized Triggers bit                                                                                                                   |

|          | 1 = ADC0 uses presynchronized triggers                                                                                                                       |

|          | 0 = ADC0 does not use presynchronized triggers                                                                                                               |

| bit 7-6  | Unimplemented: Read as '0'                                                                                                                                   |

| bit 5    | SSAMPEN5: ADC5 Synchronous Sampling bit                                                                                                                      |

|          | 1 = ADC5 uses synchronous sampling for the first sample after being idle or disabled                                                                         |

|          | 0 = ADC5 does not use synchronous sampling                                                                                                                   |

| bit 4    | SSAMPEN4: ADC4 Synchronous Sampling bit                                                                                                                      |

|          | 1 = ADC4 uses synchronous sampling for the first sample after being idle or disabled                                                                         |

|          | 0 = ADC4 does not use synchronous sampling                                                                                                                   |

| bit 3    | SSAMPEN3: ADC3 Synchronous Sampling bit                                                                                                                      |

|          | <ul> <li>1 = ADC3 uses synchronous sampling for the first sample after being idle or disabled</li> <li>0 = ADC3 does not use synchronous sampling</li> </ul> |

| bit 2    |                                                                                                                                                              |

|          | <b>SSAMPEN2:</b> ADC2Synchronous Sampling bit<br>1 = ADC2 uses synchronous sampling for the first sample after being idle or disabled                        |

|          | 0 = ADC2 does not use synchronous sampling                                                                                                                   |

| bit 1    | SSAMPEN1: ADC1 Synchronous Sampling bit                                                                                                                      |

|          | 1 = ADC1 uses synchronous sampling for the first sample after being idle or disabled                                                                         |

|          | 0 = ADC1 does not use synchronous sampling                                                                                                                   |

| bit 0    | SSAMPEN0: ADC0 Synchronous Sampling bit                                                                                                                      |

|          | 1 = ADC0 uses synchronous sampling for the first sample after being idle or disabled                                                                         |

|          | 0 = ADC0 does not use synchronous sampling                                                                                                                   |

|          |                                                                                                                                                              |

| Note 1   | <ul> <li>Regardless of which alternate input is selected by SHXALT for ADC0-ADC5 only all control and results and</li> </ul>                                 |

**Note 1:** Regardless of which alternate input is selected by SHxALT, for ADC0-ADC5 only, all control and results are handled by the native SHxALT = `0b00 input. For example, SH0ALT = `0b11 = AN24. However, from a software and silicon hardware control and results register perspective, the user must initialize the ADC0 module as if AN24 were actually AN0.

## 26.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

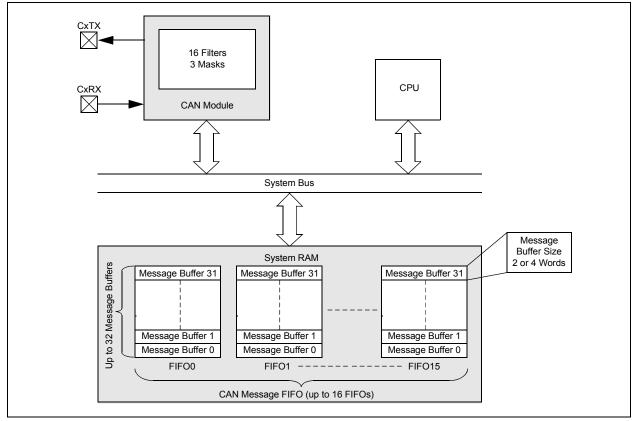

The Controller Area Network (CAN) module supports the following key features:

- · Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 16 message FIFOs

- Each FIFO can have up to 32 messages for a total of 512 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 16 acceptance filters for message filtering

- Three acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet<sup>™</sup> addressing support

- Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32MK system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 26-1 illustrates the general structure of the CAN module.

## FIGURE 26-1: PIC32MK CAN MODULE BLOCK DIAGRAM

## REGISTER 26-12: CxFLTCON2: CAN FILTER CONTROL REGISTER 2 ('x' = 1-4) (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit                                              |

|-----------|--------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                    |

|           | 0 = Filter is disabled                                                   |

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits                                    |

|           | 11 = Reserved                                                            |

|           | 10 = Acceptance Mask 2 is selected                                       |

|           | 01 = Acceptance Mask 1 is selected<br>00 = Acceptance Mask 0 is selected |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits                                          |

| 511 12 0  | 11111 = Message matching filter is stored in FIFO buffer 31              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30              |

|           | •                                                                        |

|           |                                                                          |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1          |

|           | 00000 = Message matching filter is stored in FIFO buffer 0               |

| bit 7     | FLTEN8: Filter 8 Enable bit                                              |

|           | 1 = Filter is enabled                                                    |

|           | 0 = Filter is disabled                                                   |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits                                    |

|           | 11 = Reserved                                                            |

|           | 10 = Acceptance Mask 2 is selected                                       |

|           | 01 = Acceptance Mask 1 is selected<br>00 = Acceptance Mask 0 is selected |

| bit 4-0   | FSEL8<4:0>: FIFO Selection bits                                          |

|           | 11111 = Message matching filter is stored in FIFO buffer 31              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30              |

|           | •                                                                        |

|           | •                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0               |

|           |                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 31-12: IOCONx: PWMX I/O CONTROL REGISTER 'x' ('x' = 1 THROUGH 12) (CONTINUED)

- bit 25 **CLPOL:** Current-Limit Polarity bits for PWM Generator 'x'<sup>(2,4)</sup>

- 1 = The selected current-limit source is active-low

- 0 = The selected current-limit source is active-high

- bit 24 **CLMOD:** Current-Limit Mode Enable bit for PWM Generator 'x'<sup>(2,4)</sup>

- 1 = Current-limit function is enabled

- 0 = Current-limit function is disabled, current-limit overrides disabled (current-limit interrupts can still be generated). If Faults are enabled, FLTMOD will override the CLMOD bit.

Changes take effect on the next PWM cycle boundary following PWM being enabled, and subsequently on each PWM cycle boundary. When updating CLMOD from '1' to '0', if the current-limit input is still active, the current-limit override condition will not be removed.

- bit 23 Unimplemented: Read as '0'

- Note 1: During PWM initialization, if the PWMLOCK fuse bit is 'enabled' (logic '0'), the control on the state of the PWMxL/PWMxH output pins rests solely with the PENH and PENL bits. However, these bits are at '0', which leaves the pin control with the I/O module. Care must be taken to not inadvertently set the TRIS bits to output, which could impose an incorrect output on the PWMxH/PWMxL pins even if there are external pull-up and pull-down resistors. The data direction for the pins must be set to input if tri-state behavior is desired or be driven to the appropriate logic states. The PENH and PENL bits must always be initialized prior to enabling the MCPWM module (PTEN bit = 1).

- 2: These bits must not be changed after the MCPWM module is enabled (PTEN bit = 1).

- 3: State represents Active/Inactive state of the PWM, depending on the POLH and POLL bits. For example, if FLTDAT<1> is set to '1' and POLH is set to '1', the PWMxH pin will be at logic level 0 (active level) when a Fault occurs.

- 4: If (PWMLOCK = 0), these bits are writable only after the proper sequence is written to the PWMKEY register. If (PWMLOCK = 1), these bits are writable at all times. The user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation for the IOCONx register if PWMLOCK = 1. Write access to a IOCONx register must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. This is not an atomic operation, and therefore, any CPU interrupts that occur during or immediately after an unlock sequence may cause the IOCONx SFR write access to fail.

Note: Dead Time Compensation, Current-Limit, and Faults share common inputs on the FLTx inputs ('x' = 1-8, and 15). Therefore, it is not recommended that a user application assign these multiple functions on the same Fault FLTx pin. In addition, DTCMP functions are fixed to specific FLTx inputs, where Current-Limit, (CLSRC<3:0> bits) and Faults (FLTSRC<3:0> bits) can be assigned to any one of 15 unique and separate inputs. For example, if a user application was required to assign multiple simultaneous Fault, Current-Limit, DTCMP to a single PWM1. Refer to the following examples for both desirable and undesirable practices.

**Desirable Example PWM1:** (DTCMP1 = FLT3 pin, Current Limit = FLT7 pin, Fault = FLT8 pin)

| <pre>PWMCON1bits.DTC = 0b11;</pre>                                 | <pre>//Enable DTCMP1 input on FLT3 function pin</pre> |

|--------------------------------------------------------------------|-------------------------------------------------------|

| IOCON1bits.CLMOD = 1;                                              | //Enable PWM1 Current-Limit mode                      |

| IOCON1bits.CLSRC = 0b0110;                                         | //Enable current limit for PWM1 on FLT7 pin           |

| IOCON1bits.FLTMOD = 1;                                             | //Enable PWM1 Fault mode                              |

| <b>Undesirable Example: PWM1: (DTCM</b><br>PWMCON1bits.DTC = 0b11; | //Enable DTCMP1 input on FLT3 function pin            |

| <pre>IOCON1bits.CLMOD = 1;</pre>                                   | //Enable PWM1 Current-Limit mode                      |

| IOCON1bits.CLSRC = 0b0010;                                         | //Enable current limit for PWM1 on FLT3 pin           |

| IOCON1bits.FLTMOD = 1;                                             | //Enable PWM1 Fault mode                              |

| IOCON1bits.FLTSRC = 0b0010;                                        | //Enable Fault for PWM1 on FLT3 pin                   |

## REGISTER 31-12: IOCONX: PWMX I/O CONTROL REGISTER 'x' ('x' = 1 THROUGH 12) (CONTINUED)

bit 22-19 **FLTSRC<3:0>:** Fault Control Signal Source Select bits for PWM Generator 'x'<sup>(2,4)</sup> These bits specify the Fault control source.

1111 **= FLT15**

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Comparator 5

- 1011 = Comparator 4

- 1010 = Comparator 3

- 1001 = Comparator 2 1000 = Comparator 1

- 0111 = FLT8

- 0111 = FLT8 0110 = FLT7

- 0110 = FLT70101 = FLT6

- 0100 = FLT5

- 0011 = FLT4

- 0010 = FLT3

- 00010 = FLT2

- 0000 = FLT1

- **Note 1:** During PWM initialization, if the PWMLOCK fuse bit is 'enabled' (logic '0'), the control on the state of the PWMxL/PWMxH output pins rests solely with the PENH and PENL bits. However, these bits are at '0', which leaves the pin control with the I/O module. Care must be taken to not inadvertently set the TRIS bits to output, which could impose an incorrect output on the PWMxH/PWMxL pins even if there are external pull-up and pull-down resistors. The data direction for the pins must be set to input if tri-state behavior is desired or be driven to the appropriate logic states. The PENH and PENL bits must always be initialized prior to enabling the MCPWM module (PTEN bit = 1).

- 2: These bits must not be changed after the MCPWM module is enabled (PTEN bit = 1).

- 3: State represents Active/Inactive state of the PWM, depending on the POLH and POLL bits. For example, if FLTDAT<1> is set to '1' and POLH is set to '1', the PWMxH pin will be at logic level 0 (active level) when a Fault occurs.

- 4: If (PWMLOCK = 0), these bits are writable only after the proper sequence is written to the PWMKEY register. If (PWMLOCK = 1), these bits are writable at all times. The user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation for the IOCONx register if PWMLOCK = 1. Write access to a IOCONx register must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. This is not an atomic operation, and therefore, any CPU interrupts that occur during or immediately after an unlock sequence may cause the IOCONx SFR write access to fail.

| Note: | and 15). Therefore, it is not recommen<br>same Fault FLTx pin. In addition, DTCM<br>(CLSRC<3:0> bits) and Faults (FLTSRC<br>inputs. For example, if a user application                                                                                                                                                                                                                                                  | hit, and Faults share common inputs on the FLTx inputs (' $x'$ = 1-8,<br>ded that a user application assign these multiple functions on the<br><i>I</i> P functions are fixed to specific FLTx inputs, where Current-Limit,<br>C<3:0> bits) can be assigned to any one of 15 unique and separate<br>n was required to assign multiple simultaneous Fault, Current-Limit,<br>e following examples for both desirable and undesirable practices. |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | Desirable Example PWM1: (DTCMP1 = FLT3 pin, Current Limit = FLT7 pin, Fault = FLT8 pin)<br>PWMCON1bits.DTC = 0b11; //Enable DTCMP1 input on FLT3 function pin<br>IOCON1bits.CLMOD = 1; //Enable PWM1 Current-Limit mode<br>IOCON1bits.CLSRC = 0b0110; //Enable current limit for PWM1 on FLT7 pin<br>IOCON1bits.FLTMOD = 1; //Enable PWM1 Fault mode<br>IOCON1bits.FLTSRC = 0b0111; //Enable Fault for PWM1 on FLT8 pin |                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|       | Undesirable Example: PWM1: (DTCM                                                                                                                                                                                                                                                                                                                                                                                        | /IP1 = Current Limit = Fault = FLT3 pin)                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|       | IOCON1bits.FLTMOD = 1;                                                                                                                                                                                                                                                                                                                                                                                                  | <pre>//Enable DTCMP1 input on FLT3 function pin<br/>//Enable PWM1 Current-Limit mode<br/>//Enable current limit for PWM1 on FLT3 pin<br/>//Enable PWM1 Fault mode<br/>//Enable Fault for PWM1 on FLT3 pin</pre>                                                                                                                                                                                                                                |  |  |  |  |  |  |

## REGISTER 31-24: LEBDLYx: LEADING-EDGE BLANKING DELAY REGISTER 'x' ('x' = 1 THROUGH 12)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24     | —                 | —                 | —                 |                   | _                 | _                 | _                | —                |  |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10     | —                 | —                 | —                 | _                 | —                 | _                 | _                | —                |  |

| 15:8      | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0      | —                 | —                 | —                 | -                 | LEB<11:8>         |                   |                  |                  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0       | LEB<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-12 Unimplemented: Read as '0'

bit 11-0 **LEB<11:0>:** Leading-Edge Blanking Delay bits for Current-Limit and Fault Inputs bits These bits specify the time period for which the selected current limit and fault signals are blanked or delayed following the selected edge transition of the PWM signals. This retriggerable counter has the PWM module clock source (SYSCLK) as the time base.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   |                   | —                 | —                 | _                | —                |