Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | CANbus, IrDA, LINbus, PMP, QEI, SPI, UART/USART, USB OTG                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, Motor Control PWM, WDT        |

| Number of I/O              | 49                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 27x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-QFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk0512mcf064t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 8-3: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interrupt Course(1)             |                               | IRQ Vester# |                  | Interrupt Bit Location |          |             |              |           |  |

|---------------------------------|-------------------------------|-------------|------------------|------------------------|----------|-------------|--------------|-----------|--|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name              | # Vector #  |                  | Flag                   | Enable   | Priority    | Sub-priority | Interrupt |  |

|                                 | Highest                       | Natura      | I Order Priority |                        |          |             |              |           |  |

| Core Timer Interrupt            | _CORE_TIMER_VECTOR            | 0           | OFF000<17:1>     | IFS0<0>                | IEC0<0>  | IPC0<4:2>   | IPC0<1:0>    | No        |  |

| Core Software Interrupt 0       | _CORE_SOFTWARE_0_VECTOR       | 1           | OFF001<17:1>     | IFS0<1>                | IEC0<1>  | IPC0<12:10> | IPC0<9:8>    | No        |  |

| Core Software Interrupt 1       | _CORE_SOFTWARE_1_VECTOR       | 2           | OFF002<17:1>     | IFS0<2>                | IEC0<2>  | IPC0<20:18> | IPC0<17:16>  | No        |  |

| External Interrupt 0            | _EXTERNAL_0_VECTOR            | 3           | OFF003<17:1>     | IFS0<3>                | IEC0<3>  | IPC0<28:26> | IPC0<25:24>  | No        |  |

| Timer1                          | _TIMER_1_VECTOR               | 4           | OFF004<17:1>     | IFS0<4>                | IEC0<4>  | IPC1<4:2>   | IPC1<1:0>    | No        |  |

| Input Capture 1 Error           | _INPUT_CAPTURE_1_ERROR_VECTOR | 5           | OFF005<17:1>     | IFS0<5>                | IEC0<5>  | IPC1<12:10> | IPC1<9:8>    | Yes       |  |

| Input Capture 1                 | _INPUT_CAPTURE_1_VECTOR       | 6           | OFF006<17:1>     | IFS0<6>                | IEC0<6>  | IPC1<20:18> | IPC1<17:16>  | Yes       |  |

| Output Compare 1                | _OUTPUT_COMPARE_1_VECTOR      | 7           | OFF007<17:1>     | IFS0<7>                | IEC0<7>  | IPC1<28:26> | IPC1<25:24>  | No        |  |

| External Interrupt 1            | _EXTERNAL_1_VECTOR            | 8           | OFF008<17:1>     | IFS0<8>                | IEC0<8>  | IPC2<4:2>   | IPC2<1:0>    | No        |  |

| Timer2                          | _TIMER_2_VECTOR               | 9           | OFF009<17:1>     | IFS0<9>                | IEC0<9>  | IPC2<12:10> | IPC2<9:8>    | No        |  |

| Input Capture 2 Error           | _INPUT_CAPTURE_2_ERROR_VECTOR | 10          | OFF010<17:1>     | IFS0<10>               | IEC0<10> | IPC2<20:18> | IPC2<17:16>  | Yes       |  |

| Input Capture 2                 | _INPUT_CAPTURE_2_VECTOR       | 11          | OFF011<17:1>     | IFS0<11>               | IEC0<11> | IPC2<28:26> | IPC2<25:24>  | Yes       |  |

| Output Compare 2                | _OUTPUT_COMPARE_2_VECTOR      | 12          | OFF012<17:1>     | IFS0<12>               | IEC0<12> | IPC3<4:2>   | IPC3<1:0>    | No        |  |

| External Interrupt 2            | _EXTERNAL_2_VECTOR            | 13          | OFF013<17:1>     | IFS0<13>               | IEC0<13> | IPC3<12:10> | IPC3<9:8>    | No        |  |

| Timer3                          | _TIMER_3_VECTOR               | 14          | OFF014<17:1>     | IFS0<14>               | IEC0<14> | IPC3<20:18> | IPC3<17:16>  | No        |  |

| Input Capture 3 Error           | _INPUT_CAPTURE_3_ERROR_VECTOR | 15          | OFF015<17:1>     | IFS0<15>               | IEC0<15> | IPC3<28:26> | IPC3<25:24>  | Yes       |  |

| Input Capture 3                 | _INPUT_CAPTURE_3_VECTOR       | 16          | OFF016<17:1>     | IFS0<16>               | IEC0<16> | IPC4<4:2>   | IPC4<1:0>    | Yes       |  |

| Output Compare 3                | _OUTPUT_COMPARE_3_VECTOR      | 17          | OFF017<17:1>     | IFS0<17>               | IEC0<17> | IPC4<12:10> | IPC4<9:8>    | No        |  |

| External Interrupt 3            | _EXTERNAL_3_VECTOR            | 18          | OFF018<17:1>     | IFS0<18>               | IEC0<18> | IPC4<20:18> | IPC4<17:16>  | No        |  |

| Timer4                          | _TIMER_4_VECTOR               | 19          | OFF019<17:1>     | IFS0<19>               | IEC0<19> | IPC4<28:26> | IPC4<25:24>  | No        |  |

| Input Capture 4 Error           | _INPUT_CAPTURE_4_ERROR_VECTOR | 20          | OFF020<17:1>     | IFS0<20>               | IEC0<20> | IPC5<4:2>   | IPC5<1:0>    | Yes       |  |

| Input Capture 4                 | _INPUT_CAPTURE_4_VECTOR       | 21          | OFF021<17:1>     | IFS0<21>               | IEC0<21> | IPC5<12:10> | IPC5<9:8>    | Yes       |  |

| Output Compare 4                | _OUTPUT_COMPARE_4_VECTOR      | 22          | OFF022<17:1>     | IFS0<22>               | IEC0<22> | IPC5<20:18> | IPC5<17:16>  | No        |  |

| External Interrupt 4            | _EXTERNAL_4_VECTOR            | 23          | OFF023<17:1>     | IFS0<23>               | IEC0<23> | IPC5<28:26> | IPC5<25:24>  | No        |  |

| Timer5                          | _TIMER_5_VECTOR               | 24          | OFF024<17:1>     | IFS0<24>               | IEC0<24> | IPC6<4:2>   | IPC6<1:0>    | No        |  |

| Input Capture 5 Error           | _INPUT_CAPTURE_5_ERROR_VECTOR | 25          | OFF025<17:1>     | IFS0<25>               | IEC0<25> | IPC6<12:10> | IPC6<9:8>    | Yes       |  |

| Input Capture 5                 | _INPUT_CAPTURE_5_VECTOR       | 26          | OFF026<17:1>     | IFS0<26>               | IEC0<26> | IPC6<20:18> | IPC6<17:16>  | Yes       |  |

| Output Compare 5                | _OUTPUT_COMPARE_5_VECTOR      | 27          | OFF027<17:1>     | IFS0<27>               | IEC0<27> | IPC6<28:26> | IPC6<25:24>  | No        |  |

| Reserved                        | —                             | 28          | —                | —                      | —        | —           | —            | —         |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MK General Purpose (GP) Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

**3:** This interrupt source is not available on 100-pin devices.

**REGISTER 8-7:** IPCx: INTERRUPT PRIORITY CONTROL REGISTER 'x' ('x' = 0-63) (CONTINUED)

bit 12-10 IP1<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 . 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 9-8 **IS1<1:0>:** Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Unimplemented: Read as '0' bit 7-5 bit 4-2 IP0<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 1-0 ISO<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Note: This register represents a generic definition of the IPCx register. Refer to Table 8-3 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | PLLODIV<2:0>      |                  |                  |  |  |

| 23:16        | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-y             | R/W-y             | R/W-y            | R/W-y            |  |  |

| 23.10        | —                 | PLLMULT<6:0>      |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |

| 10.0         | —                 |                   |                   |                   |                   | PLLIDIV<2:0>      |                  |                  |  |  |

| 7:0          | R/W-y             | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |

| 7:0          | PLLICLK           |                   | _                 | _                 |                   | PL                | LRANGE<2:        | 0>               |  |  |

## REGISTER 9-3: SPLLCON: SYSTEM PLL CONTROL REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

## bit 31-27 Unimplemented: Read as '0'

bit 26-24 PLLODIV<2:0>: System PLL Output Clock Divider bits

111 = Reserved 110 = Reserved 101 = PLL Divide by 32 100 = PLL Divide by 16 011 = PLL Divide by 8 010 = PLL Divide by 4 001 = PLL Divide by 2 000 = Reserved

The default setting is specified by the FPLLODIV<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "Special Features" for information.

## bit 23 Unimplemented: Read as '0'

bit 22-16 PLLMULT<6:0>: System PLL Multiplier bits

1111111 = Multiply by 128 1111110 = Multiply by 127 1111101 = Multiply by 126 1111100 = Multiply by 125

•

•

0000000 = Multiply by 1

The default setting is specified by the FPLLMULT<6:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "**Special Features**" for information.

## bit 15-11 Unimplemented: Read as '0'

| Note 1: | Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced |

|---------|-----------------------------------------------------------------------------------------------------|

|         | PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.                               |

| -       |                                                                                                     |

- 2: Writes to this register are not allowed if the SPLL is selected as a clock source (COSC<2:0> = 001).

- 3: While the PLL is active, and if updating the PLL bits in the OSCCON register at run-time, the user application must remain within the following limits at all times for all nodes in the PLL clock tree. Therefore, the order in which the PLL values may be modified, (i.e., PLLODIV, PLLMULT, PLLODIV) becomes important. Failure to maintain PLL nodes within min/max ranges may result in unstable PLL and system behavior.

- Output and input to PLLIDIV block (i.e., FPLLI) 5 MHz to 64 MHz (min/max at all times)

- VCO output, (i.e., FVCO) 350 MHz to 700 MHz (min/max at all times)

- Output of PLLODIV, (i.e., FPLL) 10 MHz to 120 MHz (min/max at all times)

# REGISTER 11-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

- 2: The maximum CRC length supported by the DMA module is 32.

- 3: This bit is unused when CRCTYP is equal to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | CHCSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 11-16: DCHxCSIZ: DMA CHANNEL x CELL-SIZE REGISTER

# Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

| RPnR SFR             | RPnR bits                                                                                          | RPnR Value to Peripheral<br>Selection                                                                               |

|----------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| RPB6R                | RPB6R<4:0>                                                                                         | 00000 = Off<br>00001 = U3TX                                                                                         |

| RPC15R               | RPC15R<4:0>                                                                                        | 00010 = <u>U4R</u> TS<br>00011 = SS1                                                                                |

| RPA4R                | RPA4R<4:0>                                                                                         | 00100 = Reserved<br>00101 = OC4                                                                                     |

| RPB13R               | RPB13R<4:0>                                                                                        | 00110 = OC5<br>00111 = REFCLKO1                                                                                     |

| RPB2R                | RPB2R<4:0>                                                                                         | 01000 = C5OUT<br>01001 = OC10                                                                                       |

| RPC6R                | RPC6R<4:0>                                                                                         | 01010 = OC14<br>01011 = U6TX                                                                                        |

| RPC1R                | RPC1R<4:0>                                                                                         | 01100 = C3TX<br>01101 = Reserved                                                                                    |

| RPA7R                | RPA7R<4:0>                                                                                         | $01110 = \frac{SS3}{SS4}$<br>$01111 = \frac{SS4}{SS4}$                                                              |

| RPE14R               | RPE14R<4:0>                                                                                        | 10000 = SS5<br>10001 = SDO6                                                                                         |

| RPG8R                | RPG8R<4:0>                                                                                         | 10010 = REFCLKO2<br>10011 = Reserved                                                                                |

| RPF0R                | RPF0R<4:0>                                                                                         | 10100 = QEICMP3<br>10101 = Reserved                                                                                 |

| RPD4R <sup>(1)</sup> | RPD4R<4:0> (1)                                                                                     | •<br>•<br>11111 = Reserved                                                                                          |

|                      | RPC15R<br>RPA4R<br>RPB13R<br>RPB2R<br>RPC6R<br>RPC1R<br>RPC1R<br>RPA7R<br>RPE14R<br>RPG8R<br>RPF0R | RPC15R       RPC15R<4:0>         RPA4R       RPA4R<4:0>         RPB13R       RPB13R<4:0>         RPB2R       RPB2R< |

# TABLE 13-2: OUTPUT PIN SELECTION (CONTINUED)

Note 1: This selection is not available on 64-pin devices.

# **REGISTER 22-1: UXMODE: UARTX MODE REGISTER (CONTINUED)**

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits<sup>(2)</sup>

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- bit 5 ABAUD: Auto-Baud Enable bit

- 1 = Enable baud rate measurement on the next reception of Sync character (0x55); cleared by hardware upon completion

- 0 = Baud rate measurement disabled or completed

- bit 4 RXINV: Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 **BRGH:** High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- Note 1: These bits can be changed only when the ON bit (UxMODE<15>) is set to '0'.

- 2: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see 13.3 "Peripheral Pin Select (PPS)" for more information).

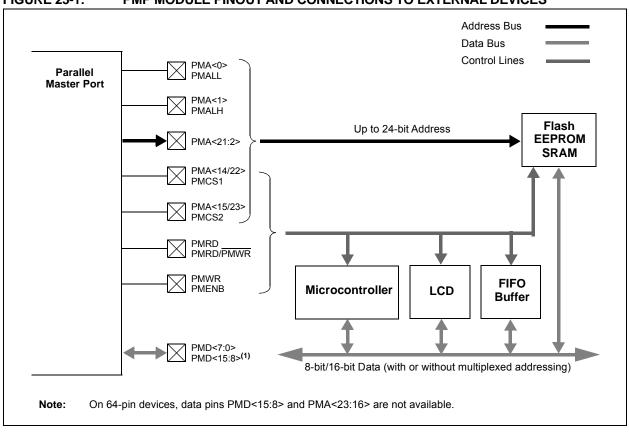

# PIC32MK GP/MC Family

## FIGURE 23-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        |                   |                   |                   | TRGSRC3<4:0>      |                   |                   |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | —                 | —                 |                   | Т                 | RGSRC2<4:0>       |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | _                 | —                 | —                 | TRGS              |                   | RGSRC1<4:0        | 31<4:0>          |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          |                   |                   |                   | TRGSRC0<4:0>      |                   |                   |                  |                  |  |

## REGISTER 25-18: ADCTRG1: ADC TRIGGER SOURCE 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                |

|-------------------|------------------|------------------------------------|----------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x =           | Bit is unknown |

## bit 31-29 Unimplemented: Read as '0'

bit 28-24 TRGSRC3<4:0>: Trigger Source for Conversion of ADC3 Module Select bits

- 11111 = Reserved 11110 = Reserved 11101 = PWM Generator 6 Current-Limit (Motor Control Variants Only) 11100 = PWM Generator 5 Current-Limit (Motor Control Variants Only) 11011 = PWM Generator 4 Current-Limit (Motor Control Variants Only) 11010 = PWM Generator 3 Current-Limit (Motor Control Variants Only) 11001 = PWM Generator 2 Current-Limit (Motor Control Variants Only) 11000 = PWM Generator 1 Current-Limit (Motor Control Variants Only) 10111 = Reserved 10110 = Reserved 10101 = Reserved 10100 = CTMU trip 10011 = Output Compare 4 (Rising Edge Only) 10010 = Output Compare 3 (Rising Edge Only) 10001 = Output Compare 2 (Rising Edge Only) 10000 = Output Compare 1 (Rising Edge Only) 01111 = PWM Generator 6 trigger (Motor Control Variants Only) 01110 = PWM Generator 5 trigger (Motor Control Variants Only) 01101 = PWM Generator 4 trigger (Motor Control Variants Only) 01100 = PWM Generator 3 trigger (Motor Control Variants Only) 01011 = PWM Generator 2 trigger (Motor Control Variants Only) 01010 = PWM Generator 1 trigger (Motor Control Variants Only) 01001 = Secondary Special Event trigger (Motor Control Variants Only) 01000 = Primary Special Event trigger (Motor Control Variants Only) 00111 = General Purpose Timer5 00110 = General Purpose Timer3 00101 = General Purpose Timer1 00100 = INTO 00011 = Scan trigger (see Note) 00010 = Software level trigger 00001 = Software edge trigger 00000 = No Trigger

- **Note:** For Scan Trigger, in addition to setting the trigger, it also requires programming of the STRGSRC<4:0> bits (ADCCON1<20:16>) to select the trigger source, and requires the appropriate CSS bits to be set in the ADCCSSx registers.

bit 23-21 Unimplemented: Read as '0'

#### **REGISTER 26-9:** CxRXMn: CAN ACCEPTANCE FILTER MASK 'n' REGISTER ('x' = 1-4 ' n' = 0, 1, 2 OR 3)

|              | (x = 1-4; n = 0, 1, 2  OR  3) |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        |                               |                   |                   | SID<1             | 0:3>              |                   |                  |                  |  |  |

| 23:16        | R/W-0                         | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |

| 23.10        | SID<2:0>                      |                   |                   | -                 | MIDE              | —                 | EID<             | 17:16>           |  |  |

| 15:8         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | EID<15:8>                     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                               |                   |                   | EID<              | 7:0>              |                   |                  |                  |  |  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include the SIDx bit in filter comparison

- 0 = The SIDx bit is a 'don't care' in filter operation

## bit 20 Unimplemented: Read as '0'

## bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

- Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

## bit 18 Unimplemented: Read as '0'

## bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include the EIDx bit in filter comparison

- 0 = The EIDx bit is a 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CxCON<23:21>) = 100).

# PIC32MK GP/MC Family

#### REGISTER 26-16: CxFIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('x' = 1-4:'n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-----------------------|-----------------------|---------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0                   | U-0                   | U-0                       | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | —                     | —                     | _                         | _                 | _                 | —                | _                |  |  |  |

| 23:16        | U-0               | U-0                   | U-0                   | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | _                 | —                     | —                     | FSIZE<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |

| 15:8         | U-0               | S/HC-0                | S/HC-0                | R/W-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 10.0         | _                 | FRESET                | UINC                  | DONLY <sup>(1)</sup>      | _                 | -                 | -                | _                |  |  |  |

| 7:0          | R/W-0             | R-0                   | R-0                   | R-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup>      | TXREQ             | RTREN             | TXPR             | <1:0>            |  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-21 Unimplemented: Read as '0'

- bit 20-16 FSIZE<4:0>: FIFO Size bits<sup>(1)</sup>

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep

- 00001 = FIFO is 2 messages deep

- 00000 = FIFO is 1 message deep

- bit 15 Unimplemented: Read as '0'

- bit 14 FRESET: FIFO Reset bits

- 1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

- 0 = No effect

## bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{FIFO}$  (FIFO configured as a Transmit FIFO) When this bit is set the FIFO head will increment by a single message  $\frac{TXEN = 0:}{FIFO}$  (FIFO configured as a Receive FIFO) When this bit is set the FIFO tail will increment by a single message

# bit 12 **DONLY:** Store Message Data Only bit<sup>(1)</sup>

<u>TXEN = 1:</u> (FIFO configured as a Transmit FIFO) This bit is not used and has no effect.

TXEN = 0: (FIFO configured as a Receive FIFO)

- 1 = Only data bytes will be stored in the FIFO

- 0 = Full message is stored, including identifier

- bit 11-8 Unimplemented: Read as '0'

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CxCON<23:21>) = 100).

- **2:** This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

# REGISTER 30-1: QEIXCON: QEIX CONTROL REGISTER (CONTINUED)

- bit 6-4 **INTDIV<2:0>:** Timer Input Clock Prescale Select bits (Interval timer, Main timer (position counter), velocity counter and index counter internal clock divider select)<sup>(3)</sup>

- 111 = 1:128 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- bit **CNTPOL:** Position and Index Counter/Timer Direction Select bit

- 1 = Counter direction is negative unless modified by external Up/Down signal

- 0 = Counter direction is positive unless modified by external Up/Down signal

- bit GATEN: External Count Gate Enable bit

- 1 = External gate signal controls position counter operation

- 0 = External gate signal does not affect position counter/timer operation

## bit CCM<1:0>: Counter Control Mode Selection bits

- 11 = Internal Timer mode with optional QEB external clock gating input control based on GATEN. QEB High = Timer Run, QEB Low = Timer Stop.

- 10 = QEA is the external clock input, QEB is optional clock gating input control based on GATEN. QEB High = Clock Run, QEB Low = Clock Stop.

- 01 = QEA is the external clock input, QEB is external UP/DN direction input. QEB High = Count Up, QEB Low = Count Down

- 00 = Quadrature Encoder Interface Count mode (x4 mode)

- **Note 1:** When CCM equals modes '01', '10', and '11', all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.

- 2: When CCM = 00 and QEA and QEB values match Index Match Value (IMV), the POSxCNTH and POSxCNTL registers are reset.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | VELHLD            | )<31:24>          |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | VELHLD<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | VELHLD<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | VELHL             | D<7:0>            |                   |                  |                  |  |  |

# REGISTER 30-6: VELxHLD: VELOCITY HOLD REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-0 VELHLD<31:0>: 32-bit Velocity Hold bits

When VELxCNT is read, the contents are captured at the same time into the VELxHLD register.

| CEGISTER 30-7. INTERED. INTERVAL TIMER HOLD REGISTER |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range                                         | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24                                                | INTHLD<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40                                                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16                                                | INTHLD<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8                                                 | INTHLD<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0                                                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|                                                      |                   |                   |                   | INTHL             | D<7:0>            |                   |                  | •                |  |  |  |

# REGISTER 30-7: INTxHLD: INTERVAL TIMER HOLD REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 INTHLD<31:0>: 32-bit Index Counter Hold bits

When the next count pulse is detected, the current contents of the interval timer (INTxTMR) are transferred to the Interval Hold register (INTxHLD) and the interval timer is cleared and the process repeats.

# REGISTER 33-4: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Reserved

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = USB PLL (UPLL Module) (input clock and divider set by UPLLCON)

- 010 = Primary Oscillator (Posc) (HS, EC)

- 001 = System PLL (SPLL Module) (input clock and divider set by SPLLCON)

- 000 = Fast RC Oscillator (FRC) divided by the FRCDIV<2:0> bits (OSCCON<26:24>) (supports FRC / n, where n = 1, 2, 4, 8, 16, 32, 64, 256

# 35.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 35.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 35.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 35.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 35.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 36.2 AC Characteristics and Timing Parameters

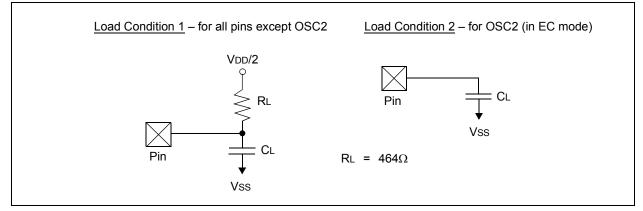

The information contained in this section defines PIC32MK GP/MC device AC characteristics and timing parameters.

# FIGURE 36-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## TABLE 36-14: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHA        | AC CHARACTERISTICS |                 |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.2V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |            |  |

|---------------|--------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| Param.<br>No. | Symbol             | Characteristics | Min. | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Max. | Units | Conditions |  |

| DO56          | CL                 | All I/O pins    |      | _                                                                                                                                                                                                                                                                                     | 50   | pF    | _          |  |

**Note 1:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

# TABLE 36-25: TIMER2-TIMER9 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS |                          |                                |                  | d Operating Conditions:<br>otherwise stated)<br>Ig temperature $-40^{\circ}C \le -40^{\circ}C \le$ | ≦ TA ≤ + |                       |                                        |                                                      |  |

|---------------|--------------------|--------------------------|--------------------------------|------------------|----------------------------------------------------------------------------------------------------|----------|-----------------------|----------------------------------------|------------------------------------------------------|--|

| Param.<br>No. | Symbol             | Cha                      | racteristic                    | s <sup>(1)</sup> | Min.                                                                                               | Max.     | Max. Units Conditions |                                        |                                                      |  |

| TB10          | ТтхН               | TxCK<br>High Time        | Synchronous, with<br>prescaler |                  | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                             | —        | ns                    | Must also<br>meet<br>parameter<br>TB15 | N = prescale<br>value<br>(1, 2, 4, 8,<br>16, 32, 64, |  |

| TB11          | TTXL               | TxCK<br>Low Time         | Synchron<br>prescaler          | ous, with        | [(12.5 ns or 1 TPBCLK3)<br>/N] + 25 ns                                                             | _        | ns                    | Must also<br>meet<br>parameter<br>TB15 | 256)                                                 |  |

| TB15          | T⊤xP               | TxCK<br>Input            | Synchron<br>prescaler          | ous, with        | [(Greater of [(25 ns or<br>2 TPBCLK3)/N] + 30 ns                                                   | —        | ns                    | VDD > 2.7V                             |                                                      |  |

|               | Period             |                          |                                |                  | [(Greater of [(25 ns or<br>2 TPBCLK3)/N] + 50 ns                                                   | —        | ns                    | VDD < 2.7V                             |                                                      |  |

| TB20          | TCKEXTMRL          | Delay from<br>Clock Edge |                                |                  | —                                                                                                  | 1        | TPBCLK3               |                                        | _                                                    |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

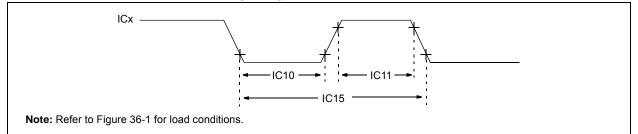

## FIGURE 36-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

# TABLE 36-26: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHA        | RACTER | ISTICS                 | (unless of               | Operating Conditions: 2herwise stated)temperature $-40^{\circ}C \le TA$ $-40^{\circ}C \le TA$ | ×≤+85° | C for In |                                      |                                                                |

|---------------|--------|------------------------|--------------------------|-----------------------------------------------------------------------------------------------|--------|----------|--------------------------------------|----------------------------------------------------------------|

| Param.<br>No. | Symbol | Charac                 | teristics <sup>(1)</sup> | Min.                                                                                          | Max.   | Units    | Conditions                           |                                                                |

| IC10          | TccL   | ICx Input Low<br>Time  |                          | ((TPBCLKx/N) + 25 ns)                                                                         |        | ns       | Must also meet<br>parameter<br>IC15. | x = 2 for IC1-IC9<br>x = 3 for IC10-IC16<br>N = prescale value |

| IC11          | ТссН   | ICx Input High<br>Time |                          | ((TPBCLKx/N) + 25 ns)                                                                         | _      | ns       | Must also meet<br>parameter<br>IC15. | (1, 4, 16)                                                     |

| IC15          | TCCP   | ICx Inp                | ut Period                | ((TPBCLKx/N) + 50 ns)                                                                         | _      | ns       | —                                    |                                                                |

| Note 1: | These parameters are | characterized, but | not tested in m | anufacturing. |

|---------|----------------------|--------------------|-----------------|---------------|

|         |                      |                    |                 |               |

| AC CHA        | AC CHARACTERISTICS <sup>(2)</sup> |                                                            |                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.2V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                               |                              |                                                                                                                                                                                                                                                                           |  |

|---------------|-----------------------------------|------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol                            | Characteristics                                            | Min.                  | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                                     | Max.                          | Units                        | Conditions                                                                                                                                                                                                                                                                |  |

| Clock P       | arameter                          | S                                                          |                       |                                                                                                                                                                                                                                                                                         |                               |                              |                                                                                                                                                                                                                                                                           |  |

| AD50          | Tad                               | ADC Clock Period                                           | 16.667                | _                                                                                                                                                                                                                                                                                       | 6250                          | ns                           | —                                                                                                                                                                                                                                                                         |  |

| Through       | nput Rate                         | •                                                          |                       |                                                                                                                                                                                                                                                                                         |                               |                              |                                                                                                                                                                                                                                                                           |  |

| AD51          | Ftp                               | Sample Rate for<br>ADC0-ADC5<br>(Class 1 Inputs)           | <br>                  | <br>                                                                                                                                                                                                                                                                                    | 3.75<br>4.284<br>4.992<br>6   | Msps<br>Msps<br>Msps<br>Msps | 12-bit resolution Source Impedance $\leq 200\Omega$ 10-bit resolution Source Impedance $\leq 200\Omega$ 8-bit resolution Source Impedance $\leq 200\Omega$ 6-bit resolution Source Impedance $\leq 200\Omega$                                                             |  |

|               |                                   | Sample Rate for<br>ADC7<br>(Class 2 and Class<br>3 Inputs) | <br> <br>             |                                                                                                                                                                                                                                                                                         | 3.53<br>4.00<br>4.615<br>5.45 | Msps<br>Msps<br>Msps<br>Msps | $\begin{array}{l} \mbox{12-bit resolution Source Impedance} \leq 200\Omega \\ \mbox{10-bit resolution Source Impedance} \leq 200\Omega \\ \mbox{8-bit resolution Source Impedance} \leq 200\Omega \\ \mbox{6-bit resolution Source Impedance} \leq 200\Omega \end{array}$ |  |

| Timing        | Paramete                          | ers                                                        |                       |                                                                                                                                                                                                                                                                                         |                               |                              |                                                                                                                                                                                                                                                                           |  |

| AD60          | TSAMP                             | Sample Time for<br>ADC0-ADC5<br>(Class 1 Inputs)           | 3<br>4<br>5<br>13     | _                                                                                                                                                                                                                                                                                       | _                             | Tad                          | Source Impedance $\leq 200\Omega$ , Max ADC clock<br>Source Impedance $\leq 500\Omega$ , Max ADC clock<br>Source Impedance $\leq 1 \text{ K}\Omega$ , Max ADC clock<br>Source Impedance $\leq 5 \text{ K}\Omega$ , Max ADC clock                                          |  |

|               |                                   | Sample Time for<br>ADC7<br>(Class 2 and Class<br>3 Inputs) | 4<br>5<br>6<br>14     | _                                                                                                                                                                                                                                                                                       | _                             | Tad                          | Source Impedance $\leq 200\Omega$ , Max ADC clock<br>Source Impedance $\leq 500\Omega$ , Max ADC clock<br>Source Impedance $\leq 1 \text{ K}\Omega$ , Max ADC clock<br>Source Impedance $\leq 5 \text{ K}\Omega$ , Max ADC clock                                          |  |

|               |                                   | Sample Time for<br>ADC7<br>(Class 2 and Class<br>3 Inputs) | See<br>Table<br>36-41 | _                                                                                                                                                                                                                                                                                       | _                             | Tad                          | CVDEN (ADCCON1<11>) = 1                                                                                                                                                                                                                                                   |  |

| AD62          | TCONV                             | Conversion Time<br>(after sample time is<br>complete)      |                       |                                                                                                                                                                                                                                                                                         | 13<br>11<br>9<br>7            | Tad                          | 12-bit resolution<br>10-bit resolution<br>8-bit resolution<br>6-bit resolution                                                                                                                                                                                            |  |

| AD65          | Twake                             | Wake-up time from<br>Low-Power Mode                        |                       | 500<br>20                                                                                                                                                                                                                                                                               |                               | Tad<br>μs                    | Lesser of 500 Tad or 20 µs                                                                                                                                                                                                                                                |  |

# TABLE 36-40: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is guaranteed, but not characterized.

# Revision E (April 2018)

This revision includes the following major changes, which are referenced by their respective chapter in Table A-3.

In addition, minor updates to text and formatting were incorporated throughout the document.

# TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                             | Update Description                                                                                                                                                                                                       |  |  |  |  |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "32-bit General Purpose and                                                              | The 120 MHz Operating Conditions were updated.                                                                                                                                                                           |  |  |  |  |  |

| Motor Control Application MCUs                                                           | Secure boot was removed from the Security Features.                                                                                                                                                                      |  |  |  |  |  |

| with FPU and up to 1 MB Live-<br>Update Flash, 256 KB SRAM, 4<br>KB EEPROM, and Op amps" | The FRC internal oscillator Clock Management operating conditions were updated.                                                                                                                                          |  |  |  |  |  |

|                                                                                          | The number of ADC channels for 64-pin TQFP and QFN Motor Control devices was updated (see Table 2).                                                                                                                      |  |  |  |  |  |

| 1.0 "Device Overview"                                                                    | The I2Cx and PLVD references were removed from the PIC32MK GP/MC Family Block Diagram (see Figure 1-1).                                                                                                                  |  |  |  |  |  |

| 5.0 "Flash Program Memory"                                                               | The Wait state bits, LPRDWS<4:0> (NVMCON2), were updated to include a table with low-power Wait state information (see Register 5-8).                                                                                    |  |  |  |  |  |

| 10.0 "Prefetch Module"                                                                   | The Wait states table in the PFMWS<2:0> bits (CHECON<2:0>) was updated (see Register 10-1).                                                                                                                              |  |  |  |  |  |

| 11.0 "Direct Memory Access<br>(DMA) Controller"                                          | A note was added to the CHSIRQ<7:0> bits (DCHxECON<15:8>) (see Register 11-8).                                                                                                                                           |  |  |  |  |  |

| 14.0 "Timer1"                                                                            | The Timer1 Block Diagram was updated (see Figure 14-1).                                                                                                                                                                  |  |  |  |  |  |

| 15.0 "Timer2 Through Timer9"                                                             | The Timer2-Timer9 Block Diagram was updated (see Figure 15-1).                                                                                                                                                           |  |  |  |  |  |

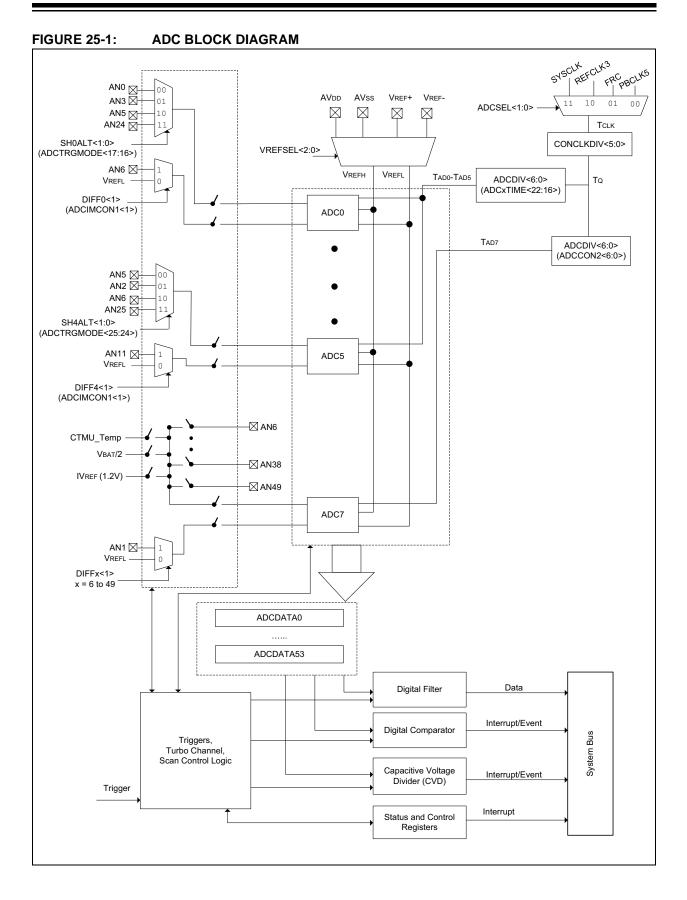

| 25.0 "12-bit High-Speed                                                                  | The Step 7 was updated (see 25.1 "Activation Sequence").                                                                                                                                                                 |  |  |  |  |  |

| Successive Approximation<br>Register (SAR) Analog-to-Digital<br>Converter (ADC)"         | Table 25-1: "PIC32MKXXX Based on a 60 MHz TAD clock (16.667 ns)" was updated.                                                                                                                                            |  |  |  |  |  |

|                                                                                          | IVTEMP references were removed from the:                                                                                                                                                                                 |  |  |  |  |  |

|                                                                                          | ADC Block Diagram (see Figure 25-1)                                                                                                                                                                                      |  |  |  |  |  |

|                                                                                          | <ul> <li>S&amp;H Block Diagram (see Figure 25-2)</li> </ul>                                                                                                                                                              |  |  |  |  |  |

|                                                                                          | ADC Register Map (see Table 25-2)                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                          | The ADCDATA51 register was removed (see Table 25-2).                                                                                                                                                                     |  |  |  |  |  |

|                                                                                          | The ADCCON2 register was updated (see Register 25-12).                                                                                                                                                                   |  |  |  |  |  |

|                                                                                          | The following bits were removed:                                                                                                                                                                                         |  |  |  |  |  |

|                                                                                          | <ul> <li>CSS51 (see Table 25-2 and Register 25-12)</li> <li>ARDY51 (see Table 25-2 and Register 25-14)</li> <li>EIRDY51 (see Table 25-2 and Register 25-37)</li> <li>AN51 (see Table 25-2 and Register 25-41)</li> </ul> |  |  |  |  |  |

|                                                                                          | The definition for bit value '110011' in the ADINSEL<5:0> bits in the ADC Control Register 3 was updated to Reserved (see Register 25-3).                                                                                |  |  |  |  |  |

|                                                                                          | A Note was added to the TRGSRC3<4:0> bits in the ADC Trigger Source x Registers (see Register 25-18 through Register 25-24).                                                                                             |  |  |  |  |  |

|                                                                                          | The definition for bit value '110101' in the AINID<5:0> bits in the ADC Digital Comparator 1 Control Register 3 was updated to Reserved (see Register 25-25).                                                            |  |  |  |  |  |

|                                                                                          | The definition for the LVL27:LVL0 bits in the ADC Trigger Level/Edge Sensitivity Register was updated (see Register 25-32).                                                                                              |  |  |  |  |  |