Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | CANbus, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 77                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 4K x 8                                                                            |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 42x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk1024gpe100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

1

#### TABLE 5: PIN NAMES FOR 100-PIN GENERAL PURPOSE (GPD/GPE) DEVICES

### **100-PIN TQFP (TOP VIEW)**

### PIC32MK0512GPD100 PIC32MK0512GPE100 PIC32MK1024GPD100 PIC32MK1024GPE100

| 1 | 00 |  |

|---|----|--|

|   |    |  |

Pin # Full Pin Name 1 AN23/PMA23/RG15 2 Vdd 3 TCK/RPA7/PMD5/RA7 4 RPB14/VBUSON1/PMD6/RB14 5 RPB15/PMD7/RB15 RD1 6 7 RD2 RPD3/RD3 8 RPD4/RD4 9 AN19/RPG6/VBUSON2/PMA5/RG6 10 AN18/RPG7/1/PMA4/RG7<sup>(5)</sup> 11 AN17/RPG8//PMA3/RG8(6) 12 13 MCLR AN16/RPG9/PMA2/RG9 14 15 Vss 16 VDD 17 AN22/RG10 AN21/RE8 18 19 AN20/RE9 20 AN10/RPA12/RA12 21 AN9/RPA11/RA11 OA2OUT/AN0/C2IN4-/C4IN3-/RPA0/RA0 22 OA2IN+/AN1/C2IN1+/RPA1/RA1 23 PGED3/OA2IN-/AN2/C2IN1-/RPB0/CTED2/RB0 24 25 PGEC3/OA1OUT/AN3/C1IN4-/C4IN2-/RPB1/CTED1/RB1 26 PGEC1/OA1IN+/AN4/C1IN1+/C1IN3-/C2IN3-/RPB2/RB2 PGED1/OA1IN-/AN5/CTCMP/C1IN1-/RTCC/RPB3/RB3 27 28 VREF-/AN33/PMA7/RF9 29 VREF+/AN34/PMA6/RF10 30 AVDD 31 AVss 32 OA3OUT/AN6/C3IN4-/C4IN1+/C4IN4-/RPC0/RC0 OA3IN-/AN7/C3IN1-/C4IN1-/RPC1/RC1 33 OA3IN+/AN8/C3IN1+/C3IN3-/RPC2/PMA13/RC2 34 35 AN11/C1IN2-/PMA12/RC11

| Pin #             | Full Pin Name                                 |

|-------------------|-----------------------------------------------|

| 36                | Vss                                           |

| 37                | Vdd                                           |

| 38                | AN35/RG11                                     |

| 39                | AN36/RF13                                     |

| 40                | AN37/RF12                                     |

| 41 <sup>(6)</sup> | AN12/C2IN2-/C5IN2-/PMA11/RE12                 |

| 42 <sup>(5)</sup> | AN13/C3IN2-/PMA10/RE13                        |

| 43                | AN14/RPE14/PMA1/RE14                          |

| 44                | AN15/RPE15/PMA0/RE15                          |

| 45                | Vss                                           |

| 46                | Vdd                                           |

| 47                | AN38/RD14                                     |

| 48                | AN39/RD15                                     |

| 49                | TDI/CDAC3/AN26/RPA8/PMA9/RA8 <sup>(6)</sup>   |

| 50                | RPB4/PMA8/RB4 <sup>(5)</sup>                  |

| 51                | OA5IN+/CDAC1/AN24/C5IN1+/C5IN3-/RPA4/T1CK/RA4 |

| 52                | AN40/RPE0/RE0                                 |

| 53                | AN41/RPE1/RE1                                 |

| 54                | VBUS1                                         |

| 55                | VUSB3V3                                       |

| 56                | D1-                                           |

| 57                | D1+                                           |

| 58                | VBUS2                                         |

| 59                | D2-                                           |

| 60                | D2+                                           |

| 61                | AN45/RF5                                      |

| 62                | Vdd                                           |

| 63                | OSC1/CLKI/AN49/RPC12/RC12                     |

| 64                | OSC2/CLKO/RPC15/RC15                          |

| 65                | Vss                                           |

| 66                | AN46/RPA14/RA14                               |

| 67                | AN47/RPA15/RA15                               |

| 68                | VBAT <sup>(7)</sup>                           |

| 69                | PGED2/RPB5/USBID1/RB5 <sup>(6)</sup>          |

| 70                | PGEC2/RPB6/SCK2/PMA15/RB6 <sup>(5)</sup>      |

The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 13.3 "Peripheral Pin Select (PPS)" Note 1: for restrictions.

Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See 13.0 "I/O Ports" for more information. 2:

3: Shaded pins are 5V tolerant.

Functions are restricted to input functions only and inputs will be slower than standard inputs. 4:

The I<sup>2</sup>C library is available in MPLAB Harmony. For future hardware or silicon compatibility, it is recommended to use these pins for the 5: I<sup>2</sup>C master/slave clock. (i.e., SCL).

The I<sup>2</sup>C library is available in MPLAB Harmony. For future hardware or silicon compatibility, it is recommended to use these pins for the 6: I<sup>2</sup>C data I/O, (i.e., SDA).

7: VBAT functionality is compromised, see errata for additional information. This pin should be connected to VDD.

### 2.4 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For additional information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

### 2.5 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

### 2.6 Trace

When present on select pin counts, the trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

### 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

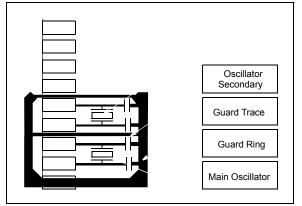

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# FIGURE 4-3: BOOT AND ALIAS MEMORY MAP

| Physical I              | Memory Map <sup>(1)</sup>                                     |                |  |  |

|-------------------------|---------------------------------------------------------------|----------------|--|--|

| -                       |                                                               | 0x1FC64FFF     |  |  |

|                         |                                                               | 0x1FC64000     |  |  |

|                         | Seq/Configuration                                             | 0x1FC63FFF     |  |  |

| Boot Flash 2            | Word Space                                                    | 0x1FC63FB0     |  |  |

|                         |                                                               | 0x1FC63FAC     |  |  |

|                         |                                                               | 0x1FC60000     |  |  |

|                         |                                                               | 0x1FC5FFFF     |  |  |

|                         |                                                               |                |  |  |

| R                       | eserved                                                       |                |  |  |

|                         |                                                               | 0x1FC45800     |  |  |

|                         |                                                               | 0x1FC457FF     |  |  |

|                         |                                                               | 0x1FC45040     |  |  |

|                         | DATA EE CAL                                                   | 0x1FC4503C     |  |  |

|                         | (DEVEE0-DEVEE3)                                               | 0x1FC45030     |  |  |

|                         | <u></u>                                                       | 0x1FC4502F     |  |  |

|                         | Device Serial Number <sup>(4)</sup>                           | 0x1FC4502C     |  |  |

|                         | DEVSNx, x=0-3                                                 | 0x1FC45020     |  |  |

| Public Test Flash       | - ,                                                           | 0x1FC4501C     |  |  |

| FUDIIC TEST FIASIT      |                                                               | 0x1FC4501C     |  |  |

|                         | DEVADC7<br>DEVADC5                                            | 0x1FC45016     |  |  |

|                         |                                                               |                |  |  |

|                         | DEVADC4                                                       | 0x1FC45010     |  |  |

|                         | DEVADC3                                                       | 0x1FC4500C     |  |  |

|                         | DEVADC2                                                       | 0x1FC45008     |  |  |

|                         | DEVADC1                                                       | 0x1FC45004     |  |  |

|                         | DEVADC0                                                       | 0x1FC45000     |  |  |

|                         |                                                               | 0x1FC44FFF     |  |  |

|                         |                                                               | 0x1FC44000     |  |  |

| Boot Flash 1            | Seq/Configuration                                             | 0x1FC43FFF     |  |  |

| Bootridon               | Word Space                                                    | 0x1FC43FB0     |  |  |

|                         |                                                               | 0x1FC43FAC     |  |  |

|                         |                                                               | 0x1FC40000     |  |  |

| D                       | eserved                                                       | 0x1FC3FFFF     |  |  |

|                         | eserveu                                                       | 0x1FC25000     |  |  |

|                         |                                                               | 0x1FC24FFF     |  |  |

| Uppe                    | r Boot Alias                                                  |                |  |  |

| oppo                    |                                                               |                |  |  |

|                         |                                                               | 0x1FC20000     |  |  |

| R                       | eserved                                                       | 0x1FC1FFFF     |  |  |

|                         |                                                               | 0x1FC05000     |  |  |

|                         |                                                               | 0x1FC04FFF     |  |  |

|                         |                                                               | 0x1FC04000     |  |  |

| Lower Post Alice        | Seq/Configuration                                             | 0x1FC03FFF     |  |  |

| Lower Boot Alias        | Word Space                                                    | 0x1FC03FB0     |  |  |

|                         |                                                               | 0x1FC03FAC     |  |  |

|                         |                                                               | 0x1FC00000     |  |  |

| Note 1: Memo            | ory areas are not shown to                                    | scale.         |  |  |

|                         | ory locations 0x1FC03FB0                                      |                |  |  |

|                         | C03FFC are used to initialize<br>guration registers (see 33.0 |                |  |  |

|                         | lires").                                                      | opeciai        |  |  |

| <ol><li>Refer</li></ol> | to 4.1.1 "Boot Flash Seq                                      |                |  |  |

| Confi                   | guration Spaces" for mor<br>bry locations 0x1FC5020 ar        | e information. |  |  |

|                         | in a unique device serial ni                                  |                |  |  |

| 33.0 "                  | Special Features").                                           |                |  |  |

|                         | configuration space cannot<br>ting code in the upper Boo      |                |  |  |

| EXECU                   | ang oode in the upper DOC                                     |                |  |  |

|                         |                                                               |                |  |  |

### TABLE 4-1: SFR MEMORY MAP

|               | Virtual Ad | dress           |

|---------------|------------|-----------------|

| Peripheral    | Base       | Offset<br>Start |

| CFG-PMD       |            | 0x0000          |

| CACHE         |            | 0x0800          |

| FC-NVM        |            | 0x0A00          |

| WDT           |            | 0x0C00          |

| DMT           | 0xBF800000 | 0x0E00          |

| ICD           |            | 0x1000          |

| CRU           |            | 0x1200          |

| PPS           |            | 0x1400          |

| PLVD          |            | 0x1800          |

| EVIC          | 0.000      | 0x0000          |

| DMA           | 0xBF810000 | 0x1000          |

| Timer1-Timer9 |            | 0x0000          |

| IC1-IC9       |            | 0x2000          |

| OC1-OC9       |            | 0x4000          |

| I2C1-I2C2     |            | 0x6000          |

| SPI1-SPI2     |            | 0x7000          |

| UART1-UART2   |            | 0x8000          |

| DATAEE        | 0xBF820000 | 0x9000          |

| PWM1-PWM12    |            | 0xA000          |

| QEI1-QEI6     |            | 0xB200          |

| CMP           |            | 0xC000          |

| CDAC1         |            | 0xC200          |

| CTMU          |            | 0xD000          |

| PMP           |            | 0xE000          |

| IC10-IC16     |            | 0x3200          |

| OC10-OC16     |            | 0x5200          |

| I2C3-I2C4     | 0xBF840000 | 0x6400          |

| SPI3-SPI6     | 0107040000 | 0x7400          |

| UART3-UART6   | ]          | 0x8400          |

| CDAC2-CDAC3   |            | 0xC400          |

| PORTA-PORTG   | 0xBF860000 | 0x0000          |

| CAN1-CAN4     |            | 0x0000          |

| ADC           | 0xBF880000 | 0x7000          |

| USB1-USB2     |            | 0x9000          |

| RTCC          |            | 0x0000          |

| Deep Sleep    | 0xBF8C0000 | 0x0200          |

| SSX CTL       | 0xBF8F0000 | 0x0000          |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

### REGISTER 4-9: SBTxRDy: SYSTEM BUS TARGET 'x' REGION 'y' READ PERMISSIONS REGISTER ('x' = 0-3; 'y' = 0-2)

|              |                   | 1                 | <u> </u>          | /                 |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 |                   |                   | _                 | -                 | —                 | -                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | _                 | —                 |                   | —                 |                  | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          |                   |                   |                   | _                 | GROUP3            | GROUP2            | GROUP1           | GROUP0           |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

### bit 31-4 Unimplemented: Read as '0'

bit 3 GROUP3: Group 3 Read Permissions bits 1 = Privilege Group 3 has read permission 0 = Privilege Group 3 does not have read permission bit 2 GROUP2: Group 2 Read Permissions bits 1 = Privilege Group 2 has read permission 0 = Privilege Group 2 does not have read permission GROUP1: Group 1 Read Permissions bits bit 1 1 = Privilege Group 1 has read permission 0 = Privilege Group 1 does not have read permission bit 0 GROUP0: Group 0 Read Permissions bits 1 = Privilege Group 0 has read permission 0 = Privilege Group 0 does not have read permission

Note 1: Refer to Table 4-6 for the list of available targets and their descriptions.

2: For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for more information.

## 6.0 DATA EEPROM

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 58. "Data EEPROM" (DS60001341), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Data EEPROM module provides the following features:

- 1K x 32-bit (4K x 8-bit) Emulated Data EEPROM using the 1K x 16 x 33-bit (66 KB)

- · Register-based indirect access

- Register-based, non-memory mapped, SFR

Program/Erase/Read interface

- · Read:

- Byte or Word read

- Read start Control bit and read complete status flag

- Read complete interrupt

- Program/Erase:

- No user erase required prior to program

- Hardware Word program verify

- Automatic page erase as part of wear-leveling scheme

- Hardware page erase verify

- Bulk and page erase

- Write complete and error interrupts

- · Brown-out protection for all commands

- Concurrent Data EEPROM read with Program Flash read/write

- Endurance:

- 160K program cycles per address location

- Transparent wear-leveling scheme

- No software overhead

- Automatic page erase (once every 17 program write operations)

- "Worn out" page detection and error flag

- "Imminent Page Erase" prediction status flag to allow user to schedule wear leveling page erasure

- · Low-power features:

- Always in stand-by unless accessed

- Power down in Sleep and/or Idle mode

- Independent Data EEPROM Flash power down in Idle Control bit

### 6.1 Data EEPROM Flash

Table 6-1 provides the status of the Data EEPROM Flash.

| TABLE 6-1: | DATA EEPROM FLASH |

|------------|-------------------|

|------------|-------------------|

| Data EE Wait Status<br>EEWS<7:0> bits<br>(CFGCON2<7:0>) = | PBCLK (FSYSCLK /<br>PBDIV<6:0> bits<br>(PB2DIV<6:0>)) |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| 0                                                         | 0-39 MHz                                              |  |  |  |  |

| 1                                                         | 40-59 MHz                                             |  |  |  |  |

| 2                                                         | 60-79 MHz                                             |  |  |  |  |

| 3                                                         | 80-97 MHz                                             |  |  |  |  |

| 4                                                         | 98-117 MHz                                            |  |  |  |  |

| 5                                                         | 118-120 MHz                                           |  |  |  |  |

- Note 1: The Data EEPROM Flash must have its calibration trim bits reinitialized after each cold power-up before any attempted accesses. Refer to Section 58. "Data EEPROM" (DS60001341) of the "PIC32 Family Reference Manual" for additional information.

- 2: Before any attempts to access the Data EEPROM module, the user application must configure the appropriate number of Wait states by configuring the EEWS<7:0> bits (CFGCON2< 7:0>) according to Table 6-1.

### TABLE 8-4: INTERRUPT REGISTER MAP (CONTINUED)

| SS                          |                                 |           |       |       |       |       | •     |       |      |           | lits |      |      |      |      |      |       |        |         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-----------|------|------|------|------|------|------|-------|--------|---------|

| #)                          | j£                              | ge        |       |       |       |       |       |       |      |           | 11.5 | 1    |      |      | 1    |      | 1     |        | esets   |

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Res |

|                             | 055000                          | 31:16     | —     | _     | —     | —     | _     | _     | -    | _         | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000    |

| 0808                        | OFF226                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | _      | 0000    |

|                             | 055007                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _         | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000    |

| 0800                        | OFF227                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | —      | 0000    |

|                             | 055000                          | 31:16     | _     | _     | _     | —     | _     | _     | —    | _         | _    | _    | _    | —    | _    | —    | VOFF< | 17:16> | 0000    |

| 08D0                        | OFF228                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | _      | 0000    |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _         | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000    |

| 08D4                        | OFF229                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | —      | 0000    |

|                             | 055000                          | 31:16     | _     | _     | _     | —     | _     | _     | —    | —         | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000    |

| 8080                        | OFF230                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | _      | 0000    |

|                             | 055044                          | 31:16     | —     | _     | _     | _     | _     | _     | _    | —         | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000    |

| 0910                        | OFF244                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | —      | 0000    |

|                             | 055045                          | 31:16     | —     | _     | _     | _     | _     | _     | _    | —         | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000    |

| 0914                        | OFF245                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | —      | 0000    |

|                             | 055040                          | 31:16     | —     | _     | _     | —     | _     | _     | _    | —         | _    | _    | _    | —    | _    | —    | VOFF< | 17:16> | 0000    |

| 0918                        | OFF246                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       | _      | 0000    |

|                             | 055054                          | 31:16     | _     | _     | _     | —     | _     | _     | —    | _         | _    | _    | _    | —    | _    | —    | VOFF< | 17:16> | 0000    |

| 0938                        | OFF254                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1 | >    |      |      |      |      |      |       |        | 0000    |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

2: This bit is not available on 64-pin devices.

3: This bit is not available on devices without a CAN module.

4: This bit is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 22 is not available on 64-pin devices.

7: The IFSx bits, as with all interrupt flag status register bits, are set as long as the peripheral is enabled and an interrupt condition event occurs. Interrupts do not have to be enabled for the IFSx bits to be set. If the user application does not want to use an interrupt, it can poll the corresponding peripheral IFSx bit to see whether an interrupt condition has occurred. The IFSx bits are persistent, they must be cleared if they are set by user software after an IFSx user bit interrogation.

### **TABLE 9-2: OSCILLATOR CONFIGURATION REGISTER MAP (CONTINUED)**

| ess                         |                       |           |       |       |       |       |          |       |            |         | Bits    |      |         | Bits    |           |         |          |        |                           |  |  |  |  |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|----------|-------|------------|---------|---------|------|---------|---------|-----------|---------|----------|--------|---------------------------|--|--|--|--|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11    | 26/10 | 25/9       | 24/8    | 23/7    | 22/6 | 21/5    | 20/4    | 19/3      | 18/2    | 17/1     | 16/0   | All Resets <sup>(1)</sup> |  |  |  |  |

| 1340                        | PB5DIV                | 31:16     | _     | _     | _     | _     | —        | _     | —          | —       | —       | —    | -       | _       | _         | —       | —        | _      | 0000                      |  |  |  |  |

| 1340                        | 15:0                  |           | ON    |       | _     | _     | PBDIVRDY | _     | —          | —       | —       |      |         |         | PBDIV<6:0 | >       |          |        | 8801                      |  |  |  |  |

| 1350                        | PB6DIV <sup>(2)</sup> | 31:16     | _     | Ι     | _     | _     | —        | _     | _          | _       | —       | _    | _       | _       | _         | —       | _        | _      | 0000                      |  |  |  |  |

| 1350                        | FBUDIVY               | 15:0      | ON    |       | _     | _     | PBDIVRDY | _     | —          | —       | —       |      |         |         | PBDIV<6:0 | >       |          |        | 8801                      |  |  |  |  |

| 1360                        | PB7DIV <sup>(3)</sup> | 31:16     | _     | Ι     | _     | _     | —        | _     | _          | _       | —       | _    | _       | _       | _         | —       | _        | _      | 0000                      |  |  |  |  |

| 1300                        | FDIDIV                | 15:0      | ON    |       | _     | _     | PBDIVRDY | _     | —          | —       | —       |      |         |         | PBDIV<6:0 | >       |          |        | 8800                      |  |  |  |  |

| 1200                        | SLEWCON               | 31:16     | _     | Ι     | _     | _     | —        | _     | _          | _       | —       | _    | _       | _       |           | SYSD    | 01V<3:0> |        | 0000                      |  |  |  |  |

| 1360                        | SLEWCON .             | 15:0      | —     | —     | —     | —     | —        | Ś     | SLWDIV<2:0 | >       | —       | —    | —       | —       | —         | UPEN    | DNEN     | BUSY   | 0000                      |  |  |  |  |

| 1390                        | CLKSTAT               | 31:16     | _     | _     | _     | _     | _        | _     | _          | —       | —       | _    | —       | _       | _         | _       | _        | _      | 0000                      |  |  |  |  |

| 1390                        | GENGIAI               | 15:0      | _     | _     | _     | _     | —        |       | —          | UPLLRDY | SPLLRDY | _    | LPRCRDY | SOSCRDY | _         | POSCRDY | _        | FRCRDY | 0000                      |  |  |  |  |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

Reset values are dependent on the DEVCFGx Configuration bits and the type of reset. Refer to Table 36-16 in **36.0** "Electrical Characteristics" for PBCLK6 frequency limitations. 2:

3: The PB7DIV register is read-only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | —                 | —                 | UPOSCEN           | —                 | —                 | F                 | PLLODIV<2:0      | >                |  |

| 23:16        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | —                 | PLLMULT<6:0>      |                   |                   |                   |                   |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | —                 |                   |                   |                   |                   | I                 | PLLIDIV<2:0>     | •                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          |                   |                   |                   |                   |                   | PL                | LRANGE<2:        | 0>               |  |

### REGISTER 9-4: UPLLCON: USB PLL CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-30 Unimplemented: Read as '0'

- bit 29 **UPOSCEN:** Output Enable bit 1 = USB input clock is Posc

- 0 = USB input clock is UPLL

bit 28-27 Unimplemented: Read as '0'

- bit 26-24 PLLODIV<2:0>: System PLL Output Clock Divider bits

- 111 = Reserved 110 = Reserved 101 = PLL Divide by 32 100 = PLL Divide by 16 011 = PLL Divide by 8 010 = PLL Divide by 4 001 = PLL Divide by 2 000 = Reserved

The default setting is specified by the FPLLODIV<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 33-5 in **33.0** "**Special Features**" for information.

bit 23 Unimplemented: Read as '0'

# Note 1: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

2: Writes to this register are not allowed if the UPLL is selected as a clock source (COSC<2:0> = 001).

3: While the PLL is active, and if updating the PLL bits in the OSCCON register at run-time, the user application must remain within the following limits at all times for all nodes in the PLL clock tree. Therefore, the order in which the PLL values may be modified, (i.e., PLLODIV, PLLMULT, PLLODIV) becomes important. Failure to maintain PLL nodes within min/max ranges may result in unstable PLL and system behavior.

- Output and input to PLLIDIV block (i.e., FPLLI) 5 MHz to 64 MHz (min/max at all times)

- VCO output, (i.e., FVCO) 350 MHz to 700 MHz (min/max at all times)

- Output of PLLODIV, (i.e., FPLL) 10 MHz to 120 MHz (min/max at all times)

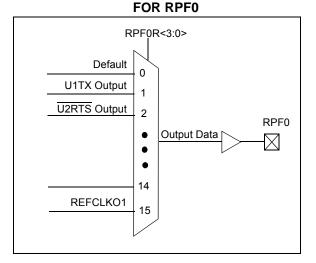

### 13.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 13-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 13-2 and Figure 13-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 13-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT

### 13.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. The PIC32MK GP/MC devices include two features to prevent alterations to the peripheral map:

- · Control register lock sequence

- Configuration bit select lock

### 13.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting the IOLOCK bit prevents writes to the control registers and clearing the IOLOCK bit allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to the **Section 42.** "Oscillators with Enhanced PLL" (DS60001250) in the "*PIC32 Family Reference Manual*" for details.

### 13.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If the IOLOCK bit remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

|                      | OT PIN SELECTION      |                            |                                                      |

|----------------------|-----------------------|----------------------------|------------------------------------------------------|

| RPn Port Pin         | RPnR SFR              | RPnR bits                  | RPnR Value to Peripheral<br>Selection                |

| RPA1                 | RPA1R                 | RPA1R<4:0>                 | 00000 = <u>Off</u><br>00001 = U3RTS                  |

| RPB5                 | RPB5R                 | RPB5R<4:0>                 | 00010 = U4TX<br>00011 = SDO1                         |

| RPB1                 | RPB1R                 | RPB1R<4:0>                 | 00100 = SDO2<br>00101 = OC2                          |

| RPB11                | RPB11R                | RPB11R<4:0>                | 00110 = OC8<br>00111 = C3OUT                         |

| RPA8                 | RPA8R                 | RPA8R<4:0>                 | 01000 = OC9<br>01001 = OC12                          |

| RPC8                 | RPC8R                 | RPC8R<4:0>                 | 01010 = <u>OC16</u><br>01011 = U6RTS<br>01100 = C4TX |

| RPB12                | RPB12R                | RPB12R<4:0>                | 01100 = C41X<br>01101 = Reserved<br>01110 = SDO3     |

| RPA12                | RPA12R                | RPA12R<4:0>                | 01111 = SDO4<br>10000 = SDO5                         |

| RPD6                 | RPD6R                 | RPD6R<4:0>                 | 10001 = SCK6<br>10010 = REFCLKO3                     |

| RPG7                 | RPG7R                 | RPG7R<4:0>                 | 10011 = Reserved<br>10100 = QEICMP2                  |

| RPG0 <sup>(1)</sup>  | RPG0R <sup>(1)</sup>  | RPG0R<4:0> (1)             | 10101 = QEICMP6<br>10110 = Reserved                  |

| RPE1 <sup>(1)</sup>  | RPE1R <sup>(1)</sup>  | RPE1R<4:0> (1)             | ].<br> .                                             |

| RPA14 <sup>(1)</sup> | RPA14R <sup>(1)</sup> | RPA14R<4:0> <sup>(1)</sup> | 11111 = Reserved                                     |

|  | TABLE 13-2: | <b>OUTPUT PIN SELECTION (</b> | (CONTINUED) |

|--|-------------|-------------------------------|-------------|

|--|-------------|-------------------------------|-------------|

Note 1: This selection is not available on 64-pin devices.

### TABLE 13-5: PORTB REGISTER MAP FOR 64-PIN AND 100-PIN DEVICES

| ess                         |                                 | 6             |               |               |               |               |                |               |              | Bits         |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|---------------|---------------|---------------|---------------|---------------|----------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14         | 29/13         | 28/12         | 27/11          | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0100                        | ANSELB                          | 31:16<br>15:0 | _             |               | _             | _             | _              | _             | —<br>ANSB9   |              | —<br>ANSB7   | _            |              |              | —<br>ANSB3   | —<br>ANSB2   | —<br>ANSB1   | —<br>ANSB0   | 0000<br>008F  |

| 0110                        | TRISB                           | 31:16         | _             |               | _             | _             | _              | _             | —            | _            | —            |              |              | _            | —            | —            | —            | —            | 0000          |

| 0400                        |                                 | 15:0<br>31:16 | TRISB15       | TRISB14       | TRISB13       | TRISB12       | TRISB11        | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF<br>0000  |

| 0120                        | PORTB                           | 15:0<br>31:16 | RB15          | RB14          | RB13          | RB12          | RB11           | RB10          | RB9          | RB8          | RB7          | RB6          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx<br>0000  |

| 0130                        | LATB                            | 15:0          | LATB15        | LATB14        | LATB13        | LATB12        | LATB11         | LATB10        | LATB9        | LATB8        | LATB7        | LATB6        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx          |

| 0140                        | ODCB                            | 31:16<br>15:0 | —<br>ODCB15   | —<br>ODCB14   | - ODCB13      | - ODCB12      | - ODCB11       | - ODCB10      | —<br>ODCB9   |              | ODCB7        | —<br>ODCB6   | —<br>ODCB5   | —<br>ODCB4   | —<br>ODCB3   | —<br>ODCB2   | —<br>ODCB1   | - ODCB0      | 0000          |

| 0150                        | CNPUB                           | 31:16<br>15:0 | —<br>CNPUB15  | —<br>CNPUB14  | —<br>CNPUB13  | —<br>CNPUB12  | —<br>CNPUB11   | —<br>CNPUB10  | —<br>CNPUB9  | —<br>CNPUB8  | —<br>CNPUB7  | —<br>CNPUB6  | —<br>CNPUB5  | —<br>CNPUB4  | —<br>CNPUB3  | —<br>CNPUB2  | —<br>CNPUB1  | —<br>CNPUB0  | 0000          |

| 0160                        | CNPDB                           | 31:16         | _             | _             |               | _             | _              | _             | _            | _            | _            | _            | —            | _            | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0<br>31:16 | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12       | CNPDB11<br>—   | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000          |

| 0170                        | CNCONB                          | 15:0          | ON            | _             | SIDL          | _             | EDGE<br>DETECT | —             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0180                        | CNENB                           | 31:16<br>15:0 | —<br>CNIEB15  | —<br>CNIEB14  | —<br>CNIEB13  | —<br>CNIEB12  | —<br>CNIEB11   | —<br>CNIEB10  | —<br>CNIEB9  | —<br>CNIEB8  | —<br>CNIEB7  | —<br>CNIEB6  | —<br>CNIEB5  | —<br>CNIEB4  | —<br>CNIEB3  | —<br>CNIEB2  | —<br>CNIEB1  | —<br>CNIEB0  | 0000          |

|                             |                                 | 31:16         | —             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0190                        | CNSTATB                         | 15:0          | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 | CN<br>STATB11  | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000          |

| 01A0                        | CNNEB                           | 31:16<br>15:0 | —<br>CNNEB15  | —<br>CNNEB14  | —<br>CNNEB13  | —<br>CNNEB12  | —<br>CNNEB11   | —<br>CNNEB10  | —<br>CNNEB9  | —<br>CNNEB8  | —<br>CNNEB7  | —<br>CNNEB6  | —<br>CNNEB5  | —<br>CNNEB4  | —<br>CNNEB3  | —<br>CNNEB2  | —<br>CNNEB1  | —<br>CNNEB0  | 0000          |

| 01B0                        | CNFB                            | 31:16         | _             |               | _             |               | _              | _             | _            | -            |              | _            | _            |              | _            |              |              | _            | 0000          |

| 0100                        |                                 | 15:0          | CNFB15        | CNFB14        | CNFB13        | CNFB12        | CNFB11         | CNFB10        | CNFB9        | CNFB8        | CNFB7        | CNFB6        | CNFB5        | CNFB4        | CNFB3        | CNFB2        | CNFB1        | CNFB0        | 0000          |

| 01C0                        | SRCON0B                         | 31:16<br>15:0 |               | —<br>SR0B14   | —<br>SR0B13   | —<br>SR0B12   | —<br>SR0B11    | —<br>SR0B10   |              |              |              | —<br>SR0B6   |              | —<br>SR0B4   |              |              | _            | _            | 0000          |

| 04.000                      | 00001/2                         | 31:16         |               | _             | <u> </u>      | —             |                | <u> </u>      |              |              |              | _            |              | -            | _            |              | _            | _            | 0000          |

| 0100                        | SRCON1B                         | 15:0          | SR1B15        | SR1B14        | SR1B13        | SR1B12        | SR1B11         | SR1B10        | _            | _            | SR1B7        | SR1B6        | _            | SR1B4        | _            |              | _            | _            | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See **13.2** "CLR, SET, and INV Registers" for more Note 1: information.

### TABLE 13-15: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                      |           |       |       |       |       |       |       |      | B    | lits |      |      |      |      |       |        |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 1500                        | IC12R                | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    |      | —    | —    | _    |      | —     | —      | _    | 0000       |

| 1500                        | IC IZR               | 15:0      | —     | —     | _     | _     | —     | _     | —    | _    | —    | _    | _    | _    |      | IC12F | <3:0>  |      | 0000       |

| 1504                        | IC13R                | 31:16     |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | —     | —      | —    | 0000       |

| 1504                        | 1013K                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | IC13F | R<3:0> | -    | 0000       |

| 1508                        | IC14R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | _     | —      | —    | 0000       |

| 1508                        |                      | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | IC14F | R<3:0> |      | 0000       |

| 150C                        | IC15R                | 31:16     |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | —     | —      | —    | 0000       |

| 1500                        | IC ISK               | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | IC15F | R<3:0> | -    | 0000       |

| 1510                        | IC16R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | —     | —      | —    | 0000       |

| 1510                        | ICIOR                | 15:0      | -     | —     | _     | _     | —     | _     | _    | _    | _    | —    | _    | _    |      | IC16F | R<3:0> |      | 0000       |

| 1514                        | SCK5R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | _     | —      | —    |            |

| 1514                        | SONON                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | SCK5  | R<3:0> |      |            |

| 1518                        | SDI5R                | 31:16     | -     | —     | _     | _     | —     | _     | _    | _    | _    | —    | _    | _    | _    | —     | _      | —    | 0000       |

| 1310                        | SDISK                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | SDI5F | R<3:0> | -    | 0000       |

| 151C                        | SS5R                 | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | _    |      |      | —     | —      | —    | 0000       |

| 1310                        | 3337                 | 15:0      |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | SS5R  | <3:0>  |      | 0000       |

| 1520                        | SCK6R                | 31:16     | _     | —     | —     | —     | —     | _     | _    | —    | _    | —    | —    | —    | -    | —     | —      | —    |            |

| 1520                        | SCROK                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | SCK6  | R<3:0> |      |            |

| 1524                        | SDI6R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | _    |      |      | —     | —      | —    | 0000       |

| 1524                        | SDIOK                | 15:0      |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | SDI6F | R<3:0> |      | 0000       |

| 1528                        | SS6R                 | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    | -    | —    | —    | —    |      | —     |        | —    | 0000       |

| 1520                        | 0001                 | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | SS6R  | <3:0>  |      | 0000       |

| 152C                        | C3RXR <sup>(3)</sup> | 31:16     | -     | _     | —     | —     | _     | —     | —    | —    |      | _    | —    | —    |      | —     | —      | —    | 0000       |

| 1520                        | CJKAR                | 15:0      | _     | _     | —     | —     | _     | —     | —    | —    | -    | _    | —    | —    |      | C3RX  | R<3:0> |      | 0000       |

| 1530                        | C4RXR <sup>(3)</sup> | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    |      | _    | —    | _    |      | —     | —      | —    | 0000       |

| 1550                        | 0 <del>4</del> NAN*7 | 15:0      | -     | —     | —     | _     | —     | —     | —    | -    | -    | —    | _    | —    |      | C4RX  | R<3:0> |      | 0000       |

| 1534                        | QEA3R                | 31:16     |       | _     | —     | _     |       | _     | _    | —    |      | _    | _    | -    |      | —     | _      | —    | 0000       |

| 1004                        | QLAUN                | 15:0      | _     |       | _     | —     |       | —     | _    | _    |      |      | _    |      |      | QEA3  | R<3:0> |      | 0000       |

| 1538                        | QEB3R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    | —    | ļ    | -     | —      | —    | 0000       |

| 1000                        | QLDJK                | 15:0      | _     | —     | —     | —     | —     | —     | _    |      |      | —    | —    | -    |      | QEB3  | R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

3: This register is only available on PIC32MKXXXGPEXXX devices.

# DS60001402E-page 268

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | -                    | —                 | —                 | —                 | _                 | _                 | _                | —                |

| 23:16     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | —                    | —                 | —                 | —                 | —                 | _                 | _                | —                |

| 45.0      | R/W-0                | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON                   | —                 | SIDL              | —                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0                | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR <sup>(1)</sup> | ICI<1:0>          |                   | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

## **REGISTER 18-1:** ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER ('x' = 1-16)

### Legend:

| 0                                          |                  |                       |                  |   |

|--------------------------------------------|------------------|-----------------------|------------------|---|

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit |                  |   |

| -n = Bit Value at POR: ('0', '1', x = unkn | own)             | P = Programmable bit  | r = Reserved bit | I |

| bit 31-16 | Unimplemented: Read as '0'                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit                                                                                    |

|           | 1 = Module enabled                                                                                                     |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                 |

| bit 14    | Unimplemented: Read as '0'                                                                                             |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                         |

|           | 1 = Halt in CPU Idle mode                                                                                              |

|           | 0 = Continue to operate in CPU Idle mode                                                                               |

| bit 12-10 | Unimplemented: Read as '0'                                                                                             |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                             |

|           | 1 = Capture rising edge first                                                                                          |

|           | 0 = Capture falling edge first                                                                                         |

| bit 8     | C32: 32-bit Capture Select bit                                                                                         |

|           | 1 = 32-bit timer resource capture                                                                                      |

|           | 0 = 16-bit timer resource capture                                                                                      |

| bit 7     | <b>ICTMR:</b> Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is $(1')^{(1)}$                   |

|           | <ul> <li>0 = Timery is the counter source for capture</li> <li>1 = Timerx is the counter source for capture</li> </ul> |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                       |

| DIL 0-3   | 11 = Interrupt on every fourth capture event                                                                           |

|           | 10 = Interrupt on every third capture event                                                                            |

|           | 01 = Interrupt on every second capture event                                                                           |

|           | 00 = Interrupt on every capture event                                                                                  |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                               |

|           | 1 = Input capture overflow occurred                                                                                    |

|           | 0 = No input capture overflow occurred                                                                                 |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                           |

|           | 1 = Input capture buffer is not empty; at least one more capture value can be read                                     |

|           | 0 = Input capture buffer is empty                                                                                      |

|           |                                                                                                                        |

**Note 1:** Refer to Table 18-1 for Timerx and Timery selections.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31.24        | —                 | —                 | _                 | -                 | ABAT              | REQOP<2:0>        |                  |                  |

| 23:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23.10        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | _                 | _                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | -                 | CANBUSY           | _                 | _                | —                |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 | _                 |                   | [                 | DNCNT<4:0>        |                  |                  |

### **REGISTER 26-1:** CxCON: CAN MODULE CONTROL REGISTER ('x' = 1-4)

| Legend:           | HC = Hardware Clear | S = Settable bit     |                    |

|-------------------|---------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

### **REGISTER 26-9:** CxRXMn: CAN ACCEPTANCE FILTER MASK 'n' REGISTER ('x' = 1-4 ' n' = 0, 1, 2 OR 3)

|              | ( X               | = 1-4; n =        | = U, I, Z UK      | 3)                |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        |                   | SID<10:3>         |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |

| 23.10        |                   | SID<2:0>          |                   | -                 | MIDE              | —                 | EID<             | 17:16>           |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | 15:8 EID<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   | EID<7:0>          |                   |                   |                   |                   |                  |                  |  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

### bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include the SIDx bit in filter comparison

- 0 = The SIDx bit is a 'don't care' in filter operation

### bit 20 Unimplemented: Read as '0'

### bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

- Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

### bit 18 Unimplemented: Read as '0'

### bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include the EIDx bit in filter comparison

- 0 = The EIDx bit is a 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CxCON<23:21>) = 100).

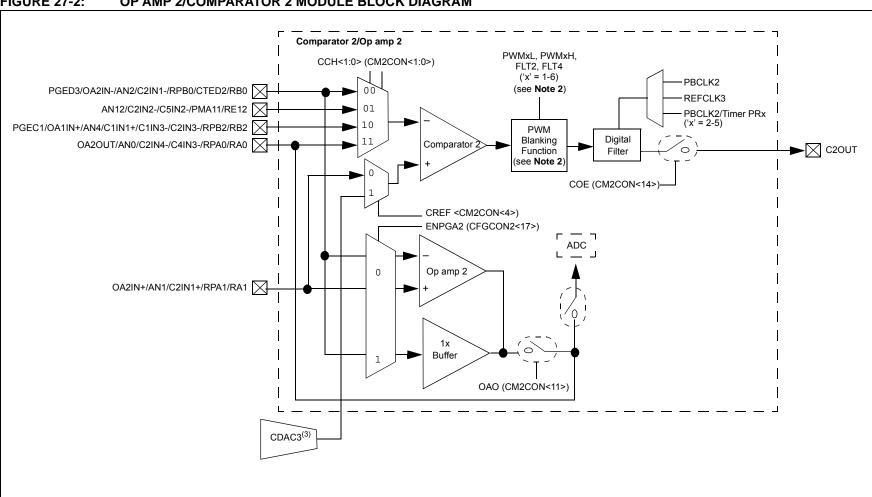

## 27.0 OP AMP/COMPARATOR MODULE

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 39. "Op amp/Comparator" (DS60001178), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

Depending on the device, the Op amp/Comparator module consists of a Comparator and Op amp modules. When available, the Op amps can be independently enabled or disabled from the Comparator.

Key features of the Comparator include:

- Differential inputs

- Rail-to-rail operation

- · Selectable output and trigger event polarity

- · Selectable inputs:

- Analog inputs multiplexed with I/O pins

- On-chip internal voltage reference via a 12-bit CDAC output or an external pin

- Output debounce or Digital noise filter with these selectable clocks:

- Peripheral Bus Clock (PBCLK2)

- System Clock (SYSCLK)

- Reference Clock 3 (REFCLK3)

- PBCLK2/Timer PRx ('x' = 2-5)

- PWM Secondary Special Event

- Outputs can be internally configured as trigger sources

The following are key features of the Op amps:

- Inverting and non-inverting Inputs and output accessible on pins

- Rail-to-rail operation  $(3V \le AVDD \le 3.6V)$

- Internal connection to ADC Sample and Hold circuits/SAR cores

- Special voltage follower mode for buffering signals

Please refer to the PIC32MK GP Family Features in TABLE 1: "PIC32MK General Purpose (GP) Family Features" for the actual number of available Op amp/ Comparator modules on your specific device.

Block diagrams of the Op amp/Comparator module are illustrated in Figure 27-1 through Figure 27-5.

Note: The Op amps are disabled by default (i.e., OPAxMD bit in the PMD2 register is equal to '1') on any Reset. Before use or access to any corresponding Op amp, ensure that the OPAxMD bit is equal to '0'.

### **FIGURE 27-2: OP AMP 2/COMPARATOR 2 MODULE BLOCK DIAGRAM**

Refer to the device pin tables (Table 3 and Table 5) for other analog inputs that may be also be connected to the Op amp and Comparator inputs. Note 1:

The PWM Blank Function is available only on PIC32MKXXMCXXX devices. 2:

Caution: To avoid false comparator output faults or glitches when using the internal DAC as a comparator reference, always initialize the DAC before initializing and enabling the comparator. 3:

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0     |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-----------------------------|-------------------|------------------------------|----------------------|--|