Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, IrDA, LINbus, PMP, QEI, SPI, UART/USART, USB OTG                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, Motor Control PWM, WDT       |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                      |

| Data Converters            | A/D 27x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mk1024mcf064-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R-1               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | М                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | KScr Exist<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 3-4: CONFIG4: CONFIGURATION REGISTER 4; CP0 REGISTER 16, SELECT 4

| Legend:           | r = Reserved     |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

- bit 31 M: Config5 Register Present bit

- 1 = Config5 register is present

- 0 = Config5 register is not present

- bit 30-24 Unimplemented: Read as '0'

- bit 23-16 KScr Exist<7:0>: Number of Scratch Registers Available to Kernel Mode bits

Indicates how many scratch registers are available to Kernel mode software within CP0 Register 31. Each bit represents a select for Coprocessor0 Register 31. Bit 16 represents Select 0. Bit 23 represents Select 7. If the bit is set, the associated scratch register is implemented and is available for Kernel mode software.

Note: These bits are read-only, and this field is all zeros on these products, as is read as '0'.

#### bit 15-0 Reserved: Read/write as '0'

NOTES:

# 6.0 DATA EEPROM

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 58. "Data EEPROM" (DS60001341), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Data EEPROM module provides the following features:

- 1K x 32-bit (4K x 8-bit) Emulated Data EEPROM using the 1K x 16 x 33-bit (66 KB)

- · Register-based indirect access

- Register-based, non-memory mapped, SFR

Program/Erase/Read interface

- · Read:

- Byte or Word read

- Read start Control bit and read complete status flag

- Read complete interrupt

- Program/Erase:

- No user erase required prior to program

- Hardware Word program verify

- Automatic page erase as part of wear-leveling scheme

- Hardware page erase verify

- Bulk and page erase

- Write complete and error interrupts

- · Brown-out protection for all commands

- Concurrent Data EEPROM read with Program Flash read/write

- Endurance:

- 160K program cycles per address location

- Transparent wear-leveling scheme

- No software overhead

- Automatic page erase (once every 17 program write operations)

- "Worn out" page detection and error flag

- "Imminent Page Erase" prediction status flag to allow user to schedule wear leveling page erasure

- · Low-power features:

- Always in stand-by unless accessed

- Power down in Sleep and/or Idle mode

- Independent Data EEPROM Flash power down in Idle Control bit

# 6.1 Data EEPROM Flash

Table 6-1 provides the status of the Data EEPROM Flash.

| TABLE 6-1: | DATA EEPROM FLASH |

|------------|-------------------|

|------------|-------------------|

| Data EE Wait Status<br>EEWS<7:0> bits<br>(CFGCON2<7:0>) = | PBCLK (FSYSCLK /<br>PBDIV<6:0> bits<br>(PB2DIV<6:0>)) |

|-----------------------------------------------------------|-------------------------------------------------------|

| 0                                                         | 0-39 MHz                                              |

| 1                                                         | 40-59 MHz                                             |

| 2                                                         | 60-79 MHz                                             |

| 3                                                         | 80-97 MHz                                             |

| 4                                                         | 98-117 MHz                                            |

| 5                                                         | 118-120 MHz                                           |

- Note 1: The Data EEPROM Flash must have its calibration trim bits reinitialized after each cold power-up before any attempted accesses. Refer to Section 58. "Data EEPROM" (DS60001341) of the "PIC32 Family Reference Manual" for additional information.

- 2: Before any attempts to access the Data EEPROM module, the user application must configure the appropriate number of Wait states by configuring the EEWS<7:0> bits (CFGCON2< 7:0>) according to Table 6-1.

#### TABLE 8-4: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |        | 1     | İ     | -     |       |       |               | - ,   |        | В                 | lits |      |      |                            |                |         |                  |                  | 6          |

|-----------------------------|--------|-------|-------|-------|-------|-------|---------------|-------|--------|-------------------|------|------|------|----------------------------|----------------|---------|------------------|------------------|------------|

| Virtual Address<br>(BF81_#) |        |       | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10 | 25/9   | 24/8              | 23/7 | 22/6 | 21/5 | 20/4                       | 19/3           | 18/2    | 17/1             | 16/0             | All Resets |

| 0370                        | IPC35  | 31:16 | —     | —     | —     |       | AD1D37IP<2:0> |       | AD1D37 | 7IS<1:0>          | —    | —    |      | A                          | D1D36IP<2:     | 0>      | AD1D36           | S<1:0>           | 0000       |

| 0370                        | IF 035 | 15:0  | —     | —     | —     |       | AD1D35IP<2:   | 0>    | AD1D35 | 5IS<1:0>          | —    | _    |      | A                          | D1D34IP<2:     | 0>      | AD1D34           | S<1:0>           | 0000       |

| 0380                        | IPC36  | 31:16 | —     | —     | —     |       | AD1D41IP<2:   | 0>    | AD1D41 | IIS<1:0>          | —    | —    | —    | A                          | D1D40IP<2:     | 0>      | AD1D40           | S<1:0>           | 0000       |

| 0300                        | 11 030 | 15:0  | _     | _     | _     |       | AD1D39IP<2:   | 0>    | AD1D39 | 9IS<1:0>          |      | _    | _    | A                          | D1D38IP<2:     | 0>      | AD1D38           | S<1:0>           | 0000       |

| 0390                        | IPC37  | 31:16 | —     | —     | —     | ,     | AD1D45IP<2:   | 0>    | AD1D45 | 5IS<1:0>          | —    | —    | _    | —                          | —              |         | —                | _                | 0000       |

| 0000                        | 11 007 | 15:0  | —     | —     | —     | —     | —             |       | —      | —                 | —    | —    |      | —                          | —              | —       | —                | —                | 0000       |

| 03A0                        | IPC38  | 31:16 | —     | —     | —     | ,     | AD1D49IP<2:   | 0>    | AD1D49 | 9IS<1:0>          | —    | —    |      | A                          | D1D48IP<2:     | 0>      | AD1D48           | S<1:0>           | 0000       |

| 00/10                       | 11 000 | 15:0  | —     | —     | —     |       | AD1D47IP<2:   | 0>    | AD1D47 | 7IS<1:0>          | —    | —    | _    | A                          | D1D46IP<2:     | 0>      | AD1D46           | S<1:0>           | 0000       |

| 03B0                        | IPC39  | 31:16 | —     | _     | —     |       | AD1D53IP<2:   | 0>    | AD1D53 | BIS<1:0>          | —    | —    | _    | A                          | D1D52IP<2:     | 0>      | AD1D52           | S<1:0>           | 0000       |

| 0000                        |        | 15:0  | —     | _     | —     |       | AD1D51IP<2:   | 0>    | AD1D51 | IIS<1:0>          | —    | —    | _    | AD1D50IP<2:0>              |                | AD1D50  | S<1:0>           | 0000             |            |

| 03C0                        | IPC40  | 31:16 | —     | —     | —     | —     | —             | —     | —      | —                 | —    | —    | _    | CMP5IP<2:0>                |                | CMP5IS  | S<1:0>           | 0000             |            |

| 0000                        | 11 040 | 15:0  | —     | —     | —     |       | CMP4IP<2:0>   |       |        | S<1:0>            | —    | —    | _    | CMP3IP<2:0>                |                | CMP3IS  | S<1:0>           | 0000             |            |

| 03D0                        | IPC41  | 31:16 | —     | —     | —     | (     | CAN1IP<2:0>   | (3)   | CAN1IS | i<1:0> <b>(3)</b> | —    | —    | _    | U6TXIP<2:0>                |                | U6TXIS  | S<1:0>           | 0000             |            |

| 0000                        | 11 041 | 15:0  | —     | —     | —     |       | U6RXIP<2:0    | >     | U6RXI  | S<1:0>            | —    | _    | —    | U6EIP<2:0>                 |                | U6EIS-  | <1:0>            | 0000             |            |

| 03E0                        | IPC42  | 31:16 | —     | —     | —     | P     | WMPEVTIP<2    | 2:0>  | PWMSEV | /TIP<1:0>         | —    | —    |      | — QEI2IP<2:0>              |                | QEI2SIF |                  | 0000             |            |

| UULU                        | 11 042 | 15:0  | —     | —     | —     |       | QEI1IP<2:0>   | >     | QEI1SI | P<1:0>            | —    | —    |      | CAN2IP<2:0> <sup>(3)</sup> |                | CAN2IS< | <1:0> <b>(3)</b> | 0000             |            |

| 03F0                        | IPC43  | 31:16 | _     | _     | _     |       | PWM3IP<2:0    | >     | PWM3S  | SIP<1:0>          |      | _    | _    | F                          | PWM2IP<2:0     | >       | PWM2SI           | P<1:0>           | 0000       |

| 0010                        | 11 040 | 15:0  | _     | _     | _     |       | PWM1IP<2:0    | >     | PWM1S  | SIP<1:0>          |      | _    | _    | PW                         | /MSEVTIP<      | 2:0>    | PWMSEVT          | SIP<1:0>         | 0000       |

| 0400                        | IPC44  | 31:16 | —     | —     | —     | _     | —             | —     | —      | —                 | —    | _    |      | F                          | PWM6IP<2:0     | >       | PWM6SI           | P<1:0>           | 0000       |

| 0400                        | 11 044 | 15:0  | —     | _     | —     |       | PWM5IP<2:0    | >     | PWM5S  | SIP<1:0>          | —    | —    | _    | F                          | PWM4IP<2:0     | >       | PWM4SI           | P<1:0>           | 0000       |

| 0410                        | IPC45  | 31:16 | —     | —     | —     |       | DMA5IP<2:0    | >     | DMA5I  | S<1:0>            | —    | _    |      | [                          | DMA4IP<2:0     | >       | DMA4IS           | 6<1:0>           | 0000       |

| 0410                        | 11 040 | 15:0  | —     | _     | —     | —     | _             | —     | —      | _                 | —    | —    | _    | _                          | _              | _       | —                | _                | 0000       |

| 0420                        | IPC46  | 31:16 | —     | —     | —     | (     | CAN3IP<2:0>   | (3)   | CAN3IS | <1:0> <b>(3)</b>  | —    | _    |      | D.                         | ATAEEIP<2:     | 0>      | DATAEE           | IS<1:0>          | 0000       |

| 0420                        | IF C40 | 15:0  | —     | _     | —     |       | DMA7IP<2:0>   |       | DMA7I  | S<1:0>            | —    | _    |      | DMA6IP<2:0>                |                | DMA6IS  | 6<1:0>           | 0000             |            |

| 0430                        | IPC47  | 31:16 | _     | _     | _     |       | QEI5IP<2:0>   |       | QEI5SI | P<1:0>            | _    | _    |      |                            | QEI4IP<2:0>    |         | QEI4SIF          |                  | 0000       |

| 0430                        | 16041  | 15:0  | —     | —     | —     |       | QEI3IP<2:0>   |       | QEI3SI | P<1:0>            | —    | —    | _    | С                          | CAN4IP<2:0>(3) |         | CAN4IS<          | <1:0> <b>(3)</b> | 0000       |

| 0440                        | IPC48  | 31:16 | —     | —     | _     | —     |               |       | —      | _                 | _    | —    | _    | —                          | _              | _       | —                | _                | 0000       |

| 0440                        | 16049  | 15:0  | _     |       | _     |       | _             |       |        | _                 |      | _    | _    |                            | QEI6IP<2:0     | >       | QEI6SIF          | P<1:0>           | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

2: This bit is not available on 64-pin devices.

3: This bit is not available on devices without a CAN module.

4: This bit is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 22 is not available on 64-pin devices.

7: The IFSx bits, as with all interrupt flag status register bits, are set as long as the peripheral is enabled and an interrupt condition event occurs. Interrupts do not have to be enabled for the IFSx bits to be set. If the user application does not want to use an interrupt, it can poll the corresponding peripheral IFSx bit to see whether an interrupt condition has occurred. The IFSx bits are persistent, they must be cleared if they are set by user software after an IFSx user bit interrogation.

# 10.2 Prefetch Control Registers

## TABLE 10-1: PREFETCH REGISTER MAP

| ess                                                            | Bits   |                      |                    |                   |       |           |       |          |        |          | s        |           |         |         |      |           |          |         |               |

|----------------------------------------------------------------|--------|----------------------|--------------------|-------------------|-------|-----------|-------|----------|--------|----------|----------|-----------|---------|---------|------|-----------|----------|---------|---------------|

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(†)</sup> |        | Bit Range            | 31/15              | 30/14             | 29/13 | 28/12     | 27/11 | 26/10    | 25/9   | 24/8     | 23/7     | 22/6      | 21/5    | 20/4    | 19/3 | 18/2      | 17/1     | 16/0    | All Reset     |

| 0000                                                           |        | 31:16                | Ι                  |                   | _     | _         | _     | PERCHEEN | DCHEEN | ICHEEN   |          | PERCHEINV | DCHEINV | ICHEINV | _    | PERCHECOH | DCHECOH  | ICHECOF | <b>1</b> 0700 |

| 0800                                                           | CHECON | 15:0                 | _                  | _                 | _     | CHEPERFEN | _     | _        | —      | PFMAWSEN | _        | _         | PREFE   | N<1:0>  | _    | PF        | MWS<2:0> |         | 0107          |

| 0000                                                           | CHEHIT | 31:16                |                    |                   |       |           |       |          |        | CHEHI    | T<31:16> | <b>`</b>  |         |         |      |           |          |         | 0000          |

| 0820                                                           | CHEHII | 15:0                 |                    | CHEHIT<15:0> 0000 |       |           |       |          |        |          | 0000     |           |         |         |      |           |          |         |               |

| 0020                                                           |        | 31:16                | CHEMIS<31:16> 0000 |                   |       |           |       |          |        | 0000     |          |           |         |         |      |           |          |         |               |

| 0830                                                           | CHEMIS | 15:0 CHEMIS<15:0> 0( |                    |                   |       |           |       |          | 0000   |          |          |           |         |         |      |           |          |         |               |

PIC32MK GP/MC Family

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section13.2 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|--|--|--|

| 24.04        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |  |

| 31:24        | CHPIGN<7:0>         |                   |                   |                   |                   |                   |                  |                       |  |  |  |

| 23:16        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |  |  |  |

| 23.10        | -                   | -                 | —                 | -                 | —                 | —                 | -                | —                     |  |  |  |

| 45.0         | R/W-0               | U-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0              | R/W-0                 |  |  |  |

| 15:8         | CHBUSY              | _                 | CHIPGNEN          | —                 | CHPATLEN          | _                 | _                | CHCHNS <sup>(1)</sup> |  |  |  |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |  |  |  |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | —                 | CHEDET            | CHPF             | RI<1:0>               |  |  |  |

#### **REGISTER 11-7:** DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER ('x' = 0-7)

#### Legend:

bit 7

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-24 CHPIGN<7:0>: Channel Register Data bits

Pattern Terminate mode:

Any byte matching these bits during a pattern match may be ignored during the pattern match determination when the CHPIGNEN bit is set. If a byte is read that is identical to this data byte, the pattern match logic will treat it as a "don't care" when the pattern matching logic is enabled and the CHPIGEN bit is set.

- bit 23-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 CHPIGNEN: Enable Pattern Ignore Byte bit

- 1 = Treat any byte that matches the CHPIGN<7:0> bits as a "don't care" when pattern matching is enabled

- 0 = Disable this feature

- bit 12 Unimplemented: Read as '0'

- bit 11 CHPATLEN: Pattern Length bit

- 1 = 2 byte length

- 0 = 1 byte length

- bit 10-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

- bit 5 CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

|              |                   | ••••••            |                   |                   |                   |                   | -,                    |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 31.24        | -                 | —                 | —                 | —                 | -                 | —                 | -                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23.10        | -                 | —                 | —                 | —                 | -                 | —                 | -                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         |                   |                   | _                 | _                 | _                 | _                 |                       | _                                                |

|              | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

#### REGISTER 12-7: UxIE: USB INTERRUPT ENABLE REGISTER ('x' = 1 AND 2)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>STALLIE:</b> STALL Handshake Interrupt Enable bit<br>1 = STALL interrupt is enabled<br>0 = STALL interrupt is disabled |

|-------|---------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit                                                                                     |

|       | <ul><li>1 = ATTACH interrupt is enabled</li><li>0 = ATTACH interrupt is disabled</li></ul>                                |

| bit 5 | <b>RESUMEIE:</b> RESUME Interrupt Enable bit                                                                              |

|       | <ul><li>1 = RESUME interrupt is enabled</li><li>0 = RESUME interrupt is disabled</li></ul>                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                                                                                  |

|       | 1 = Idle interrupt is enabled                                                                                             |

|       | 0 = Idle interrupt is disabled                                                                                            |

| bit 3 | <b>TRNIE:</b> Token Processing Complete Interrupt Enable                                                                  |

|       | 1 = TRNIF interrupt is enabled                                                                                            |

|       | 0 = TRNIF interrupt is disabled                                                                                           |

| bit 2 | SOFIE: SOF Token Interrupt Enable bit                                                                                     |

|       | 1 = SOFIF interrupt is enabled                                                                                            |

|       |                                                                                                                           |

- 1 = SOFIF interrupt is enabled 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (UxIE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

# TABLE 13-15: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                      |           |       |       |       |       |       |       |      | B    | lits |      |      |      |      |       |        |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 1500                        | IC12R                | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    |      | —    | —    | _    |      | —     | —      | _    | 0000       |

| 1500                        | IC IZR               | 15:0      | —     | —     | _     | _     | —     | _     | —    | _    | —    | _    | _    | _    |      | IC12F | <3:0>  |      | 0000       |

| 1504                        | IC13R                | 31:16     |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | —     | —      | —    | 0000       |

| 1504                        | 1013K                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | IC13F | R<3:0> | -    | 0000       |

| 1508                        | IC14R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | —     | —      | —    | 0000       |

| 1508                        |                      | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | _    |      |      | IC14F | R<3:0> |      | 0000       |

| 150C                        | IC15R                | 31:16     |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | —     | —      | —    | 0000       |

| 1500                        | IC ISK               | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | IC15F | R<3:0> | -    | 0000       |

| 1510                        | IC16R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | —     | —      | —    | 0000       |

| 1510                        | ICIOR                | 15:0      | -     | —     | _     | _     | —     | _     | _    | _    | _    | —    | _    | _    |      | IC16F | R<3:0> |      | 0000       |

| 1514                        | SCK5R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | _     | —      | —    |            |

| 1514                        | SONON                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | SCK5  | R<3:0> |      |            |

| 1518                        | SDI5R                | 31:16     | -     | —     | _     | _     | —     | _     | _    | _    | _    | —    | _    | _    | _    | —     | _      | —    | 0000       |

| 1310                        | SDISK                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | SDI5F | R<3:0> | -    | 0000       |

| 151C                        | SS5R                 | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | _    |      |      | —     | —      | —    | 0000       |

| 1310                        | 3337                 | 15:0      |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | SS5R  | <3:0>  |      | 0000       |

| 1520                        | SCK6R                | 31:16     | _     | —     | —     | —     | —     | _     | _    | —    | _    | —    | —    | —    | -    | —     | —      | —    |            |

| 1520                        | SCROK                | 15:0      |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    |      |      | SCK6  | R<3:0> |      |            |

| 1524                        | SDI6R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | _    |      |      | —     | —      | —    | 0000       |

| 1524                        | SDIOK                | 15:0      |       | _     | _     | _     | _     | —     | _    | _    |      | _    | _    |      |      | SDI6F | R<3:0> |      | 0000       |

| 1528                        | SS6R                 | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    | -    | —    | —    | —    |      | —     |        | —    | 0000       |

| 1520                        | 0001                 | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | SS6R  | <3:0>  |      | 0000       |

| 152C                        | C3RXR <sup>(3)</sup> | 31:16     | -     | _     | —     | —     | _     | —     | —    | —    |      | _    | _    | —    |      | —     | —      | —    | 0000       |

| 1520                        | CJKAR                | 15:0      | _     | _     | —     | —     | _     | —     | —    | —    | -    | _    | —    | —    |      | C3RX  | R<3:0> |      | 0000       |

| 1530                        | C4RXR <sup>(3)</sup> | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    |      | —    | —    | _    |      | —     | —      | —    | 0000       |

| 1550                        | 0 <del>4</del> NAN*7 | 15:0      | -     | —     | —     | _     | —     | —     | —    | -    | -    | _    | _    | —    |      | C4RX  | R<3:0> |      | 0000       |

| 1534                        | QEA3R                | 31:16     |       | _     | —     | _     |       | _     | _    | —    |      | _    | _    | -    |      | —     | _      | —    | 0000       |

| 1004                        | QLAUN                | 15:0      | _     |       | _     | —     |       | —     | _    | _    |      |      | _    |      |      | QEA3  | R<3:0> |      | 0000       |

| 1538                        | QEB3R                | 31:16     |       | —     | —     | —     | —     | —     | _    | _    |      | —    | —    | —    | ļ    | -     | —      | —    | 0000       |

| 1000                        | QLDJK                | 15:0      | _     | —     | —     | —     | —     | —     | _    |      |      | —    | —    | -    |      | QEB3  | R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

3: This register is only available on PIC32MKXXXGPEXXX devices.

# DS60001402E-page 268

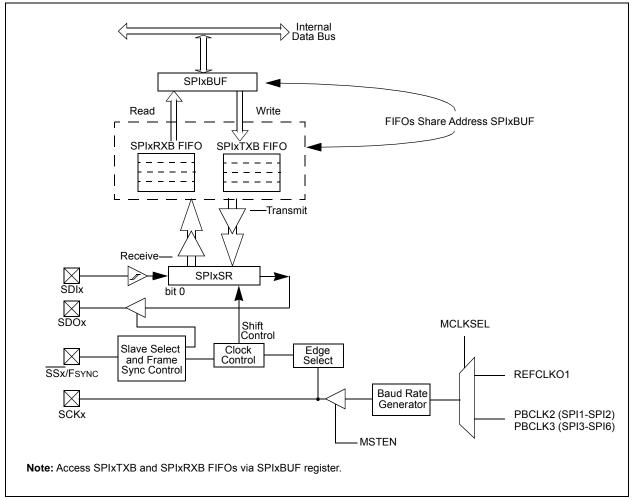

# 20.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note: This data sheet summarizes the features of the PIC32MK GP/MC family of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to Section 23. "Serial (SPI)" Peripheral Interface (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well as digital audio devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, analog-to-digital converters (ADC), etc.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The following are some of the key features of the SPI module:

- · Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 32/24/16/8-bit data width

- Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/24/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- · Audio codec support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

#### FIGURE 20-1: SPI/I<sup>2</sup>S MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                 | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC R-0, HS, HC |                   | R-0, HS, HC      | R-0, HS, HC      |  |

| 31:24        | — — — RXBUFELM<4:0> |                   |                   |                   |                         |                   |                  |                  |  |

| 22:16        | U-0                 | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC             | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 23:16        | —                   | _                 | _                 |                   | TX                      | >                 |                  |                  |  |

| 45.0         | U-0                 | U-0               | U-0               | R/C-0, HS         | R-0, HS, HC             | U-0               | U-0              | R-0              |  |

| 15:8         | _                   |                   |                   | FRMERR            | SPIBUSY                 |                   | _                | SPITUR           |  |

| 7.0          | R-0, HS, HC         | R/C-0, HS         | R-1, HS, HC       | U-0               | R-1, HS, HC             | U-0               | R-0, HS, HC      | R-0, HS, HC      |  |

| 7:0          | SRMT                | SPIROV            | SPIRBE            | -                 | SPITBE                  |                   | SPITBF           | SPIRBF           |  |

#### REGISTER 20-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | HC = Cleared in hardware | HS = Set in hardware               | C = Clearable bit  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 FRMERR: SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 **SPITUR:** Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 SRMT: Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 **SPIROV:** Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can only be cleared (= 0) in software.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1)

- 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0                U-0              |

| 31.24     | _                 | -                 | —                 | -                 | _                 | _                 | -                | _                |

| 23:16     | U-0                U-0              |

| 23.10     | —                 | _                 | —                 | _                 | _                 | _                 | _                | —                |

| 15:8      | U-0                U-0              |

| 10.0      | —                 | _                 | —                 | _                 | _                 | _                 | _                | —                |

| 7:0       | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | _                 | _                 | _                 | _                 | DIFF49            | SIGN49            | DIFF48           | SIGN48           |

### REGISTER 25-8: ADCIMCON4: ADC INPUT MODE CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 3 DIFF49: AN49 Mode bit

- 1 = Selects AN49 differential input pair as AN49+ and AN1-

- 0 = AN49 is using Single-ended mode

- bit 2 SIGN49: AN41 Signed Data Mode bit

- 1 = AN49 is using Signed Data mode

- 0 = AN49 is using Unsigned Data mode

#### bit 1 DIFF48: AN48 Mode bit

1 = Selects AN40 differential input pair as AN48+ and AN1-

0 = AN48 is using Single-ended mode

#### bit 0 SIGN48: AN48 Signed Data Mode bit

- 1 = AN48 is using Signed Data mode

- 0 = AN48 is using Unsigned Data mode

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6    | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|-----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| 31:24     | U-0                  |

| 31.24     | _                    | —                    | —                    | _                    | —                    | _                    | _                    | —                    |

| 22:16     | U-0                  | U-0                  | R/W-0                | R/W-0                | U-0                  | R/W-0                | R/W-0                | R/W-0                |

| 23:16     | _                    | —                    | CSS53 <sup>(2)</sup> | CSS52 <sup>(2)</sup> | —                    | CSS50 <sup>(2)</sup> | CSS49                | CSS48                |

| 45.0      | R/W-0                | R/W-0                | R/W-0                | U-0                  | U-0                  | U-0                  | R/W-0                | R/W-0                |

| 15:8      | CSS47 <sup>(1)</sup> | CSS46 <sup>(1)</sup> | CSS45 <sup>(1)</sup> | _                    | _                    | _                    | CSS41 <sup>(1)</sup> | CSS40 <sup>(1)</sup> |

| 7:0       | R/W-0                | U-0                  |

| 7.0       | CSS39 <sup>(1)</sup> | CSS38 <sup>(1)</sup> | CSS37 <sup>(1)</sup> | CSS36 <sup>(1)</sup> | CSS35 <sup>(1)</sup> | CSS34 <sup>(1)</sup> | CSS33 <sup>(1)</sup> | _                    |

#### REGISTER 25-12: ADCCSS2: ADC COMMON SCAN SELECT REGISTER 2

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31-22 Unimplemented: Read as '0'

| bit 21-20 | <b>CSS53:CSS52:</b> Analog Common Scan Select bits 1 = Select AN <i>x</i> for input scan |

|-----------|------------------------------------------------------------------------------------------|

|           | 0 = Skip AN <i>x</i> for input scan                                                      |

| h:+ 10    | Unimulamented, Deed as (0)                                                               |

- bit 19 Unimplemented: Read as '0'

- bit 21-20 **CSS50:CSS45:** Analog Common Scan Select bits 1 = Select AN*x* for input scan 0 = Skip AN*x* for input scan bit 9-1 **CSS41:CSS33:** Analog Common Scan Select bits

- 1 = Select AN x for input scan0 = Skip AN x for input scan

- bit 0 Unimplemented: Read as '0'

- Note 1: This bit is not available on 64-pin devices.

- 2: CSS50-CSS53 are internal analog inputs with respect to (IVREF, IVREF Temp, VBAT/2, and CTMU Temp).

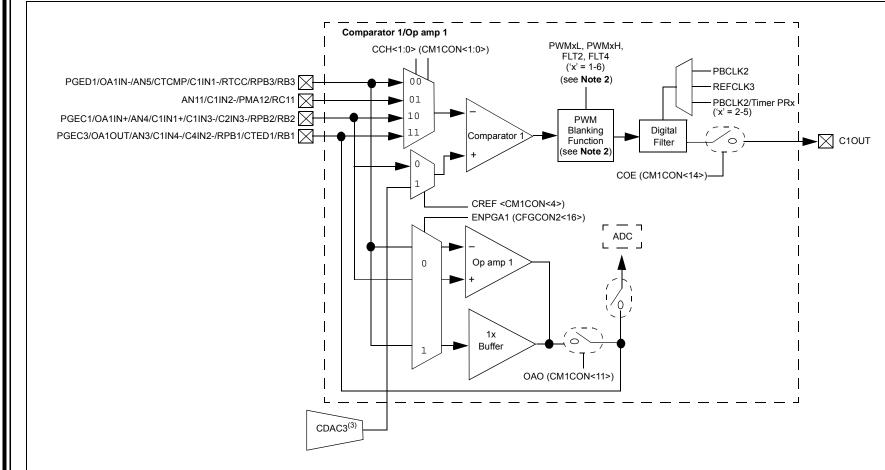

# FIGURE 27-1: OP AMP 1/COMPARATOR 1 MODULE BLOCK DIAGRAM

Note 1: Refer to the device pin tables (Table 3 and Table 5) for other analog inputs that may be also be connected to the Op amp and Comparator inputs.

- 2: The PWM Blank Function is available only on PIC32MKXXMCXXX devices.

- 3: Caution: To avoid false comparator output faults or glitches when using the internal DAC as a comparator reference, always initialize the DAC before initializing and enabling the comparator.

0

# 27.8 Op amp/Comparator Control Registers

#### TABLE 27-2: OP AMP/COMPARATOR REGISTER MAP

| ess                       |                                 | 6         |       |       |       |       |       |        |         | Bits  |      |              |          |       |         |         |          |       |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------|---------|-------|------|--------------|----------|-------|---------|---------|----------|-------|------------|

| Virtual Address<br>(BF82) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10  | 25/9    | 24/8  | 23/7 | 22/6         | 21/5     | 20/4  | 19/3    | 18/2    | 17/1     | 16/0  | All Resets |

| C000                      | CMSTAT                          | 31:16     | —     | —     | —     | —     | —     | -      | —       | —     | —    | —            | —        | —     | —       | —       | —        | —     | 0000       |

| 0000                      | CINISTAT                        | 15:0      |       | -     | SIDL  | —     | -     | —      | —       |       |      | -            | _        | C5OUT | C4OUT   | C3OUT   | C2OUT    | C10UT | 0000       |

| C010                      | CM1CON                          | 31:16     |       |       | —     | —     |       | -      | —       |       |      | С            | FSEL<2:0 | >     | CFLTREN | CF      | DIV<2:0> |       | 0000       |

| 0010                      | CINICON                         | 15:0      | ON    | COE   | CPOL  | _     | OAO   | AMPMOD | _       | COUT  | EVPO | L<1:0>       | _        | CREF  | _       | _       | CCH      | <1:0> | 0000       |

| C020                      | CM1MSKCON <sup>(2)</sup>        | 31:16     | —     | —     | —     | —     |       | SELSR  | CC<3:0> |       |      | SELSRC       | B<3:0>   |       |         | SELSRCA | <3:0>    |       | 0000       |

| 0020                      |                                 | 15:0      | HLMS  | -     | OCEN  | OCNEN | OBEN  | OBNEN  | OAEN    | OANEN | NAGS | PAGS         | ACEN     | ACNEN | ABEN    | ABNEN   | AAEN     | AANEN | 0000       |

| C030                      | CM2CON                          | 31:16     |       | -     | _     | —     |       | —      | —       | -     | -    | C            | FSEL<2:0 | >     | CFLTREN | CF      | DIV<2:0> |       | 0000       |

| 0000                      | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     | OAO   | AMPMOD | _       | COUT  | EVPO | L<1:0>       | —        | CREF  | —       |         | CCH      | <1:0> | 0000       |

| C040                      | CM2MSKCON <sup>(2)</sup>        | 31:16     |       | -     | _     | —     |       | SELSR  | CC<3:0> |       |      | SELSRCB<3:0> |          |       | SELSRCA | <3:0>   |          | 0000  |            |

| 0040                      |                                 | 15:0      | HLMS  | _     | OCEN  | OCNEN | OBEN  | OBNEN  | OAEN    | OANEN | NAGS | PAGS         | ACEN     | ACNEN | ABEN    | ABNEN   |          | AANEN | 0000       |

| C050                      | CM3CON                          | 31:16     | _     | _     | —     | —     | _     | —      | _       | _     | _    | C            | FSEL<2:0 | >     | CFLTREN | CF      | DIV<2:0> |       | 0000       |

| 0000                      | omeeen                          | 15:0      | ON    | COE   | CPOL  | —     | OAO   | AMPMOD | —       | COUT  | EVPO |              | —        | CREF  | —       | —       | CCH      | <1:0> | 0000       |

| C060                      | CM3MSKCON <sup>(2)</sup>        | 31:16     | _     | _     | —     | —     |       | SELSR  | CC<3:0> |       |      | SELSRC       | B<3:0>   |       |         | SELSRCA |          |       | 0000       |

| 0000                      |                                 | 15:0      | HLMS  | _     | OCEN  | OCNEN | OBEN  | OBNEN  | OAEN    | OANEN | NAGS | PAGS         | ACEN     | ACNEN | ABEN    | ABNEN   |          | AANEN | 0000       |

| C070                      | CM4CON                          | 31:16     | —     | _     |       | —     | _     | —      | _       | _     | —    | C            | FSEL<2:0 | >     | CFLTREN | CF      | DIV<2:0> |       | 0000       |

|                           |                                 | 15:0      | ON    | COE   | CPOL  | _     |       | —      | _       | COUT  | EVPO | L<1:0>       | —        | CREF  | —       | —       | CCH      | <1:0> | 0000       |

| C080                      | CM4MSKCON <sup>(2)</sup>        | 31:16     | —     | _     |       | —     |       | r      | CC<3:0> |       |      | SELSRCB<3:0> |          |       | SELSRCA |         |          | 0000  |            |

| 0000                      |                                 | 15:0      | HLMS  | _     | OCEN  | OCNEN | OBEN  | OBNEN  | OAEN    | OANEN | NAGS | PAGS         | ACEN     | ACNEN | ABEN    | ABNEN   |          | AANEN | 0000       |

| C090                      | CM5CON                          | 31:16     | _     | —     | —     | —     |       | —      | —       | —     | —    | -            | FSEL<2:0 |       | CFLTREN | CF      | DIV<2:0> |       | 0000       |

|                           |                                 | 15:0      | ON    | COE   | CPOL  | —     | OAO   | AMPMOD | _       | COUT  | EVPO | L<1:0>       | —        | CREF  | —       | _       | CCH      | <1:0> | 0000       |

| C0A0                      | CM5MSKCON <sup>(2)</sup>        | 31:16     | —     | —     | —     | _     |       |        | CC<3:0> |       |      | SELSRC       | -        | 1     |         | SELSRCA |          |       | 0000       |

|                           |                                 | 15:0      | HLMS  | _     | OCEN  | OCNEN | OBEN  | OBNEN  | OAEN    | OANEN | NAGS | PAGS         | ACEN     | ACNEN | ABEN    | ABNEN   | AAEN     | AANEN | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See 13.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on PIC32MKXXMCXX devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0              R/W-0            |  |  |  |  |  |

| 31:24        | VELCNT<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0              R/W-0            |  |  |  |  |  |

| 23:16        |                   | VELCNT<23:16>     |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0              R/W-0            |  |  |  |  |  |

| 15:8         | VELCNT<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0              R/W-0            |  |  |  |  |  |

| 7:0          |                   | •                 | •                 | VELCN             | IT<7:0>           |                   |                  | •                |  |  |  |  |  |

#### REGISTER 30-5: VELxCNT: VELOCITY COUNTER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-0 VELCNT<31:0>: 32-bit Velocity Counter bits

The velocity counter is automatically cleared after every processor read of the velocity counter. It is not reset by the index input or otherwise affected by any of the PIMOD<2:0> specified modes. The contents of the counter represents the distance traveled during the time between samples. Velocity equals the distance traveled per unit of time. The velocity counter can save the application software the trouble of performing 32-bit math operations between current and previous position counter values to calculate velocity. If the velocity counter rolls over from 0x7FFFFFFF to 0x80000000, or from 0x80000000 to 0x7FFFFFFF, an overflow/underflow condition is detected. If the VELOVIEN bit is set in the QEISTAT register, an interrupt will be generated.

# **PIC32MK GP/MC Family**

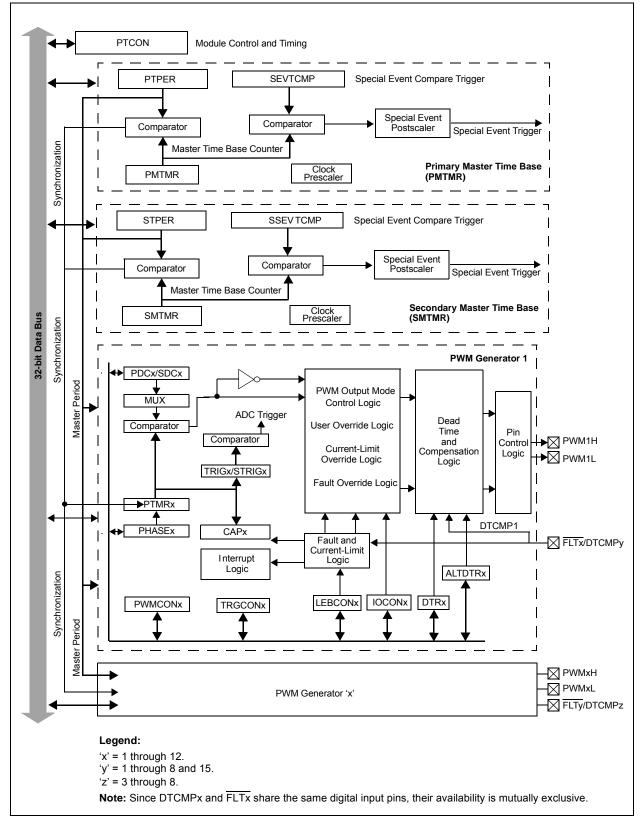

#### FIGURE 31-2: MOTOR CONTROL PWM MODULE REGISTER INTERCONNECTION DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/P               | r-1               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

|              | UPLLEN            | LLEN — BORSEL     |                   | FDSEN             | DSWDTEN           | DSWDTOSC DSWD     |                  | TPS<4:3>         |  |  |

| 23:16        | R/P                R/P              |  |  |

|              | DSWDTPS<2:0> DSE  |                   |                   | DSBOREN           | VBAT-<br>BOREN    | FPLLODIV<2:0>     |                  |                  |  |  |

| 15:8         | r-1               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

|              | _                 | FPLLMULT<6:0>     |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |  |

|              | FPLLICLK          | F                 | PLLRNG<2:0        | >                 |                   | FPLLIDIV<2:0>     |                  |                  |  |  |

#### REGISTER 33-5: DEVCFG2: DEVICE CONFIGURATION WORD 2

| Legend:           | r = Reserved bit | P = Programmable bit   | P = Programmable bit |  |  |  |

|-------------------|------------------|------------------------|----------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'          |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown   |  |  |  |

- bit 31 UPLLEN: USB PLL Enable bit

- 1 = USB PLL is disabled

- 0 = USB PLL is enabled

- bit 30 Reserved: Write as '1'

- bit 29 BORSEL: Brown-out Reset Select Trip Voltage bit

- 1 = BOR trip voltage 2.1V (non-Op amp device operation)

- 0 = BOR trip voltage 2.8V (Op amp device operation)

- **Note:** The user application should select the greatest BORSEL voltage to enable the highest trip voltage possible that is still less than VDD application operating voltage.

- bit 28 **FDSEN:** Deep Sleep Bit Enable bit

- 1 = DS bit (DSCON<15>) is enabled on a WAIT command

- 0 = DS bit (DSCON<15>) is disabled

- bit 27 DSWDTEN: Deep Sleep Watchdog Timer Enable bit

- 1 = Enable DSWDT during Deep Sleep

- 0 = Disable DSWDT during Deep Sleep

- bit 26 **DSWDTOSC:** Deep Sleep Watchdog Timer Reference Clock Select bit

- 1 = Select LPRC as DSWDT reference clock

- 0 = Select SOSC as DSWDT reference clock

| AC CHARACTERISTICS <sup>(2)</sup> |                   |                                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.2V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                               |                              |                                                                                                                                                                                                                                                                           |  |

|-----------------------------------|-------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.                     | Symbol            | Characteristics                                            | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(1)</sup> | Max.                          | Units                        | Conditions                                                                                                                                                                                                                                                                |  |

| Clock Parameters                  |                   |                                                            |                                                                                                                                                                                                                                                                                       |                     |                               |                              |                                                                                                                                                                                                                                                                           |  |

| AD50                              | Tad               | ADC Clock Period                                           | 16.667                                                                                                                                                                                                                                                                                | _                   | 6250                          | ns                           | —                                                                                                                                                                                                                                                                         |  |

| Through                           | Throughput Rate   |                                                            |                                                                                                                                                                                                                                                                                       |                     |                               |                              |                                                                                                                                                                                                                                                                           |  |

| AD51 F                            | Ftp               | Sample Rate for<br>ADC0-ADC5<br>(Class 1 Inputs)           | <br>                                                                                                                                                                                                                                                                                  | <br>                | 3.75<br>4.284<br>4.992<br>6   | Msps<br>Msps<br>Msps<br>Msps | 12-bit resolution Source Impedance $\leq 200\Omega$ 10-bit resolution Source Impedance $\leq 200\Omega$ 8-bit resolution Source Impedance $\leq 200\Omega$ 6-bit resolution Source Impedance $\leq 200\Omega$                                                             |  |

|                                   |                   | Sample Rate for<br>ADC7<br>(Class 2 and Class<br>3 Inputs) | <br> <br>                                                                                                                                                                                                                                                                             |                     | 3.53<br>4.00<br>4.615<br>5.45 | Msps<br>Msps<br>Msps<br>Msps | $\begin{array}{l} \mbox{12-bit resolution Source Impedance} \leq 200\Omega \\ \mbox{10-bit resolution Source Impedance} \leq 200\Omega \\ \mbox{8-bit resolution Source Impedance} \leq 200\Omega \\ \mbox{6-bit resolution Source Impedance} \leq 200\Omega \end{array}$ |  |

| Timing                            | Timing Parameters |                                                            |                                                                                                                                                                                                                                                                                       |                     |                               |                              |                                                                                                                                                                                                                                                                           |  |

| AD60                              | TSAMP             | Sample Time for<br>ADC0-ADC5<br>(Class 1 Inputs)           | 3<br>4<br>5<br>13                                                                                                                                                                                                                                                                     | _                   | _                             | Tad                          | Source Impedance $\leq 200\Omega$ , Max ADC clock<br>Source Impedance $\leq 500\Omega$ , Max ADC clock<br>Source Impedance $\leq 1 \text{ K}\Omega$ , Max ADC clock<br>Source Impedance $\leq 5 \text{ K}\Omega$ , Max ADC clock                                          |  |

|                                   |                   | Sample Time for<br>ADC7<br>(Class 2 and Class<br>3 Inputs) | 4<br>5<br>6<br>14                                                                                                                                                                                                                                                                     | _                   | _                             | Tad                          | Source Impedance $\leq 200\Omega$ , Max ADC clock<br>Source Impedance $\leq 500\Omega$ , Max ADC clock<br>Source Impedance $\leq 1 \text{ K}\Omega$ , Max ADC clock<br>Source Impedance $\leq 5 \text{ K}\Omega$ , Max ADC clock                                          |  |

|                                   |                   | Sample Time for<br>ADC7<br>(Class 2 and Class<br>3 Inputs) | See<br>Table<br>36-41                                                                                                                                                                                                                                                                 | _                   | _                             | Tad                          | CVDEN (ADCCON1<11>) = 1                                                                                                                                                                                                                                                   |  |

| AD62                              | TCONV             | Conversion Time<br>(after sample time is<br>complete)      |                                                                                                                                                                                                                                                                                       |                     | 13<br>11<br>9<br>7            | Tad                          | 12-bit resolution<br>10-bit resolution<br>8-bit resolution<br>6-bit resolution                                                                                                                                                                                            |  |

| AD65                              | Twake             | Wake-up time from<br>Low-Power Mode                        |                                                                                                                                                                                                                                                                                       | 500<br>20           |                               | Tad<br>μs                    | Lesser of 500 Tad or 20 µs                                                                                                                                                                                                                                                |  |

# TABLE 36-40: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is guaranteed, but not characterized.

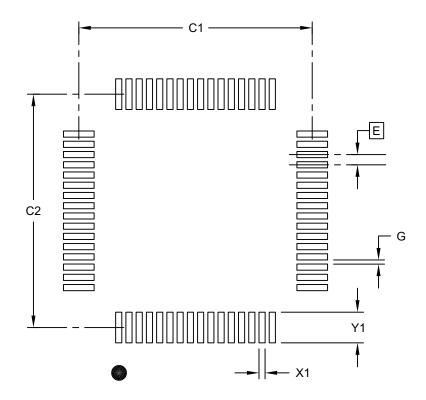

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |  |

|--------------------------|-------------|----------|-------|------|--|

| Dimension                | MIN         | NOM      | MAX   |      |  |

| Contact Pitch            | E           | 0.50 BSC |       |      |  |

| Contact Pad Spacing      | C1          |          | 11.40 |      |  |

| Contact Pad Spacing      | C2          |          | 11.40 |      |  |

| Contact Pad Width (X28)  | X1          |          |       | 0.30 |  |

| Contact Pad Length (X28) | Y1          |          |       | 1.50 |  |

| Distance Between Pads    | G           | 0.20     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2085B Sheet 1 of 1

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support