Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 39                                                          |

| Program Memory Size        | 16KB (16K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 16x12b                                                  |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dv16amlf |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 4 Memory**

Table 4-3. High-Page Register Summary (Sheet 2 of 3)

| Address           | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x1847            | Reserved      | —      | —      | —      | —      | —      | —      | —      | —      |

| 0x1848            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1849            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x184A            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x184B            | Reserved      |        | —      |        | _      | _      | _      | —      | —      |

| 0x184C            | PTBSC         | 0      | 0      | 0      | 0      | PTBIF  | PTBACK | PTBIE  | PTBMOD |

| 0x184D            | PTBPS         | PTBPS7 | PTBPS6 | PTBPS5 | PTBPS4 | PTBPS3 | PTBPS2 | PTBPS1 | PTBPS0 |

| 0x184E            | PTBES         | PTBES7 | PTBES6 | PTBES5 | PTBES4 | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| 0x184F            | Reserved      |        |        | _      | _      |        | _      | —      | _      |

| 0x1850            | PTCPE         | PTCPE7 | PTCPE6 | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1851            | PTCSE         | PTCSE7 | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x1852            | PTCDS         | PTCDS7 | PTCDS6 | PTCDS5 | PTCDS4 | PTCDS3 | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x1853–<br>0x1857 | Reserved      | _      | _      | _      | _      | _      | _      | _      | _      |

| 0x1858            | PTDPE         | PTDPE7 | PTDPE6 | PTDPE5 | PTDPE4 | PTDPE3 | PTDPE2 | PTDPE1 | PTDPE0 |

| 0x1859            | PTDSE         | PTDSE7 | PTDSE6 | PTDSE5 | PTDSE4 | PTDSE3 | PTDSE2 | PTDSE1 | PTDSE0 |

| 0x185A            | PTDDS         | PTDDS7 | PTDDS6 | PTDDS5 | PTDDS4 | PTDDS3 | PTDDS2 | PTDDS1 | PTDDS0 |

| 0x185B            | Reserved      | —      | _      | _      | _      | —      | _      | —      | —      |

| 0x185C            | PTDSC         | 0      | 0      | 0      | 0      | PTDIF  | PTDACK | PTDIE  | PTDMOD |

| 0x185D            | PTDPS         | PTDPS7 | PTDPS6 | PTDPS5 | PTDPS4 | PTDPS3 | PTDPS2 | PTDPS1 | PTDPS0 |

| 0x185E            | PTDES         | PTDES7 | PTDES6 | PTDES5 | PTDES4 | PTDES3 | PTDES2 | PTDES1 | PTDES0 |

| 0x185F            | Reserved      | —      | _      | _      | _      | —      | _      | —      | —      |

| 0x1860            | PTEPE         | PTEPE7 | PTEPE6 | PTEPE5 | PTEPE4 | PTEPE3 | PTEPE2 | PTEPE1 | PTEPE0 |

| 0x1861            | PTESE         | PTESE7 | PTESE6 | PTESE5 | PTESE4 | PTESE3 | PTESE2 | PTESE1 | PTESE0 |

| 0x1862            | PTEDS         | PTEDS7 | PTEDS6 | PTEDS5 | PTEDS4 | PTEDS3 | PTEDS2 | PTEDS1 | PTEDS0 |

| 0x1863–<br>0x1867 | Reserved      | _      | _      |        |        | _      |        | _      | _      |

| 0x1868            | PTFPE         | PTFPE7 | PTFPE6 | PTFPE5 | PTFPE4 | PTFPE3 | PTFPE2 | PTFPE1 | PTFPE0 |

| 0x1869            | PTFSE         | PTFSE7 | PTFSE6 | PTFSE5 | PTFSE4 | PTFSE3 | PTFSE2 | PTFSE1 | PTFSE0 |

| 0x186A            | PTFDS         | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| 0x186B–<br>0x186F | Reserved      | _      | _      |        |        | _      | _      | _      | _      |

| 0x1870            | PTGPE         | 0      | 0      | PTGPE5 | PTGPE4 | PTGPE3 | PTGPE2 | PTGPE1 | PTGPE0 |

| 0x1871            | PTGSE         | 0      | 0      | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| 0x1872            | PTGDS         | 0      | 0      | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| 0x1873–<br>0x187F | Reserved      |        |        |        |        |        |        |        |        |

| 0x1880            | CANCTL0       | RXFRM  | RXACT  | CSWAI  | SYNCH  | TIME   | WUPE   | SLPRQ  | INITRQ |

| 0x1881            | CANCTL1       | CANE   | CLKSRC | LOOPB  | LISTEN | BORM   | WUPM   | SLPAK  | INITAK |

| 0x1882            | CANBTR0       | SJW1   | SJW0   | BRP5   | BRP4   | BRP3   | BRP2   | BRP1   | BRP0   |

|                   |               |        |        |        |        |        |        |        |        |

MC9S08DV60 Series Data Sheet, Rev 3

Chapter 5 Resets, Interrupts, and General System Control

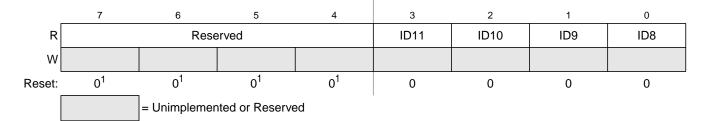

# 5.8.6 System Device Identification Register (SDIDH, SDIDL)

These high page read-only registers are included so host development systems can identify the HCS08 derivative and revision number. This allows the development software to recognize where specific memory blocks, registers, and control bits are located in a target MCU.

<sup>1</sup> The revision number that is hard coded into these bits reflects the current silicon revision level.

#### Figure 5-7. System Device Identification Register — High (SDIDH)

### Table 5-8. SDIDH Register Field Descriptions

| Field         | Description                                                                           |

|---------------|---------------------------------------------------------------------------------------|

| 3:0<br>ID[11: | n Number — MC9S08DV60 Series MCUs are hard-coded to the value 0x00E. See also ID bits |

| _      | 7                           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| R      | ID7                         | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |  |

| w      |                             |     |     |     |     |     |     |     |  |

| Reset: | 0                           | 0   | 0   | 0   | 1   | 1   | 1   | 0   |  |

|        | = Unimplemented or Reserved |     |     |     |     |     |     |     |  |

### Figure 5-8. System Device Identification Register — Low (SDIDL)

Table 5-9. SDIDL Register Field Descriptions

| Field          | Description                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[7:0] | Part Identification Number — MC9S08DV60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-8. |

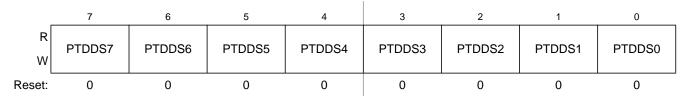

## 6.5.4.5 Port D Drive Strength Selection Register (PTDDS)

Figure 6-28. Drive Strength Selection for Port D Register (PTDDS)

### Table 6-26. PTDDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTDDS[7:0] | <ul> <li>Output Drive Strength Selection for Port D Bits — Each of these control bits selects between low and high output drive for the associated PTD pin. For port D pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port D bit n.</li> <li>1 High output drive strength selected for port D bit n.</li> </ul> |

### 6.5.4.6 Port D Interrupt Status and Control Register (PTDSC)

|        | 7 | 6                           | 5 | 4 | 3     | 2      | 1     | 0      |  |

|--------|---|-----------------------------|---|---|-------|--------|-------|--------|--|

| R      | 0 | 0                           | 0 | 0 | PTDIF | 0      | PTDIE | PTDMOD |  |

| W      |   |                             |   |   |       | PTDACK | FIDE  |        |  |

| Reset: | 0 | 0                           | 0 | 0 | 0     | 0      | 0     | 0      |  |

|        |   | = Unimplemented or Reserved |   |   |       |        |       |        |  |

### Figure 6-29. Port D Interrupt Status and Control Register (PTDSC)

#### Table 6-27. PTDSC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTDIF  | <ul> <li>Port D Interrupt Flag — PTDIF indicates when a port D interrupt is detected. Writes have no effect on PTDIF.</li> <li>0 No port D interrupt detected.</li> <li>1 Port D interrupt detected.</li> </ul>                         |

| 2<br>PTDACK | <b>Port D Interrupt Acknowledge</b> — Writing a 1 to PTDACK is part of the flag clearing mechanism. PTDACK always reads as 0.                                                                                                           |

| 1<br>PTDIE  | <ul> <li>Port D Interrupt Enable — PTDIE determines whether a port D interrupt is requested.</li> <li>0 Port D interrupt request not enabled.</li> <li>1 Port D interrupt request enabled.</li> </ul>                                   |

| 0<br>PTDMOD | <ul> <li>Port A Detection Mode — PTDMOD (along with the PTDES bits) controls the detection mode of the port D interrupt pins.</li> <li>0 Port D pins detect edges only.</li> <li>1 Port D pins detect both edges and levels.</li> </ul> |

Chapter 7 Central Processor Unit (S08CPUV3)

# 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

| Source<br>Form                                                                                                  | Operation                                                                               | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                  | Affect<br>on CCR      |            |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------|-----------------------|------------|

| Form                                                                                                            |                                                                                         | Add                                                 |                                                                                  | δ                               | Details                                                | <b>V</b> 1 1 <b>H</b> | INZC       |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry<br>A $\leftarrow$ (A) + (M) + (C)                                        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A9 ii<br>B9 dd<br>C9 hh ll<br>D9 ee ff<br>E9 ff<br>F9<br>9E D9 ee ff<br>9E E9 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp        | ↓11↓                  | - ↓ ↓ ↓    |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry<br>A $\leftarrow$ (A) + (M)                                           | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AB ii<br>BB dd<br>CB hh 11<br>DB ee ff<br>EB ff<br>FB<br>9E DB ee ff<br>9E EB ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rpp<br>rfp<br>prpp<br>prpp | \$11\$                | - \$ \$ \$ |

| AIS #opr8i                                                                                                      | Add Immediate Value (Signed) to Stack Pointer $SP \leftarrow (SP) + (M)$                | ІММ                                                 | A7 ii                                                                            | 2                               | qq                                                     | - 1 1 -               |            |

| AIX #opr8i                                                                                                      | Add Immediate Value (Signed) to<br>Index Register (H:X)<br>$H:X \leftarrow (H:X) + (M)$ | IMM                                                 | AF ii                                                                            | 2                               | qq                                                     | - 1 1 -               |            |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP | Logical AND<br>A $\leftarrow$ (A) & (M)                                                 | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp       | 011-                  | - \$ \$ -  |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL oprx8,SP                                              | Arithmetic Shift Left                                                                   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp             | ↓11-                  | - \$ \$ \$ |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                              | Arithmetic Shift Right                                                                  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp             | ↓11-                  | - ↓ ↓ ↓    |

Table 7-2. Instruction Set Summary (Sheet 1 of 9)

configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

## 10.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled, a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

### 10.4.4.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADCRH and ADCRL. This is indicated by the setting of COCO. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADCRH and ADCRL if the previous data is in the process of being read while in 12-bit or 10-bit MODE (the ADCRH register has been read but the ADCRL register has not). When blocking is active, the data transfer is blocked, COCO is not set, and the new result is lost. In the case of single conversions with the compare function enabled and the compare condition false, blocking has no effect and ADC operation is terminated. In all other cases of operation, when a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled).

If single conversions are enabled, the blocking mechanism could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

### **10.4.4.3** Aborting Conversions

Any conversion in progress is aborted when:

- A write to ADCSC1 occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADCSC2, ADCCFG, ADCCVH, or ADCCVL occurs. This indicates a mode of operation change has occurred and the current conversion is therefore invalid.

- The MCU is reset.

- The MCU enters stop mode with ADACK not enabled.

# Chapter 12 Freescale Controller Area Network (S08MSCANV1)

# 12.1 Introduction

The Freescale controller area network (MSCAN) is a communication controller implementing the CAN 2.0A/B protocol as defined in the Bosch specification dated September 1991. To fully understand the MSCAN specification, it is recommended that the Bosch specification be read first to gain familiarity with the terms and concepts contained within this document.

Though not exclusively intended for automotive applications, CAN protocol is designed to meet the specific requirements of a vehicle serial data bus: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness, and required bandwidth.

MSCAN uses an advanced buffer arrangement resulting in predictable real-time behavior and simplified application software.

The MSCAN module is available in all devices in the MC9S08DV60 Series.

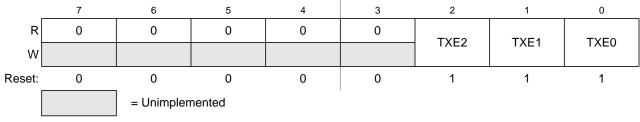

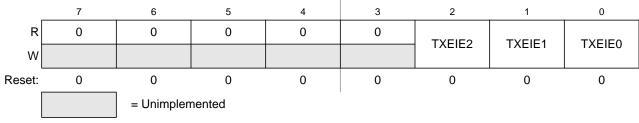

### Figure 12-10. MSCAN Transmitter Flag Register (CANTFLG)

### NOTE

The CANTFLG register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable when not in initialization mode (INITRQ = 0 and INITAK = 0).

Read: Anytime

Write: Anytime for TXEx flags when not in initialization mode; write of 1 clears flag, write of 0 is ignored

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0<br>TXE[2:0] | <ul> <li>Transmitter Buffer Empty — This flag indicates that the associated transmit message buffer is empty, and thus not scheduled for transmission. The CPU must clear the flag after a message is set up in the transmit buffer and is due for transmission. The MSCAN sets the flag after the message is sent successfully. The flag is also set by the MSCAN when the transmission request is successfully aborted due to a pending abort request (see Section 12.3.8, "MSCAN Transmitter Message Abort Request Register (CANTARQ)"). If not masked, a transmit interrupt is pending while this flag is set.</li> <li>Clearing a TXEx flag also clears the corresponding ABTAKx (see Section 12.3.9, "MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)"). When a TXEx flag is set, the corresponding ABTRQx bit is cleared (see Section 12.3.8, "MSCAN Transmitter Message Abort Request Register (CANTARQ)").</li> <li>When listen-mode is active (see Section 12.3.2, "MSCAN Control Register 1 (CANCTL1)") the TXEx flags cannot be cleared and no transmission is started.</li> <li>Read and write accesses to the transmit buffer are blocked, if the corresponding TXEx bit is cleared (TXEx = 0) and the buffer is scheduled for transmission.</li> <li>0 The associated message buffer is full (loaded with a message due for transmission)</li> <li>1 The associated message buffer is empty (not scheduled)</li> </ul> |

#### Table 12-11. CANTFLG Register Field Descriptions

# 12.3.7 MSCAN Transmitter Interrupt Enable Register (CANTIER)

This register contains the interrupt enable bits for the transmit buffer empty interrupt flags.

MC9S08DV60 Series Data Sheet, Rev 3

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit (don't care)</li> </ul> |

#### Table 12-22. CANIDMR0–CANIDMR3 Register Field Descriptions

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AM0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Figure 12-22. MSCAN Identifier Mask Registers (Second Bank) — CANIDMR4–CANIDMR7

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

### Table 12-23. CANIDMR4–CANIDMR7 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit (don't care)</li> </ul> |

# 12.4 Programmer's Model of Message Storage

The following section details the organization of the receive and transmit message buffers and the associated control registers.

To simplify the programmer interface, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13 byte data structure.

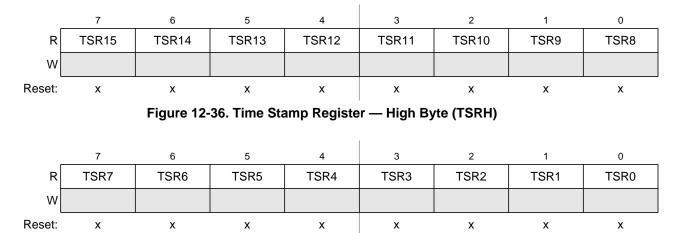

An additional transmit buffer priority register (TBPR) is defined for the transmit buffers. Within the last two bytes of this memory map, the MSCAN stores a special 16-bit time stamp, which is sampled from an internal timer after successful transmission or reception of a message. This feature is only available for transmit and receiver buffers if the TIME bit is set (see Section 12.3.1, "MSCAN Control Register 0 (CANCTL0)").

The time stamp register is written by the MSCAN. The CPU can only read these registers.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

Section 12.3.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

Figure 12-37. Time Stamp Register — Low Byte (TSRL)

Read: Anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

Write: Unimplemented

# 12.5 Functional Description

# 12.5.1 General

This section provides a complete functional description of the MSCAN. It describes each of the features and modes listed in the introduction.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

## 12.5.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

- Any CAN node is able to send out a stream of scheduled messages without releasing the CAN bus between the two messages. Such nodes arbitrate for the CAN bus immediately after sending the previous message and only release the CAN bus in case of lost arbitration.

- The internal message queue within any CAN node is organized such that the highest priority message is sent out first, if more than one message is ready to be sent.

The behavior described in the bullets above cannot be achieved with a single transmit buffer. That buffer must be reloaded immediately after the previous message is sent. This loading process lasts a finite amount of time and must be completed within the inter-frame sequence (IFS) to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU reacts with short latencies to the transmit interrupt.

A double buffer scheme de-couples the reloading of the transmit buffer from the actual message sending and, therefore, reduces the reactiveness requirements of the CPU. Problems can arise if the sending of a message is finished while the CPU re-loads the second buffer. No buffer would then be ready for transmission, and the CAN bus would be released.

At least three transmit buffers are required to meet the first of the above requirements under all circumstances. The MSCAN has three transmit buffers.

The second requirement calls for some sort of internal prioritization which the MSCAN implements with the "local priority" concept described in Section 12.5.2.2, "Transmit Structures."

# 12.5.2.2 Transmit Structures

The MSCAN triple transmit buffer scheme optimizes real-time performance by allowing multiple messages to be set up in advance. The three buffers are arranged as shown in Figure 12-38.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see Section 12.4, "Programmer's Model of Message Storage"). An additional Section 12.4.5, "Transmit Buffer Priority Register (TBPR) contains an 8-bit local priority field (PRIO) (see Section 12.4.5, "Transmit Buffer Priority Register (TBPR)"). The remaining two bytes are used for time stamping of a message, if required (see Section 12.4.6, "Time Stamp Register (TSRH–TSRL)").

To transmit a message, the CPU must identify an available transmit buffer, which is indicated by a set transmitter buffer empty (TXEx) flag (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)"). If a transmit buffer is available, the CPU must set a pointer to this buffer by writing to the CANTBSEL register (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). This makes the respective buffer accessible within the CANTXFG address space (see Section 12.4, "Programmer's Model of Message Storage"). The algorithmic feature associated with the CANTBSEL register simplifies the transmit buffer selection. In addition, this scheme makes the handler software simpler because only one address area is applicable for the transmit process, and the required address space is minimized.

The CPU then stores the identifier, the control bits, and the data content into one of the transmit buffers. Finally, the buffer is flagged as ready for transmission by clearing the associated TXE flag.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

field of the CAN frame, is received into the next available RxBG. If the MSCAN receives an invalid message in its RxBG (wrong identifier, transmission errors, etc.) the actual contents of the buffer will be over-written by the next message. The buffer will then not be shifted into the FIFO.

When the MSCAN module is transmitting, the MSCAN receives its own transmitted messages into the background receive buffer, RxBG, but does not shift it into the receiver FIFO, generate a receive interrupt, or acknowledge its own messages on the CAN bus. The exception to this rule is in loopback mode (see Section 12.3.2, "MSCAN Control Register 1 (CANCTL1)") where the MSCAN treats its own messages exactly like all other incoming messages. The MSCAN receives its own transmitted messages in the event that it loses arbitration. If arbitration is lost, the MSCAN must be prepared to become a receiver.

An overrun condition occurs when all receive message buffers in the FIFO are filled with correctly received messages with accepted identifiers and another message is correctly received from the CAN bus with an accepted identifier. The latter message is discarded and an error interrupt with overrun indication is generated if enabled (see Section 12.5.7.5, "Error Interrupt"). The MSCAN remains able to transmit messages while the receiver FIFO is full, but all incoming messages are discarded. As soon as a receive buffer in the FIFO is available again, new valid messages will be accepted.

# 12.5.3 Identifier Acceptance Filter

The MSCAN identifier acceptance registers (see Section 12.3.11, "MSCAN Identifier Acceptance Control Register (CANIDAC)") define the acceptable patterns of the standard or extended identifier (ID[10:0] or ID[28:0]). Any of these bits can be marked 'don't care' in the MSCAN identifier mask registers (see Section 12.3.16, "MSCAN Identifier Mask Registers (CANIDMR0–CANIDMR7)").

A filter hit is indicated to the application software by a set receive buffer full flag (RXF = 1) and three bits in the CANIDAC register (see Section 12.3.11, "MSCAN Identifier Acceptance Control Register (CANIDAC)"). These identifier hit flags (IDHIT[2:0]) clearly identify the filter section that caused the acceptance. They simplify the application software's task to identify the cause of the receiver interrupt. If more than one hit occurs (two or more filters match), the lower hit has priority.

A very flexible programmable generic identifier acceptance filter has been introduced to reduce the CPU interrupt loading. The filter is programmable to operate in four different modes (see Bosch CAN 2.0A/B protocol specification):

- Two identifier acceptance filters, each to be applied to:

- The full 29 bits of the extended identifier and to the following bits of the CAN 2.0B frame:

- Remote transmission request (RTR)

- Identifier extension (IDE)

- Substitute remote request (SRR)

- The 11 bits of the standard identifier plus the RTR and IDE bits of the CAN 2.0A/B messages<sup>1</sup>. This mode implements two filters for a full length CAN 2.0B compliant extended identifier. Figure 12-39 shows how the first 32-bit filter bank (CANIDAR0–CANIDAR3, CANIDMR0–CANIDMR3) produces a filter 0 hit. Similarly, the second filter bank (CANIDAR4–CANIDAR7, CANIDMR4–CANIDMR7) produces a filter 1 hit.

<sup>1.</sup> Although this mode can be used for standard identifiers, it is recommended to use the four or eight identifier acceptance filters for standard identifiers

| Syntax         | Description                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC_SEG       | System expects transitions to occur on the CAN bus during this period.                                                                                                   |

| Transmit Point | A node in transmit mode transfers a new value to the CAN bus at this point.                                                                                              |

| Sample Point   | A node in receive mode samples the CAN bus at this point. If the<br>three samples per bit option is selected, then this point marks the<br>position of the third sample. |

The synchronization jump width (see the Bosch CAN specification for details) can be programmed in a range of 1 to 4 time quanta by setting the SJW parameter.

The SYNC\_SEG, TSEG1, TSEG2, and SJW parameters are set by programming the MSCAN bus timing registers (CANBTR0, CANBTR1) (see Section 12.3.3, "MSCAN Bus Timing Register 0 (CANBTR0)" and Section 12.3.4, "MSCAN Bus Timing Register 1 (CANBTR1)").

Table 12-35 gives an overview of the CAN compliant segment settings and the related parameter values.

NOTE

It is the user's responsibility to ensure the bit time settings are in compliance with the CAN standard.

| Time Segment 1 | TSEG1 | Time Segment 2 | TSEG2 | Synchronization<br>Jump Width | SJW |

|----------------|-------|----------------|-------|-------------------------------|-----|

| 5 10           | 49    | 2              | 1     | 12                            | 01  |

| 4 11           | 3 10  | 3              | 2     | 13                            | 02  |

| 5 12           | 4 11  | 4              | 3     | 14                            | 03  |

| 6 13           | 5 12  | 5              | 4     | 14                            | 03  |

| 7 14           | 6 13  | 6              | 5     | 14                            | 03  |

| 8 15           | 7 14  | 7              | 6     | 14                            | 03  |

| 9 16           | 8 15  | 8              | 7     | 14                            | 03  |

Table 12-35. CAN Standard Compliant Bit Time Segment Settings

## 12.5.4 Modes of Operation

### 12.5.4.1 Normal Modes

The MSCAN module behaves as described within this specification in all normal system operation modes.

### 12.5.4.2 Special Modes

The MSCAN module behaves as described within this specification in all special system operation modes.

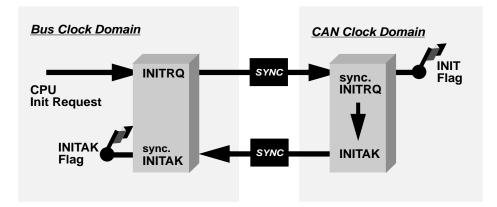

## 12.5.5.5 MSCAN Initialization Mode

In initialization mode, any on-going transmission or reception is immediately aborted and synchronization to the CAN bus is lost, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations, the MSCAN immediately drives the TXCAN pin into a recessive state.

### NOTE

The user is responsible for ensuring that the MSCAN is not active when initialization mode is entered. The recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before setting the INITRQ bit in the CANCTL0 register. Otherwise, the abort of an on-going message can cause an error condition and can impact other CAN bus devices.

In initialization mode, the MSCAN is stopped. However, interface registers remain accessible. This mode is used to reset the CANCTLO, CANRFLG, CANRIER, CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL registers to their default values. In addition, the MSCAN enables the configuration of the CANBTRO, CANBTR1 bit timing registers; CANIDAC; and the CANIDAR, CANIDMR message filters. See Section 12.3.1, "MSCAN Control Register 0 (CANCTLO)," for a detailed description of the initialization mode.

Figure 12-46. Initialization Request/Acknowledge Cycle

Due to independent clock domains within the MSCAN, INITRQ must be synchronized to all domains by using a special handshake mechanism. This handshake causes additional synchronization delay (see Section Figure 12-46., "Initialization Request/Acknowledge Cycle").

If there is no message transfer ongoing on the CAN bus, the minimum delay will be two additional bus clocks and three additional CAN clocks. When all parts of the MSCAN are in initialization mode, the INITAK flag is set. The application software must use INITAK as a handshake indication for the request (INITRQ) to go into initialization mode.

### NOTE

The CPU cannot clear INITRQ before initialization mode (INITRQ = 1 and INITAK = 1) is active.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

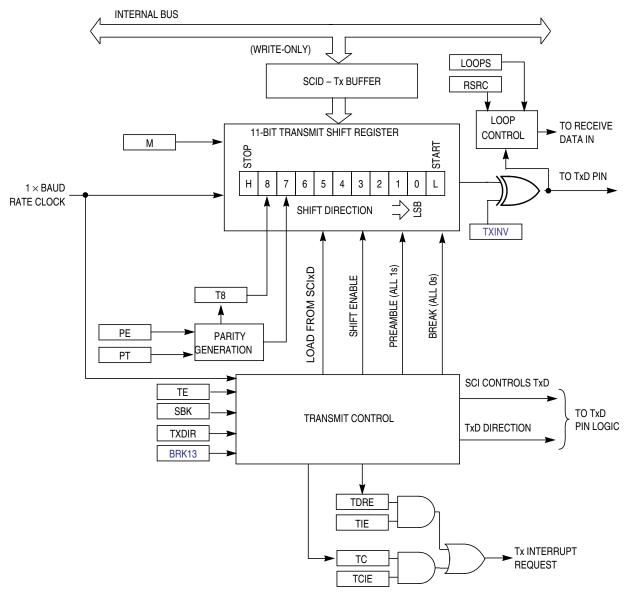

Chapter 14 Serial Communications Interface (S08SCIV4)

# 14.1.4 Block Diagram

Figure 14-2 shows the transmitter portion of the SCI.

Figure 14-2. SCI Transmitter Block Diagram

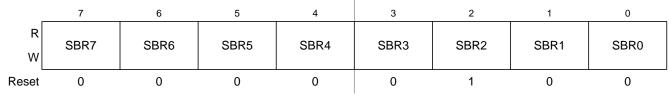

### Figure 14-5. SCI Baud Rate Register (SCIxBDL)

Table 14-3. SCIxBDL Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>SBR[7:0] | <b>Baud Rate Modulo Divisor</b> — These 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 14-2. |

# 14.2.2 SCI Control Register 1 (SCIxC1)

This read/write register is used to control various optional features of the SCI system.

|        | 7     | 6       | 5    | 4 | 3    | 2   | 1  | 0  |

|--------|-------|---------|------|---|------|-----|----|----|

| R<br>W | LOOPS | SCISWAI | RSRC | М | WAKE | ILT | PE | PT |

| Reset  | 0     | 0       | 0    | 0 | 0    | 0   | 0  | 0  |

### Figure 14-6. SCI Control Register 1 (SCIxC1)

### Table 14-4. SCIxC1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Mode Select — Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.</li> <li>0 Normal operation — RxD and TxD use separate pins.</li> <li>1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD pin is not used by SCI.</li> </ul>                                                                 |

| 6<br>SCISWAI | <ul> <li>SCI Stops in Wait Mode</li> <li>0 SCI clocks continue to run in wait mode so the SCI can be the source of an interrupt that wakes up the CPU.</li> <li>1 SCI clocks freeze while CPU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                |

| 5<br>RSRC    | <ul> <li>Receiver Source Select — This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS = 1, the receiver input is internally connected to the TxD pin and RSRC determines whether this connection is also connected to the transmitter output.</li> <li>Provided LOOPS = 1, RSRC = 0 selects internal loop back mode and the SCI does not use the RxD pins.</li> <li>Single-wire SCI mode where the TxD pin is connected to the transmitter output.</li> </ul> |

| 4<br>M       | <ul> <li>9-Bit or 8-Bit Mode Select</li> <li>0 Normal — start + 8 data bits (LSB first) + stop.</li> <li>1 Receiver and transmitter use 9-bit data characters<br/>start + 8 data bits (LSB first) + 9th data bit + stop.</li> </ul>                                                                                                                                                                                                                                                      |

Chapter 14 Serial Communications Interface (S08SCIV4)

## 16.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

### 16.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

## 16.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

### 16.4.2.1 Input Capture Mode

With the input-capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input-capture channel, the TPM latches the contents of the TPM counter into the channel-value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

In input capture mode, the TPMxCnVH and TPMxCnVL registers are read only.

When either half of the 16-bit capture register is read, the other half is latched into a buffer to support coherent 16-bit accesses in big-endian or little-endian order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) which may optionally generate a CPU interrupt request.

While in BDM, the input capture function works as configured by the user. When an external event occurs, the TPM latches the contents of the TPM counter (which is frozen because of the BDM mode) into the channel value registers and sets the flag bit.

## 16.4.2.2 Output Compare Mode

With the output-compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel-value registers of an output-compare channel, the TPM can set, clear, or toggle the channel pin.

NOTES:

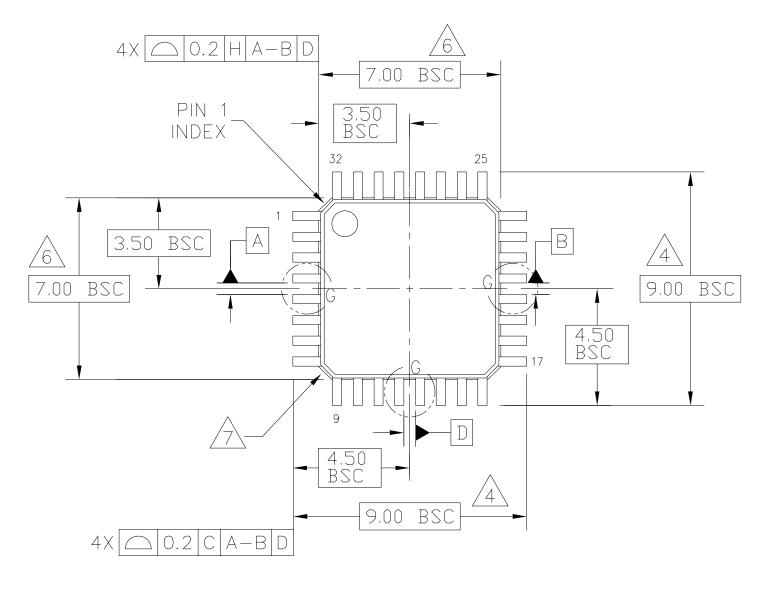

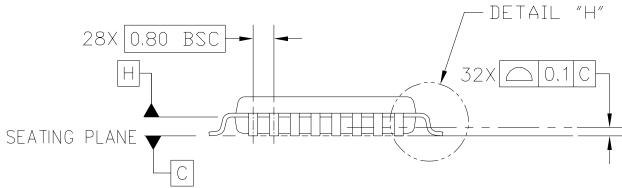

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

/4. DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.

/5]. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

/6. THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

/8]

/7. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.25 mm FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       | DOCUMENT NO  | ): 98ASS23234W   | REV: E      |

| 10 X 10 X 1.4 P                                         | CASE NUMBER  | 2: 840F-02       | 11 AUG 2006 |

| 0.5 PITCH, CASE OL                                      | STANDARD: JE | DEC MS-026 BCD   |             |

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA    | L OUTLINE      | PRINT VERSION NE | IT TO SCALE |

|---------------------------------------------------------|--------------|----------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NE  | ]: 98ASH70029A | RE∨∶D            |             |

| LOW PROFILE QUAD FLAT PA                                | CASE NUMBER  | 8: 873A-03     | 19 MAY 2005      |             |

| 32 LEAD, 0.8 PITCH (7 X                                 | STANDARD: JE | DEC MS-026 BBA |                  |             |