Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 39                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 16x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dv16mlf |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

**Section Number**

Page

### Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08DV60 Series | 21 |

|-----|----------------------------------|----|

| 1.2 | MCU Block Diagram                | 22 |

| 1.3 | System Clock Distribution        | 24 |

### Chapter 2 Pins and Connections

| 2.1 | Device | Pin Assignment                                              | 27 |

|-----|--------|-------------------------------------------------------------|----|

|     |        | nended System Connections                                   |    |

|     |        | Power                                                       |    |

|     | 2.2.2  | Oscillator                                                  | 31 |

|     | 2.2.3  | RESET                                                       | 31 |

|     | 2.2.4  | Background / Mode Select (BKGD/MS)                          | 32 |

|     |        | ADC Reference Pins (V <sub>REFH</sub> , V <sub>REFL</sub> ) |    |

|     |        | General-Purpose I/O and Peripheral Ports                    |    |

|     |        | 1 1                                                         |    |

## Chapter 3 Modes of Operation

| 3.1 | Introdu  | ction                                    | 35 |

|-----|----------|------------------------------------------|----|

| 3.2 | Feature  | S                                        | 35 |

| 3.3 | Run Mo   | ode                                      | 35 |

| 3.4 | Active 1 | Background Mode                          | 35 |

|     |          | ode                                      |    |

|     |          | odes                                     |    |

|     | 1        | Stop3 Mode                               |    |

|     |          | Stop2 Mode                               |    |

|     |          | On-Chip Peripheral Modules in Stop Modes |    |

### Chapter 4 Memory

| 4.1 | MC9S08DV60 Series Memory Map           | 41 |

|-----|----------------------------------------|----|

| 4.2 | Reset and Interrupt Vector Assignments | 42 |

| 4.3 | Register Addresses and Bit Assignments | 44 |

|     | RĂM                                    |    |

| 4.5 | Flash                                  | 52 |

|     | 4.5.1 Features                         |    |

|     |                                        |    |

MC9S08DV60 Series Data Sheet, Rev 3

# Chapter 1 Device Overview

Controller Area Network MC9S08DV60 Series devices provide significant value to customers for CAN based applications requiring peripheral flexibility. MC9S08DV60 Series devices provide lower costs, enhanced performance, higher quality, and upward pin and code compatibility with MC9S08DZ60 Series devices.

## 1.1 Devices in the MC9S08DV60 Series

This data sheet covers members of the MC9S08DV60 Series of MCUs:

- MC9S08DV60

- MC9S08DV48

- MC9S08DV32

- MC9S08DV16

Table 1-1 summarizes the feature set available in the MC9S08DV60 Series.

| Feature               | М   | C9S08DV          | 60 | M   | C9S08DV          | 48  | М     | C9S08DV          | 32    | MC9S0 | 8DV16 |

|-----------------------|-----|------------------|----|-----|------------------|-----|-------|------------------|-------|-------|-------|

| Flash size<br>(bytes) |     | 62080            |    |     | 49152            |     | 33792 |                  | 16896 |       |       |

| RAM size (bytes)      |     | 3072             |    |     | 2048             |     | 2048  |                  |       | 1024  |       |

| Pin quantity          | 64  | 48               | 32 | 64  | 48               | 32  | 64    | 48               | 32    | 48    | 32    |

| ACMP1                 |     |                  |    |     |                  | yes |       |                  |       |       |       |

| ACMP2                 | yes | yes <sup>1</sup> | no | yes | yes <sup>1</sup> | no  | yes   | yes <sup>1</sup> | no    | yes   | no    |

| ADC channels          | 16  | 16               | 10 | 16  | 16               | 10  | 16    | 16               | 10    | 16    | 10    |

| DBG                   |     |                  |    |     |                  | yes |       |                  |       |       |       |

| IIC                   |     |                  |    |     |                  | yes |       |                  |       |       |       |

| IRQ                   |     |                  |    |     |                  | yes |       |                  |       |       |       |

| MCG                   |     |                  |    |     |                  | yes |       |                  |       |       |       |

| MSCAN                 |     |                  |    |     |                  | yes |       |                  |       |       |       |

| RTC                   |     |                  |    |     |                  | yes |       |                  |       |       |       |

| SCI1                  |     |                  |    |     |                  | yes |       |                  |       |       |       |

| SCI2                  |     | yes              |    |     | yes              |     |       | yes              |       | n     | 0     |

| SPI                   |     |                  |    | •   |                  | yes |       |                  |       |       |       |

| TPM1 channels         | 6   | 6                | 4  | 6   | 6                | 4   | 6     | 6                | 4     | 6     | 4     |

| TPM2 channels         | 2   |                  |    |     |                  |     |       |                  |       |       |       |

| XOSC                  | yes |                  |    |     |                  |     |       |                  |       |       |       |

| COP Watchdog          |     |                  |    |     |                  | yes |       |                  |       |       |       |

#### Table 1-1. MC9S08DV60 Series Features by MCU and Pin Count

# Chapter 2 Pins and Connections

This section describes signals that connect to package pins. It includes pinout diagrams, recommended system connections, and detailed discussions of signals.

## 2.1 Device Pin Assignment

This section shows the pin assignments for MC9S08DV60 Series MCUs in the available packages.

Figure 2-1. 64-Pin LQFP

MC9S08DV60 Series Data Sheet, Rev 3

Chapter 3 Modes of Operation

### 3.6.1.2 Active BDM Enabled in Stop3 Mode

Entry into the active background mode from run mode is enabled if ENBDM in BDCSCR is set. This register is described in Chapter 17, "Development Support." If ENBDM is set when the CPU executes a STOP instruction, the system clocks to the background debug logic remain active when the MCU enters stop mode. Because of this, background debug communication remains possible. In addition, the voltage regulator does not enter its low-power standby state but maintains full internal regulation.

Most background commands are not available in stop mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from stop and enter active background mode if the ENBDM bit is set. After entering background debug mode, all background commands are available.

## 3.6.2 Stop2 Mode

Stop2 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. Most of the internal circuitry of the MCU is powered off in stop2 with the exception of the RAM. Upon entering stop2, all I/O pin control signals are latched so that the pins retain their states during stop2.

Exit from stop2 is performed by asserting RESET. On 3M05C or older masksets only, exit from stop2 can also be performed by asserting PTA7/ADP7/IRQ.

#### NOTE

On 3M05C or older masksets only, PTA7/ADP7/IRQ is an active low wake-up and must be configured as an input prior to executing a STOP instruction to avoid an immediate exit from stop2. PTA7/ADP7/IRQ can be disabled as a wake-up if it is configured as a high driven output. For lowest power consumption in stop2, this pin should not be left open when configured as input (enable the internal pullup; or tie an external pullup/down device; or set pin as output).

In addition, the real-time counter (RTC) can wake the MCU from stop2, if enabled.

Upon wake-up from stop2 mode, the MCU starts up as from a power-on reset (POR):

- All module control and status registers are reset

- The LVD reset function is enabled and the MCU remains in the reset state if V<sub>DD</sub> is below the LVD trip point (low trip point selected due to POR)

- The CPU takes the reset vector

In addition to the above, upon waking up from stop2, the PPDF bit in SPMSC2 is set. This flag is used to direct user code to go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

```

Chapter 4 Memory

```

#### Table 4-2. Direct-Page Register Summary (Sheet 1 of 3)

| Address                            | Register<br>Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b>                     | PTAD             | PTAD7  | PTAD6  | PTAD5  | PTAD4  | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b>                     | PTADD            | PTADD7 | PTADD6 | PTADD5 | PTADD4 | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>02</b>                     | PTBD             | PTBD7  | PTBD6  | PTBD5  | PTBD4  | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| 0x00 <b>03</b>                     | PTBDD            | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| 0x00 <b>04</b>                     | PTCD             | PTCD7  | PTCD6  | PTCD5  | PTCD4  | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

| 0x00 <b>05</b>                     | PTCDD            | PTCDD7 | PTCDD6 | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| 0x00 <b>06</b>                     | PTDD             | PTDD7  | PTDD6  | PTDD5  | PTDD4  | PTDD3  | PTDD2  | PTDD1  | PTDD0  |

| 0x00 <b>07</b>                     | PTDDD            | PTDDD7 | PTDDD6 | PTDDD5 | PTDDD4 | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| 0x00 <b>08</b>                     | PTED             | PTED7  | PTED6  | PTED5  | PTED4  | PTED3  | PTED2  | PTED1  | PTED0  |

| 0x00 <b>09</b>                     | PTEDD            | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |

| <b>A0</b> 00x0                     | PTFD             | PTFD7  | PTFD6  | PTFD5  | PTFD4  | PTFD3  | PTFD2  | PTFD1  | PTFD0  |

| 0x00 <b>0B</b>                     | PTFDD            | PTFDD7 | PTFDD6 | PTFDD5 | PTFDD4 | PTFDD3 | PTFDD2 | PTFDD1 | PTFDD0 |

| 0x00 <b>0C</b>                     | PTGD             | 0      | 0      | PTGD5  | PTGD4  | PTGD3  | PTGD2  | PTGD1  | PTGD0  |

| 0x00 <b>0D</b>                     | PTGDD            | 0      | 0      | PTGDD5 | PTGDD4 | PTGDD3 | PTGDD2 | PTGDD1 | PTGDD0 |

| 0x00 <b>0E</b>                     | ACMP1SC          | ACME   | ACBGS  | ACF    | ACIE   | ACO    | ACOPE  | ACMOD1 | ACMOD0 |

| 0x00 <b>0F</b>                     | ACMP2SC          | ACME   | ACBGS  | ACF    | ACIE   | ACO    | ACOPE  | ACMOD1 | ACMOD0 |

| 0x00 <b>10</b>                     | ADCSC1           | COCO   | AIEN   | ADCO   |        |        | ADCH   | •      |        |

| 0x00 <b>11</b>                     | ADCSC2           | ADACT  | ADTRG  | ACFE   | ACFGT  | 0      | 0      |        | —      |

| 0x00 <b>12</b>                     | ADCRH            | 0      | 0      | 0      | 0      | ADR11  | ADR10  | ADR9   | ADR8   |

| 0x00 <b>13</b>                     | ADCRL            | ADR7   | ADR6   | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

| 0x00 <b>14</b>                     | ADCCVH           | 0      | 0      | 0      | 0      | ADCV11 | ADCV10 | ADCV9  | ADCV8  |

| 0x00 <b>15</b>                     | ADCCVL           | ADCV7  | ADCV6  | ADCV5  | ADCV4  | ADCV3  | ADCV2  | ADCV1  | ADCV0  |

| 0x00 <b>16</b>                     | ADCCFG           | ADLPC  | AD     | DIV    | ADLSMP | MC     | DE     | ADI    | CLK    |

| 0x00 <b>17</b>                     | APCTL1           | ADPC7  | ADPC6  | ADPC5  | ADPC4  | ADPC3  | ADPC2  | ADPC1  | ADPC0  |

| 0x00 <b>18</b>                     | APCTL2           | ADPC15 | ADPC14 | ADPC13 | ADPC12 | ADPC11 | ADPC10 | ADPC9  | ADPC8  |

| 0x00 <b>19</b>                     | APCTL3           | ADPC23 | ADPC22 | ADPC21 | ADPC20 | ADPC19 | ADPC18 | ADPC17 | ADPC16 |

| 0x00 <b>1A</b> -<br>0x00 <b>1B</b> | Reserved         | _      | _      | _      | _      | _      | _      | _      | _      |

| 0x00 <b>1C</b>                     | IRQSC            | 0      | IRQPDD | IRQEDG | IRQPE  | IRQF   | IRQACK | IRQIE  | IRQMOD |

| 0x001 <b>D</b> –<br>0x001 <b>F</b> | Reserved         | _      | _      | _      | _      | _      |        | _      | _      |

| 0x00 <b>20</b>                     | TPM1SC           | TOF    | TOIE   | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1    | PS0    |

| 0x00 <b>21</b>                     | TPM1CNTH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>22</b>                     | TPM1CNTL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>23</b>                     | TPM1MODH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>24</b>                     | TPM1MODL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>25</b>                     | TPM1C0SC         | CH0F   | CH0IE  | MS0B   | MS0A   | ELS0B  | ELS0A  | 0      | 0      |

| 0x00 <b>26</b>                     | TPM1C0VH         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>27</b>                     | TPM1C0VL         | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

### 4.5.10 Flash Registers and Control Bits

The Flash module has seven 8-bit registers in the high-page register space and three locations in the nonvolatile register space in Flash memory. Two of those locations are copied into two corresponding high-page control registers at reset. There is also an 8-byte comparison key in Flash memory. Refer to Table 4-3 and Table 4-5 for the absolute address assignments for all Flash registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

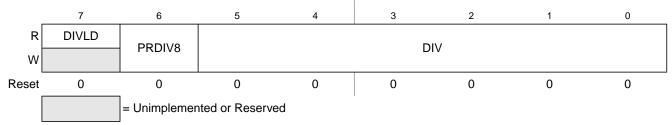

### 4.5.10.1 Flash Clock Divider Register (FCDIV)

Bit 7 of this register is a read-only flag. Bits 6:0 may be read at any time but can be written only one time. Before any erase or programming operations are possible, write to this register to set the frequency of the clock for the nonvolatile memory system within acceptable limits.

#### Figure 4-5. Flash Clock Divider Register (FCDIV)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD  | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for Flash.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for Flash.</li> </ul>                                                                                                                                                               |

| 6<br>PRDIV8 | <ul> <li>Prescale (Divide) Flash Clock by 8 (This bit is write once.)</li> <li>0 Clock input to the Flash clock divider is the bus rate clock.</li> <li>1 Clock input to the Flash clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5:0<br>DIV  | <b>Divisor for Flash Clock Divider</b> — These bits are write once. The Flash clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV field plus one. The resulting frequency of the internal Flash clock must fall within the range of 200 kHz to 150 kHz for proper Flash operations. Program/Erase timing pulses are one cycle of this internal Flash clock which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. |

#### Table 4-7. FCDIV Register Field Descriptions

if PRDIV8 = 0 —

$$f_{FCLK} = f_{Bus} \div (DIV + 1)$$

Eqn. 4-1

if PRDIV8 = 1 —

$$f_{FCLK} = f_{Bus} \div (8 \times (DIV + 1))$$

Eqn. 4-2

Table 4-8 shows the appropriate values for PRDIV8 and DIV for selected bus frequencies.

MC9S08DV60 Series Data Sheet, Rev 3

| FPS       | Address Area Protected | Memory Size Protected (bytes) | Number of Sectors Protected |

|-----------|------------------------|-------------------------------|-----------------------------|

| 0x1B      | 0x2800-0xFFFF          | 54K                           | 72                          |

| 0x1A      | 0x2200-0xFFFF          | 55.5K                         | 74                          |

| 0x19      | 0x1C00–0xFFFF          | 57K                           | 76                          |

| 0x18–0x00 | 0x0000-0xFFFF          | 64K                           | 86                          |

Table 4-13. Flash Block Protection (continued)

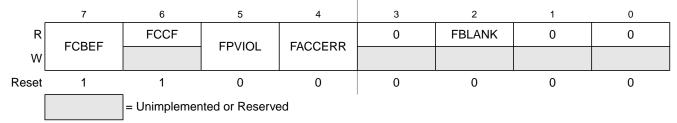

### 4.5.10.5 Flash Status Register (FSTAT)

#### Figure 4-9. Flash Status Register (FSTAT)

#### Table 4-14. FSTAT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FCBEF  | <ul> <li>Command Buffer Empty Flag — The FCBEF bit is used to launch commands. It also indicates that the command buffer is empty so that a new command sequence can be executed when performing burst programming. The FCBEF bit is cleared by writing a 1 to it or when a burst program command is transferred to the array for programming. Only burst program commands can be buffered.</li> <li>0 Command buffer is full (not ready for additional commands).</li> <li>1 A new burst program command can be written to the command buffer.</li> </ul> |

| 6<br>FCCF   | <ul> <li>Command Complete Flag — FCCF is set automatically when the command buffer is empty and no command is being processed. FCCF is cleared automatically when a new command is started (by writing 1 to FCBEF to register a command). Writing to FCCF has no meaning or effect.</li> <li>0 Command in progress</li> <li>1 All commands complete</li> </ul>                                                                                                                                                                                             |

| 5<br>FPVIOL | <ul> <li>Protection Violation Flag — FPVIOL is set automatically when a command that attempts to erase or program a location in a protected block is launched (the erroneous command is ignored). FPVIOL is cleared by writing a 1 to FPVIOL.</li> <li>0 No protection violation.</li> <li>1 An attempt was made to erase or program a protected location.</li> </ul>                                                                                                                                                                                      |

Chapter 6 Parallel Input/Output Control

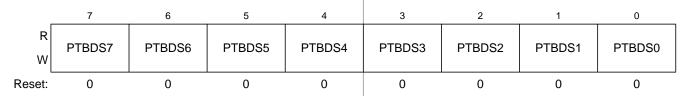

### 6.5.2.5 Port B Drive Strength Selection Register (PTBDS)

Figure 6-15. Drive Strength Selection for Port B Register (PTBDS)

#### Table 6-13. PTBDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDS[7:0] | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port B bit n.</li> <li>1 High output drive strength selected for port B bit n.</li> </ul> |

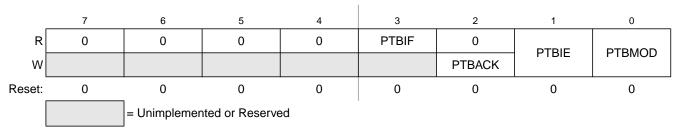

### 6.5.2.6 Port B Interrupt Status and Control Register (PTBSC)

#### Figure 6-16. Port B Interrupt Status and Control Register (PTBSC)

#### Table 6-14. PTBSC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTBIF  | <ul> <li>Port B Interrupt Flag — PTBIF indicates when a Port B interrupt is detected. Writes have no effect on PTBIF.</li> <li>0 No Port B interrupt detected.</li> <li>1 Port B interrupt detected.</li> </ul>                         |

| 2<br>PTBACK | <b>Port B Interrupt Acknowledge</b> — Writing a 1 to PTBACK is part of the flag clearing mechanism. PTBACK always reads as 0.                                                                                                           |

| 1<br>PTBIE  | <ul> <li>Port B Interrupt Enable — PTBIE determines whether a port B interrupt is requested.</li> <li>0 Port B interrupt request not enabled.</li> <li>1 Port B interrupt request enabled.</li> </ul>                                   |

| 0<br>PTBMOD | <ul> <li>Port B Detection Mode — PTBMOD (along with the PTBES bits) controls the detection mode of the port B interrupt pins.</li> <li>0 Port B pins detect edges only.</li> <li>1 Port B pins detect both edges and levels.</li> </ul> |

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

# 8.3 Register Definition

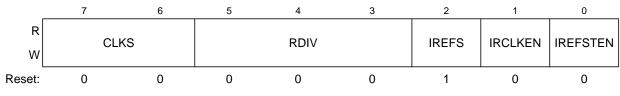

## 8.3.1 MCG Control Register 1 (MCGC1)

Figure 8-3. MCG Control Register 1 (MCGC1)

#### Table 8-1. MCG Control Register 1 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:6<br>CLKS   | Clock Source Select — Selects the system clock source.         00       Encoding 0 — Output of FLL or PLL is selected.         01       Encoding 1 — Internal reference clock is selected.         10       Encoding 2 — External reference clock is selected.         11       Encoding 3 — Reserved, defaults to 00.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 5:3<br>RDIV   | Reference Divider — Selects the amount to divide down the reference clock selected by the IREFS bit. If the         FLL is selected, the resulting frequency must be in the range 31.25 kHz to 39.0625 kHz. If the PLL is selected,         the resulting frequency must be in the range 1 MHz to 2 MHz.         000       Encoding 0 — Divides reference clock by 1 (reset default)         001       Encoding 1 — Divides reference clock by 2         010       Encoding 2 — Divides reference clock by 4         011       Encoding 3 — Divides reference clock by 8         100       Encoding 4 — Divides reference clock by 16         101       Encoding 5 — Divides reference clock by 64         111       Encoding 7 — Divides reference clock by 128 |  |  |  |  |

| 2<br>IREFS    | Internal Reference Select — Selects the reference clock source.<br>1 Internal reference clock selected<br>0 External reference clock selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — Enables the internal reference clock for use as MCGIRCLK.<br>1 MCGIRCLK active<br>0 MCGIRCLK inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 0<br>IREFSTEN | <ul> <li>Internal Reference Stop Enable — Controls whether or not the internal reference clock remains enabled when the MCG enters stop mode.</li> <li>1 Internal reference clock stays enabled in stop if IRCLKEN is set or if MCG is in FEI, FBI, or BLPI mode before entering stop</li> <li>0 Internal reference clock is disabled in stop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

### 8.5.2.2 Example # 2: Moving from PEE to BLPI Mode: External Crystal = 4 MHz, Bus Frequency =16 kHz

In this example, the MCG will move through the proper operational modes from PEE mode with a 4 MHz crystal configured for an 8 MHz bus frequency (see previous example) to BLPI mode with a 16 kHz bus frequency.First, the code sequence will be described. Then a flowchart will be included which illustrates the sequence.

- 1. First, PEE must transition to PBE mode:

- a) MCGC1 = 0x90 (%10010000)

- CLKS (bits 7 and 6) set to %10 in order to switch the system clock source to the external reference clock

- b) Loop until CLKST (bits 3 and 2) in MCGSC are %10, indicating that the external reference clock is selected to feed MCGOUT

- 2. Then, PBE must transition either directly to FBE mode or first through BLPE mode and then to FBE mode:

- a) BLPE: If a transition through BLPE mode is desired, first set LP (bit 3) in MCGC2 to 1

- b) BLPE/FBE: MCGC1 = 0xB8 (%10111000)

- RDIV (bits 5-3) set to %111, or divide-by-128 because 4 MHz / 128 = 31.25 kHz which is in the 31.25 kHz to 39.0625 kHz range required by the FLL. In BLPE mode, the configuration of the RDIV does not matter because both the FLL and PLL are disabled. Changing them only sets up the dividers for FLL usage in FBE mode

- c) BLPE/FBE: MCGC3 = 0x04 (%00000100)

- PLLS (bit 6) clear to 0 to select the FLL. In BLPE mode, changing this bit only prepares the MCG for FLL usage in FBE mode. With PLLS = 0, the VDIV value does not matter.

- d) BLPE: If transitioning through BLPE mode, clear LP (bit 3) in MCGC2 to 0 here to switch to FBE mode

- e) FBE: Loop until PLLST (bit 5) in MCGSC is clear, indicating that the current source for the PLLS clock is the FLL

- f) FBE: Optionally, loop until LOCK (bit 6) in the MCGSC is set, indicating that the FLL has acquired lock. Although the FLL is bypassed in FBE mode, it is still enabled and running.

- 3. Next, FBE mode transitions into FBI mode:

- a) MCGC1 = 0x44 (%01000100)

- CLKS (bits7 and 6) in MCGSC1 set to %01 in order to switch the system clock to the internal reference clock

- IREFS (bit 2) set to 1 to select the internal reference clock as the reference clock source

- RDIV (bits 5-3) set to %000, or divide-by-1 because the trimmed internal reference should be within the 31.25 kHz to 39.0625 kHz range required by the FLL

- b) Loop until IREFST (bit 4) in MCGSC is 1, indicating the internal reference clock has been selected as the reference clock source

- c) Loop until CLKST (bits 3 and 2) in MCGSC are %01, indicating that the internal reference clock is selected to feed MCGOUT

Chapter 11 Inter-Integrated Circuit (S08IICV2)

Refer to the direct-page register summary in the memory chapter of this document for the absolute address assignments for all IIC registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

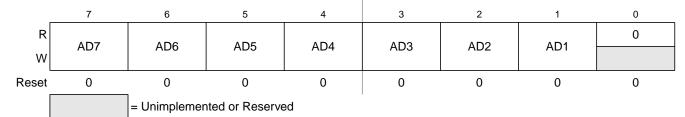

# 11.3.1 IIC Address Register (IICA)

#### Figure 11-3. IIC Address Register (IICA)

| Field          | Description                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–1<br>AD[7:1] | <b>Slave Address.</b> The AD[7:1] field contains the slave address to be used by the IIC module. This field is used on the 7-bit address scheme and the lower seven bits of the 10-bit address scheme. |

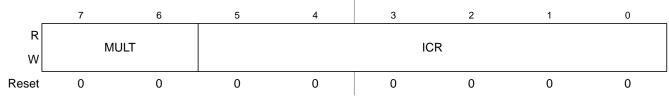

## 11.3.2 IIC Frequency Divider Register (IICF)

Figure 11-4. IIC Frequency Divider Register (IICF)

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except bits IDHITx, which are read-only

#### Table 12-16. CANIDAC Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>IDAM[1:0]  | Identifier Acceptance Mode — The CPU sets these flags to define the identifier acceptance filter organization (see Section 12.5.3, "Identifier Acceptance Filter"). Table 12-17 summarizes the different settings. In filter closed mode, no message is accepted such that the foreground buffer is never reloaded. |

| 2:0<br>IDHIT[2:0] | Identifier Acceptance Hit Indicator — The MSCAN sets these flags to indicate an identifier acceptance hit (see Section 12.5.3, "Identifier Acceptance Filter"). Table 12-18 summarizes the different settings.                                                                                                      |

Table 12-17. Identifier Acceptance Mode Settings

| IDAM1 | IDAM0 | Identifier Acceptance Mode     |  |  |  |

|-------|-------|--------------------------------|--|--|--|

| 0     | 0     | Two 32-bit acceptance filters  |  |  |  |

| 0     | 1     | Four 16-bit acceptance filters |  |  |  |

| 1     | 0     | Eight 8-bit acceptance filters |  |  |  |

| 1     | 1     | Filter closed                  |  |  |  |

| IDHIT2 | IDHIT1 | IDHIT0 | Identifier Acceptance Hit |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | Filter 0 hit              |

| 0      | 0      | 1      | Filter 1 hit              |

| 0      | 1      | 0      | Filter 2 hit              |

| 0      | 1      | 1      | Filter 3 hit              |

| 1      | 0      | 0      | Filter 4 hit              |

| 1      | 0      | 1      | Filter 5 hit              |

| 1      | 1      | 0      | Filter 6 hit              |

| 1      | 1      | 1      | Filter 7 hit              |

Table 12-18. Identifier Acceptance Hit Indication

The IDHITx indicators are always related to the message in the foreground buffer (RxFG). When a message gets shifted into the foreground buffer of the receiver FIFO the indicators are updated as well.

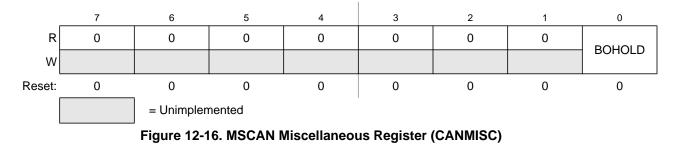

### 12.3.12 MSCAN Miscellaneous Register (CANMISC)

This register provides additional features.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

Read: Anytime Write: Anytime; write of '1' clears flag; write of '0' ignored

Table 12-19. CANMISC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BOHOLD | <ul> <li>Bus-off State Hold Until User Request — If BORM is set in Section 12.3.2, "MSCAN Control Register 1 (CANCTL1), this bit indicates whether the module has entered the bus-off state. Clearing this bit requests the recovery from bus-off. Refer to Section 12.6.2, "Bus-Off Recovery," for details.</li> <li>0 Module is not bus-off or recovery has been requested by user in bus-off state</li> <li>1 Module is bus-off and holds this state until user request</li> </ul> |

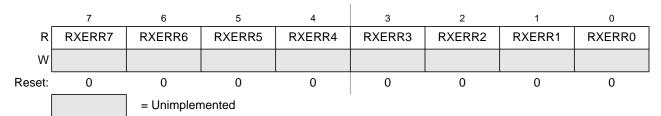

## 12.3.13 MSCAN Receive Error Counter (CANRXERR)

This register reflects the status of the MSCAN receive error counter.

Figure 12-17. MSCAN Receive Error Counter (CANRXERR)

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1)

Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

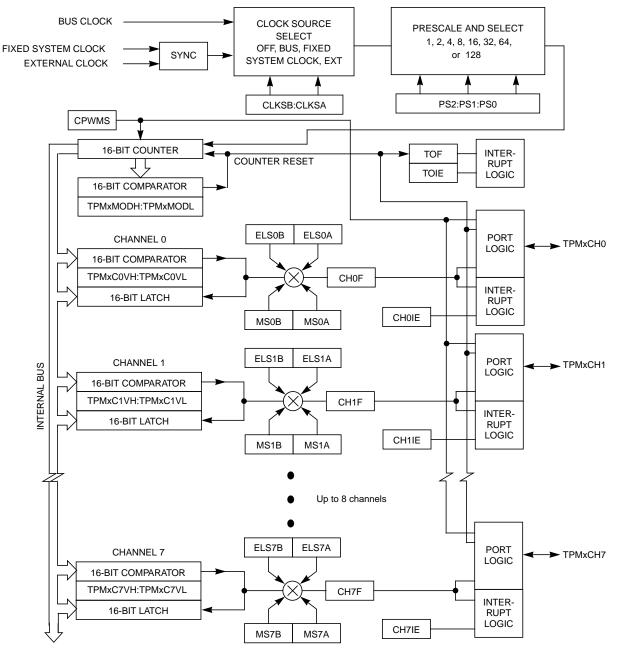

Chapter 16 Timer/PWM Module (S08TPMV3)

Figure 16-2. TPM Block Diagram

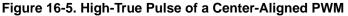

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter; the timer counter is counting up and the channel value register matches the timer counter; the timer counter is counter is counter; the timer counter is counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Figure 16-6. Low-True Pulse of a Center-Aligned PWM

Chapter 16 Timer/PWM Module (S08TPMV3)

## 16.3 Register Definition

This section consists of register descriptions in address order.

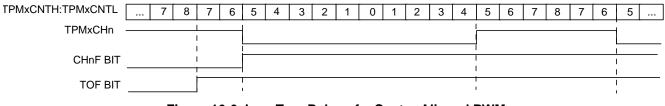

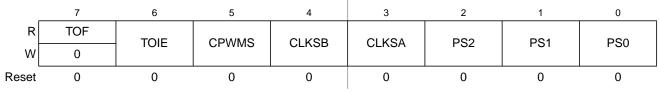

## 16.3.1 TPM Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits used to configure the interrupt enable, TPM configuration, clock source, and prescale factor. These controls relate to all channels within this timer module.

Figure 16-7. TPM Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TOF         | <ul> <li>Timer overflow flag. This read/write flag is set when the TPM counter resets to 0x0000 after reaching the movalue programmed in the TPM counter modulo registers. Clear TOF by reading the TPM status and control register when TOF is set and then writing a logic 0 to TOF. If another TPM overflow occurs before the clear sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. This is done so a TOF interrupt request cannot be lost during the clearing sequence for previous TOF. Reset clears TOF. Writing a logic 1 to TOF has no effect.</li> <li>0 TPM counter has not reached modulo value or overflow</li> <li>1 TPM counter has overflowed</li> </ul> |  |  |  |  |  |

| 6<br>TOIE        | Timer overflow interrupt enable. This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals one. Reset clears TOIE.<br>0 TOF interrupts inhibited (use for software polling)<br>1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 5<br>CPWMS       | <ul> <li>Center-aligned PWM select. When present, this read/write bit selects CPWM operating mode. By default, the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up/down counting mode for CPWM functions. Reset clears CPWMS.</li> <li>0 All channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register.</li> <li>1 All channels operate in center-aligned PWM mode.</li> </ul>                                                                                                                                                        |  |  |  |  |  |

| 4–3<br>CLKS[B:A] | Clock source selects. As shown in Table 16-3, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The fixed system clock source is only meaningful in systems with a PLL-based or FLL-based system clock. When there is no PLL or FLL, the fixed-system clock source is the same as the bus rate clock. The external source is synchronized to the bus clock by TPM module, and the fixed system clock source (when a PLL or FLL is present) is synchronized to the bus clock by an on-chip synchronization circuit. When a PLL or FLL is present but not enabled, the fixed-system clock source is the same as the bus-rate clock.                                                 |  |  |  |  |  |

| 2–0<br>PS[2:0]   | Prescale factor select. This 3-bit field selects one of 8 division factors for the TPM clock input as shown in Table 16-4. This prescaler is located after any clock source synchronization or clock source selection so it affects the clock source selected to drive the TPM system. The new prescale factor will affect the clock source on the next system clock cycle after the new value is updated into the register bits.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

#### Table 16-2. TPMxSC Field Descriptions

All TPM interrupts are listed in Table 16-8 which shows the interrupt name, the name of any local enable that can block the interrupt request from leaving the TPM and getting recognized by the separate interrupt processing logic.

| Interrupt | Local<br>Enable | Source           | Description                                                                                                            |

|-----------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| TOF       | TOIE            | Counter overflow | Set each time the timer counter reaches its terminal count (at transition to next count value which is usually 0x0000) |

| CHnF      | CHnIE           | Channel event    | An input capture or output compare event took place on channel n                                                       |

| Table 16-8. | Interrupt | Summary |

|-------------|-----------|---------|

|-------------|-----------|---------|

The TPM module will provide a high-true interrupt signal. Vectors and priorities are determined at chip integration time in the interrupt module so refer to the user's guide for the interrupt module or to the chip's complete documentation for details.

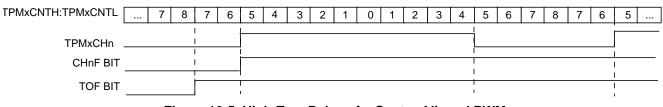

### 16.6.2 Description of Interrupt Operation

For each interrupt source in the TPM, a flag bit is set upon recognition of the interrupt condition such as timer overflow, channel-input capture, or output-compare events. This flag may be read (polled) by software to determine that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will generate whenever the associated interrupt flag equals one. The user's software must perform a sequence of steps to clear the interrupt flag before returning from the interrupt-service routine.

TPM interrupt flags are cleared by a two-step process including a read of the flag bit while it is set (1) followed by a write of zero (0) to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

### 16.6.2.1 Timer Overflow Interrupt (TOF) Description

The meaning and details of operation for TOF interrupts varies slightly depending upon the mode of operation of the TPM system (general purpose timing functions versus center-aligned PWM operation). The flag is cleared by the two step sequence described above.

#### 16.6.2.1.1 Normal Case

Normally TOF is set when the timer counter changes from 0xFFFF to 0x0000. When the TPM is not configured for center-aligned PWM (CPWMS=0), TOF gets set when the timer counter changes from the terminal count (the value in the modulo register) to 0x0000. This case corresponds to the normal meaning of counter overflow.

A force-type breakpoint waits for the current instruction to finish and then acts upon the breakpoint request. The usual action in response to a breakpoint is to go to active background mode rather than continuing to the next instruction in the user application program.

The tag vs. force terminology is used in two contexts within the debug module. The first context refers to breakpoint requests from the debug module to the CPU. The second refers to match signals from the comparators to the debugger control logic. When a tag-type break request is sent to the CPU, a signal is entered into the instruction queue along with the opcode so that if/when this opcode ever executes, the CPU will effectively replace the tagged opcode with a BGND opcode so the CPU goes to active background mode rather than executing the tagged instruction. When the TRGSEL control bit in the DBGT register is set to select tag-type operation, the output from comparator A or B is qualified by a block of logic in the debug module that tracks opcodes and only produces a trigger to the debugger if the opcode at the compare address is actually executed. There is separate opcode tracking logic for each comparator so more than one compare event can be tracked through the instruction queue at a time.

### 17.3.5 Trigger Modes

The trigger mode controls the overall behavior of a debug run. The 4-bit TRG field in the DBGT register selects one of nine trigger modes. When TRGSEL = 1 in the DBGT register, the output of the comparator must propagate through an opcode tracking circuit before triggering FIFO actions. The BEGIN bit in DBGT chooses whether the FIFO begins storing data when the qualified trigger is detected (begin trace), or the FIFO stores data in a circular fashion from the time it is armed until the qualified trigger is detected (end trigger).

A debug run is started by writing a 1 to the ARM bit in the DBGC register, which sets the ARMF flag and clears the AF and BF flags and the CNT bits in DBGS. A begin-trace debug run ends when the FIFO gets full. An end-trace run ends when the selected trigger event occurs. Any debug run can be stopped manually by writing a 0 to ARM or DBGEN in DBGC.

In all trigger modes except event-only modes, the FIFO stores change-of-flow addresses. In event-only trigger modes, the FIFO stores data in the low-order eight bits of the FIFO.

The BEGIN control bit is ignored in event-only trigger modes and all such debug runs are begin type traces. When TRGSEL = 1 to select opcode fetch triggers, it is not necessary to use R/W in comparisons because opcode tags would only apply to opcode fetches that are always read cycles. It would also be unusual to specify TRGSEL = 1 while using a full mode trigger because the opcode value is normally known at a particular address.

The following trigger mode descriptions only state the primary comparator conditions that lead to a trigger. Either comparator can usually be further qualified with R/W by setting RWAEN (RWBEN) and the corresponding RWA (RWB) value to be matched against R/W. The signal from the comparator with optional R/W qualification is used to request a CPU breakpoint if BRKEN = 1 and TAG determines whether the CPU request will be a tag request or a force request.

## A.13 Flash

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal V<sub>DD</sub> supply. For more detailed information about program/erase operations, see Chapter 4, "Memory."

| Num | С | Rating                                                                                                        | Symbol                  | Min Typical |         | Мах | Unit              |

|-----|---|---------------------------------------------------------------------------------------------------------------|-------------------------|-------------|---------|-----|-------------------|

| 1   | — | Supply voltage for program/erase                                                                              | V <sub>prog/erase</sub> | 2.7         | 2.7 5.5 |     | V                 |

| 2   | _ | Supply voltage for read operation<br>0 < f <sub>Bus</sub> < 8 MHz<br>0 < f <sub>Bus</sub> < 20 MHz            | V <sub>Read</sub>       | 2.7 5.5     |         | V   |                   |

| 3   | _ | Internal FCLK frequency <sup>1</sup>                                                                          | f <sub>FCLK</sub>       | 150         |         | 200 | kHz               |

| 4   | _ | Internal FCLK period (1/FCLK)                                                                                 | t <sub>Fcyc</sub>       | 5           | 5 6.67  |     | μs                |

| 5   | _ | Byte program time (random location) <sup>(2)</sup>                                                            | t <sub>prog</sub>       | 9           |         |     | t <sub>Fcyc</sub> |

| 6   | _ | Byte program time (burst mode) <sup>(2)</sup>                                                                 | t <sub>Burst</sub>      | 4           |         |     | t <sub>Fcyc</sub> |

| 7   | _ | Page erase time <sup>2</sup>                                                                                  | t <sub>Page</sub>       | 4000        |         |     | t <sub>Fcyc</sub> |

| 8   | — | Mass erase time <sup>(2)</sup>                                                                                | t <sub>Mass</sub>       | 20,000      |         |     | t <sub>Fcyc</sub> |

| 9   | с | Flash Program/erase endurance <sup>3</sup><br>T <sub>L</sub> to T <sub>H</sub> = -40°C to + 125°C<br>T = 25°C | N <sub>FLPE</sub>       | 10,000      | 100,000 |     | cycles            |

| 10  | С | Data retention <sup>4</sup>                                                                                   | t <sub>D_ret</sub>      | 15          | 100     | —   | years             |

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> **Typical endurance** for Flash is based on the intrinsic bit cell performance. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619, *Typical Endurance for Nonvolatile Memory.*

<sup>4</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618, *Typical Data Retention for Nonvolatile Memory.*

## A.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

Appendix B Timer Pulse-Width Modulator (TPMV2)

Figure B-1. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter. (The values 0x0000 or 0xFFFF effectively make the counter free running.) Software can read the counter value at any time without affecting the counting sequence. Any write to either byte of the TPMxCNT counter resets the counter regardless of the data value written.