Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 10x12b                                                  |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dv32amlc |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 1 Device Overview**

### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pull-up devices or change the direction of unused or non-bonded pins to outputs so they do not float.

# 3.6 Stop Modes

One of two stop modes is entered upon execution of a STOP instruction when the STOPE bit in SOPT1 register is set. In both stop modes, all internal clocks are halted. The MCG module can be configured to leave the reference clocks running. See Chapter 8, "Multi-Purpose Clock Generator (S08MCGV1)," for more information.

Table 3-1 shows all of the control bits that affect stop mode selection and the mode selected under various conditions. The selected mode is entered following the execution of a STOP instruction.

| STOPE | ENBDM <sup>1</sup> | <sup>1</sup> LVDE LVDSE |  | PPDC | Stop Mode                                                              |

|-------|--------------------|-------------------------|--|------|------------------------------------------------------------------------|

| 0     | х                  | x                       |  | х    | Stop modes disabled; illegal opcode reset if STOP instruction executed |

| 1     | 1                  | х                       |  | х    | Stop3 with BDM enabled <sup>2</sup>                                    |

| 1     | 0                  | Both bits must be 1     |  | х    | Stop3 with voltage regulator active                                    |

| 1     | 0                  | Either bit a 0          |  | 0    | Stop3                                                                  |

| 1     | 0                  | Either bit a 0          |  | 1    | Stop2                                                                  |

Table 3-1. Stop Mode Selection

<sup>1</sup> ENBDM is located in the BDCSCR, which is only accessible through BDC commands, see Section 17.4.1.1, "BDC Status and Control Register (BDCSCR)".

$^2$  When in Stop3 mode with BDM enabled, The S<sub>IDD</sub> will be near R<sub>IDD</sub> levels because internal clocks are enabled.

## 3.6.1 Stop3 Mode

Stop3 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. The states of all of the internal registers and logic, RAM contents, and I/O pin states are maintained.

Exit from stop3 is done by asserting RESET or an asynchronous interrupt pin. The asynchronous interrupt pins are IRQ, PIA0–PIA7, PIB0–PIB7, and PID0–PID7. Exit from stop3 can also be done by the low-voltage detect (LVD) reset, low-voltage warning (LVW) interrupt, ADC conversion complete interrupt, real-time clock (RTC) interrupt, MSCAN wake-up interrupt, or SCI receiver interrupt.

If stop3 is exited by means of the RESET pin, the MCU will be reset and operation will resume after fetching the reset vector. Exit by means of an interrupt will result in the MCU fetching the appropriate interrupt vector.

## 3.6.1.1 LVD Enabled in Stop3 Mode

The LVD system is capable of generating either an interrupt or a reset when the supply voltage drops below the LVD voltage. If the LVD is enabled in stop (LVDE and LVDSE bits in SPMSC1 both set) at the time the CPU executes a STOP instruction, then the voltage regulator remains active during stop mode.

For the ADC to operate the LVD must be left enabled when entering stop3.

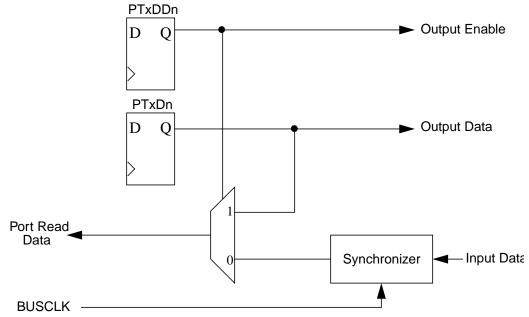

#### Chapter 6 Parallel Input/Output Control

In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

It is a good programming practice to write to the port data register before changing the direction of a port pin to become an output. This ensures that the pin will not be driven momentarily with an old data value that happened to be in the port data register.

Figure 6-1. Parallel I/O Block Diagram

## 6.2 Pull-up, Slew Rate, and Drive Strength

Associated with the parallel I/O ports is a set of registers located in the high page register space that operate independently of the parallel I/O registers. These registers are used to control pull-ups, slew rate, and drive strength for the pins.

An internal pull-up device can be enabled for each port pin by setting the corresponding bit in the pull-up enable register (PTxPEn). The pull-up device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function regardless of the state of the corresponding pull-up enable register bit. The pull-up device is also disabled if the pin is controlled by an analog function.

Slew rate control can be enabled for each port pin by setting the corresponding bit in the slew rate control register (PTxSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins that are configured as inputs.

#### NOTE

Slew rate reset default values may differ between engineering samples and final production parts. Always initialize slew rate control to the desired value to ensure correct operation.

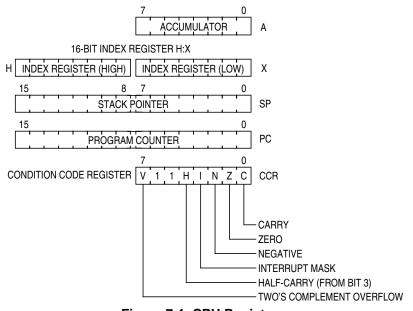

Chapter 7 Central Processor Unit (S08CPUV3)

# 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

## 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the addressing modes to specify the addressing modes to specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

## 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

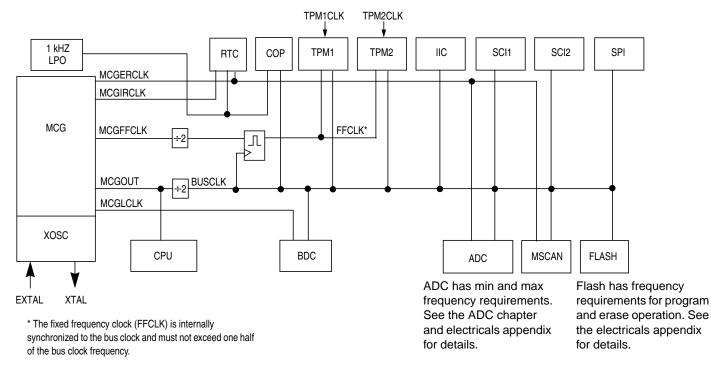

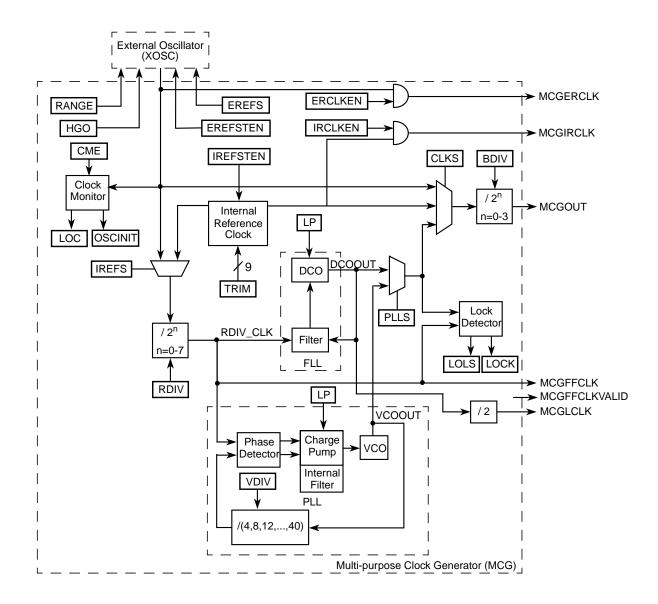

Figure 8-2. Multi-Purpose Clock Generator (MCG) Block Diagram

```

Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

```

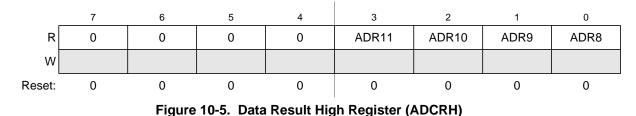

If the MODE bits are changed, any data in ADCRH becomes invalid.

# 10.3.4 Data Result Low Register (ADCRL)

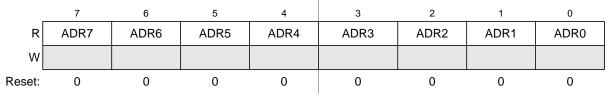

ADCRL contains the lower eight bits of the result of a 12-bit or 10-bit conversion, and all eight bits of an 8-bit conversion. This register is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. When a compare event does occur, the value is the addition of the conversion result and the two's complement of the compare value. In 12-bit and 10-bit mode, reading ADCRH prevents the ADC from transferring subsequent conversion results into the result registers until ADCRL is read. If ADCRL is not read until the after next conversion is completed, the intermediate conversion results are lost. In 8-bit mode, there is no interlocking with ADCRH. If the MODE bits are changed, any data in ADCRL becomes invalid.

Figure 10-6. Data Result Low Register (ADCRL)

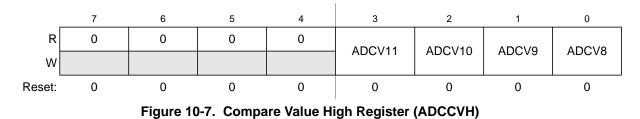

## 10.3.5 Compare Value High Register (ADCCVH)

In 12-bit mode, the ADCCVH register holds the upper four bits of the 12-bit compare value. When the compare function is enabled, these bits are compared to the upper four bits of the result following a conversion in 12-bit mode.

| Field       | Description                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC15 | ADC Pin Control 15. ADPC15 controls the pin associated with channel AD15.<br>0 AD15 pin I/O control enabled<br>1 AD15 pin I/O control disabled |

| 6<br>ADPC14 | ADC Pin Control 14. ADPC14 controls the pin associated with channel AD14.<br>0 AD14 pin I/O control enabled<br>1 AD14 pin I/O control disabled |

| 5<br>ADPC13 | ADC Pin Control 13. ADPC13 controls the pin associated with channel AD13.<br>0 AD13 pin I/O control enabled<br>1 AD13 pin I/O control disabled |

| 4<br>ADPC12 | ADC Pin Control 12. ADPC12 controls the pin associated with channel AD12.<br>0 AD12 pin I/O control enabled<br>1 AD12 pin I/O control disabled |

| 3<br>ADPC11 | ADC Pin Control 11. ADPC11 controls the pin associated with channel AD11.<br>0 AD11 pin I/O control enabled<br>1 AD11 pin I/O control disabled |

| 2<br>ADPC10 | ADC Pin Control 10. ADPC10 controls the pin associated with channel AD10.<br>0 AD10 pin I/O control enabled<br>1 AD10 pin I/O control disabled |

| 1<br>ADPC9  | ADC Pin Control 9. ADPC9 controls the pin associated with channel AD9.<br>0 AD9 pin I/O control enabled<br>1 AD9 pin I/O control disabled      |

| 0<br>ADPC8  | ADC Pin Control 8. ADPC8 controls the pin associated with channel AD8.<br>0 AD8 pin I/O control enabled<br>1 AD8 pin I/O control disabled      |

#### Table 10-11. APCTL2 Register Field Descriptions

# 10.3.10 Pin Control 3 Register (APCTL3)

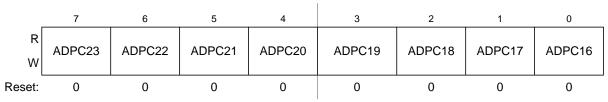

APCTL3 controls channels 16–23 of the ADC module.

Figure 10-12. Pin Control 3 Register (APCTL3)

Chapter 11 Inter-Integrated Circuit (S08IICV2)

# 11.7 Initialization/Application Information

| 1  | Write: IIC                                                                                                 | Module Initialization (Slave)                                                                  |  |  |  |

|----|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|

| 1. |                                                                                                            | nable or disable general call                                                                  |  |  |  |

|    |                                                                                                            | elect 10-bit or 7-bit addressing mode                                                          |  |  |  |

| 2. | Write: IIC                                                                                                 | -                                                                                              |  |  |  |

|    |                                                                                                            | et the slave address                                                                           |  |  |  |

| 3. | Write: IIC                                                                                                 |                                                                                                |  |  |  |

| -  | — to e                                                                                                     | nable IIC and interrupts                                                                       |  |  |  |

| 4. |                                                                                                            | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                      |  |  |  |

| 5. |                                                                                                            | RAM variables used to achieve the routine shown in Figure 11-12                                |  |  |  |

|    |                                                                                                            |                                                                                                |  |  |  |

|    |                                                                                                            |                                                                                                |  |  |  |

| 4  | Mrita IIC                                                                                                  | Module Initialization (Master)                                                                 |  |  |  |

| 1. | Write: IIC                                                                                                 |                                                                                                |  |  |  |

| 2. | Write: IIC                                                                                                 | et the IIC baud rate (example provided in this chapter)                                        |  |  |  |

| ۷. |                                                                                                            | nable IIC and interrupts                                                                       |  |  |  |

| 3. |                                                                                                            | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                      |  |  |  |

| 4. |                                                                                                            | RAM variables used to achieve the routine shown in Figure 11-12                                |  |  |  |

| 5. | Write: IIC                                                                                                 |                                                                                                |  |  |  |

| •  | — to e                                                                                                     | nable TX                                                                                       |  |  |  |

| 6. | Write: IIC                                                                                                 | CC1                                                                                            |  |  |  |

|    | — to e                                                                                                     | nable MST (master mode)                                                                        |  |  |  |

| 7. | Write: IIC                                                                                                 |                                                                                                |  |  |  |

|    | — with                                                                                                     | the address of the target slave. (The lsb of this byte determines whether the communication is |  |  |  |

|    | mas                                                                                                        | ter receive or transmit.)                                                                      |  |  |  |

|    |                                                                                                            | Module Use                                                                                     |  |  |  |

|    | The routine shown in Figure 11-12 can handle both master and slave IIC operations. For slave operation, an |                                                                                                |  |  |  |

|    |                                                                                                            | IIC message that contains the proper address begins IIC communication. For master operation,   |  |  |  |

|    | commun                                                                                                     | ication must be initiated by writing to the IICD register.                                     |  |  |  |

|    |                                                                                                            |                                                                                                |  |  |  |

|    |                                                                                                            | Devictor Medel                                                                                 |  |  |  |

|    |                                                                                                            | Register Model                                                                                 |  |  |  |

|    | IICA                                                                                                       | AD[7:1] 0                                                                                      |  |  |  |

|    | 10/1                                                                                                       |                                                                                                |  |  |  |

|    |                                                                                                            | When addressed as a slave (in slave mode), the module responds to this address                 |  |  |  |

|    | IICF MULT ICR                                                                                              |                                                                                                |  |  |  |

|    | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                                                            |                                                                                                |  |  |  |

|    | IICC1                                                                                                      | IICEN IICIE MST TX TXAK RSTA 0 0                                                               |  |  |  |

|    |                                                                                                            | Module configuration                                                                           |  |  |  |

|    | IICS                                                                                                       |                                                                                                |  |  |  |

|    | 100                                                                                                        | Module status flags                                                                            |  |  |  |

|    | IICD                                                                                                       |                                                                                                |  |  |  |

|    | IICD                                                                                                       |                                                                                                |  |  |  |

|    |                                                                                                            | Data register; Write to transmit IIC data read to read IIC data                                |  |  |  |

|    | IICC2                                                                                                      |                                                                                                |  |  |  |

|    |                                                                                                            | Address configuration                                                                          |  |  |  |

Figure 11-11. IIC Module Quick Start

MC9S08DV60 Series Data Sheet, Rev 3

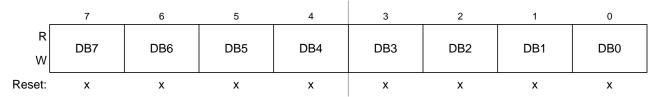

Figure 12-33. Data Segment Registers (DSR0–DSR7) — Extended Identifier Mapping

#### Table 12-31. DSR0–DSR7 Register Field Descriptions

| Field          | Description   |

|----------------|---------------|

| 7:0<br>DB[7:0] | Data bits 7:0 |

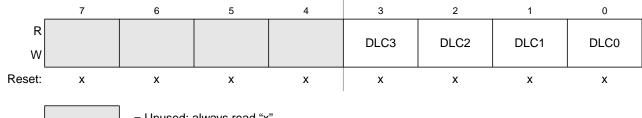

#### 12.4.4 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

= Unused; always read "x"

| Table 12-32. | <b>DLR Register Field</b> | Descriptions |

|--------------|---------------------------|--------------|

|--------------|---------------------------|--------------|

| Field | Description                                                                                                                                                                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0   | Data Length Code Bits — The data length code contains the number of bytes (data byte count) of the respective                                                                                                                                                                |

|       | message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 12-33 shows the effect of setting the DLC bits. |

|            | MSCAN Mode                                       |                                                  |                                     |                                     |  |

|------------|--------------------------------------------------|--------------------------------------------------|-------------------------------------|-------------------------------------|--|

| CPU Mode   |                                                  | Reduced Power Consumption                        |                                     |                                     |  |

|            | Normal                                           | Sleep                                            | Power Down                          | Disabled<br>(CANE=0)                |  |

| Run        | CSWAI = X <sup>1</sup><br>SLPRQ = 0<br>SLPAK = 0 | CSWAI = X<br>SLPRQ = 1<br>SLPAK = 1              |                                     | CSWAI = X<br>SLPRQ = X<br>SLPAK = X |  |

| Wait       | CSWAI = 0<br>SLPRQ = 0<br>SLPAK = 0              | CSWAI = 0<br>SLPRQ = 1<br>SLPAK = 1              | CSWAI = 1<br>SLPRQ = X<br>SLPAK = X | CSWAI = X<br>SLPRQ = X<br>SLPAK = X |  |

| Stop3      |                                                  | CSWAI = X <sup>2</sup><br>SLPRQ = 1<br>SLPAK = 1 | CSWAI = X<br>SLPRQ = 0<br>SLPAK = 0 | CSWAI = X<br>SLPRQ = X<br>SLPAK = X |  |

| Stop1 or 2 |                                                  |                                                  | CSWAI = X<br>SLPRQ = X<br>SLPAK = X | CSWAI = X<br>SLPRQ = X<br>SLPAK = X |  |

#### Table 12-36. CPU vs. MSCAN Operating Modes

<sup>1</sup> 'X' means don't care.

<sup>2</sup> For a safe wake up from Sleep mode, SLPRQ and SLPAK must be set to 1 before going into Stop3 mode.

### 12.5.5.1 Operation in Run Mode

As shown in Table 12-36, only MSCAN sleep mode is available as low power option when the CPU is in run mode.

### 12.5.5.2 Operation in Wait Mode

The WAIT instruction puts the MCU in a low power consumption stand-by mode. If the CSWAI bit is set, additional power can be saved in power down mode because the CPU clocks are stopped. After leaving this power down mode, the MSCAN restarts its internal controllers and enters normal mode again.

While the CPU is in wait mode, the MSCAN can be operated in normal mode and generate interrupts (registers can be accessed via background debug mode). The MSCAN can also operate in any of the low-power modes depending on the values of the SLPRQ/SLPAK and CSWAI bits as seen in Table 12-36.

### 12.5.5.3 Operation in Stop Mode

The STOP instruction puts the MCU in a low power consumption stand-by mode. In stop1 or stop2 modes, the MSCAN is set in power down mode regardless of the value of the SLPRQ/SLPAK. In stop3 mode, power down or sleep modes are determined by the SLPRQ/SLPAK values set prior to entering stop3. CSWAI bit has no function in any of the stop modes.Table 12-36.

| Table 14-5. SCIxC2 Field Descri | ptions (continued) |

|---------------------------------|--------------------|

|---------------------------------|--------------------|

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>TE  | Transmitter Enable         0       Transmitter off.         1       Transmitter on.         TE must be 1 in order to use the SCI transmitter. When TE = 1, the SCI forces the TxD pin to act as an output for the SCI system.         When the SCI is configured for single-wire operation (LOOPS = RSRC = 1), TXDIR controls the direction of traffic on the single SCI communication line (TxD pin).         TE also can be used to queue an idle character by writing TE = 0 then TE = 1 while a transmission is in progress.         Refer to Section 14.3.2.1, "Send Break and Queued Idle" for more details.         When TE is written to 0, the transmitter keeps control of the port TxD pin until any data, queued idle, or queued break character finishes transmitting before allowing the pin to revert to a general-purpose I/O pin. |

| 2<br>RE  | <ul> <li>Receiver Enable — When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin.</li> <li>If LOOPS = 1 the RxD pin reverts to being a general-purpose I/O pin even if RE = 1.</li> <li>0 Receiver off.</li> <li>1 Receiver on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1<br>RWU | Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more details.         0       Normal SCI receiver operation.         1       SCI receiver in standby waiting for wakeup condition.                                                                                                                                                                    |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 (13 or 14 if BRK13 = 1) bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 14.3.2.1, "Send Break and Queued Idle" for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                                                                                                                                                      |

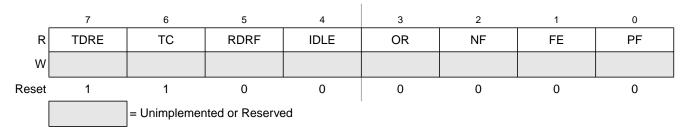

# 14.2.4 SCI Status Register 1 (SCIxS1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

Figure 14-8. SCI Status Register 1 (SCIxS1)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6<br>TC   | Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.         0       Transmitter active (sending data, a preamble, or a break).         1       Transmitter idle (transmission activity complete).         TC is cleared automatically by reading SCIxS1 with TC = 1 and then doing one of the following three things:         •       Write to the SCI data register (SCIxD) to transmit new data         •       Queue a preamble by changing TE from 0 to 1         •       Queue a break character by writing 1 to SBK in SCIxC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5<br>RDRF | Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). To clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD).         0       Receive data register empty.         1       Receive data register full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the previous character do not count toward the full character time of logic high needed for the receiver to detect an idle line.         To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE will get set only once even if the receive line remains idle for an extended period.         0       No idle line detected.         1       Idle line was detected. |

| 3<br>OR   | Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).         0       No overrun.         1       Receive overrun (new SCI data lost).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 14-6. SCIxS1 Field Descriptions

## 15.1.2 Features

Features of the RTC module include:

- 8-bit up-counter

- 8-bit modulo match limit

- Software controllable periodic interrupt on match

- Three software selectable clock sources for input to prescaler with selectable binary-based and decimal-based divider values

- 1-kHz internal low-power oscillator (LPO)

- External clock (ERCLK)

- 32-kHz internal clock (IRCLK)

### 15.1.3 Modes of Operation

This section defines the operation in stop, wait and background debug modes.

### 15.1.3.1 Wait Mode

The RTC continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the RTC can bring the MCU out of wait mode if the real-time interrupt is enabled. For lowest possible current consumption, the RTC should be stopped by software if not needed as an interrupt source during wait mode.

### 15.1.3.2 Stop Modes

The RTC continues to run in stop2 or stop3 mode if the RTC is enabled before executing the STOP instruction. Therefore, the RTC can bring the MCU out of stop modes with no external components, if the real-time interrupt is enabled.

The LPO clock can be used in stop2 and stop3 modes. ERCLK and IRCLK clocks are only available in stop3 mode.

Power consumption is lower when all clock sources are disabled, but in that case, the real-time interrupt cannot wake up the MCU from stop modes.

### 15.1.3.3 Active Background Mode

The RTC suspends all counting during active background mode until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as the RTCMOD register is not written and the RTCPS and RTCLKS bits are not altered.

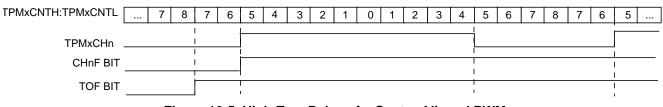

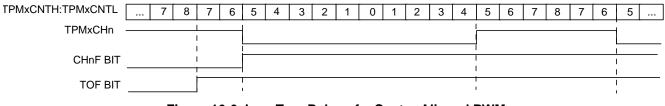

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter is counter; the timer counter is counter is counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Figure 16-6. Low-True Pulse of a Center-Aligned PWM

• Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

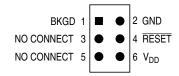

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 17-1. BDM Tool Connector

## 17.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 17.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 17.2.2, "Communication Details," for more detail.

# Appendix A Electrical Characteristics

# A.1 Introduction

This section contains the most accurate electrical and timing information for the MC9S08DV60 Series of microcontrollers available at the time of publication.

# A.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| с | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### **Table A-1. Parameter Classifications**

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# A.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-2 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

## **B.2.1** Timer Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

|       | 7                           | 6    | 5        | 4     | 3     | 2           | 1   | 0   |  |

|-------|-----------------------------|------|----------|-------|-------|-------------|-----|-----|--|

| R     | TOF                         |      | CPWMS    |       | CLKSA | <b>DC</b> 2 | DC1 | DCO |  |

| w     |                             | TOIE | CP VIVIS | CLKSB | ULKSA | PS2         | PS1 | PS0 |  |

| Reset | 0                           | 0    | 0        | 0     | 0     | 0           | 0   | 0   |  |

|       | = Unimplemented or Reserved |      |          |       |       |             |     |     |  |

#### Figure B-2. Timer Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, aninterrupt is generated when TOF equals 1. Reset clears TOIE.0 TOF interrupts inhibited (use software polling)1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>O All TPMx channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>1 All TPMx channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                              |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table B-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table B-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

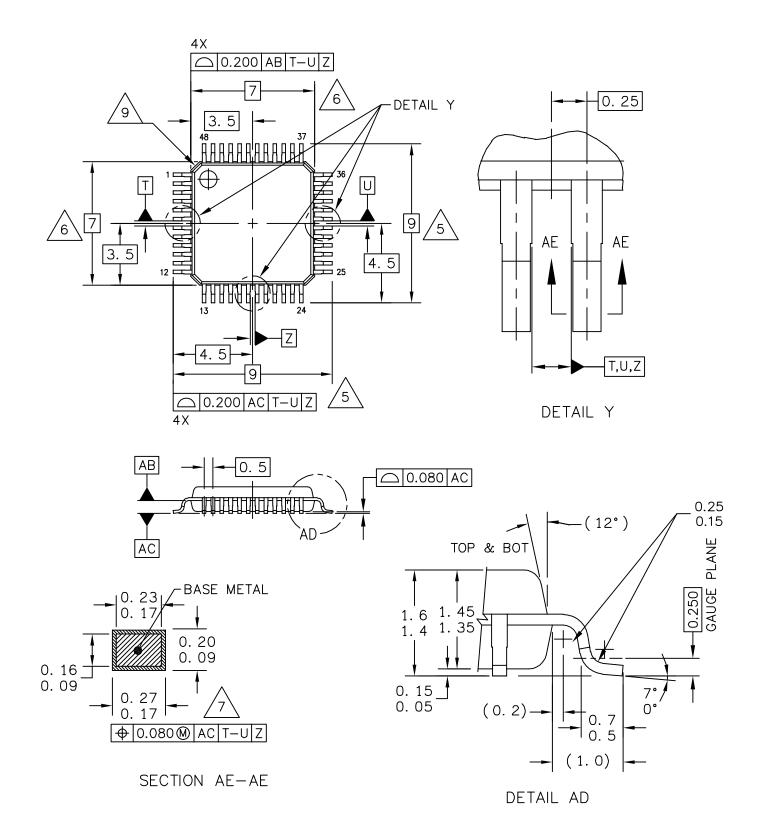

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE                 | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|-----------|--------------------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO: 98ASH00962A |                  | REV: G      |

| LQFP, 48 LEAD, 0.                                       |           | CASE NUMBER: 932-03      |                  | 14 APR 2005 |

| (7.0 X 7.0 X                                            | 1.4)      | STANDARD: JE             | DEC MS-026-BBC   |             |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:** Freescale Semiconductor

Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 1-303-675-2140 Fax: 1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

MC9S08DV60 Rev 3, 6/2008 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007-2008. All rights reserved.