Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dv32mlc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

29

$\rm V_{REFH}$  and  $\rm V_{REFL}$  are internally connected to  $\rm V_{DDA}$  and  $\rm V_{SSA},$  respectively.

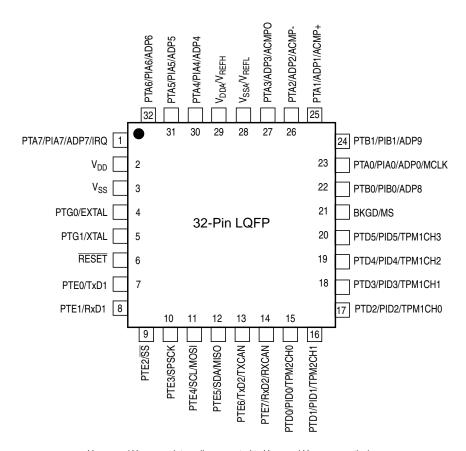

Figure 2-3. 32-Pin LQFP

Table 4-1. Reset and Interrupt Vectors

| Address<br>(High/Low)       | Vector                         | Vector Name |

|-----------------------------|--------------------------------|-------------|

| 0xFFCE:0xFFCF               | xFFCE:0xFFCF IIC               |             |

| 0xFFD0:0xFFD1               | ADC Conversion                 | Vadc        |

| 0xFFD2:0xFFD3               | Port A, Port B, Port D         | Vport       |

| 0xFFD4:0xFFD5               | SCI2 Transmit                  | Vsci2tx     |

| 0xFFD6:0xFFD7               | SCI2 Receive                   | Vsci2rx     |

| 0xFFD8:0xFFD9               | SCI2 Error                     | Vsci2err    |

| 0xFFDA:0xFFDB               | SCI1 Transmit                  | Vsci1tx     |

| 0xFFDC:0xFFDD               | SCI1 Receive                   | Vsci1rx     |

| 0xFFDE:0xFFDF               | SCI1 Error                     | Vsci1err    |

| 0xFFE0:0xFFE1               | SPI                            | Vspi        |

| 0xFFE2:0xFFE3 TPM2 Overflow |                                | Vtpm2ovf    |

| 0xFFE4:0xFFE5               | TPM2 Channel 1                 | Vtpm2ch1    |

| 0xFFE6:0xFFE7               | TPM2 Channel 0                 | Vtpm2ch0    |

| 0xFFE8:0xFFE9               | TPM1 Overflow                  | Vtpm1ovf    |

| 0xFFEA:0xFFEB               | A:0xFFEB TPM1 Channel 5        |             |

| 0xFFEC:0xFFED               | TPM1 Channel 4                 | Vtpm1ch4    |

| 0xFFEE:0xFFEF               | TPM1 Channel 3                 | Vtpm1ch3    |

| 0xFFF0:0xFFF1               | TPM1 Channel 2                 | Vtpm1ch2    |

| 0xFFF2:0xFFF3               | TPM1 Channel 1                 | Vtpm1ch1    |

| 0xFFF4:0xFFF5               | TPM1 Channel 0                 | Vtpm1ch0    |

| 0xFFF6:0xFFF7               | 0xFFF6:0xFFF7 MCG Loss of lock |             |

| 0xFFF8:0xFFF9               | 8:0xFFF9 Low-Voltage Detect    |             |

| 0xFFFA:0xFFFB               | IRQ                            | Virq        |

| 0xFFFC:0xFFFD               | SWI                            | Vswi        |

| 0xFFFE:0xFFFF               | Reset                          | Vreset      |

|                             |                                |             |

## **Chapter 4 Memory**

Reset

This register is loaded from nonvolatile location NVPROT during reset.

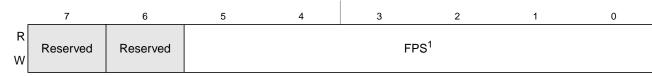

Figure 4-8. Flash Protection Register (FPROT)

**Table 4-12. FPROT Register Field Descriptions**

| Field      | Description                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>FPS | Flash Protect Select Bits — This 6-bit field determines the protected Flash locations that cannot be erased or programmed. See Table 4-13. |

**Table 4-13. Flash Block Protection**

| FPS  | Address Area Protected | Memory Size Protected (bytes) | Number of Sectors Protected |  |  |

|------|------------------------|-------------------------------|-----------------------------|--|--|

| 0x3F | N/A                    | 0                             | 0                           |  |  |

| 0x3E | 0xFA00-0xFFFF 1.5K     |                               | 2                           |  |  |

| 0x3D | 0xF400-0xFFFF          | 3К                            | 4                           |  |  |

| 0x3C | 0xEE00-0xFFFF          | 4.5K                          | 6                           |  |  |

| 0x3B | 0xE800-0xFFFF          | 6K                            | 8                           |  |  |

|      |                        |                               |                             |  |  |

| 0x37 | 0xD000-0xFFFF          | 12K                           | 16                          |  |  |

| 0x36 | 0xCA00-0xFFFF          | 13.5K                         | 18                          |  |  |

| 0x35 | 0xC400-0xFFFF          | 15K                           | 20                          |  |  |

| 0x34 | 0xBE00-0xFFFF          | 16.5K                         | 22                          |  |  |

|      |                        |                               |                             |  |  |

| 0x2C | 0x8E00-0xFFFF          | 28.5K                         | 38                          |  |  |

| 0x2B | 0x8800-0xFFFF          | 30K                           | 40                          |  |  |

| 0x2A | 0x8200-0xFFFF          | 31.5K                         | 42                          |  |  |

| 0x29 | 0x7C00-0xFFFF          | 33K                           | 44                          |  |  |

|      |                        |                               |                             |  |  |

| 0x22 | 0x5200-0xFFFF          | 43.5K                         | 58                          |  |  |

| 0x21 | 0x4C00-0xFFFF          | 45K                           | 60                          |  |  |

| 0x20 | 0x4600-0xFFFF          | 46.5K                         | 62                          |  |  |

| 0x1F | 0x4000-0xFFFF          | 48K                           | 64                          |  |  |

|      |                        |                               |                             |  |  |

MC9S08DV60 Series Data Sheet, Rev 3

#### 5.6 Low-Voltage Detect (LVD) System

The MC9S08DV60 Series includes a system to protect against low-voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2 (it will enter stop3 instead), and the current consumption in stop3 with the LVD enabled will be higher.

#### 5.6.1 **Power-On Reset Operation**

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level, V<sub>POR</sub>, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low-voltage detection low threshold, V<sub>I VDI</sub>. Both the POR bit and the LVD bit in SRS are set following a POR.

#### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low-voltage condition by setting LVDRE to 1. The low-voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low-voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

#### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low-voltage warning flag to indicate to the user that the supply voltage is approaching the low-voltage condition. When a low-voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

#### **MCLK Output** 5.7

The PTA0 pin is shared with the MCLK clock output. If the MCSEL bits are all zeroes, the MCLK clock is disabled. Setting any of the MCSEL bits causes the PTA0 pin to output a divided version of the internal MCU bus clock regardless of the state of the port data direction control bit for the pin. The divide ratio is determined by the MCSEL bits. The slew rate and drive strength for the pin are controlled by PTASE0 and PTADS0, respectively. The maximum clock output frequency is limited if slew rate control is enabled, see the electrical specifications for the maximum frequency under different conditions.

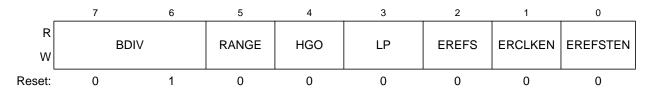

# 8.3.2 MCG Control Register 2 (MCGC2)

Figure 8-4. MCG Control Register 2 (MCGC2)

**Table 8-2. MCG Control Register 2 Field Descriptions**

| Field         | Description                                                                                                                                                                                                                                                                                                                                                         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>BDIV   | Bus Frequency Divider — Selects the amount to divide down the clock source selected by the CLKS bits in the MCGC1 register. This controls the bus frequency.  00 Encoding 0 — Divides selected clock by 1  01 Encoding 1 — Divides selected clock by 2 (reset default)  10 Encoding 2 — Divides selected clock by 4  11 Encoding 3 — Divides selected clock by 8    |

| 5<br>RANGE    | Frequency Range Select — Selects the frequency range for the external oscillator or external clock source.  1 High frequency range selected for the external oscillator of 1 MHz to 16 MHz (1 MHz to 40 MHz for external clock source)  0 Low frequency range selected for the external oscillator of 32 kHz to 100 kHz (32 kHz to 1 MHz for external clock source) |

| 4<br>HGO      | High Gain Oscillator Select — Controls the external oscillator mode of operation.  1 Configure external oscillator for high gain operation  0 Configure external oscillator for low power operation                                                                                                                                                                 |

| 3<br>LP       | Low Power Select — Controls whether the FLL (or PLL) is disabled in bypassed modes.  1 FLL (or PLL) is disabled in bypass modes (lower power).  0 FLL (or PLL) is not disabled in bypass modes.                                                                                                                                                                     |

| 2<br>EREFS    | External Reference Select — Selects the source for the external reference clock.  1 Oscillator requested  0 External Clock Source requested                                                                                                                                                                                                                         |

| 1<br>ERCLKEN  | External Reference Enable — Enables the external reference clock for use as MCGERCLK.  1 MCGERCLK active 0 MCGERCLK inactive                                                                                                                                                                                                                                        |

| 0<br>EREFSTEN | External Reference Stop Enable — Controls whether or not the external reference clock remains enabled when the MCG enters stop mode.  1 External reference clock stays enabled in stop if ERCLKEN is set or if MCG is in FEE, FBE, PEE, PBE, or BLPE mode before entering stop  0 External reference clock is disabled in stop                                      |

#### Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

- LP bit is written to 1

- BDM mode is not active

In bypassed low power external mode, the MCGOUT clock is derived from the external reference clock. The external reference clock which is enabled can be an external crystal/resonator or it can be another external clock source.

The PLL and the FLL are disabled at all times in BLPE mode and the MCGLCLK will not be available for BDC communications. If the BDM becomes active the mode will switch to one of the bypassed external modes as determined by the state of the PLLS bit.

## 8.4.1.9 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, the FLL and PLL are disabled and all MCG clock signals are static except in the following cases:

MCGIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN = 1

- IREFSTEN = 1

MCGERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN = 1

- EREFSTEN = 1

# 8.4.2 Mode Switching

When switching between engaged internal and engaged external modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the reference frequency stays in the range required by the state of the PLLS bit (31.25 kHz to 39.0625 kHz if the FLL is selected, or 1 MHz to 2 MHz if the PLL is selected). After a change in the IREFS value the FLL or PLL will begin locking again after the switch is completed. The completion of the switch is shown by the IREFST bit .

For the special case of entering stop mode immediately after switching to FBE mode, if the external clock and the internal clock are disabled in stop mode, (EREFSTEN = 0 and IREFSTEN = 0), it is necessary to allow 100us after the IREFST bit is cleared to allow the internal reference to shutdown. For most cases the delay due to instruction execution times will be sufficient.

The CLKS bits can also be changed at anytime, but in order for the MCGLCLK to be configured correctly the RDIV bits must be changed simultaneously so that the reference frequency stays in the range required by the state of the PLLS bit (31.25 kHz to 39.0625 kHz if the FLL is selected, or 1 MHz to 2MHz if the PLL is selected). The actual switch to the newly selected clock will be shown by the CLKST bits. If the newly selected clock is not available, the previous clock will remain selected.

For details see Figure 8-8.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

Chapter 9 Analog Comparator (S08ACMPV3)

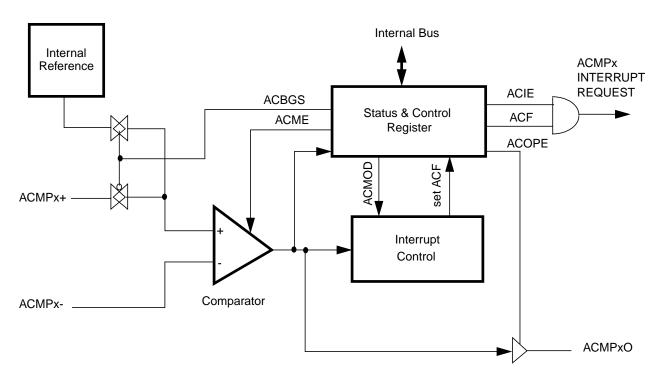

## 9.1.4 Block Diagram

The block diagram for the analog comparator module is shown Figure 9-2.

Figure 9-2. Analog Comparator (ACMP) Block Diagram

# 9.2 External Signal Description

The ACMP has two analog input pins, ACMPx+ and ACMPx- and one digital output pin ACMPxO. Each of these pins can accept an input voltage that varies across the full operating voltage range of the MCU. As shown in Figure 9-2, the ACMPx- pin is connected to the inverting input of the comparator, and the ACMPx+ pin is connected to the comparator non-inverting input if ACBGS is a 0. As shown in Figure 9-2, the ACMPxO pin can be enabled to drive an external pin.

The signal properties of ACMP are shown in Table 9-1.

Signal Function I/O

ACMPx- Inverting analog input to the ACMP. (Minus input)

ACMPx+ Non-inverting analog input to the ACMP. (Positive input)

ACMPxO Digital output of the ACMP. O

**Table 9-1. Signal Properties**

MC9S08DV60 Series Data Sheet, Rev 3

# 9.3 Memory Map/Register Definition

The ACMP includes one register:

• An 8-bit status and control register

Refer to the direct-page register summary in the memory section of this document for the absolute address assignments for the ACMP register. This section refers to register and control bits only by their names and relative address offsets.

Some MCUs may have more than one ACMP, so register names include placeholder characters (x) to identify which ACMP is being referenced.

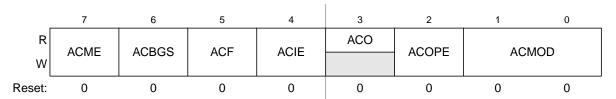

Name 7 4 6 5 3 2 1 0 ACO **ACMPxSC ACBGS ACOPE ACME** ACF ACIE **ACMOD** W

**Table 9-2. ACMP Register Summary**

# 9.3.1 ACMPx Status and Control Register (ACMPxSC)

ACMPxSC contains the status flag and control bits used to enable and configure the ACMP.

Figure 9-3. ACMPx Status and Control Register (ACMPxSC)

Table 9-3. ACMPxSC Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACME  | Analog Comparator Module Enable. Enables the ACMP module.  0 ACMP not enabled 1 ACMP is enabled                                                                                                                                                                                                            |

| 6<br>ACBGS | Analog Comparator Bandgap Select. Selects between the bandgap reference voltage or the ACMPx+ pin as the input to the non-inverting input of the analog comparator.  0 External pin ACMPx+ selected as non-inverting input to comparator  1 Internal reference select as non-inverting input to comparator |

| 5<br>ACF   | Analog Comparator Flag. ACF is set when a compare event occurs. Compare events are defined by ACMOD. ACF is cleared by writing a one to it.  O Compare event has not occurred  Compare event has occurred                                                                                                  |

| 4<br>ACIE  | Analog Comparator Interrupt Enable. Enables the interrupt from the ACMP. When ACIE is set, an interrupt is asserted when ACF is set.  0 Interrupt disabled 1 Interrupt enabled                                                                                                                             |

MC9S08DV60 Series Data Sheet, Rev 3

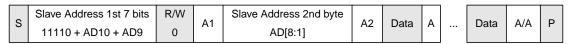

## 11.4.2 10-bit Address

For 10-bit addressing, 0x11110 is used for the first 5 bits of the first address byte. Various combinations of read/write formats are possible within a transfer that includes 10-bit addressing.

#### 11.4.2.1 Master-Transmitter Addresses a Slave-Receiver

The transfer direction is not changed (see Table 11-9). When a 10-bit address follows a start condition, each slave compares the first seven bits of the first byte of the slave address (11110XX) with its own address and tests whether the eighth bit  $(R/\overline{W})$  direction bit) is 0. More than one device can find a match and generate an acknowledge (A1). Then, each slave that finds a match compares the eight bits of the second byte of the slave address with its own address. Only one slave finds a match and generates an acknowledge (A2). The matching slave remains addressed by the master until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Table 11-9. Master-Transmitter Addresses Slave-Receiver with a 10-bit Address

After the master-transmitter has sent the first byte of the 10-bit address, the slave-receiver sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

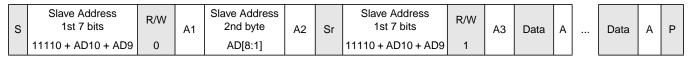

#### 11.4.2.2 Master-Receiver Addresses a Slave-Transmitter

The transfer direction is changed after the second  $R/\overline{W}$  bit (see Table 11-10). Up to and including acknowledge bit A2, the procedure is the same as that described for a master-transmitter addressing a slave-receiver. After the repeated start condition (Sr), a matching slave remembers that it was addressed before. This slave then checks whether the first seven bits of the first byte of the slave address following Sr are the same as they were after the start condition (S) and tests whether the eighth  $(R/\overline{W})$  bit is 1. If there is a match, the slave considers that it has been addressed as a transmitter and generates acknowledge A3. The slave-transmitter remains addressed until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

Table 11-10. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

#### Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers, only when RXF flag is set (see Section 12.3.4.1, "MSCAN Receiver Flag Register (CANRFLG)").

Write: For transmit buffers, anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). Unimplemented for receive buffers.

Reset: Undefined (0x00XX) because of RAM-based implementation

| Register<br>Name |        | Bit 7 | 6            | 5             | 4                | 3                | 2   | 1   | Bit 0 |

|------------------|--------|-------|--------------|---------------|------------------|------------------|-----|-----|-------|

| IDR0             | R<br>W | ID10  | ID9          | ID8           | ID7              | ID6              | ID5 | ID4 | ID3   |

| IDR1             | R<br>W | ID2   | ID1          | ID0           | RTR <sup>1</sup> | IDE <sup>2</sup> |     |     |       |

| IDR2             | R<br>W |       |              |               |                  |                  |     |     |       |

| IDR3             | R<br>W |       |              |               |                  |                  |     |     |       |

|                  | [      |       | = Unused, al | ways read 'x' |                  |                  |     |     |       |

Figure 12-24. Receive/Transmit Message Buffer — Standard Identifier Mapping

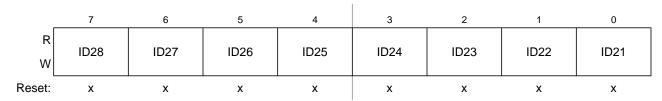

## 12.4.1 Identifier Registers (IDR0-IDR3)

The identifier registers for an extended format identifier consist of a total of 32 bits; ID[28:0], SRR, IDE, and RTR bits. The identifier registers for a standard format identifier consist of a total of 13 bits; ID[10:0], RTR, and IDE bits.

## 12.4.1.1 IDR0-IDR3 for Extended Identifier Mapping

Figure 12-25. Identifier Register 0 (IDR0) — Extended Identifier Mapping

<sup>&</sup>lt;sup>1</sup> The position of RTR differs between extended and standard indentifier mapping.

<sup>&</sup>lt;sup>2</sup> IDE is 0.

#### Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

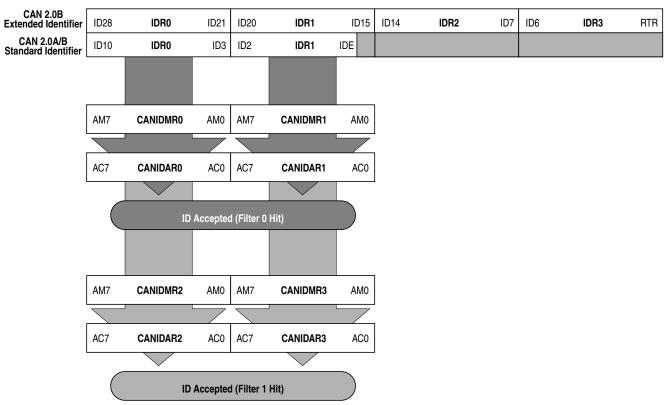

Figure 12-40. 16-bit Maskable Identifier Acceptance Filters

| Table 14-6. SCIxS1 F | Field Descriptions | (continued) |

|----------------------|--------------------|-------------|

|----------------------|--------------------|-------------|

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>FE | Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIxS1 with FE = 1 and then read the SCI data register (SCIxD).  0 No framing error detected. This does not guarantee the framing is correct.  1 Framing error.                                                                                                                                             |

| 0<br>PF | Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD).  No parity error.  Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD). |

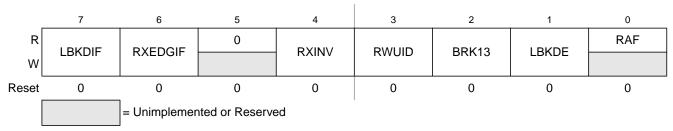

# 14.2.5 SCI Status Register 2 (SCIxS2)

This register has one read-only status flag.

Figure 14-9. SCI Status Register 2 (SCIxS2)

Table 14-7. SCIxS2 Field Descriptions

| Field                   | Description                                                                                                                                                                                                                                                                                                                              |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIF             | LIN Break Detect Interrupt Flag — LBKDIF is set when the LIN break detect circuitry is enabled and a LIN break character is detected. LBKDIF is cleared by writing a "1" to it.  0 No LIN break character has been detected.  1 LIN break character has been detected.                                                                   |

| 6<br>RXEDGIF            | RxD Pin Active Edge Interrupt Flag — RXEDGIF is set when an active edge (falling if RXINV = 0, rising if RXINV=1) on the RxD pin occurs. RXEDGIF is cleared by writing a "1" to it.  0 No active edge on the receive pin has occurred.  1 An active edge on the receive pin has occurred.                                                |

| 4<br>RXINV <sup>1</sup> | Receive Data Inversion — Setting this bit reverses the polarity of the received data input.  0 Receive data not inverted 1 Receive data inverted                                                                                                                                                                                         |

| 3<br>RWUID              | Receive Wake Up Idle Detect— RWUID controls whether the idle character that wakes up the receiver sets the IDLE bit.  0 During receive standby state (RWU = 1), the IDLE bit does not get set upon detection of an idle character.  1 During receive standby state (RWU = 1), the IDLE bit gets set upon detection of an idle character. |

| 2<br>BRK13              | Break Character Generation Length — BRK13 is used to select a longer transmitted break character length.  Detection of a framing error is not affected by the state of this bit.  0 Break character is transmitted with length of 10 bit times (11 if M = 1)  1 Break character is transmitted with length of 13 bit times (14 if M = 1) |

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

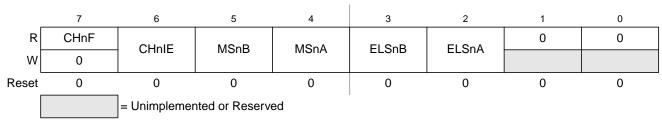

# 16.3.4 TPM Channel n Status and Control Register (TPMxCnSC)

TPMxCnSC contains the channel-interrupt-status flag and control bits used to configure the interrupt enable, channel configuration, and pin function.

Figure 16-12. TPM Channel n Status and Control Register (TPMxCnSC)

Table 16-5. TPMxCnSC Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF  | Channel n flag. When channel n is an input-capture channel, this read/write bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned/center-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. When channel n is an edge-aligned/center-aligned PWM channel and the duty cycle is set to 0% or 100%, CHnF will not be set even when the value in the TPM counter registers matches the value in the TPM channel n value registers. |

|            | A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMxCnSC while CHnF is set and then writing a logic 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF remains set after the clear sequence completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost due to clearing a previous CHnF.                                                                                                              |

|            | Reset clears the CHnF bit. Writing a logic 1 to CHnF has no effect.  O No input capture or output compare event occurred on channel n  Input capture or output compare event on channel n                                                                                                                                                                                                                                                                                                                                                                                   |

| 6<br>CHnIE | Channel n interrupt enable. This read/write bit enables interrupts from channel n. Reset clears CHnIE.  O Channel n interrupt requests disabled (use for software polling)  Channel n interrupt requests enabled                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>MSnB  | Mode select B for TPM channel n. When CPWMS=0, MSnB=1 configures TPM channel n for edge-aligned PWM mode. Refer to the summary of channel mode and setup controls in Table 16-6.                                                                                                                                                                                                                                                                                                                                                                                            |

Chapter 16 Timer/PWM Module (S08TPMV3)

## 16.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

## 16.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

#### 16.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

## 16.4.2.1 Input Capture Mode

With the input-capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input-capture channel, the TPM latches the contents of the TPM counter into the channel-value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

In input capture mode, the TPMxCnVH and TPMxCnVL registers are read only.

When either half of the 16-bit capture register is read, the other half is latched into a buffer to support coherent 16-bit accesses in big-endian or little-endian order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) which may optionally generate a CPU interrupt request.

While in BDM, the input capture function works as configured by the user. When an external event occurs, the TPM latches the contents of the TPM counter (which is frozen because of the BDM mode) into the channel value registers and sets the flag bit.

## 16.4.2.2 Output Compare Mode

With the output-compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel-value registers of an output-compare channel, the TPM can set, clear, or toggle the channel pin.

MC9S08DV60 Series Data Sheet, Rev 3

configure the channel pin as output port pin and set the output pin; configure the channel to generate the EPWM signal but keep ELSnB:ELSnA as 00; configure the other registers (TPMxMODH, TPMxMODL, TPMxCnVH, TPMxCnVL, ...); configure CLKSB:CLKSA bits (TPM v3 starts to generate the high-true EPWM signal, however TPM does not control the channel pin, so the EPWM signal is not available); wait until the TOF is set (or use the TOF interrupt); enable the channel output by configuring ELSnB:ELSnA bits (now EPWM signal is available);

**Table 17-1. BDC Command Summary**

| Command Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |  |

|------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|--|

| SYNC             | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |  |

| ACK_ENABLE       | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to Freescale document order no. HCS08RMv1/D.          |  |

| ACK_DISABLE      | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to Freescale document order no. HCS08RMv1/D.         |  |

| BACKGROUND       | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |  |

| READ_STATUS      | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |  |

| WRITE_CONTROL    | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |  |

| READ_BYTE        | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |  |

| READ_BYTE_WS     | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |  |

| READ_LAST        | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |  |

| WRITE_BYTE       | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |  |

| WRITE_BYTE_WS    | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |  |

| READ_BKPT        | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |  |

| WRITE_BKPT       | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |  |

| GO               | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |  |

| TRACE1           | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |  |

| TAGGO            | Active BDM                   | 18/d                | Same as GO but enable external tagging (HCS08 devices have no external tagging pin       |  |

| READ_A           | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |  |

| READ_CCR         | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |  |

| READ_PC          | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |  |

| READ_HX          | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |  |

| READ_SP          | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |  |

| READ_NEXT        | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                                |  |

| READ_NEXT_WS     | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |  |

| WRITE_A          | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |  |

| WRITE_CCR        | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |  |

| WRITE_PC         | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |  |

| WRITE_HX         | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |  |

| WRITE_SP         | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |  |

| WRITE_NEXT       | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byt located at H:X                               |  |

| WRITE_NEXT_WS    | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |  |

$<sup>^{\</sup>mbox{\scriptsize 1}}$  The SYNC command is a special operation that does not have a command code.

## MC9S08DV60 Series Data Sheet, Rev 3

#### Appendix A Electrical Characteristics

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either V<sub>SS</sub> or V<sub>DD</sub>).

| Num | Rating                                                                                       | Symbol          | Value                    | Unit |

|-----|----------------------------------------------------------------------------------------------|-----------------|--------------------------|------|

| 1   | Supply voltage                                                                               | V <sub>DD</sub> | -0.3 to + 5.8            | V    |

| 2   | Input voltage                                                                                | V <sub>In</sub> | $-0.3$ to $V_{DD} + 0.3$ | V    |

| 3   | Instantaneous maximum current Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | I <sub>D</sub>  | ± 25                     | mA   |

| 4   | Maximum current into V <sub>DD</sub>                                                         | I <sub>DD</sub> | 120                      | mA   |

| 5   | Storage temperature                                                                          | Teta            | -55 to +150              | °C   |

**Table A-2. Absolute Maximum Ratings**

#### **A.4** Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or V<sub>DD</sub> and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and V<sub>SS</sub> or V<sub>DD</sub> will be very small.

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

All functional non-supply pins are internally clamped to  $\rm V_{SS}$  and  $\rm V_{DD}$

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of VDD and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMxCNTH or TPMxCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

#### **B.3.2** Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

## **B.3.2.1** Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

MC9S08DV60 Series Data Sheet, Rev 3

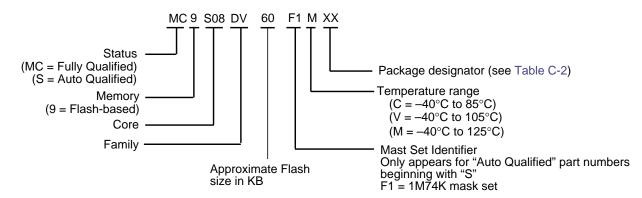

# Appendix C Ordering Information and Mechanical Drawings

# **C.1** Ordering Information

This section contains ordering information for MC9S08DV60 Series devices.

Example of the device numbering system:

## C.1.1 MC9S08DV60 Series Devices

Table C-1. Devices in the MC9S08DV60 Series

| Device Number      | Memory |      | Available Packages <sup>1</sup> |  |

|--------------------|--------|------|---------------------------------|--|

| Device Number      | Flash  | RAM  | Available Fackages              |  |

| MC9S08 <b>DV60</b> | 62,080 | 3072 | - 64-LQFP,<br>48-LQFP, 32-LQFP  |  |

| MC9S08 <b>DV48</b> | 49,152 | 2048 |                                 |  |

| MC9S08 <b>DV32</b> | 33,792 | 2048 |                                 |  |

| MC9S08 <b>DV16</b> | 16,896 | 1024 | 48-LQFP, 32-LQFP                |  |

See for package information.

# C.2 Mechanical Drawings

The following pages are mechanical drawings for the packages described in the following table: