Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dv32mlf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Chapter 1 Device Overview**

<sup>1</sup> ACMP2O is not available.

# 1.2 MCU Block Diagram

Figure 1-1 is the MC9S08DV60 Series system-level block diagram.

### 2.2.1 **Power**

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise. The MC9S08DV60 Series has two V<sub>DD</sub> pins except on the 32-pin package. Each pin must have a bypass capacitor for best noise suppression.

$V_{DDA}$  and  $V_{SSA}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC module. A 0.1- $\mu$ F ceramic bypass capacitor should be located as near to the MCU power pins as practical to suppress high-frequency noise.

### 2.2.2 Oscillator

Immediately after reset, the MCU uses an internally generated clock provided by the multi-purpose clock generator (MCG) module. For more information on the MCG, see Chapter 8, "Multi-Purpose Clock Generator (S08MCGV1)."

The oscillator (XOSC) in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator. Rather than a crystal or ceramic resonator, an external oscillator can be connected to the EXTAL input pin.

Refer to Figure 2-4 for the following discussion.  $R_S$  (when used) and  $R_F$  should be low-inductance resistors such as carbon composition resistors. Wire-wound resistors and some metal film resistors have too much inductance. C1 and C2 normally should be high-quality ceramic capacitors that are specifically designed for high-frequency applications.

$R_F$  is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup; its value is not generally critical. Typical systems use 1 M $\Omega$  to 10 M $\Omega$ . Higher values are sensitive to humidity, and lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin capacitance when selecting C1 and C2. The crystal manufacturer typically specifies a load capacitance which is the series combination of C1 and C2 (which are usually the same size). As a first-order approximation, use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

## 2.2.3 **RESET**

RESET is a dedicated pin with a pull-up device built in. It has input hysteresis, a high current output driver, and no output slew rate control. Internal power-on reset and low-voltage reset circuitry typically make external reset circuitry unnecessary. This pin is normally connected to the standard 6-pin background debug connector so a development system can directly reset the MCU system. If desired, a manual external reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

MC9S08DV60 Series Data Sheet, Rev 3

#### 5.6 Low-Voltage Detect (LVD) System

The MC9S08DV60 Series includes a system to protect against low-voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2 (it will enter stop3 instead), and the current consumption in stop3 with the LVD enabled will be higher.

#### 5.6.1 **Power-On Reset Operation**

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level, V<sub>POR</sub>, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low-voltage detection low threshold, V<sub>I VDI</sub>. Both the POR bit and the LVD bit in SRS are set following a POR.

#### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low-voltage condition by setting LVDRE to 1. The low-voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low-voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

#### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low-voltage warning flag to indicate to the user that the supply voltage is approaching the low-voltage condition. When a low-voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

#### **MCLK Output** 5.7

The PTA0 pin is shared with the MCLK clock output. If the MCSEL bits are all zeroes, the MCLK clock is disabled. Setting any of the MCSEL bits causes the PTA0 pin to output a divided version of the internal MCU bus clock regardless of the state of the port data direction control bit for the pin. The divide ratio is determined by the MCSEL bits. The slew rate and drive strength for the pin are controlled by PTASE0 and PTADS0, respectively. The maximum clock output frequency is limited if slew rate control is enabled, see the electrical specifications for the maximum frequency under different conditions.

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.8 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low-voltage warning function, and to configure the stop mode behavior of the MCU. This register should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

|                  | 7 | 6                           | 5                 | 4          | 3    | 2            | 1            | 0                 |

|------------------|---|-----------------------------|-------------------|------------|------|--------------|--------------|-------------------|

| R                | 0 | 0                           | LVDV <sup>1</sup> | LVWV       | PPDF | 0            | 0            | PPDC <sup>2</sup> |

| W                |   |                             | LVDV.             | LVDV LVVVV |      | PPDACK       |              |                   |

| Power-on Reset:  | 0 | 0                           | 0                 | 0          | 0    | 0            | 0            | 0                 |

| LVD Reset:       | 0 | 0                           | u                 | u          | 0    | 0            | 0            | 0                 |

| Any other Reset: | 0 | 0                           | u                 | u          | 0    | 0            | 0            | 0                 |

|                  |   | = Unimplemented or Reserved |                   |            |      | u = Unaffect | ted by reset |                   |

<sup>&</sup>lt;sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

Figure 5-10. System Power Management Status and Control 2 Register (SPMSC2)

Table 5-11. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>LVDV   | Low-Voltage Detect Voltage Select — This write-once bit selects the low-voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-12.           |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low-voltage warning (LVW) trip point voltage. See Table 5-12.                                                        |

| 3<br>PPDF   | Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.  0 MCU has not recovered from stop2 mode.  1 MCU recovered from stop2 mode. |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit.                                                                                                           |

| 0<br>PPDC   | Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.  O Stop3 mode enabled.  Stop2, partial power down, mode enabled.                   |

Table 5-12. LVD and LVW Trip Point Typical Values<sup>1</sup>

| LVDV:LVWV | LVW Trip Point             | LVD Trip Point             |

|-----------|----------------------------|----------------------------|

| 0:0       | V <sub>LVW0</sub> = 2.74 V | V <sub>LVD0</sub> = 2.56 V |

| 0:1       | V <sub>LVW1</sub> = 2.92 V |                            |

| 1:0       | V <sub>LVW2</sub> = 4.3 V  | V <sub>LVD1</sub> = 4.0 V  |

| 1:1       | V <sub>LVW3</sub> = 4.6 V  |                            |

See Electrical Characteristics appendix for minimum and maximum values.

#### MC9S08DV60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

Chapter 9 Analog Comparator (S08ACMPV3)

## 9.1.4 Block Diagram

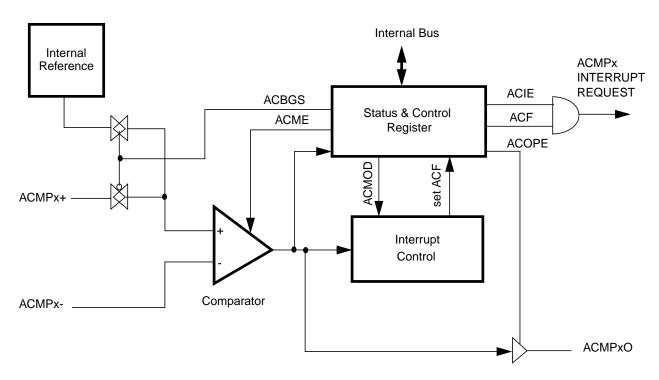

The block diagram for the analog comparator module is shown Figure 9-2.

Figure 9-2. Analog Comparator (ACMP) Block Diagram

# 9.2 External Signal Description

The ACMP has two analog input pins, ACMPx+ and ACMPx- and one digital output pin ACMPxO. Each of these pins can accept an input voltage that varies across the full operating voltage range of the MCU. As shown in Figure 9-2, the ACMPx- pin is connected to the inverting input of the comparator, and the ACMPx+ pin is connected to the comparator non-inverting input if ACBGS is a 0. As shown in Figure 9-2, the ACMPxO pin can be enabled to drive an external pin.

The signal properties of ACMP are shown in Table 9-1.

Signal Function I/O

ACMPx- Inverting analog input to the ACMP. (Minus input)

ACMPx+ Non-inverting analog input to the ACMP. (Positive input)

ACMPxO Digital output of the ACMP. O

**Table 9-1. Signal Properties**

MC9S08DV60 Series Data Sheet, Rev 3

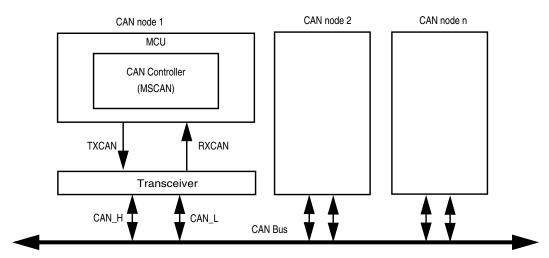

Figure 12-3. CAN System

# 12.3 Register Definition

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

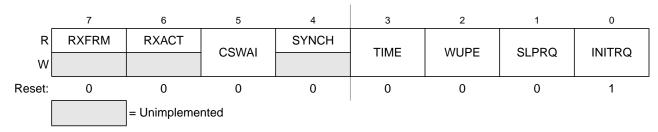

# 12.3.1 MSCAN Control Register 0 (CANCTL0)

The CANCTL0 register provides various control bits of the MSCAN module as described below.

Figure 12-4. MSCAN Control Register 0 (CANCTL0)

#### NOTE

The CANCTL0 register, except WUPE, INITRQ, and SLPRQ, is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

Read: Anytime

Write: Anytime when out of initialization mode; exceptions are read-only RXACT and SYNCH, RXFRM (which is set by the module only), and INITRQ (which is also writable in initialization mode).

| TSEG22 | TSEG21 | TSEG20 | Time Segment 2                |

|--------|--------|--------|-------------------------------|

| 0      | 0      | 0      | 1 Tq clock cycle <sup>1</sup> |

| 0      | 0      | 1      | 2 Tq clock cycles             |

| :      | :      | :      | :                             |

| 1      | 1      | 0      | 7 Tq clock cycles             |

| 1      | 1      | 1      | 8 Tq clock cycles             |

Table 12-7. Time Segment 2 Values

Table 12-8. Time Segment 1 Values

| TSEG13 | TSEG12 | TSEG11 | TSEG10 | Time segment 1                 |

|--------|--------|--------|--------|--------------------------------|

| 0      | 0      | 0      | 0      | 1 Tq clock cycle <sup>1</sup>  |

| 0      | 0      | 0      | 1      | 2 Tq clock cycles <sup>1</sup> |

| 0      | 0      | 1      | 0      | 3 Tq clock cycles <sup>1</sup> |

| 0      | 0      | 1      | 1      | 4 Tq clock cycles              |

| :      | :      | :      | :      | :                              |

| 1      | 1      | 1      | 0      | 15 Tq clock cycles             |

| 1      | 1      | 1      | 1      | 16 Tq clock cycles             |

<sup>&</sup>lt;sup>1</sup> This setting is not valid. Please refer to Table 12-35 for valid settings.

The bit time is determined by the oscillator frequency, the baud rate prescaler, and the number of time quanta (Tq) clock cycles per bit (as shown in Table 12-7 and Table 12-8).

Egn. 12-1

$$\textbf{Bit Time=} \ \frac{(Prescaler\ value)}{f_{\mbox{CANCLK}}} \bullet (1 + TimeSegment1 + TimeSegment2)$$

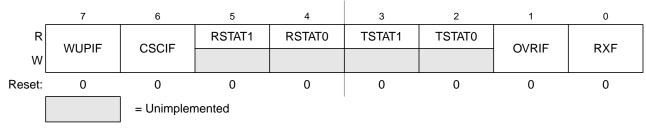

#### **MSCAN Receiver Flag Register (CANRFLG)** 12.3.4.1

A flag can be cleared only by software (writing a 1 to the corresponding bit position) when the condition which caused the setting is no longer valid. Every flag has an associated interrupt enable bit in the CANRIER register.

Figure 12-8. MSCAN Receiver Flag Register (CANRFLG)

MC9S08DV60 Series Data Sheet, Rev 3

This setting is not valid. Please refer to Table 12-35 for valid settings.

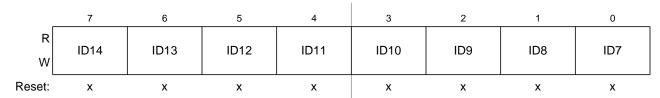

### Table 12-25. IDR0 Register Field Descriptions — Extended

| Field            | Description                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[28:21] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

| _      | 7    | 6    | 5    | 4                  | 3                  | 2    | 1    | 0    |

|--------|------|------|------|--------------------|--------------------|------|------|------|

| R<br>W | ID20 | ID19 | ID18 | SRR <sup>(1)</sup> | IDE <sup>(1)</sup> | ID17 | ID16 | ID15 |

| Reset: | Х    | Х    | Х    | Х                  | Х                  | Х    | Х    | x    |

Figure 12-26. Identifier Register 1 (IDR1) — Extended Identifier Mapping

## Table 12-26. IDR1 Register Field Descriptions — Extended

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5<br>ID[20:18] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                   |

| 4<br>SRR         | Substitute Remote Request — This fixed recessive bit is used only in extended format. It must be set to 1 by the user for transmission buffers and is stored as received on the CAN bus for receive buffers.                                                                                                                                                                                                   |

| 3<br>IDE         | ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.  O Standard format (11 bit)  Extended format (29 bit) |

| 2:0<br>ID[17:15] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                   |

Figure 12-27. Identifier Register 2 (IDR2) — Extended Identifier Mapping

### Table 12-27. IDR2 Register Field Descriptions — Extended

| Field           | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[14:7] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

### MC9S08DV60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>1</sup> SRR and IDE are both 1s.

| Table 12-30. | . IDR1 | Register | <b>Field</b> | <b>Descriptions</b> |

|--------------|--------|----------|--------------|---------------------|

|--------------|--------|----------|--------------|---------------------|

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5<br>ID[2:0] | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 12-29.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4<br>RTR       | Remote Transmission Request — This flag reflects the status of the Remote Transmission Request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.  O Data frame Remote Transmission Request — This flag reflects the status of the Remote Transmission Request bit in the CAN frame and supports the transmission of the Remote Transmission Request bit in the CAN frame and supports the transmission of the Remote Transmission Request bit in the CAN frame and supports the transmission of the Remote Transmission Request bit in the CAN frame. |

| 3<br>IDE       | ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.  O Standard format (11 bit)  Extended format (29 bit)                                                                                                                                                                                                                                                                                                                                                       |

Figure 12-31. Identifier Register 2 — Standard Mapping

Figure 12-32. Identifier Register 3 — Standard Mapping

# 12.4.3 Data Segment Registers (DSR0-7)

The eight data segment registers, each with bits DB[7:0], contain the data to be transmitted or received. The number of bytes to be transmitted or received is determined by the data length code in the corresponding DLR register.

The MSCAN then schedules the message for transmission and signals the successful transmission of the buffer by setting the associated TXE flag. A transmit interrupt (see Section 12.5.7.2, "Transmit Interrupt") is generated when TXEx is set and can be used to drive the application software to re-load the buffer.

If more than one buffer is scheduled for transmission when the CAN bus becomes available for arbitration, the MSCAN uses the local priority setting of the three buffers to determine the prioritization. For this purpose, every transmit buffer has an 8-bit local priority field (PRIO). The application software programs this field when the message is set up. The local priority reflects the priority of this particular message relative to the set of messages being transmitted from this node. The lowest binary value of the PRIO field is defined to be the highest priority. The internal scheduling process takes place whenever the MSCAN arbitrates for the CAN bus. This is also the case after the occurrence of a transmission error.

When a high priority message is scheduled by the application software, it may become necessary to abort a lower priority message in one of the three transmit buffers. Because messages that are already in transmission cannot be aborted, the user must request the abort by setting the corresponding abort request bit (ABTRQ) (see Section 12.3.8, "MSCAN Transmitter Message Abort Request Register (CANTARQ)".) The MSCAN then grants the request, if possible, by:

- 1. Setting the corresponding abort acknowledge flag (ABTAK) in the CANTAAK register.

- 2. Setting the associated TXE flag to release the buffer.

- 3. Generating a transmit interrupt. The transmit interrupt handler software can determine from the setting of the ABTAK flag whether the message was aborted (ABTAK = 1) or sent (ABTAK = 0).

#### 12.5.2.3 Receive Structures

The received messages are stored in a five stage input FIFO. The five message buffers are alternately mapped into a single memory area (see Figure 12-38). The background receive buffer (RxBG) is exclusively associated with the MSCAN, but the foreground receive buffer (RxFG) is addressable by the CPU (see Figure 12-38). This scheme simplifies the handler software because only one address area is applicable for the receive process.

All receive buffers have a size of 15 bytes to store the CAN control bits, the identifier (standard or extended), the data contents, and a time stamp, if enabled (see Section 12.4, "Programmer's Model of Message Storage").

The receiver full flag (RXF) (see Section 12.3.4.1, "MSCAN Receiver Flag Register (CANRFLG)") signals the status of the foreground receive buffer. When the buffer contains a correctly received message with a matching identifier, this flag is set.

On reception, each message is checked to see whether it passes the filter (see Section 12.5.3, "Identifier Acceptance Filter") and simultaneously is written into the active RxBG. After successful reception of a valid message, the MSCAN shifts the content of RxBG into the receiver FIFO<sup>2</sup>, sets the RXF flag, and generates a receive interrupt (see Section 12.5.7.3, "Receive Interrupt") to the CPU<sup>3</sup>. The user's receive handler must read the received message from the RxFG and then reset the RXF flag to acknowledge the interrupt and to release the foreground buffer. A new message, which can follow immediately after the IFS

MC9S08DV60 Series Data Sheet, Rev 3

<sup>1.</sup> The transmit interrupt occurs only if not masked. A polling scheme can be applied on TXEx also.

<sup>2.</sup> Only if the RXF flag is not set.

<sup>3.</sup> The receive interrupt occurs only if not masked. A polling scheme can be applied on RXF also.

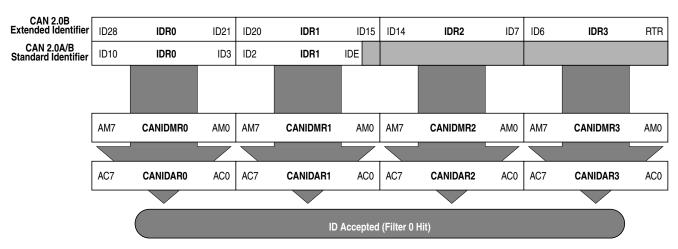

- Four identifier acceptance filters, each to be applied to

- a) the 14 most significant bits of the extended identifier plus the SRR and IDE bits of CAN 2.0B messages or

- b) the 11 bits of the standard identifier, the RTR and IDE bits of CAN 2.0A/B messages. Figure 12-40 shows how the first 32-bit filter bank (CANIDAR0–CANIDA3, CANIDMR0–3CANIDMR) produces filter 0 and 1 hits. Similarly, the second filter bank (CANIDAR4–CANIDAR7, CANIDMR4–CANIDMR7) produces filter 2 and 3 hits.

- Eight identifier acceptance filters, each to be applied to the first 8 bits of the identifier. This mode implements eight independent filters for the first 8 bits of a CAN 2.0A/B compliant standard identifier or a CAN 2.0B compliant extended identifier. Figure 12-41 shows how the first 32-bit filter bank (CANIDAR0–CANIDAR3, CANIDMR0–CANIDMR3) produces filter 0 to 3 hits. Similarly, the second filter bank (CANIDAR4–CANIDAR7, CANIDMR4–CANIDMR7) produces filter 4 to 7 hits.

- Closed filter. No CAN message is copied into the foreground buffer RxFG, and the RXF flag is never set.

Figure 12-39. 32-bit Maskable Identifier Acceptance Filter

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 4<br>MODFEN  | Master Mode-Fault Function Enable — When the SPI is configured for slave mode, this bit has no meaning or effect. (The $\overline{SS}$ pin is the slave select input.) In master mode, this bit determines how the $\overline{SS}$ pin is used (refer to Table 13-2 for more details).  0 Mode fault function disabled, master $\overline{SS}$ pin reverts to general-purpose I/O not controlled by SPI 1 Mode fault function enabled, master $\overline{SS}$ pin acts as the mode fault input or the slave select output              |  |  |  |  |  |  |  |

| 3<br>BIDIROE | Bidirectional Mode Output Enable — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1, BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin. Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO (SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect. 0 Output driver disabled so SPI data I/O pin acts as an input 1 SPI I/O pin enabled as an output |  |  |  |  |  |  |  |

| 1<br>SPISWAI | SPI Stop in Wait Mode 0 SPI clocks continue to operate in wait mode 1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 0<br>SPC0    | SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.  0 SPI uses separate pins for data input and data output 1 SPI configured for single-wire bidirectional operation                          |  |  |  |  |  |  |  |

# 13.4.3 SPI Baud Rate Register (SPIBR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

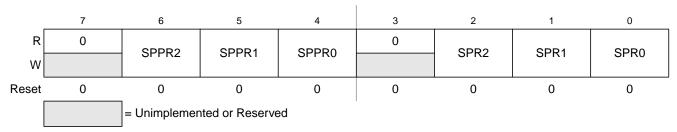

Figure 13-7. SPI Baud Rate Register (SPIBR)

Table 13-4. SPIBR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>SPPR[2:0] | SPI Baud Rate Prescale Divisor — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 13-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 13-4). |

| 2:0<br>SPR[2:0]  | SPI Baud Rate Divisor — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 13-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 13-4). The output of this divider is the SPI bit rate clock for master mode.            |

MC9S08DV60 Series Data Sheet, Rev 3

Chapter 13 Serial Peripheral Interface (S08SPIV3)

## 13.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 13.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

#### 13.5.1 SPI Clock Formats

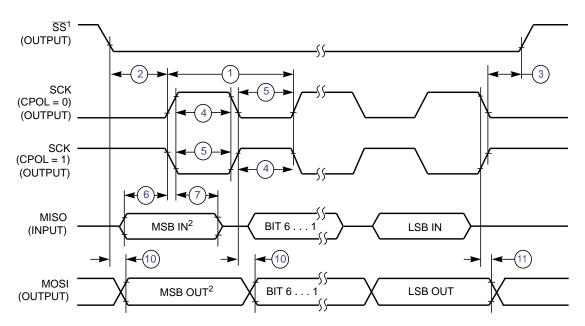

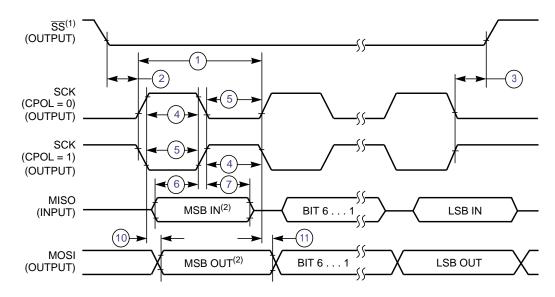

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 13-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output

#### Chapter 16 Timer/PWM Module (S08TPMV3)

All TPM interrupts are listed in Table 16-8 which shows the interrupt name, the name of any local enable that can block the interrupt request from leaving the TPM and getting recognized by the separate interrupt processing logic.

| Interrupt | Local<br>Enable | Source           | Description                                                                                                            |

|-----------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| TOF       | TOIE            | Counter overflow | Set each time the timer counter reaches its terminal count (at transition to next count value which is usually 0x0000) |

| CHnF      | CHnIE           | Channel event    | An input capture or output compare event took place on channel n                                                       |

**Table 16-8. Interrupt Summary**

The TPM module will provide a high-true interrupt signal. Vectors and priorities are determined at chip integration time in the interrupt module so refer to the user's guide for the interrupt module or to the chip's complete documentation for details.

## 16.6.2 Description of Interrupt Operation

For each interrupt source in the TPM, a flag bit is set upon recognition of the interrupt condition such as timer overflow, channel-input capture, or output-compare events. This flag may be read (polled) by software to determine that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will generate whenever the associated interrupt flag equals one. The user's software must perform a sequence of steps to clear the interrupt flag before returning from the interrupt-service routine.

TPM interrupt flags are cleared by a two-step process including a read of the flag bit while it is set (1) followed by a write of zero (0) to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

## 16.6.2.1 Timer Overflow Interrupt (TOF) Description

The meaning and details of operation for TOF interrupts varies slightly depending upon the mode of operation of the TPM system (general purpose timing functions versus center-aligned PWM operation). The flag is cleared by the two step sequence described above.

#### 16.6.2.1.1 Normal Case

Normally TOF is set when the timer counter changes from 0xFFFF to 0x0000. When the TPM is not configured for center-aligned PWM (CPWMS=0), TOF gets set when the timer counter changes from the terminal count (the value in the modulo register) to 0x0000. This case corresponds to the normal meaning of counter overflow.

MC9S08DV60 Series Data Sheet, Rev 3

#### **Chapter 17 Development Support**

**A-Only** — Trigger when the address matches the value in comparator A

**A OR B** — Trigger when the address matches either the value in comparator A or the value in comparator B

**A Then B** — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

**A AND B Data (Full Mode)** — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**A AND NOT B Data (Full Mode)** — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range** ( $A \le Address \le B$ ) — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

Outside Range (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

#### **Appendix A Electrical Characteristics**

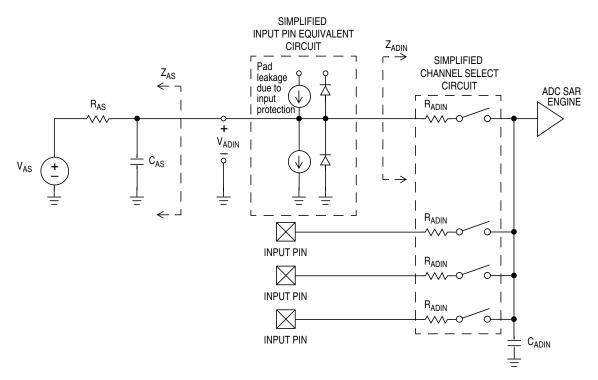

Figure A-1. ADC Input Impedance Equivalency Diagram

Table A-10. 12-bit ADC Characteristics (V<sub>REFH</sub> = V<sub>DDAD</sub>, V<sub>REFL</sub> = V<sub>SSAD</sub>)

| Characteristic               | Conditions                    | С | Symb                                   | Min  | Typ <sup>1</sup> | Max | Unit | Comment              |

|------------------------------|-------------------------------|---|----------------------------------------|------|------------------|-----|------|----------------------|

| Supply Current               | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 133              | _   | μА   | ADC current only     |

| Supply Current               | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 218              | _   | μА   | ADC current only     |

| Supply Current               | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _   | μА   | ADC current only     |

| Supply Current               | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | D | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.582            | 1   | mA   | ADC current only     |

| Supply Current               | Stop, Reset, Module Off       |   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.011            | 1   | μА   | ADC current only     |

| ADC                          | High Speed (ADLPC=0)          | Р | f <sub>ADACK</sub>                     | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> = |

| Asynchronous<br>Clock Source | Low Power (ADLPC=1)           |   |                                        | 1.25 | 2                | 3.3 |      | 1/f <sub>ADACK</sub> |

385

#### NOTES:

- 1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure A-7. SPI Master Timing (CPHA = 0)

#### NOTES:

- 1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure A-8. SPI Master Timing (CPHA = 1)

**Appendix A Electrical Characteristics**

## A.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East). For more detailed information concerning the evaluation results, conditions and setup, please refer to the EMC Evaluation Report for this device.

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

Table A-18. Radiated Emissions for 3M05C Mask Set

| Parameter                     | Symbol              | Conditions                                               | Frequency      | f <sub>osc</sub> /f <sub>CPU</sub> | Level <sup>1</sup><br>(Max) | Unit |

|-------------------------------|---------------------|----------------------------------------------------------|----------------|------------------------------------|-----------------------------|------|

|                               | V <sub>RE_TEM</sub> | V <sub>DD</sub> = 5<br>T <sub>A</sub> = +25°C<br>64 LQFP | 0.15 – 50 MHz  |                                    | 18                          | dΒμV |

|                               |                     |                                                          | 50 – 150 MHz   |                                    | 18                          |      |

| Radiated emissions,           |                     |                                                          | 150 – 500 MHz  | 16 MHz<br>Crystal                  | 13                          |      |

| electric field — Conditions - |                     |                                                          | 500 – 1000 MHz | 20 MHz Bus                         | 7                           |      |

|                               |                     |                                                          | IEC Level      |                                    | L                           | _    |

|                               |                     |                                                          | SAE Level      |                                    | 2                           | _    |

Data based on qualification test results.

# Appendix B Timer Pulse-Width Modulator (TPMV2)

#### **NOTE**

This chapter refers to S08TPM version 2, which applies to the 3M05C and older mask sets of this device. )M74K and newer mask set devices use S08TPM version 3. If your device uses mask 0M74K or newer, please refer to Chapter 16, "Timer Pulse-Width Modulator (S08TPMV3) for information pertaining to that module.

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

#### **B.0.1** Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

## **B.0.2** Block Diagram

Figure B-1 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

399

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

## **B.3.2.2** Output Compare Mode

With the output compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel value registers of an output compare channel, the TPM can set, clear, or toggle the channel pin.

In output compare mode, values are transferred to the corresponding timer channel value registers only after both 8-bit bytes of a 16-bit register have been written. This coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An output compare event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

## **B.3.2.3** Edge-Aligned PWM Mode

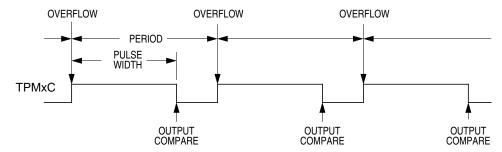

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS = 0) and can be used when other channels in the same TPM are configured for input capture or output compare functions. The period of this PWM signal is determined by the setting in the modulus register (TPMxMODH:TPMxMODL). The duty cycle is determined by the setting in the timer channel value register (TPMxCnVH:TPMxCnVL). The polarity of this PWM signal is determined by the setting in the ELSnA control bit. Duty cycle cases of 0 percent and 100 percent are possible.

As Figure B-10 shows, the output compare value in the TPM channel registers determines the pulse width (duty cycle) of the PWM signal. The time between the modulus overflow and the output compare is the pulse width. If ELSnA = 0, the counter overflow forces the PWM signal high and the output compare forces the PWM signal low. If ELSnA = 1, the counter overflow forces the PWM signal low and the output compare forces the PWM signal high.

Figure B-10. PWM Period and Pulse Width (ELSnA = 0)

When the channel value register is set to 0x0000, the duty cycle is 0 percent. By setting the timer channel value register (TPMxCnVH:TPMxCnVL) to a value greater than the modulus setting, 100% duty cycle can be achieved. This implies that the modulus setting must be less than 0xFFFF to get 100% duty cycle.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to either register, TPMxCnVH or TPMxCnVL, write to buffer registers. In edge-PWM mode, values are transferred to the corresponding timer channel registers only after both 8-bit bytes of a 16-bit register have been written and